1

(21)4683077/24

(22)24.04.89

(46) 23.04.91. Бюл. I 15

(72) В.Б.Динкевич и В.К.Маслов

(53) 681.3(088.8)

(56) Авторское свидетельство СССР

р 1506453, кл. G 06 F 15/336, 1988.

Авторское свидетельство СССР № 783799, кл. G 06 F 15/336, 1979.

(54) КОРРЕЛОМЕТР

(57) Изобретение относится к вычислительной и измерительной технике и может быть использовано для определения корреляционной функции одного из суммы случайных процессов с изменяющейся в процессе измерения задержкой. Цель изобретения - повышение точности. Коррелометр содерлит группу

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелометр | 1979 |

|

SU783799A1 |

| Устройство для определения взаимных корреляционных функций | 1981 |

|

SU1016791A1 |

| Устройство для определения взаимной корреляционной функции | 1983 |

|

SU1108463A1 |

| Коррелометр | 1977 |

|

SU682904A1 |

| Многофункциональный цифровой коррелометр | 1983 |

|

SU1096656A1 |

| Вероятностный коррелометор | 1980 |

|

SU892449A1 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1406602A1 |

| Взаимокоррелятор | 1984 |

|

SU1201846A1 |

| Коррелометр | 1983 |

|

SU1091173A1 |

| Многоканальный многомерный цифровой коррелометр | 1984 |

|

SU1187177A1 |

э

Ј Јь

:л

о

Фил.}

Внход

33 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, сумматоры 34, 35, регистры 36-38, вычи- татель 39, аналого-цифровые преобразователи 1, 2, регистр 3 сдвига,блоки 4 умножения, группы 5-23 элементов И, блоки 6 усреднения, элемент

Изобретение относится к вычислительной и измерительной технике и может быть использовано для определения корреляционной функции одного из суммы случайных процессов с изменяющейся в процессе измерения задержкой.

Цель изобретения - повышение точности измерения корреляционной функции.

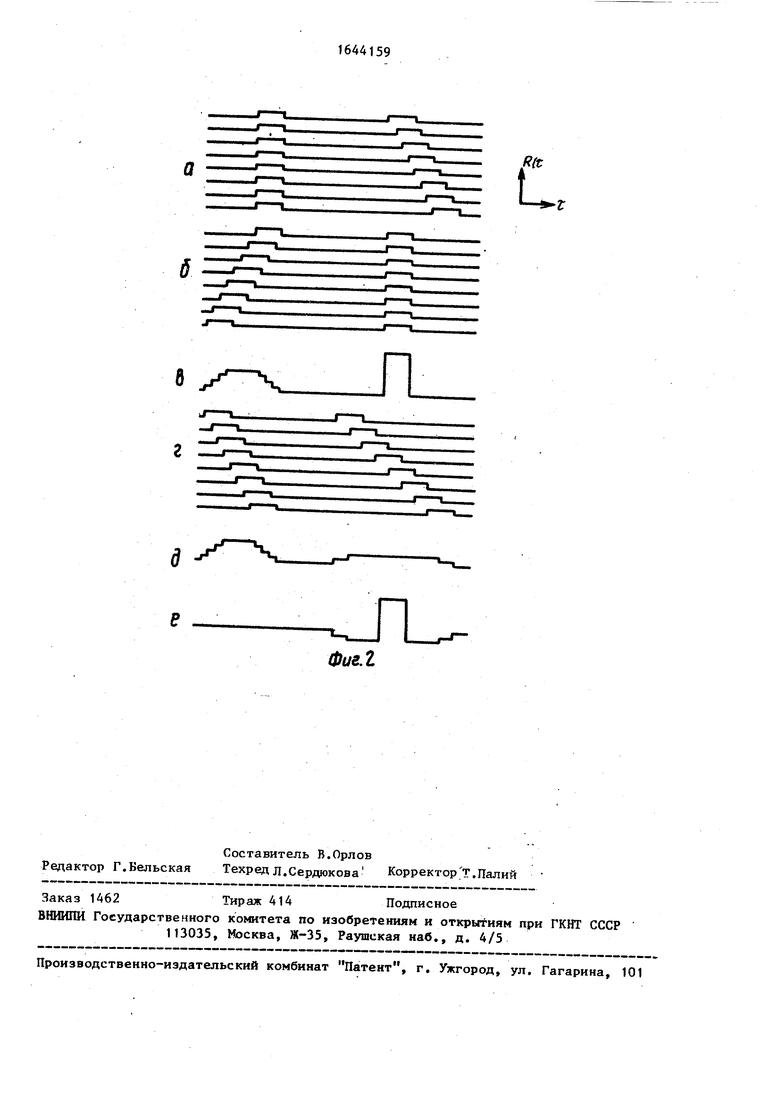

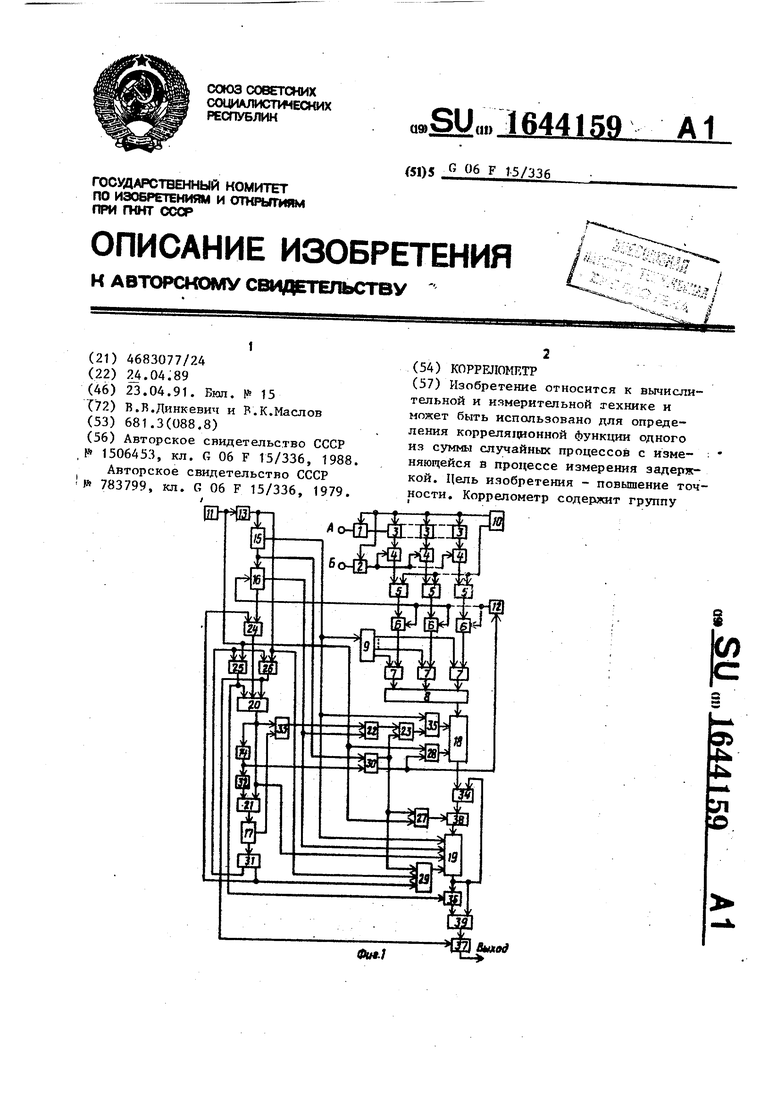

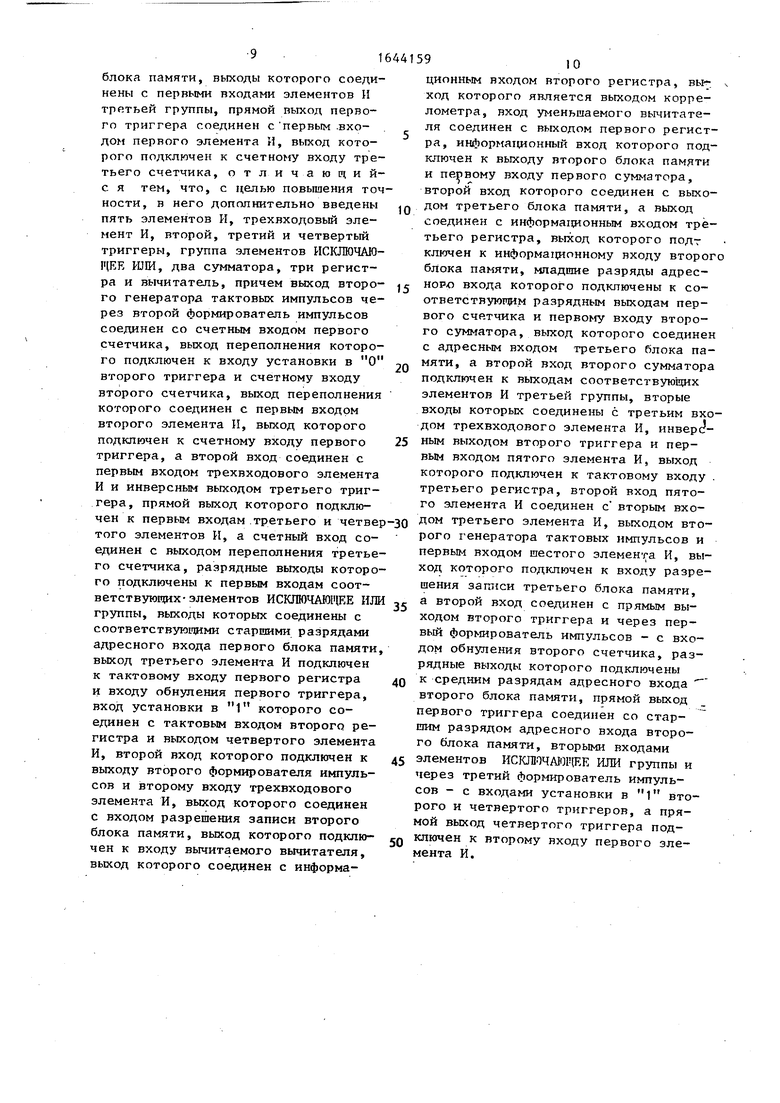

На фиг.1 показана функциональная схема предлагаемого коррелометра; на фиг.2 - частные и результирующие

коррелограммы (ЧК и РК), формируемые в коррелометре.

Коррелометр содержит аналого-цифровой (го-разрядный) преобразова- тель (АЦП) 1, А1Щ (р-разрядный) 2, регистр 3 сдвига (ril-разрядный), группу блоков 4 умножения (пр-разрядных), группу 5 элементов И,группу блоков 6 усреднения, группу элементов И 7, многовходовый элемент ИЛИ 8, дешифратор 9, генераторы 10, 11 тактовых импульсов, формирователи 12-14 импульсов, счетчики 15 - 17, блоки 18, 19 памяти, триг- гер 20, элемент И 21, блок 22 памяти, группу 23 элементов И, элементы И 24-28, трехвходовый элемент И 29, триггеры 30-32, группу 33 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, сумматоры 34, 35, регистры 36-38, вычитатель 39.

S

Коррелометр работает следующим образом. В исходном состоянии все счетчики, триггеры, регистры 36 и 37, блок 19 памяти и блоки 6 усреднения обнулены. Сигнал А поступает на вход А1Щ 1 и в момент прихода на его тактовый вход импульса генератора 10 преобразуется в n-разрядный двоичный код. Код поступает на входы п-раз- рядного регистра 3 сдвига, выполняющего роль цифровой линии задержки. Длина регистра 3 определяется треИЛИ 8, дешифратор 9, генераторы 10, 11 тактовых импульсов, формирователи 12-14 импульсов, счетчики 15-17, блоки. 18, 19, 22 памяти, триггеры 20, 30-32, элементы И 21, 24-29, группу элементов II 7. 2 ил.

5

0

с

0 5 0 5

0 ,

ij.

буемой задержкой Јмакс и количестве п ЧК:

Р

,° МО КС,.

1 -г+ 2п,,

Лс

С появлением каждого нового импульса на первом выходе генератора 10 отсчеты входного сигнала А продвигаются вправо по регистру 3. Задержанные на различные интервалы времени отсчеты сигнала А поступают на блоки 4 умножения. На вторые входы блоков 4 умножения поступают отсчеты сигнала В с выходов АЦП 2. Коды произведений синхронно с« тактовыми импульсами, вырабатываемыми на втором выходе генератора 10,передаются через группу 5 элементов И в блоки 6 усреднения. Импульсы на втором выходе генератора 10 задержаны относительно импульсов на его первом выходе на время формирования произведений в блоках 4 умножения.

Накопление произведений в блоках 6 усреденения продолжается в течение времени Т. .t.

По истечении времени Т в блоках 6 усреднения сформирована п;на ЧК. Во время ее накопления импульсы ге- нератора 11 поступают на вход формирователя 13, благодаря чему по каждому импульсу генератора 11 формируется последовательность из двух неперекрывающихся импульсов на выходах собственно генератора 11 и формирователя 13. Импульсы с выхода последнего поступают на последовательно соединенные счетчики 15 и 16., Сигнал переполнения счетчика 16 через открытый элемент И 24 проходит на счетный вход триггера 20. Его входы установки и обнуления свободны, так как элементы И 25 и 26 заперты сигналом с прямого выхода обнуленного триггера 31. Частоты генераторов 10 и 11 подобраны так, что за время изменения состояния триггера 20 в 1 и снова в О, т.е. за

время двукратного заполнения счетчика 16, в блоках 6 усреднения происходит накопление одной ЧК с фактором усреднения N4. Спад сигнала на прямом выходе триггера 20, свидетель ствующий об окончании накопления ЧК. возбуждает импульс на выходе формирователя 14, который поступает на входы установки триггеров 30 и 32 и переводит их в 1. Элемент И 28 открывается, и импульсы генератора 11 проходят на вход записи блока 18 памяти. Предполагается, что блоки 18 и 19 памяти постоянно работают в режиме считывания, за исключением моментов, когда на их входы записи поступают импульсы. Коды на адресных входах блока 18 памяти равны кодам на разрядных выходах счетчика 15, та как группа 23 элементов И закрыта сигналом логического О с инверсного выхода триггера 30. Разрядные выходы счетчика 15, емкость которого равна 1, соединены с входами дешифратора 9, благодаря чему элементы И 7, последовательно открываются и происходит последовательное считывание ординат ЧК, накопленных в блоках 6, через элементы И 7 и ИЛИ 8. За 1 импульсов генератора 11 происходит запись всех ординат ЧК в блок 18 памяти, который содержит 1 ячеек. При этом нулевая ордината записывается по адресу 0, первая - по адресу 1,..., последняя - по адресу 1-1. Процесс записи завершается при переполнении счетчика 15, когда его импульс переполнения возвращает триггер 30 в О и элемент И 28 закрывается. По спаду сигнала на прямом выходе триггера 30 формирователь 12 генерирует импульс сброса блоков 6 усреднения и счетчика 16, после чего начинает накапливаться следующая ЧК. Одновременно начинается процедура переписи в блок 19 памяти нулевой ЧК, запись которой в блок 18 к этому моменту завершена.

В каждом цикле работы коррелометра (цикл - это период накопления одной ЧК в блоках 6 усреднения) ЧК записывается в блок 19 памяти столько раз, сколько моделей изменения задержки, положительных и отрицательных, реализуется в коррелометре. Происходит это так. По окончании записи нулевой ЧК в блок 18 памяти счетчики 15-17, а также триггер 20 обнуле0

ны. О с прямого выхода триггера 20 поступает на объединенные входы группы 33 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, которые выполняют функцию управляемых повторителей-инверторов. Благодаря этому указанные элементы повторяют на своих выходах входные сигналы и прямой код разрядных выходов счетчика 17, т.е. код 0 поступает на входы старших адресных разрядов блока памяти 22, выполненного в виде постоянного запоминающего устройства. При этом на выходах блока 22 па5 мяти сохраняется код 0 независимо от состояния счетчика 16, разрядные выходы которого соединены с входами младших адресных разрядов блока 22. Код с разрядных выходов счетчика 15

0 складывается на 1-разрядном сумматоре 35 с нулем, поступившим с выхода блока 22 через группу 23 элементов И, открытых благодаря присутствию логической 1 на инверсном выходе

5 триггера 30. В результате код с разрядных выходов счетчика 15 поступает на адресные входы блока 18 памяти. К моменту поступления очередного импульса генератора 11 блрки 18 и 19

0 памяти находятся в состоянии считывания. Поскольку счетчик 15 обнулен, на адресные входы блока 18 памяти поступает код нуля. На выходе блока

18памяти формируется код нулевой ординаты нулевой ЧК. На выходе блока

19памяти присутствует код 0, так

как в исходном состоянии он был обну-/ лен. Значение нулевой ординаты проходит на выход сумматора 34 и по спаду

0 импульса генератора 11, прошедшего через элемент И 27 на тактовый вход регистра 38 (хранения), записывается в последний. После этого по импульсу формирователя 13, прошедшему через

5 элемент И 29 на вход записи блока 19 памяти, происходит запись нулевой ординаты нулевой ЧК в блок 19 памяти. По спаду этого импульса содержимое счетчика 15 увеличивается на 1.

0 Следующий импульс генератора 11 снова возбуждает последовательность из двух неперекрывающихся импульсов на выходах собственно генератора 11 и формирователя 13. Благодаря этому первая ордината нулевой ЧК также записывается в блок 19 памяти. Чер.ез 1 импульсов на выходе генератора 11 все ординаты нулевой ЧК будут записаны в блок 19 памяти.

5

5

При переполнении счетчика 16 им- пульс переполнения через элемент И 24, открытый благодаря присутствию логической 1 на инверсном выходе триггера 31, поступает на Счетный вход триггера 20 и устанавливает его в 1. После этого начинается запись нулевой ЧК в блок 19 памяти еще q раз, что необходимо для формирования q PK отрицательных моделей.

Сигнал переполнения счетчика 16 устанавливает триггер 20 в 1, и начинается формирование промежуточных коррелограмм для отрицательных моделей. По окончании этой процедуры счетчик 16 снова переполняется и обнуляет триггер 20, на чем заканчивается второй цикл работы коррелометра.

Следующие циклы его работы в первом режиме протекают аналогичным образом. Количество циклов определяется счетчиком 17 и равно n N/N{. Емкость счетчика 17 равна п. В результате в блоке 19 памяти накоплены q PK, каждая из которых соответствует одной из q положительных моделей изменения задержки между входными сигналами.

Переполнение счетчика 17 переводит триггер 31 в 1. Потенциал логического О с его инверсного выхода закрывает элементы И 24 и 29, что блокирует поступление импульсов на счетный вход триггера 20 и запрещает режим записи в блок 19 памяти. Начинается второй режим работы - вычитание РК отрицательных моделей из РК положительных. Из блока 19 памяти считывается нулевая ордината нулевой положительной модели. Импульс генератора 11 проходит через элемент И 2 и подтверждает нулевое состояние триггера 20. По спаду этого импульса происходит запись указанной ординаты в регистр 36. Импульс формирователя 13 проходит через элемент И 2 и устанавливает триггер 20 в 1. Пр этом из блока 19 памяти считывается нулевая ордината нулевой отрицательной модели, которая на вычитателе 39 вычитается из содержимого регистра 36. По спаду импульса на выходе элемента И 26 разность записывается в регистр 37. Аналогично вычитаются следующие ординаты, и т.д. Таким образом, на выходе регистра 37 после0

5

0

5

0

5

0

5

0

5

довательно формируются разности одноименных ординат одноименных положительных и отрицательных моделей. Полученный результат представляет собой коррелограмму процесса у, очищенную от следа процесса х.

Формула изобретения

Коррелометр, содержащий два аналого-цифровых преобразователя,регистр сдвига, группу блоков умножения три группы элементов И, группу блоков усреднения, многовходовый элемент ИЛИ, дешифратор, два генератора тактовых импульсов, три формирователя импульсов, три счетчика, три блока памяти, первый элемент И и первый триггер, причем информационные входы первого и второго аналого-цифровых преобразователей являются соответствующими информационными входами коррелометра, выход первого аналого- циАрового преобразователя соединен с информационным входом регистра сдвига, разрядные выходы которого подключены к первым входам соответствующих блоков умножения группы, вторые входы которых объединены и подключены к выходу второго аналого-цифрового преобразователя, вход запуска которого соединен с входом запуска первого аналого-цифрового преобразователя, синхровходом регистра сдвига и первым выходом первого генератора тактовых импульсов, второй выход которого подключен к первым входам элементов И первой группы, вторые входы которых соединены с выходами соответствующих блоков умножения группы, выходы элементов И первой группы подключены к информационным входам соответствующих блоков усреднения группы, входы обнуления которых подключены к выходу первого формирователя импульсов, а выходы соединены с первыми входами соответствующих элементов И второй группы, вторые входы которых подключены к соответствующим выходам дешифратора, а выходы соединены с входами многовходово- го элемента ИЛИ, выход которого подключен к информационному входу первого блока памяти, вход дешифратора соединен с информационным выходом первого счетчика, разрядные выходы второго счетчика подключены к младшим разрядам адресного входа первого

916

блока памяти, выходы которого соединены с первыми входами элементов И трртьей группы, прямой выход первого триггера соединен с первым вхо- дом первого элемента И, выход которого подключен к счетному входу третьего счетчика, отличаю щ и и- с я тем, что, с целью повышения точности, в него дополнительно введены пять элементов И, трехвходовый элемент И, второй, третий и четвертый триггеры, группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, два сумматора, три регистра и вычитатель, причем выход второ- го генератора тактовых импульсов через второй формирователь импульсов соединен со счетным входом первого счетчика, выход переполнения которого подключен к входу установки в О второго триггера и счетному входу второго счетчика, выход переполнения которого соединен с первым входом второго элемента И, выход которого подключен к счетному входу первого триггера, а второй вход соединен с первым входом трехвходового элемента И и инверсным выходом третьего триггера, прямой выход которого подключен к первым входам третьего и четвер того элементов И, а счетный вход соединен с выходом переполнения третьего счетчика, разрядные выходы которого подключены к первым входам соответствующих- элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, выходы которых соединены с соответствующими старшими разрядами адресного входа первого блока памяти, выход третьего элемента И подключен к тактовому входу первого регистра и входу обнуления первого триггера, вход установки в 1 которого соединен с тактовым входом второго регистра и выходом четвертого элемента И, второй вход которого подключен к выходу второго формирователя импульсов и второму входу трехвходового элемента И, выход которого соединен с входом разрешения записи второго блока памяти, выход которого подклю- чен к входу вычитаемого вычитателя, выход которого соединен с информа9ю

ционным входом второго регистра, вы ч ход которого является выходом коррелометра, вход уменьшаемого вычнтате- ля соединен с выходом первого регистра, информационный вход которого подключен к выходу второго блока памяти и первому входу первого сумматора, второй вход которого соединен с выходом третьего блока памяти, а выход соединен с информационным входом третьего регистра, выход которого подт ключей к информационному входу второго блока памяти, младшие разряды адресного входа которого подключены к соответствующим разрядным выходам первого счетчика и первому входу второго сумматора, выход которого соединен с адресным входом третьего блока памяти, а второй вход второго сумматора подключен к выходам соответствующих элементов И третьей группы, вторые входы которых соединены с третьим входом трехвходового элемента И, инверсным выходом второго триггера и первым входом пятого элемента И, выход которого подключен к тактовому входу третьего регистра, второй вход пятого элемента И соединен с вторым входом третьего элемента И, выходом второго генератора тактовых импульсов и первым входом шестого элемента И, выход которого подключен к входу разрешения записи третьего блока памяти, а второй вход соединен с прямым выходом второго триггера и через первый формирователь импульсов - с входом обнуления второго счетчика, разрядные выходы которого подключены к средним разрядам адресного входа второго блока памяти, прямой выход первого триггера соединен со старшим разрядом адресного входа второго блока памяти, вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы и через третий формирователь импульсов - с входами установки в 1 второго и четвертого триггеров, а прямой выход четвертого триггера подключен к второму входу первого элемента И.

6

a

e

Фиг.2

Rlt

U,

Авторы

Даты

1991-04-23—Публикация

1989-04-24—Подача