t

ё

(Л

If-L

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1978 |

|

SU750701A1 |

| Одновибратор | 1983 |

|

SU1115214A1 |

| Одновибратор | 1984 |

|

SU1221712A2 |

| Импульсное логическое устройство | 1987 |

|

SU1431063A1 |

| Выходной каскад устройств для дистанционного управления коммутационным аппаратом | 1989 |

|

SU1737626A1 |

| Система вторичного электропитания | 1989 |

|

SU1663606A1 |

| Логический пробник | 1984 |

|

SU1239661A2 |

| Преобразователь постоянного напряжения в постоянное | 1985 |

|

SU1302395A1 |

| Устройство управления напряжением при контактной сварке | 1987 |

|

SU1505718A2 |

| Устройство для задержки импульсов | 1981 |

|

SU1046924A1 |

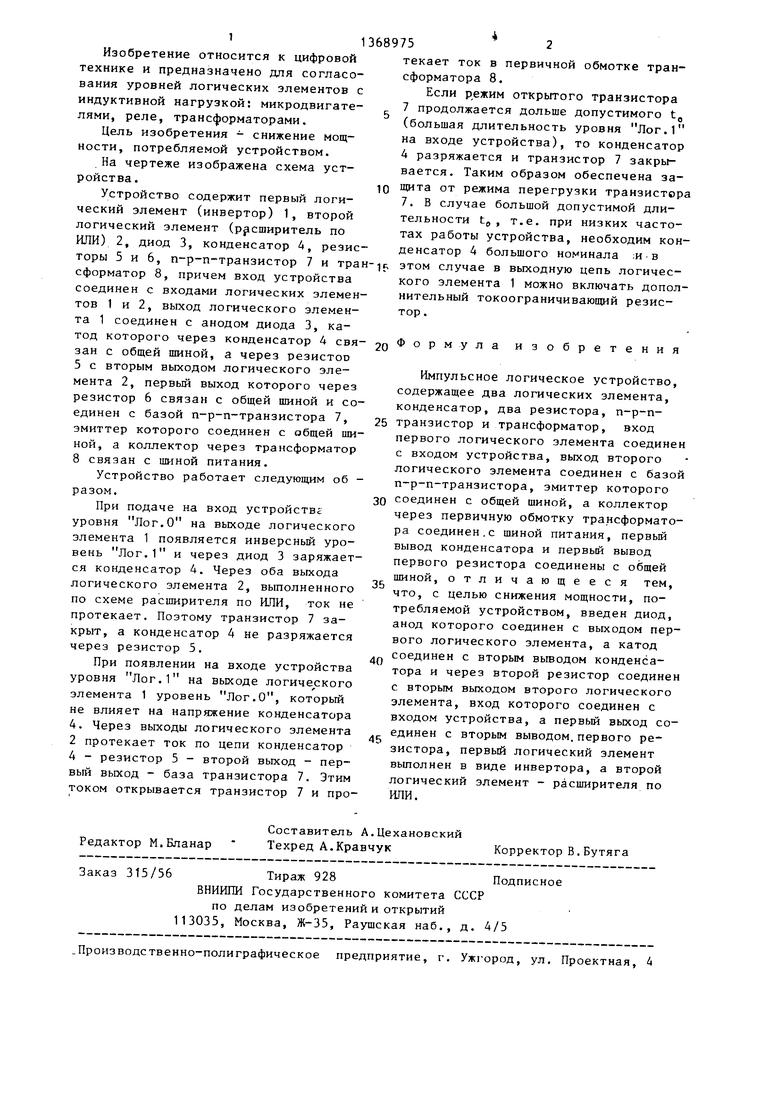

Изобретение относится к цифровой технике и предназначено для согласования уровней логических злементов с индуктивной нагрузкой. Устройство содержит инвертор 1, логический злемент (расширитель по ИЛИ) 2, конденсатор 4, резисторы 5 и 6, п-р-п-транзистор 7 и трансформатор 8. Введение диода 3 снижает мощность, потребляемую устройством. 1 ил.

00

9t 00 СО

J ел

Изобретение относится к цифровой технике и предназначено для согласования уровней логических элементов с индуктивной нагрузкой: микродвигателями, реле, трансформаторами.

Цель изобретения - снижение мощности, потребляемой устройством.

На чертеже изображена схема устройства.

Устройство содержит первый логический элемент (инвертор) 1, второй логический элемент (расширитель по ИЛИ) 2, диод 3, конденсатор 4, резисторы 5 и 6, п-р-п-транзистор 7 и тран-it этом случае в выходную цепь логичес- сформатор 8, причем вход устройства кого элемента 1 можно включать допол10

текает ток в первичной обмотке трансформатора 8.

Если режим открытого транзистора 7 продолжается дольше допустимого t (большая длительность уровня Лог.1 на входе устройства), то конденсатор 4 разряжается и транзистор 7 закрывается. Таким образом обеспечена защита от режима перегрузки транзистора 7. В случае большой допустимой длительности t(, , т.е. при низких частотах работы устройства, необходим конденсатор 4 большого номинала ;и в

соединен с входами логических элементов 1 и 2, выход логического элемента 1 соединен с анодом диода 3, катод которого через конденсатор 4 связан с общей щиной, а через резистоо 5 с вторым выходом логического элемента 2, первый выход которого через резистор 6 связан с общей шиной и соединен с базой п-р-п-транзистора 7, эмиттер которого соединен с общей шиной, а коллектор через трансформатор 8 связан с шиной питания.

Устройство работает следующим об - разом.

При подаче на вход устройства уровня Лог.О на выходе логического элемента 1 появляется инверсньй уровень Лог.1 и через диод 3 заряжается конденсатор 4. Через оба выхода логического элемента 2, выполненного по схеме расширителя по ИЛИ, ток не протекает. Поэтому транзистор 7 закрыт, а конденсатор 4 не разряжается через резистор 5.

При появлении на входе устройства уровня Лог.1 на выходе логиче/;кого элемента 1 уровень Лог.О, который не влияет на напряжение конденсатора 4. Через выходы логического элемента 2 протекает ток по цепи конденсатор 4 - резистор 5 - второй выход - первый выход - база транзистора 7, Этим током открывается транзистор 7 и проit этом случае в выходную цепь логичес- кого элемента 1 можно включать допол0

текает ток в первичной обмотке трансформатора 8.

Если режим открытого транзистора 7 продолжается дольше допустимого t (большая длительность уровня Лог.1 на входе устройства), то конденсатор 4 разряжается и транзистор 7 закрывается. Таким образом обеспечена защита от режима перегрузки транзистора 7. В случае большой допустимой длительности t(, , т.е. при низких частотах работы устройства, необходим конденсатор 4 большого номинала ;и в

20

нительный токоограничивающий резистор .

Формула изобретения

Импульсное логическое устройство, содержащее два логических элемента, конденсатор, два резистора, п-р-п5 транзистор и трансформатор, вход

первого логического элемента соединен с входом устройства, выход второго логического элемента соединен с базой п-р-п-транзистора, эмиттер которого

0 соединен с общей шиной, а коллектор через первичную обмотку трансформатора соединен.с шиной питания, первый вывод конденсатора и первый вывод первого резистора соединены с общей шиной, отличающееся тем, что, с целью снижения мощности, потребляемой устройством, введен диод, анод которого соединен с выходом первого логического элемента, а катод соединен с вторым вьгоодом конденсатора и через второй резистор соединен с вторым выходом второго логического элемента, вход которого соединен с входом устройства, а первьш выход соединен с вторым выводом.первого резистора, первый логический элемент вылолнен в виде инвертора, а второй логический элемент - расширителя по ИЛИ.

5

0

5

Авторы

Даты

1988-01-23—Публикация

1986-07-25—Подача