00

«Kj

о ;о

Фи./

диаграммы. На выходе блока памяти 5 формируются сигналы, соотв. уровням пятиуровневого сигнала +1, -1, 42, -2. При этом если в ВЦС был переход от уровня -I-1 к уровню О или от уровня О к уровню -1, то формируется сигнал -1. Если был переход от уровня +1 к уровню -1

1370790

то формируется сигнал -2. Аналогично формируются сигналы при положит, перепадах, в ВЦС. Сумматор 6, выполненный в виде сумматора по модулю N, элементы ИЛИ 7 и блоки задержки 8 восстанавливают исходный цифровой сигнал троичного кода. Введены блоки 1, 7, 8. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации регенератора (2 @ +1)-уровневого цифрового биполярного сигнала | 1982 |

|

SU1104676A1 |

| Устройство тактовой синхронизации регенератора ( @ +1)-уровневого цифрового биполярного сигнала | 1982 |

|

SU1099401A1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО С НЕПРЕРЫВНОЙ АВТОМАТИЧЕСКОЙ РЕГУЛИРОВКОЙ ВОСПРИИМЧИВОСТИ | 2014 |

|

RU2562796C1 |

| Преобразователь двоичного сигнала в балансный пятиуровневый сигнал | 1977 |

|

SU651491A1 |

| Преобразователь двоичного сигнала в балансный пятиуровневый сигнал | 1981 |

|

SU987832A1 |

| Устройство для определения прочности адгезионного соединения | 1988 |

|

SU1601570A1 |

| Регенератор цифрового сигнала | 1986 |

|

SU1363505A1 |

| Устройство тактовой синхронизации регенератора (2 @ +1)-уровневого цифрового биполярного сигнала | 1984 |

|

SU1167749A1 |

| Устройство для многоканальной магнитной записи и воспроизведения сигналов с коррекцией временных искажений | 1990 |

|

SU1777178A1 |

| Пороговое устройство для сигналов систем управления воздушным движением | 2016 |

|

RU2646690C1 |

Изобретение относится к электросвязи и может использоваться в многоканальных системах связи с временным разделением каналов. Цель изобретения - повышение помехоустойчивости путем уменьшения влияния низкочастотных помех канала связи и уменьшения размножения ошибок при использовании небалансных кодов. Регенератор содержит полосовой фильтр 1, амплитудный компаратор (АК) 2 макс, уровня входного сигнала, АК 3 миним. уровня входного сигнала, АК 4 промежуточных уровней входного сигнала, блок памяти 5, сумматор 6, элементы ИЛИ 7, блоки задержки 8 и блок так товой синхронизации 9. Полосовой фильтр 1 из входного цифрового сигнала (ВЦС) (N 3) формирует пятиуровневый цифровой сигнал без низкочастотных искажений. АК 2-4 имеют пороги срабатывания, соотв. серединам окон глазковой i (Л

1

Изобретение относится к электросвязи и может быть ис.пользовано в многоканальных системах связи с временным разделением каналов.

Целью изобретения является повьше- ние помехоустойчивости путем уменьшения влияния низкочастотных помех канала связи и уменьшения размножения ошибок при использовании небалансных кодов.

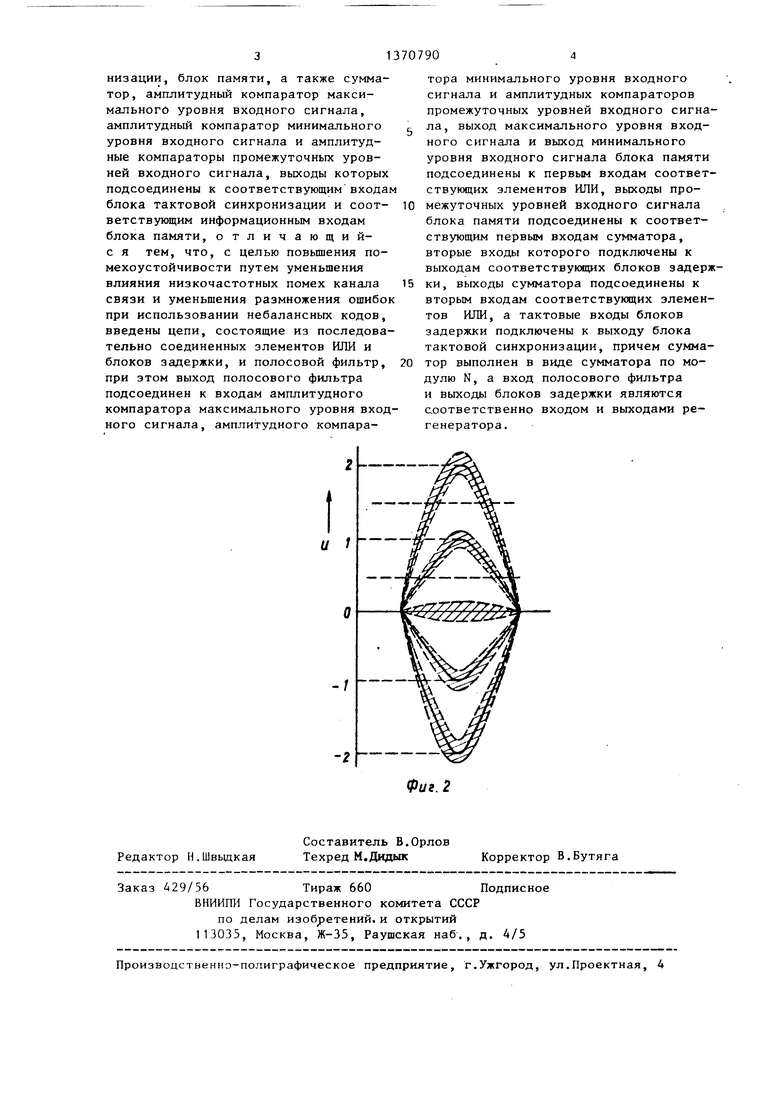

На фиг. 1. представлена электрическая схема регенератора N-уровневого цифрового сигйала; на фиг. 2 - глаз- ковая диаграмма цифрового сигнала без низкочастотных искажений при N 3 (где N - количество уровней входного цифрового сигнала).

Регенератор N-уровневого цифрового сигнала содержит полосовой фильтр 1, амплитудный компаратор 2 максимального уровня входного сигнала, амплитудный компаратор 3 минимального уровня входного сигнала, амплитудные компараторы 4 промежуточных уровней входного сигнала, блок 5 памяти, сумматор 6, элементы ИЛИ 7, блоки 8 задержки и блок 9 тактовой синхронизации.

Регенератор N-уровневого цифрового сигнала работает следующим образом (для случая N 3).

При поступлении входного цифрового сигнала, имеющего низкочастотные искажения, на выходе полосового фильтра 1 (фиг. 1) образуется пятиуровневый цифровой сигнал без низкочастотных искажений (фиг. 2), который следует йа входы амплитудных компараторов 2-4. Амплитудные компараторы 2-4 имеют пороги срабатывания, соот- ветствующие серединам окон глазко- вой диаграммы (фиг. 2), в результате чего на блоке 5 памяти появляются выходные сигналы, соответствующие уровням пятиуровневого сигнала +1, -1, +2 и -2. При этом выделение переходов напряжения вход- ного цифрового сигнала осуществляется следукнцим образом. Если во входном цифровом сигнале был переход от уровня +1 к уровню О или от уровня О к уровню -1, то с блока памяти 5 поступает сигнал -1. Если был переход от уровня н-1 к уровню -1, то с блока памяти 5 следует сигнал -2. Аналогично осуществлйется выделение переходов напряжения входного цифрового сигнала при его положительных перепадах. При этом появляются сигналы +1 и +2.

Сумматор 6, выполненный в виде сумматора по модулю N (в рассматриваемом случае N 5), элементы ИЛИ 7 и блоки 8 задержки восстанавливают исходный цифровой сигнал (троичного

5 кода). При этом, если в пятиуровневом сигнале появляется уровень +2, то это соответствует лишь переходу во входном цифровом сигнале от уровня -1 к уровню +1, т.е. уровень

0

30

-t-2 пятиуровневого сигнала соответствует уровню +1 входного цифрового сигнала, а уровень -2 пятиуровневого сигнала соответствует уровню -1 входного цифрового сигнала. Изменение выходного сигнала при поступ- 35 лении уровней +1 или -1 обеспечивает сумматор 6.

Формула изобретения

0 Регенератор N-уровневого цифрового сигнала, содержащий последовательно соединенные блок тактовой синхро

низации, блок памяти, а также сумматор, амплитудный компаратор максимального уровня входного сигнала, амплитудный компаратор минимального уровня входного сигнала и амплитудные компараторы промежуточных уровней входного сигнала, выходы которых подсоединены к соответствующим входа блока тактовой синхронизации и соответствующим информационным входам блока памяти, отличающий- с я тем, что, с целью повьщ1ения помехоустойчивости путем уменьшения влияния низкочастотных помех канала связи и уменьщения размножения ошибо при использовании небалансных кодов, введены цепи, состоящие из последовательно соединенных элементов ИЛИ и блоков задержки, и полосовой фильтр, при этом выход полосового фильтра подсоединен к входам амплитудного компаратора максимального уровня входного сигнала, амплитудного компара

и /

-2

тора минимального уровня входного сигнала и амплитудных компараторов промежуточных уровней входного сигнала, выход максимального уровня входного сигнала и выход минимального уровня входного сигнала блока памяти подсоединены к первым входам соответствующих элементов ИЛИ, выходы промежуточных уровней входного сигнала блока памяти подсоединены к соответствующим первым входам сумматора, вторые входы которого подключены к выходам соответствуюпщх блоков задержки, выходы сумматора подсоединены к вторым входам соответствующих элементов ИЛИ, а тактовые входы блоков задержки подключены к выходу блока тактовой синхронизации, причем сумматор выполнен в виде сумматора по модулю N, а вход полосового фильтра и выходы блоков задержки являются соответственно входом и выходами регенератора.

| Многоуровневый регенератор биополярных сигналов | 1976 |

|

SU640448A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Сигнализация о понижении уровня воды в паровых котлах | 1948 |

|

SU73400A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-01-30—Публикация

1985-07-26—Подача