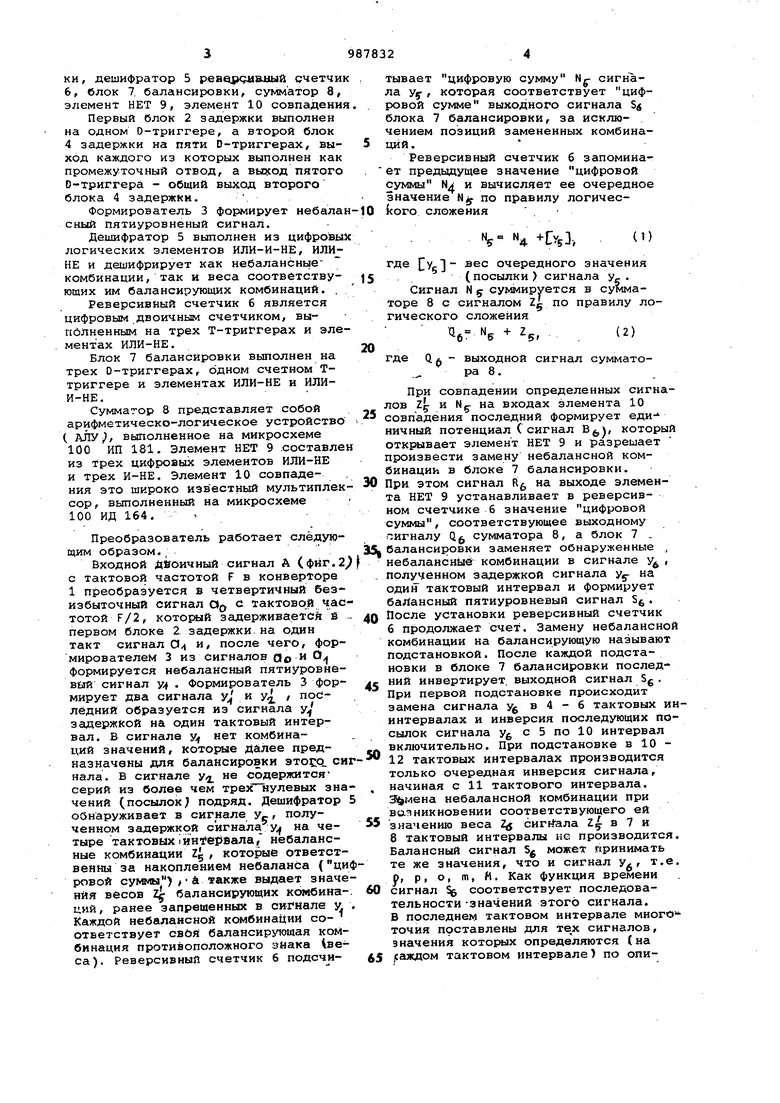

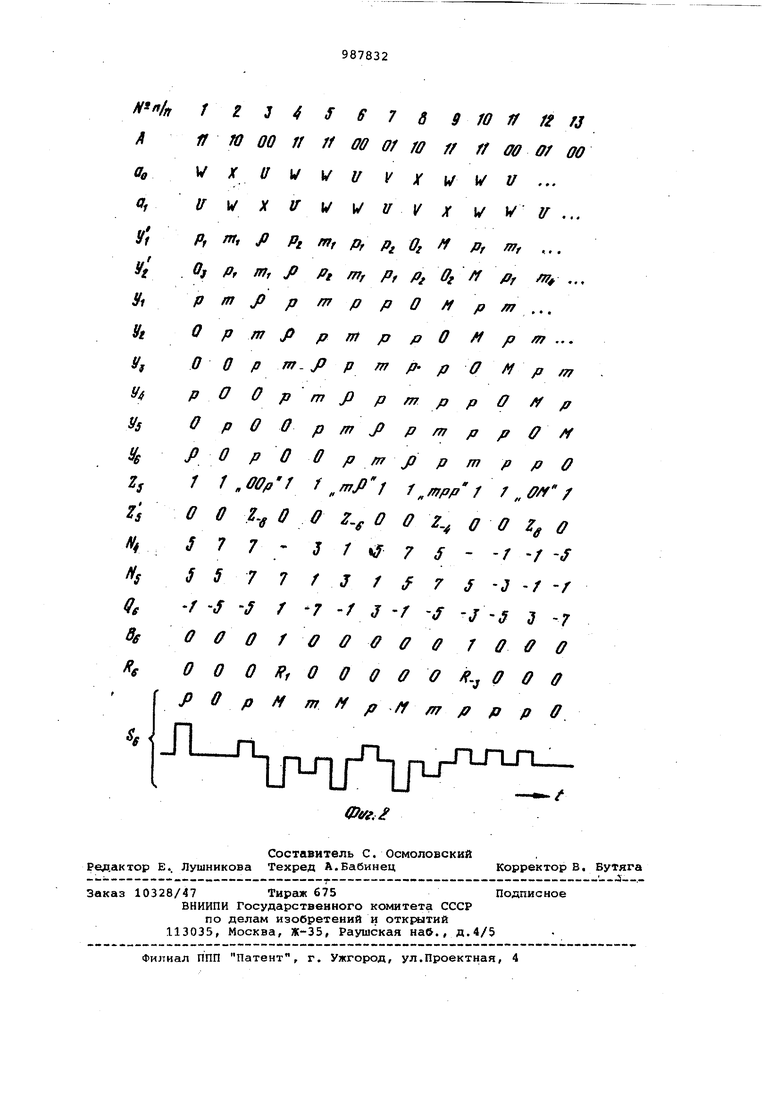

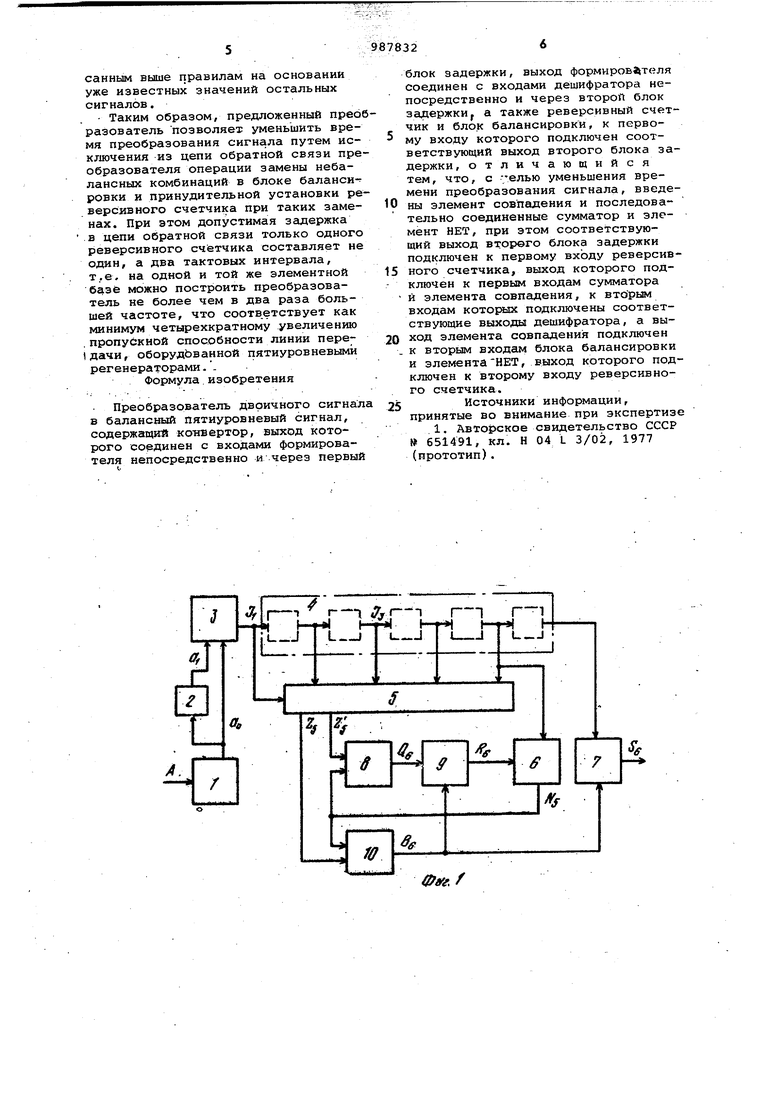

Изобретение относится к технике связи и предназначено для кодопреобразования в цифровых системах передачи данных, оборудованных регенера торами пятиуровневого сигнала. Известен преобразователь двоичного сигнала в балансный пятиуровневый сигнал, содержпщийконвертор, выход которого соединен с входами формирователя непосредственно и через первый блок задержки, выход формировате ля соединен с входами дешифратора непосредственно и через второй блок задержки, а также реверсивный счетчик и блок балансировки, к первому входу кбторого подключен соответств чощий выход второго блока задержки fij. Однако преобразователь имеет большое время преобразования сигнала изза необходимости за время одного такта последовательно выполнять замену небалансной комбинации в блоке балансировки и вычислять- очередное значение цифровой суммы в реверсивном счетчике. -Цель изобретения - уменьшение времени преобразования сигнала. . Для достижения цели в преобразователь двоичного сигнала в балансный пятиуровневый сигнал, содердащий конвертор, выход которого соединен с входами формирователя непосредственно и через первый блок задержки, выход формирователя соединен с входами дешифратора непосрественио и через второй блок задержки, а также реверсивный счетчик и блок балансировки, к первому входу которого подключен соответствующий выход второго блока задержки, введены элемент совпадения и последовательно соединенные сумматор и элемент НЕТ, при этом соответствующий выход второго блока задержки подключен к первому входу рев рсивного счетчика, выход которого подключен к первым входам сумматора и элемента совпадения, к вторым входам которых подключены соответствующие выхода дешифратора, а выход элемента совпадения подключен к входам блока балансировки и элемента НЕТ, выход которого подключен к второму входу реверсивного счетчика. На фиг,- 1 представлена структурная электрическая схема преобразователя; на фиг. 2 - временные диаграммы поясняющие его работу. Преобразователь содержит конвертор i, первый блок 2 задержки, формирователь 3, второй блок 4 задержки, дешифратор 5 реворрйвный счетчи 6, блок 7. балансировки, сумматор 8, элемент НЕТ 9, элемент 10 совпадени Первый блок 2 задержки выполнен на одном О-триггере, а второй блок 4 задержки на О-триггерах, выход каждого из которых выполнен как промежуточный отвод, а выход пятого 0-триггера - общий выход второго блока 4 задержки. . Формирователь 3 формирует небала сный пятиуровненый сигнал. Дешифратор 5 выполнен из цифровы логических элементов ИЛИ-И-НЕ, ИЛИНЕ и дешифрирует как небалансные комбинации, так и веса соответс.твугощих им балансирующих комбинаций. Реверсивный счетчик 6 является цифровым двоичным счетчиком, выполненным на трех Т-триГгерах и эле ментах ИЛИ-НЕ. Блок 7 балансировки выполнен на трех D-триггерах, одном счетном Ттриггере и элементах ИЛИ-НЕ и ИЛИИ-НЕ. Сумматор 8 представляет собой арифметическо-логическое устройство Ч АЛУ|, выполненное на микросхеме 100 ИП 181. Элемент НЕТ 9 .составле из трех цифровых элементов ИЛИ-НЕ и трех И-НЕ. Элемент 10 совпадения это широко известный мультиплек сор, выполненный на микросхеме 100 ИД 164. Преобразователь работает следующим образом.; Входной двоичный сигнал А (фиг.2 с тактовой частотой F в конверторе 1 преобразуется в четвертичный беэизбыточный сигнал а с тактовой час тотой F/2, котоЕялй задерживается S первом блоке 2. задержки, на один такт сигнал О и, после чего, формирователем 3 из сигналов (Зо и О формируется небалансный пятиуровневый сигнал у . Формирователь 3 формирует два сигнала yj У последний образуется из сигнала задержкой на один тактовый интервал. В сигнале у, нет комбинаций значений, которые далее предназначены для балансировки этосо. си нала. В сигнале у не содержится серий из более чем тре5П1улевых зна чений (посылок7 подряд. Дешифратор обнаруживает в сигнале у, полученном задержкой сигнала у на четыре тактовых Iинтервала небалансные комбинации Zg, которые ответственны за накоплением небаланса (ци ровой суммы) & также выдает значе ния весов 2 балансирующих комбинаций, ранее запрещенных в сигнале v Каждой небалансной комбинации соответствует свЬя балансирующая комбинация противоположного зйака Vaeса). Реверсивный счетчик б подсчитывает цифровую сумму Ng- уу, которая соответствует цифровой сумме выходного сигнала S блока 7 балансировки, за исключением позиций замененных комбинаций. Реверсивный счетчик б запоминает предыдущее значение цифровой суммы N4 и вычисляет ее очередное значение N по правилу логического сложения . - Аг +CV53 где ПУеЗ очередного значения , (посылки) сигнала у . Сигнал N 5 суммируется в сумматоре 8 с сигналом Z по правилу логического сложения N6 + Zg, где Q А - выходной сигнал суммато ра 8. При совпадении определенных сигналов Zg- и Ng- на входах элемента 10 совпадения последний формирует еди- ничный потенциал ( сигнал , который открывает элемент НЕТ 9 и разрешает произвести замену небалансной комбинации в блоке 7 балансировки. При этом сигнал fig, на выходе элемента НЕТ 9 устанавливает в реверсивном счетчике б значение цифровой суммы, соответствующее выходному сигналу Q сумматора 8, а блок 7 . балансировки заменяет обнаруженные , небаланснЫб комбинации в сигнале у , полученном задержкой сигнала на один тактовый интервал и формирует балансный пятиуровневый сигнал S. После установки реверсивный счетчик б продолжает счет. Замену небалансной комбинации на балансирующую называют подстановкой. После каждой подстановки в блоке 7 балансировки последний инвертирует, выходной сигнал S. При первой подстановке происходит замена сигнала у в 4 - б тактовых ининтервалах и инверсия последующих посылок сигнала у с 5 по 10 интервал включительно. При подстановке в 10 12 тактовых интервалах производится только очередная инверсия сигнала, начиная с 11 тактового интервала. небалансной комбинации при вазникновении соответствующего ей значению веса Z Z в 7 и 8 тактовый интервалы не производится. Балансный сигнал 5 может .принимать те же значения, что и сигнал у, т.е. р, р. о, т, Н. Как функция времени сигнал % соответствует последовательности-значении этого сигнала. В последнем тактовом интервале много точия прставлены для те,х сигналов, значения которых определяются (на |саждом тактовом интервале по описанным выше правилам на основании уже известных значений остальных сигналов.

Таким образом, предложенный преобразователь позволяет уменьшить время преобразования сигнала путем исключения из цепи обратной связи преобразователя операции замены небалансных комбинаций в блоке балансировки и принудительной установки реверсивного счетчика при таких заменах. При этом допустимая задержка .в цепи обратной связи только одного реверсивного счётчика составляет не один, а два тактовых интервала, т.е. на одной и той же элементной базе можно построить преобразователь не более чем в два раза большей частоте, что соотв етствует как минимум четырехкратному увеличению пропускной способности линии передачи, оборудЬванной пятиуровневыми регенераторами.Формула.изобретения

Преобразователь двоичного сигнала в балансный пятиуровневый сигнал, содержащий конвертор, выход которого соединен с входами формирователя непосредственно и через первый

блок задержки, выход формиров теля Соединен с входами дешифратора непосредственно и через второЯ блок задержкиJ а также реверсивный счетчик и блок балансировки, к первому входу которого подключен соответствующий выход второго блока задержки , отличающийся тем, что, с елью уменьшения времени преобразования сигнала, введе0ны элемент совпадения и последовательно соединенные сумматор и злемент НЕТ, при этом соответствующий выход второго блока задержки подключен к первому входу реверсивного счетчика, выход которого подключен к первым входам сумматора и элемента совпадения, к вторым входам котораах подключены соответствующие выходы дешифратора, а выход элемента совпадения подключен

0 к вторьлм входам блока балансировки и элемента НЕТ, выход которого подключен к второму входу реверсивного счетчика.

Источники информации,

5 принятые во внимание при экспертизе

.1. Авторское свидетельство СССР 651491, кл. Н 04 L 3/02, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного сигнала в балансный пятиуровневый сигнал | 1977 |

|

SU651491A1 |

| Преобразователь двоичного сигнала в балансный пятиуровневый сигнал | 1983 |

|

SU1095397A1 |

| Способ преобразования дискретных сигналов и устройство для его осуществления | 1980 |

|

SU940200A1 |

| Преобразователь двоичного сигнала в пятиуровневый сигнал | 1983 |

|

SU1172044A1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ДВОИЧНОГО СИГНАЛА В ПЯТИУРОВНЕВЫЙ СИГНАЛ | 2010 |

|

RU2428787C1 |

| Фазовый модулятор | 1978 |

|

SU771783A1 |

| Регенератор N-уровневого цифрового сигнала | 1985 |

|

SU1370790A1 |

| Формирователь сигналов с угловой модуляцией | 1985 |

|

SU1241411A1 |

| Преобразователь двоичного сигнала в квазитроичный сигнал | 1983 |

|

SU1109926A1 |

| Устройство для преобразования дискретных сигналов | 1983 |

|

SU1136199A2 |

Авторы

Даты

1983-01-07—Публикация

1981-07-10—Подача