| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь интервала времени в цифровой код | 1989 |

|

SU1746533A1 |

| Преобразователь длительности импульсов в цифровой код | 1989 |

|

SU1698992A2 |

| Измеритель длительности импульсов сложной формы | 1984 |

|

SU1174898A1 |

| Устройство синхронизации кодовой последовательности | 1988 |

|

SU1555893A1 |

| Устройство для измерения характеристики частотной избирательности радиоприемного устройства по побочным каналам приема | 1990 |

|

SU1753609A2 |

| Интегрирующий преобразователь частоты следования импульсов в код | 1981 |

|

SU961140A1 |

| Преобразователь кода | 1989 |

|

SU1612376A1 |

| Устройство с регулируемым коэффициентом усиления | 1987 |

|

SU1580529A1 |

| Интегрирующий преобразователь "аналог-код | 1980 |

|

SU903903A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1995 |

|

RU2076458C1 |

Изобретение относится к информационно-измерительной технике и предназначено для преобразования аналоговых сигналов в цифровой код. Целью изобретения является повышение помехоустойчивости преобразователя. Преобразователь содержит элементы ИЛИ-НЕ 1,2, RS-триггеры 3,4 и счетчик 5.. RS-триггер 3 является старт-триггером, поскольку при его переключении начинается работа счетчика 5, RS-триггер 4 является стоп- триггером, т.к. при его переключении прекращается работа счетчика 5. Преобразователь имеет более широкие функциональные возможности и обладает повьшенной помехоустойчивостью при отсутствии зависимости погрешности преобразования от длительности импульсов эталонной частоты. 2 ил.

fpuz. i

Изобретение относится к информационно-измерительной технлке и предназначено для преобразования аналоговых сигналов в цифровой код.

Цель изобретения - повышение помехоустойчивости преобразователя.

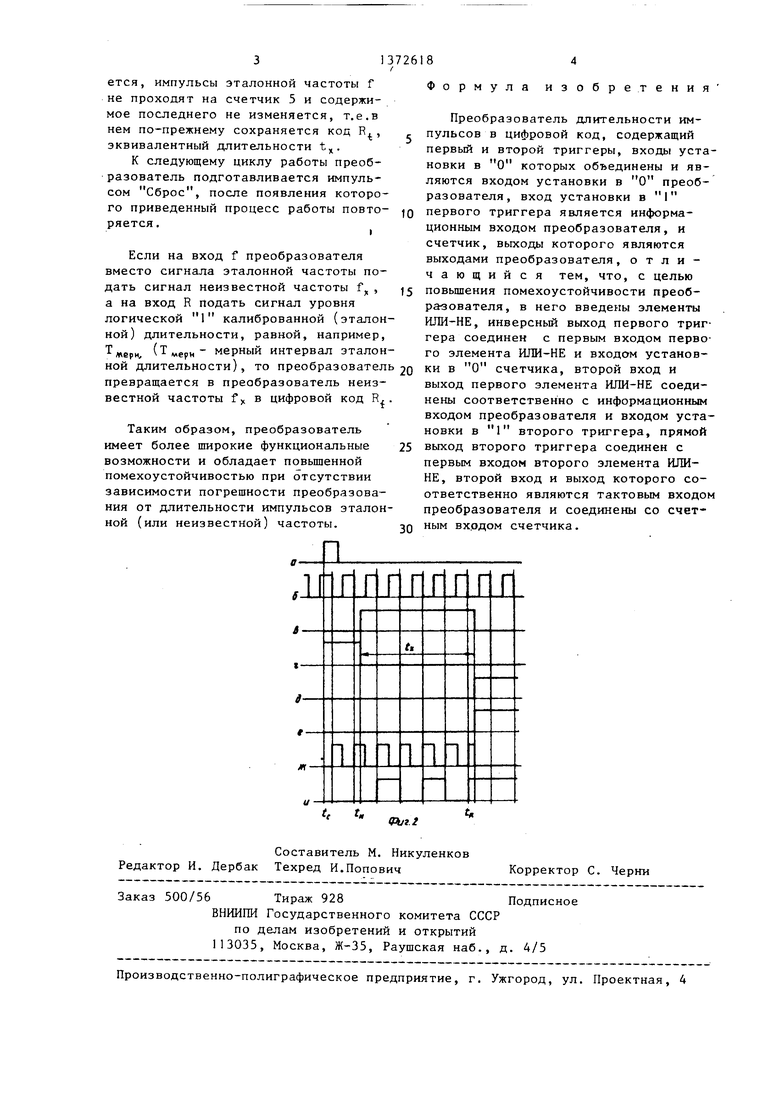

На фиг. 1 показана функциональная схема преобразователя; на фиг. 2 - временные диаграммы, поясняющие его работу.

Преобразователь содержит первый 1 и второй 2 элементы ИЛИ-НЕ, первый 3 и второй 4 RS-триггеры и счетчик 5.

Первый RS-триггер 3 является старт-триггером, поскольку при его переключении начинается работа счетчика 5, второй RS-триггер 4 является стоп-триггером, так как при его переключении прекращается работа счетчика 5.

На фиг. 2 приведены временные диаграммы сигналов: а - сигнал Сброс на входе установки в О преобразователя; б- сигнал зталонной (или неизвестной) частоты на тактовом входе пре- образова теля; в- импульсt (илимер- ный интервалТ,ррц ) , длительность которого преобразовывается в цифровой код на информационном входе преобразователя; г - сигнал на инверсном выходе триггера 3; д - сигнал на выходе элемента ИЛИ-НЕ 1; е - сигнал на прямом выходе триггера 4; ж - сигнал на выходе элемента ИЛИ-НЕ 2; и - сигнал на прямом выходе младшего разряда счетчика 5; причем tn - момент времени начала работы счетчика 5; t - момент времени окончания работы счетчика 5; tc - момент времени появления сигнала Сброс на входе установки в О преобразователя.

Преобразователь работает следующим образом.

Сигналы эталонной частоты постоянно присутствуют на тактовом входе преобразователя (фиг. 2б).

По сигналу Сброс (фиг. 2) триггеры 3 и 4 устанавливаются в нулевое состояние (момент времени, t,фиг.2): на инверсном выходе триггера 3 - уровень логической I, на прямом выходе триггера 4 - уровень логического О (фиг. 2 г и е до момента времени t). Элемент ИЛИ-НЕ 1 закрыт, на его выходе имеется уровень логического О (фиг. 2д). Элемент ИЛИ-НЕ 2 открыт, на его выходе имеются импульсы эталонной частоты, поступающие на

счетный вход С счетчика 5, но счетчик 5 не считает, поскольку он закрыт и удерживается в исходном нулевом состоянии по входу R начальной установки сигналом логической 1 с инверсного выхода триггера 3 (фиг; 2г и ж). Преобразователь переходит в режим ожидания входного импульса,

длительность которого должна быть преобразована в цифровой код.

В момент появления на входе t „ преобразователя входного импульса уровня логической Г (фиг. 2в) по

его фронту триггер 3 переключается в состояние логической 1. На инверсном выходе триггера 3 появляется уровень логического О (фиг. 2г), счетчик 5 открывается по входу R и так

как на его счетном входе С присутствует сигнал эталонной частоты, он начинает считать эти импульсы (фиг.2и). На выходе элемента ИЛИ-НЕ 1 под действием уровня логической 1 входного импульса t по-прежнему имеется уровень логического О, (фиг. 2д), который удерживается в течение длительности (фиг. 2в) входного импульса t .

По окончании входного импульса t по его срезу (момент времени t, фиг. 2) на выходе элемента ИЛИ-НЕ 1 возникает уровень логической 1 (фиг. 2д), под действием которого

триггер 4 по входу S переключается в состояние, при котором на его прямом выходе появляется уровень логической Г который закрьшает ; элемент ИЛИ-НЕ 2, на выходе

которого пропадают импульсы эталонной частоты (момент времени t, фиг. 2). Счетчик 5 прекращает работу, в нем фиксируется код Н преобразуемой длительности входного импульса

t)г в той системе счисления, в которой работает счетчик 5. На этом заканчивается цикл работы преобразователя. Он переходит в режим ожидания сигнала Сброс.

Если теперь по окончании преобразования на входе t преобразователя появляется импульс помехи уровня логической 1, то счетчик 5 не изменяет своего состояния, поскольку появившийся при этом на выходе элемента ИЛИ-НЕ 1 уровень логического О длительностью импульса помехи не сказывается на состоянии триггера 4. Поэтому элемент ИЛИ-НЕ 2 не открывается, импульсы эталонной частоты f не проходят на счетчик 5 и содержимое последнего не изменяется, т.е.в нем по-прежнему сохраняется код R,, эквивалентный длительности t.

К следующему циклу работы преобразователь подготавливается импульсом Сброс, после появления которого приведенный процесс работы повторяется.

Если на вход f преобразователя вместо сигнала эталонной частоты подать сигнал неизвестной частоты f, , а на вход R подать сигнал уровня логической 1 калиброванной (эталонной) длительности, равной, например, мери, ( мерный интервал эталонной длительности), то преобразователь превращается в преобразователь неизвестной частоты fy в цифровой код R,.

Таким образом, преобразователь имеет более широкие функциональные возможности и обладает повышенной помехоустойчивостью при отсутствии зависимости погрешности преобразования от длительности импульсов эталонной (или неизвестной) частоты.

tc

Составитель М. Никуленков Редактор И. Дербак Техред И.Попович

/

, ь on .

84

Формула изобретения

Преобразователь длительности им- 5 пульсов в цифровой код, содержащий первый и второй триггеры, входы установки в О которых объединены и являются входом установки в О преобразователя, вход установки в I

10 первого триггера является информа- ционньм входом преобразователя, н счетчик, выходы которого являются выходами преобразователя, отличающийся тем, что, с целью повьш1ения помехоустойчивости преобразователя, в него введены элементы ИЛИ-НЕ, инверсный выход первого триггера соединен с первым входом первого элемента ИЛИ-НЕ и входом установки в О счетчика, второй вход и выход первого элемента ИЛИ-НЕ соединены соответственно с информационным входом преобразователя и входом установки в 1 второго триггера, прямой

25 выход второго триггера соединен с первым входом второго элемента ИЛИ- НЕ, второй вход и выход которого соответственно являются тактовым входом преобразователя и соединены со счет3Q ным вх,одом счетчика.

iPutt

Корректор С. Черни

| Гитис Э.И., Пискунов Е.А | |||

| Аналого-цифровые преобразователи | |||

| - М.: Энергоиздат, 1981, с | |||

| Топливник с глухим подом | 1918 |

|

SU141A1 |

| Преобразователь интервала времени в цифровой код | 1984 |

|

SU1244794A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-02-07—Публикация

1986-07-23—Подача