Ьл

ел pi

00 CD

СО

Изобретение относится к электросвязи и может быть использовано в системах передачи дискретной информации для синхронизации кодовой последовательности.

Целью изобретения является повышение помехоустойчивости синхронизации.

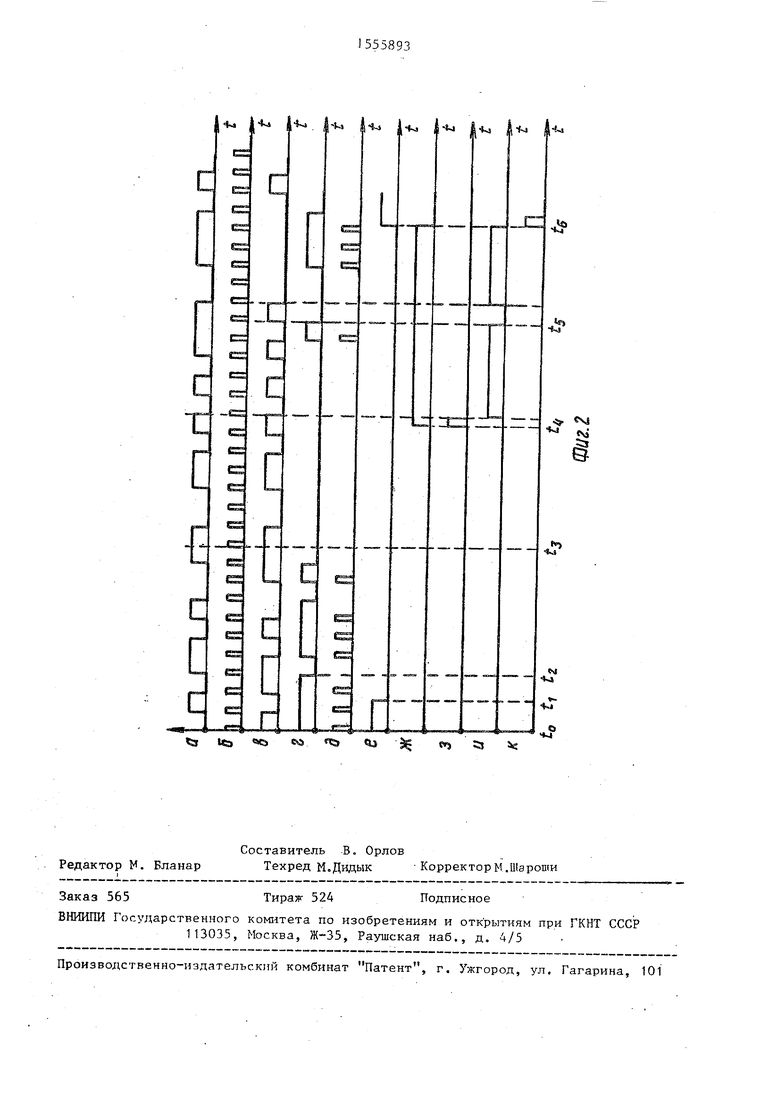

На фиг . 1 представлена структурная электрическая схема устройства синхронизации кодовой последовательности/ на фиг. 2 - временные диаграммы сигналов, поясняющие работу устройства синхронизации кодовой последовательности.

Устройство синхронизации кодовой последовательности содержит регистр сдвига 1 эталонной последовательно-

I1 (фиг.2г, интервал t -t2) , при этом на выход элемента И 7 приходят тактовые импульсы (фиг.2д, интер- вал ), вырабатываемые блоком 10 выделения.

При включении источника питания формирователь 14 формирует импульс уровня логической 1, который через

JQ элемент ИЛИ 8 (фиг.2е, интервал

t0-t,) поступает на Р.-вход RS-триг гера 9, устанавливая его в нулевое состояние (фиг.2ж). При этом первый ключ 2 закрыт, а второй ключ 3 отJ5 крыт сигналом уровня логической 1

с инверсного выхода FS-триггера 9,

С этого момента импульсы с выхода элемента И 7 через последовательно соединенные второй ключ 3, блок 12 сти, первый 2 и второй 3 ключи, счет- 20 заДеРжки поступают на управляющий чик 4 сигналов ошибок, дешифратор 5, вход регистра 1, вызывая исполнитель- блок 6 сравнения, элемент И 7, элемент ИЛИ 8, RS-триггер 9, блок 10 выделения тактовых импульсов, формирователь 1 1 сигнала Временной интер- 25 жается до тех пор, пок-а на выходе вал подсчета сигналов ошибок, блок 12 задержки селектор 13 импульсов

ньй временной сдвиг записанной в нем информации (процесс сдвига информации не показан). Этот процесс продолблока 6 сравнения на относительно про должительное время не установится уровень логического 1:01: (фиг.2г, интервал tj-t.), вызванный синхронностью входной последовательности и последовательности, записанной в регистре 1. Если в канале связи при этом нет ошибок, то тактовые импульсы не проходят на выход элемента И 7 (фиг.2д, интервал tj-t4) . Через интервал, определяемый порогом селектиро- вания, на выходе селектора 13 Формируется импульс уровня логической Г (фиг.2з, момент t), которым RS- триггер 9 переводится в положение, при котором на его прямом выходе устанавливается уровень логической J (Фиг .2ж,момент t4), отпирающий первый ключ 2,второй ключ 3 при этом запирает- 45 ся.УРовнем логического 1Г0 с инверсного выхода RS-триггера 9.

по периоду следования, формирователь 14 сигнала установки исходного состо30

35

40

ния.

Блок 6 сравнения содержит элементы 15 и 16 привязки импульсов и суматор J7 по модулю два.

Устройство синхронизации кодовой оследовательности работает следующим образом.

Перед началом работы в регистр 1 (фиг.1) с входа эталонной последова- телъности устройства синхронизации кодовой последовательности записывается заранее установленная кодовая комбинация (например, псевдослучайная последовательность), либо подается контрольная последовательность.

Входная последовательность информационных символов поступает на информационный вход устройства синхронизации кодовой последовательности (фиг.2а), из которой блоком 10 выде- ления формируются тактовые импульсы (фиг.26).

В блоке 6 сравнения входная последовательность, сравнивается с последовательностью, записанной в регистр 1(фиг.2в). В случае несоответствия символов (несинхронности последовательностей) на выходе блока 6 сравнения устанавливается уровень логиче45

55

I1 (фиг.2г, интервал t -t2) , при этом на выход элемента И 7 приходят тактовые импульсы (фиг.2д, интер- вал ), вырабатываемые блоком 10 выделения.

При включении источника питания формирователь 14 формирует импульс уровня логической 1, который через

элемент ИЛИ 8 (фиг.2е, интервал

t0-t,) поступает на Р.-вход RS-триг- гера 9, устанавливая его в нулевое состояние (фиг.2ж). При этом первый ключ 2 закрыт, а второй ключ 3 открыт сигналом уровня логической 1

С этого момента импульсы с выхода элемента И 7 через последовательно соединенные второй ключ 3, блок 12 заДеРжки поступают на управляющий вход регистра 1, вызывая исполнитель- жается до тех пор, пок-а на выходе

ньй временной сдвиг записанной в нем информации (процесс сдвига информации не показан). Этот процесс продолС этого момента импульсы с выхода элемента И 7 через последовательно соединенные второй ключ 3, блок 12 0 заДеРжки поступают на управляющий вход регистра 1, вызывая исполнитель- 5 жается до тех пор, пок-а на выходе

0

5

0

блока 6 сравнения на относительно продолжительное время не установится уровень логического 1:01: (фиг.2г, интервал tj-t.), вызванный синхронностью входной последовательности и последовательности, записанной в регистре 1. Если в канале связи при этом нет ошибок, то тактовые импульсы не проходят на выход элемента И 7 (фиг.2д, интервал tj-t4) . Через интервал, определяемый порогом селектиро- вания, на выходе селектора 13 Формируется импульс уровня логической Г (фиг.2з, момент t), которым RS- триггер 9 переводится в положение, при котором на его прямом выходе устанавливается уровень логической J (Фиг .2ж,момент t4), отпирающий первый ключ 2,второй ключ 3 при этом запирает- 45 ся.УРовнем логического 1Г0 с инверсного выхода RS-триггера 9.

С этого момента устройство синхронизации кодовой последовательности переходит в режим счета ошибок в канале связи. Этот режим характеризуется тем, что формирователь 11 из тактовых : импульсов формирует сигнал (фиг.2и, интервал ), в течение которого подсчитываются ошибки, возникающие в канале связи, счетчиком 4. Информация о количестве ошибок в течение мерного интервала снимается дешифратором 5 и выводится на выход

единенные блок выделения тактовых импульсов, элемент И, селектор импульсов по периоду следования, RS- триггер, формирователь сигнала Временной интервал подсчета сигналов ошибок, выход которого подсоединен к обнуляющему входу счетчика сигналов ошибок, а также блок задержки и формирователь сигнала установки исходного состояния, выход которого подсое-. динен к первому входу элемента ИЛИ, при этом выход блока выделения тактовых импульсов подсоединен к инфор-

сигналов ошибок и тактовому входу блока сравнения, выход которого подсоединен к второму входу элемента

устройства синхронизации кодовой последовательности .

Если в процессе работы числа ошибок в канале связи возрастает до такой величины, что за время мерного интервала счетчик 4 заполняется полностью, то на его выходе формируется импульс уровня логической 1 (фиг.2к, момент t6), который через элемент ю ИЛИ 8 поступает на R-вход RS-тригге- ра 9, устанавливая его в нулевое состояние (фиг.2ж, момент Ц), вследствие чего принудительно обнуляется

формирователь 11 (фиг.2, момент t6), 15 мационному входу Формирователя сиг- запирается первый ключ 2 и обнуляется нала Временной интервал подсчета счетчик 4. На инверсном выходе RS- триггера 9 в этот момент уровень логической 1, которым устройство синхронизации кодовой последовательности 20 И, выход которого подсоединен к ин- переводится в режим поиска синхронно- формационным входам первого и второго го состояния.ключей, прямой выход RS-триггера подПри установлении синхронного режи- соединен к управляющему входу перво- ма устройство синхронизации кодовой го ключа, выход которого подсоединен

25 к информационному входу счетчика сигналов ошибок, соответствующие выходы которого подсоединены к соответствующим входам дешифратора и второму входу элемента ИЛИ, R-вход и 30 инверсный выход RS-триггера подключены соответственно к выходу элемента ИЛИ и управляющему входу второго ключа, выход которого через блок задержки подсоединен к управляющему второй ключи, дешифратор, счетчик ВХ°ДУ регистра сдвига эталонной по- налов ошибок и элемент ИЛИ, о т л и- следовательности, а второй информа- ч ающе е с я тем, что, с целью ционный вход блока сравнения соеди- повышения помехоустойчивости синхро- нен с входом блока выделения такто- низации, введены последовательно со- вых импульсов.

последовательности вновь начинает считать ошибки, возникающие в канале связи и т.д.

Формула изобретения

Устройство синхронизации кодовой последовательности, содержащее последовательно соединенные регистр сдвига эталонной последовательности и блок сравнения, а также первый и

единенные блок выделения тактовых импульсов, элемент И, селектор импульсов по периоду следования, RS- триггер, формирователь сигнала Временной интервал подсчета сигналов ошибок, выход которого подсоединен к обнуляющему входу счетчика сигналов ошибок, а также блок задержки и формирователь сигнала установки исходного состояния, выход которого подсое-. динен к первому входу элемента ИЛИ, при этом выход блока выделения тактовых импульсов подсоединен к инфор-

сигналов ошибок и тактовому входу блока сравнения, выход которого подсоединен к второму входу элемента

мационному входу Формирователя сиг- нала Временной интервал подсчета И, выход которого подсоединен к ин- формационным входам первого и второго ключей, прямой выход RS-триггера под+J

4vi

4м

«

-tj

м

fvj

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации М-последовательности по задержке | 1986 |

|

SU1398106A1 |

| Устройство цикловой синхронизации | 1984 |

|

SU1197122A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Устройство для передачи и приема дискретной информации | 1988 |

|

SU1529459A1 |

| Устройство для исправления ошибок в волоконно-оптических системах передачи информации | 1990 |

|

SU1809534A1 |

| Устройство для цикловой синхронизации при двоичном сверточном кодировании | 1982 |

|

SU1062881A1 |

| Устройство для преобразования телеграфного кода в видеокод | 1985 |

|

SU1314461A1 |

| Вторичные часы | 1986 |

|

SU1525671A1 |

| СИСТЕМА СИНХРОНИЗАЦИИ ЧАСОВ ПО РАДИОКАНАЛУ | 1985 |

|

SU1840365A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости синхронизации. Устройство содержит регистр 1 сдвига эталонной последовательности, ключи 2 и 3, счетчик 4 сигналов ошибок, дешифратор 5, блок 6 сравнения, эл-т ИЛИ 8. Цель достигается введением эл-та И 7, RS-триггера 9, блока 10 выделения тактовых импульсов, формирователя 11 сигнала "Временной интервал подсчета сигналов ошибок", блока 12 задержки, селектора 13 импульсов по периоду следования и формирователя 14 сигнала установки исходного состояния, с помощью которых обеспечивается работа устройства в двух режимах. Это режим счета ошибок в канале связи и режим поиска синхронного состояния, когда число ошибок в канале связи возрастает до такой величины, что за время мерного интервала счетчик 4 заполняется полностью. 2 ил.

С

с

er

Г

ji«5 ««sco«tsaj f 55iie

M

S в

м

J

| Устройство для синхронизации | 1975 |

|

SU523533A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство синхронизации псевдослучайной последовательности | 1977 |

|

SU698145A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-04-07—Публикация

1988-05-03—Подача