(5) ИНТЕГРИРУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ-КОД

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегрирующий преобразователь аналог-код | 1981 |

|

SU962992A1 |

| Интегратор | 1980 |

|

SU922786A1 |

| Нелинейный преобразователь | 1988 |

|

SU1674172A1 |

| Устройство измерения отклонения сопротивления от заданного значения | 1990 |

|

SU1737360A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1124346A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012131C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

| Аналого-цифровой преобразователь параметров диэлькометрического датчика | 1985 |

|

SU1242801A1 |

Изобретение относится к области преобразования аналоговых сигналов постоянного тока в цифровые коды и может быть использовано в качестве аналого-цифрового преобразователя в системах сбора и обработки данных Известны аналого-цифровые преобразователи, которые для повышения эффективности подавления помехи содержат специальные устройства, осуществляющие подстройку времени преобразования в зависимости от частот и фазы помехи, представляющие собой преобразователь время-импульсного типа, осуществляющий преобразование входного напряжения в частоту импульсов с подстройкой времени преобразования под период и фазу поме и 1 . Однако такая подстройка является м леннодействующей и требует интервала времени в несколько периодов помехи Известен также способ измерения сигналов с наложенными помехами, пр котором измерения производятся в момент прохождения помехи через ноль(2 Однако при этом способе не осуществляется подавления импульсных помех,t Наиболее близким по технической сущности к предложенному является устройство, которое состоит из интегратора с тремя ключами на входе, компаратора, устройства управления и цифро-аналогового преобразователя, выход которого через-один из ключей подсоединен к входу интегратора fЗ. Недостатком известного устройства является его сложность, связанная с наличием цифро-аналогового преобразователя, а также влияние соотношения амплитуд помехи и полезного СИ1- нала на точность устройства. Так, в устройстве первыЛ такт интегрирования равен периоду помехи и при отклонениях периода помехи от. номинального изменяется также дли- тельность первого такта иитегрирования. в результате этого меняется коэффициент передачи устройства и ухудшается его точность .Поэтому для коррекции коэффициента передачи устройства используется цифро-аналоговый преобразователь.

Кроме того, устройство может преобразовывать аналоговые сигналы в код только в том случае, когда уровень полезного сигнала превышает уровень помехи, иначе могут происходить срабатывания компаратора в произвольные моменты времени. Такое соотношение между уровнем сигнала и помехи трудно реализовать на практике во всем диапазоне входного сигнала.

Цель изобретения - повышение точности преобразования и упрощение преобразователя.

Поставленная цель достигается тем что в интегрирующий преобразователь аналог-код, содержащий интегратор, вход которого через первый и второй ключи, соединенные последовательно с первым и вторым масштабными резисторами, подключен соответственно к :;игнальному входу и входу опорного напряжения преобразователя, третий ключ, включенный между входом и выходом интегратора, компаратор, первый вход которого соединен сдвыходом интегратора, а второй вход подключен к входу опорного напряжения, И счетчик, выход которого является выходом преобразователя, введены пять элементов И, RS-триггер, триггер со счетным входом, дополнительный счетчик, генератор импульсов и формировательимпульсов, вход которого является управляющим входом преобразователя, а выход подключен к входу сброса дополнительного счетчика и входу триггера со счетным входом, прямой выход которого соединен с первыми входами первого и второго элементов И, инверсный выход подключен к первым входам третьего, четвертого и пятого элементов И и к единичному входу RS-триггера, выход дополнительного счетчика соединен со вторыми входами первого и второго элементов И, а счетный вход подключен к выходу второго элемента И, третий вход которого и второй вход пятого элемента И соединены с выходом генератора импульсов, а выход пятого элемента И подключен ко входу счетчика, выход компаратора соединен со вторым входом четвертого элемента И,

ВЫХОД которого подключен ко второму входу третьего элемента И и нулевому входу RS-триггера, прямой и инверсный выходы RS-триггера, подключены к управляющим входам третьего ключа, а управляющие входы первого и второго ключей соединены с выходами первого и третьего элементов И соответственно, причем третий вход пятого элемента И подключен к прямому выходу RS-триггера, а третий ключ выполнен на трех ключевых элементах, два из которых соединены последовательно и включены между входом и выходом третьего ключа, третий ключевой элемент включен между общим выводом первого и второго ключевых элементов и шиной нулевого потенциала, причем управляющие входы первого и второго ключевых элементов являются первым управляющим входом третьего ключа, а управляющий вход третьего ключевого элемента является вторым управляющим входом третьего ключа.

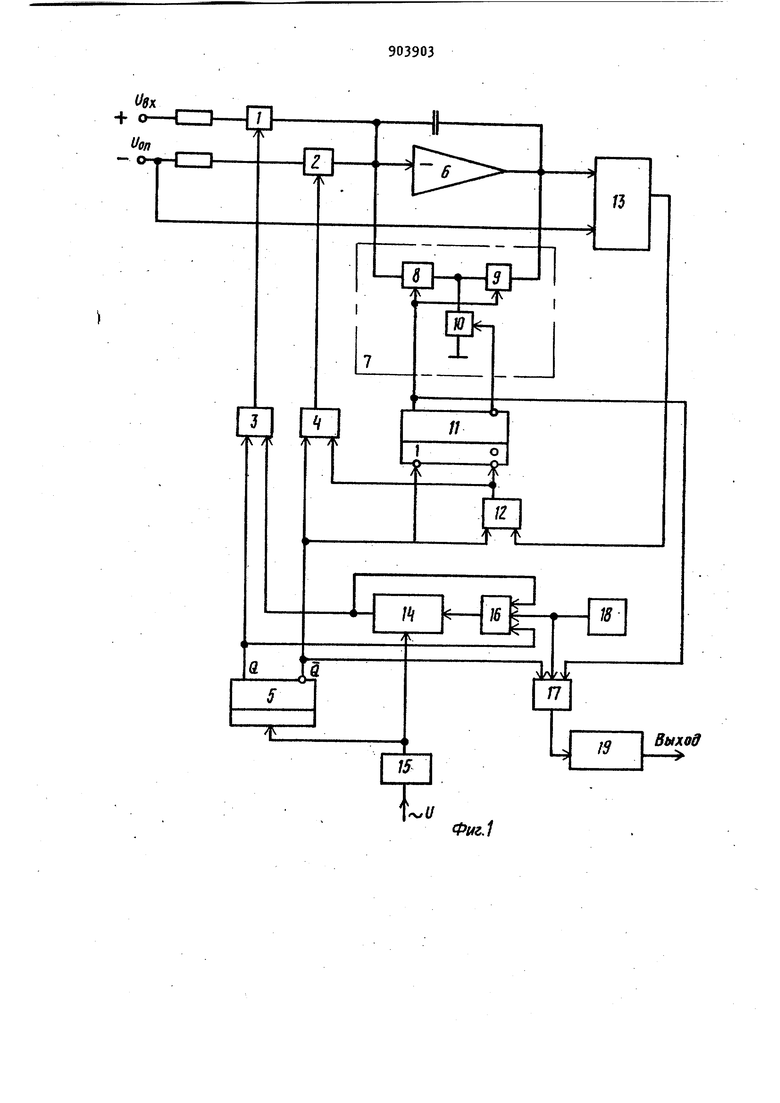

На фиг. 1 представлена функционалная схема преобразователя; на фиг.2временная диаграмма его работы.

Преобразователь содержит ключи 1 и 2, элементы И 3 и 4, триггер 5, интегратор 6, ключ 7 содержащий ключевые элементы 8-10, RS-триггер П, элемент И 12, компаратор 13, счетчик 1А, формирователь 15, элементы И 16 и 17, генератор импульсов и счетчик 19.

Преобразователь работает следующи образом.

На вход формирователя 15 поступает переменное напряжение с частотой, равной частоте помехи (фиг.2а), преобра.зуемое в импульсы (фиг.26). Триггер 5 управляется с выхода формирователя 15 и формирует на своих выходах напряжение прямоугольной формы частотой, равной половине частоты помехи (фиг.2в). Счетчик 1 сбрасывается, в ноль в момент прохождения напряжения на входе формирователя 15 через ноль.

8 момент времени t (фиг. 2г), KOI да на выходе триггера 5 устанавливается единица, начинается первый такт интегрирования, при этом замыкается ключ 1 и начинает интегрироваться входное напряжение в течение временного .нтepвaлaC , Временной интервал T/f формируется с помощью генератора 18 импульсов, элемента И 16 и счетчика Н. Длительность ин тервала 1; выбирается меньшей минимально возможной длительности полупериода помехи. В момент времени t (фиг. 2г) сигналом с выхода счет чика }Ц запираются элементы ИЗ и И16, при этом ключ 1 размыкается и интегратор 6 тереводится в режим хранения. В момент времени 1-5(рис.2 счетчик 14 сбрасывается в ноль, открывая элементы И 3 и И 16. При этом замыкается снова ключ 1 и начинает интегрироваться входное напряжение в течение временного интервала IT, равного по величине tT В момент времени t ключ 1 размыкается и интегратор 6 переводится в режим хранения. Таким образом, на первом такте происходит интегрирование входного напряжения в течение двух временных интервалов f и 1Г , равных по длительности, начал которых отстоит друг от друга на половину периода помехи. При этом исключается влияние колебания частоты помехи на степень ее подавления, .так как на каждый интервал Т и Tg в пределах одного периода приходятся равные по величине и форме, но противоположные по знаку участки кривой напряжения помехи, т.е. к моменту времени t значение помехи на выходе интегратора 6 равно нулю. Второй такт интегрирования начинается в момент времени t g- (фиг.2г) При этом триггер 5 перебрасывается, открывая элементы И k, И 12, И 17 и запирая элемент И 1б. Ключ 2 замыкается и начинает интегрироваться опорное напряжение. Одновременно импульсы с генератора 18 импульсов начинают поступать через элемент И 17 в счетчик 19 (фиг.2д). В момент времени t/ (фиг. 2д) напряжение на выходе интегратора 6 достигает уровня срабатывания компаратора 13. Компаратор 13 срабатываети через элемент И, 12 запирает элемент И k, размыкая ключ 2, перебрасывает RS-триггер 11. Элемент И 17 запирается и в счетчике 19 хранится результат аналогоцифрового преобразов ания. На выходах Q и Q RS-триггера устанавливаются напряжения, обеспечивающие замыкание ключевых элементов 8 и 9 и размыкание ключевого эле мента 10 (,фиг.2ж). Интегратор 6 разрялается через ключевые элементы 8 И 9 ДО выходного напряжения, равного нулю. В режиме интегрирования входного и опорного напряжения (tj t) ключевые элементы 8 и 9 разомкнуты, а ключевой элемент 10 замкнут. Такое соединение ключевых элементов 8-10 позволяет исключить шунтирование интегратора 6 ключом 7 и, тем самым повысить точность аналого-цифрового преобразоёания. Элемент И 12 осуществляет блокировку устройства от прЬизвольных срабатываний компаратора 13 в течение первого такта интегрирования, которые могут происходить при преобразовании сигналов с помехами, превышающими по амплитуде полезный сигнал. Таким образом, предлагаемый преобразователь осуществляет подавление наложенных на сигнал помех за счет разбиения первого такта интегрирования на два равных по длительности участка, меньших полупериода помехи. Преобразователь имеет фиксированный коэффициент передачи, определяемый фиксированным време1нем интегрирования (С -ьТ) входного напряжения, и не зависит от колебаний частоты помехи. Поэтому он обеспечивает точное преобразование аналогового входного напряжения в код, является более простым по сравнению с известным, содержащим цифро-аналоговый преобразог ватель для коррекции изменяющегося коэффициента передачи устройства. Так как в промышленных системах сбора и обработки данных, для которых предназначен предлагаемый преобразователь , основной является помеха промышленной частоты, то в качестве управляющего напряжения на схему следует подавать переменное напряж ние сети. Формула изобретения Интегрирующий преобразователь анаог-код, содержащий интегратор, вход которого через первый и второй ключи, соединенные последовательно с первым, и вторым масштабными резисторами, подключен .соответственно к сигнальному входу и входу опорного напряжения преобразователя, третий ключ, включенный между входом и выодом интегратора, компаратор, первый вход -которого соединен с выходом

интегратора, а второй вход подключен к входу опорного напряжения, и счетчик, выход которого является выходом преобразователя, отличающийс я тем, что, с целью повышения точности преобразования и упрощения преобразователя, в него введены пять элементов И, RS-триггер, триггер со счетным входом, дополнительный счетчик, генератор импульсов и формирователь импульсов, вход которого является управляющим входом преобразователя, а выход подключен к входу сброса дополнительного счетчика и входу триггера со счетным входом, прямой выход которого соединен с первыми входами первого и второго элементов И, инверсный выход подключен к первым входам третьего, четвертого и пятого элементов И и к единичному входу RS-триггера, выход дополнительного счетчика соединен со вторыми входами первого и второго элементов И, а счетный вход подключен к выходу второго элемента И, третий вход которого и второй вход пятого элемента И соединены с выходом генератора импульсов, а выход пятого элемента И подключен ко входу счетчика, выход компаратора соединен со вторым входом четвертого элемента И,о выход которого подключен ко второму входу третьего элемента И и нулевому входу RS-триггера, прямой и инверсный выходы RS-триггера подключены к управляющим входам третьего ключа, а управляющие входы первого и второго ключей соединены с выходами первого и третьего элементов 1 соответственно, причем третий вход пятого элемента И подключен к прямому выходу RS-триггера.

2, Преобразователь по п.1, о т-.

личающийся тем, что третий ключ выполнен на трех ключевых элементах, два из которых соединены последовательно и .включены между входом и выходом третьего ключа, третий

ключевой элемент включен между общим выводом первого и второго ключевых элементов .и шиной нулевого потенциала , причем управляющие входы первого и второго ключевых элементов являются первым управляющим входом третьего ключа, а управляющий вход третьего ключевого элемента является вторым управляющим входом третьего ключа.

Источники информации, принятые во внимание при экспертизе

а

4f

llT

Гг itW

Cj

Ф«з.

Авторы

Даты

1982-02-07—Публикация

1980-05-05—Подача