Фиг.1

Изобретение относится к импульсной технике и может использоваться в системах передачи цифровой информации для преобразования бикмпульсного двухфазного кода линии .в. двоичный код без возврата к нулю

Целью изобретения является повышение помехоустойчивости преобразователя.

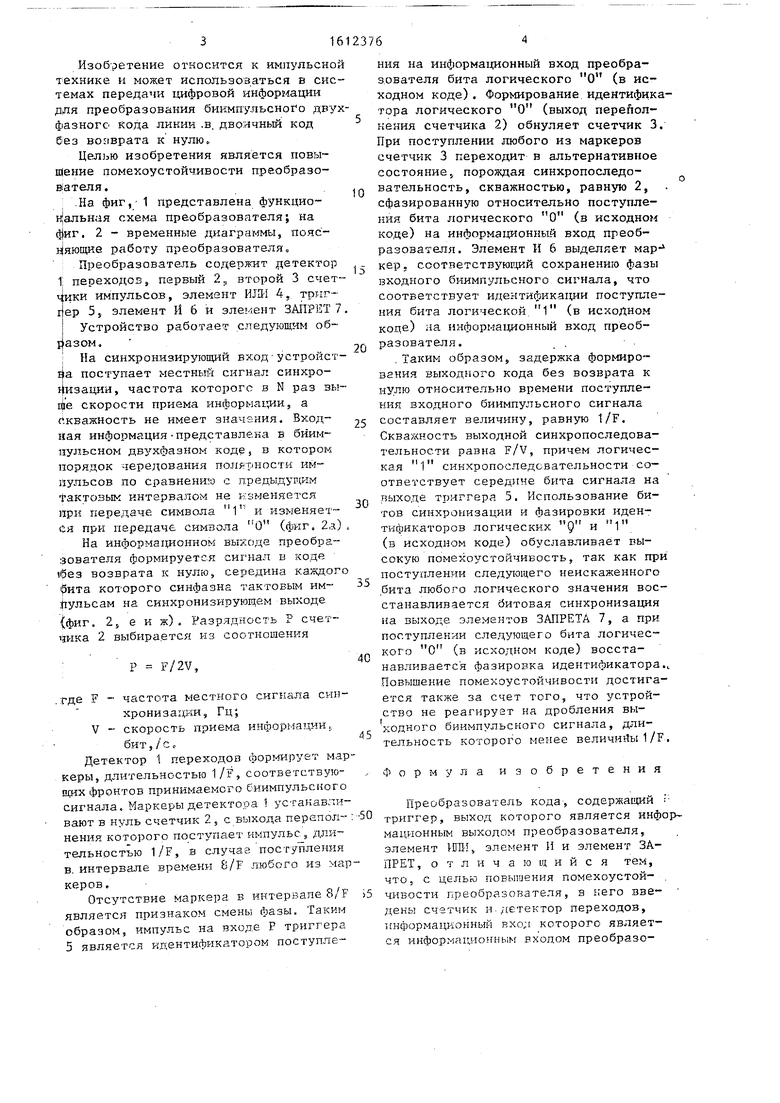

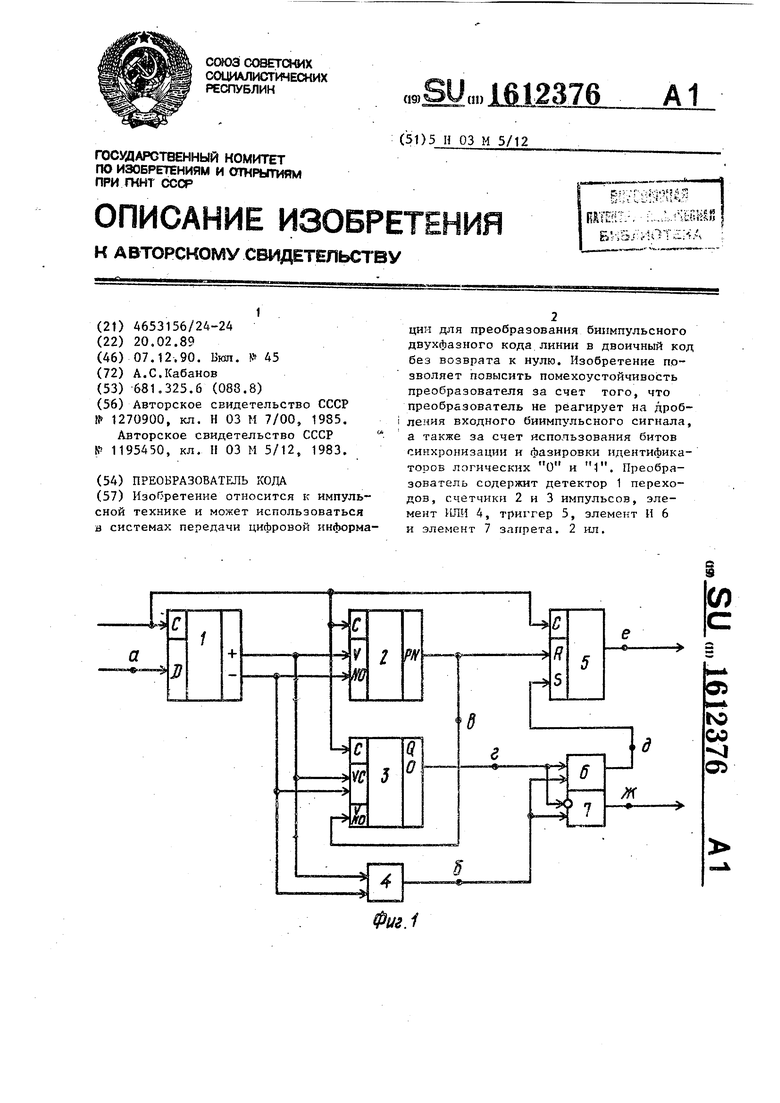

.На фиг,-1 представлена функциональная схема преобразователя; на фиг. 2 - временные диаграммы, пояс - 1 яющие работу преобразователя : Преобразователь содержит детектор 1: переходовS первый 2,, второй 3 счет«ики импульсов, элемент ИЛИ 4, триггер 5j элемент И 6 и элемент ЗАПРЕТ /

Устройство работае :{ следующим об- 1:|азом«

I На синхронизирующий входустройст- а поступает местный сигнал синхро- йизации, частота которого в N раз вы- die. скорости приема информаг ии, а Скважность не имеет значения. Входная информация Представлена в биим- нульсном двухфазном коде, в котором порядок чередования полярности импульсов по сравнени о с предыдущим тактовым интервалом не изменяется При передаче символа 1 и изменяется при передаче символа О (фиг. 2а)

На информационном выходе преобра- :3ователя формируется сигнал в коде (без возврата к нулю, середина каждог |5ита которого синфазна тактовым им- йульсам на синхронизирующем выходе {фиг. 2j е и ж). Разрядность Р счетчика 2 выбирается из соотношения

Р F/2V,

где F - частота местного сигнала синхронизадаи, Гц; V - скорость приема информации,;,

бит,/с с

Детектор 1 переходов фор -4Ирует маркеры, длительностью 1/F, соответствующих фронтов принимаемого биимпульсного сигнала. Маркеры детектора 1 устанавливают в нуль счетчик 2 , с выхода перепол- : нения которого поступает импульс, длительностью 1/F, в случае. поступления в. интервале времени B/F любого из маркеров.

Отсутствие маркера в интервале Ь/1 является признаком смены фазы. Таким образом, импульс на входе Р триггера 5 является идентификатором поступле

0

5

0

5

0

45

ния на информационный вход преобразователя бита логического О (в исходном коде). Формирование идентификатора логического О (выход переполнения счетчика 2) обнуляет счетчик 3. При поступлении любого из маркеров счетчик 3 переходит в альтернативное состояние, порождая синхропоследо- вательность, скважностью, равную 2, сфазированную относительно поступления бита логического О (в исходном коде) на инфopмaциoннЬLч вход преобразователя . Элемент И 6 выделяет мар- кер, соответствующий сохранению фазы входного б -гимпульсного сигнала, что соответствует идентифика1щи поступления бита логической.1 (в исходном коде) на информационный вход преобразователя.

Таким образом, задержка формиро™ вания выходного кода без возврата к нулю относительно времени поступления входного бинмпульсного сигнала составляет величину, равную 1/F, Сква хность выходной синхропоследова- тельности равна F/V, причем логическая 1 сикхропоследовательности соответствует середине бита сигнала на выходе триггера 5, Использование битов синхронизации и фазировки идентификаторов логических Q и 1 (в исходном коде) обуславливает высокую помехоустойчивость, так как при поступлении следующего неискаженного бита любого логического значения восстанавливается битовая синхронизация на выходе элементов ЗАПРЕТА 7, а при поступлении следующего бита логического О (в исходном коде) восстанавливается фазировка идентификатора.. Повышение помехоустойчивости достигается также за счет того, что устройство не реагирует на дробления вы- ходного биимпульсного сигнала, длительность которого менее величины 1/F.

Формула изобретения

Преобразователь кода, содержащий триггер, выход которого является информационным выходом преобразователя, элемент ИШ1, элемент И и элемент ЗАПРЕТ, отличающийся тем, что. с целью повышения помехоустой- . чивости преобразователя, в него введены счетчик и.детектор переходов, информационный вхо;г которого является информационныьг входом преобразователя, синхронизирующий вход детектора переходов объединен с синхрона- зируюпщми входами первого, второго счетчиков, триггера и является синхронизирующим входом преобразоват я первый выход детектора переходов соединен с первыми управляющими входами первого, второго счетчиков и первГ входом элемента 1ШИ, выход которого соединен с прямым входом элемента ЗАПРЕТ и первым входом элемента И, выход которого соединен с входом установки

16

д

1612376

в 1 триггера, второй выход детектора переходов соединен с вторыми управляющими входами первого, второго счетчиков и вторьш входом элемента лт, выход первого счетчика соединен с входом установки О триггера и третьим управляющим входом второго счетчика, выход которого соединен с вторым входом элемента И и инверсным входом элемента ЗАПРЕТ, выход которого является синхронизирующим выходом преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| СПОСОБ УСТОЙЧИВОЙ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ ПРИ ПРИМЕНЕНИИ ЖЕСТКИХ И МЯГКИХ РЕШЕНИЙ И МОДУЛЯЦИИ ПО ТИПУ СТЫКА С1-ФЛ | 2023 |

|

RU2812964C1 |

| Устройство для приема информации | 1988 |

|

SU1672571A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА, ПРЕОБРАЗОВАНИЯ И СИНХРОНИЗАЦИИ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2004 |

|

RU2279182C1 |

| ДЕКОДЕР ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА КОДА RZ | 2005 |

|

RU2291560C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ С ЖЕСТКИМИ И МЯГКИМИ РЕШЕНИЯМИ ДЛЯ ДВУХСТУПЕНЧАТОГО КАСКАДНОГО КОДА И МОДУЛЯЦИИ ПО ТИПУ СТЫКА С1-ФЛ | 2024 |

|

RU2834891C1 |

| Преобразователь биимпульсного двоичного сигнала в бинарный сигнал | 1983 |

|

SU1200426A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И СИНХРОНИЗАЦИИ КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2344543C1 |

| Преобразователь длительности импульсов в цифровой код | 1986 |

|

SU1372618A1 |

| Преобразователь кода во временной интервал | 1990 |

|

SU1753512A1 |

Изобретение относится к импульсной технике и может использоваться в системах передачи цифровой информации для преобразования биимпульсного двухфазного кода линии двоичный код без возврата к нулю. Изобретение позволяет повысить помехоустойчивость преобразователя за счет того, что преобразователь не реагирует на дробления входного биимпульсного сигнала, а также за счет использования битов синхронизации и фазировки идентификаторов логических "0" и "1". Преобразователь содержит детектор 1 переходов, счетчики 2 и 3 импульсов, элемент 4 ИЛИ, триггер 5, элемент И 6 и элемент 7 запрета. 2 ил.

-LJULJULJLJCLmjLjtill

e- LJ fLJL n JL

г

f-П:fLJL

Jl

Л

ri

-IL-JLJLJLJLJLJLJ Jl.

Физ. 2

Jl

Л

| Устройство для преобразования последовательного кода в код | 1985 |

|

SU1270900A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь кода | 1983 |

|

SU1195450A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-12-07—Публикация

1989-02-20—Подача