ffl

8м

4

,л,

Фиг f

Изобретение относится к технике электросвязи и может использоваться в аппаратуре передачи данных для приема дискретных сигналов.

Цель изобретения - повышение помехоустойчивости за счет компенсации амплитудных и фазовых флуктуации сигнала,

На фиг.1 представлена структурная электрическая схема предложенного устройства;на фиг.2 - вариант выполнения блока компенсации фазовых не- стабильностей| на фиг.З - блок компенсации амплитудных нестабильно- стей; на фиг,4 - решающий блок; на фиг.5 блок подстройки амплитуды; на фиг,6 - блок вычислений орибки фазы; на фиг.7 - стационарный фильтр на фиг,8 - адаптивный фильтр;, на фиг,9 блок подстройки коэффициентов ,

Устройство для приема дискретных сигналов содержит входной согласующий блок 1, фазовращатель 2,аналого-цифровой преобразователь 3, полосовой корректор 4, блок 5 тактовой синхронизации, блок 6 компенсации фазовых нестабильностей, блок 7 компенсации амплитудных нестабильностей решающий блок 8, блок 9 подстройки амплитуды, блок 10 вычисления ошибки фазы, стационарный фильтр 11, адаптивный фильтр 12, блок 13 подстройки коэффициентов, сумматор 14, нелинейный преобразователь 15 и декодер 16о

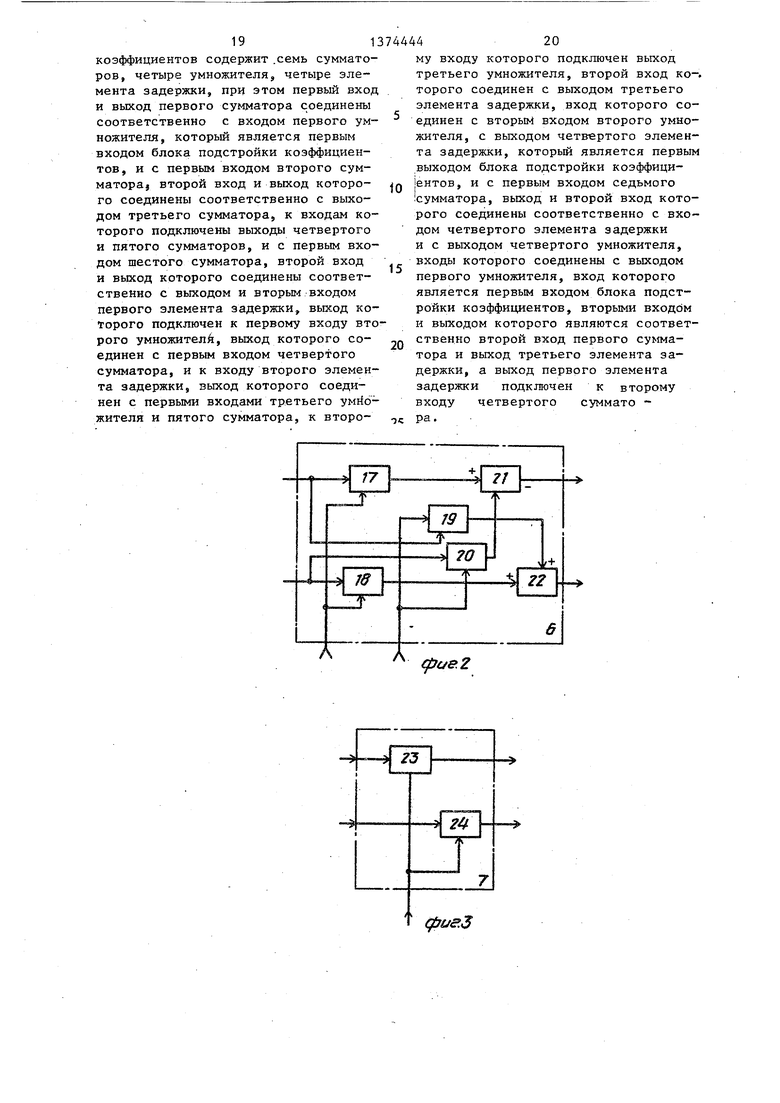

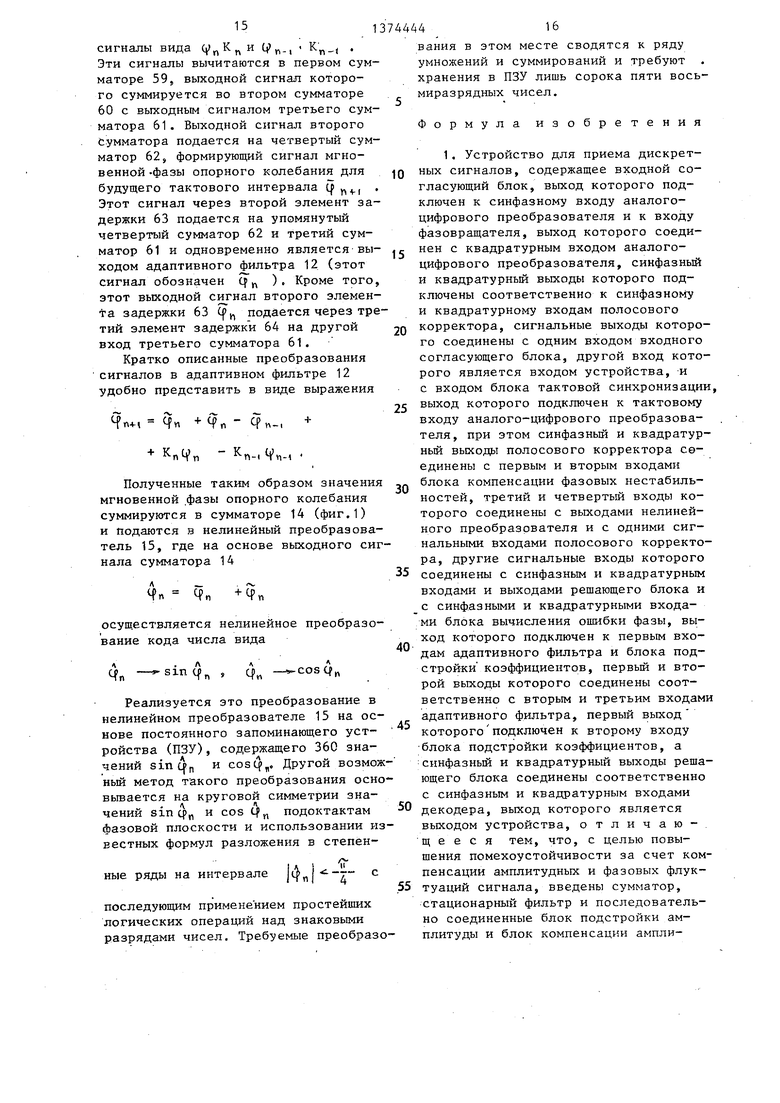

Блок б компенсации фазовых кеста- бильностей содержит (фиг,2) первый, второй, третий и четвертый умножители 17--7.0, ры 2t и 22,

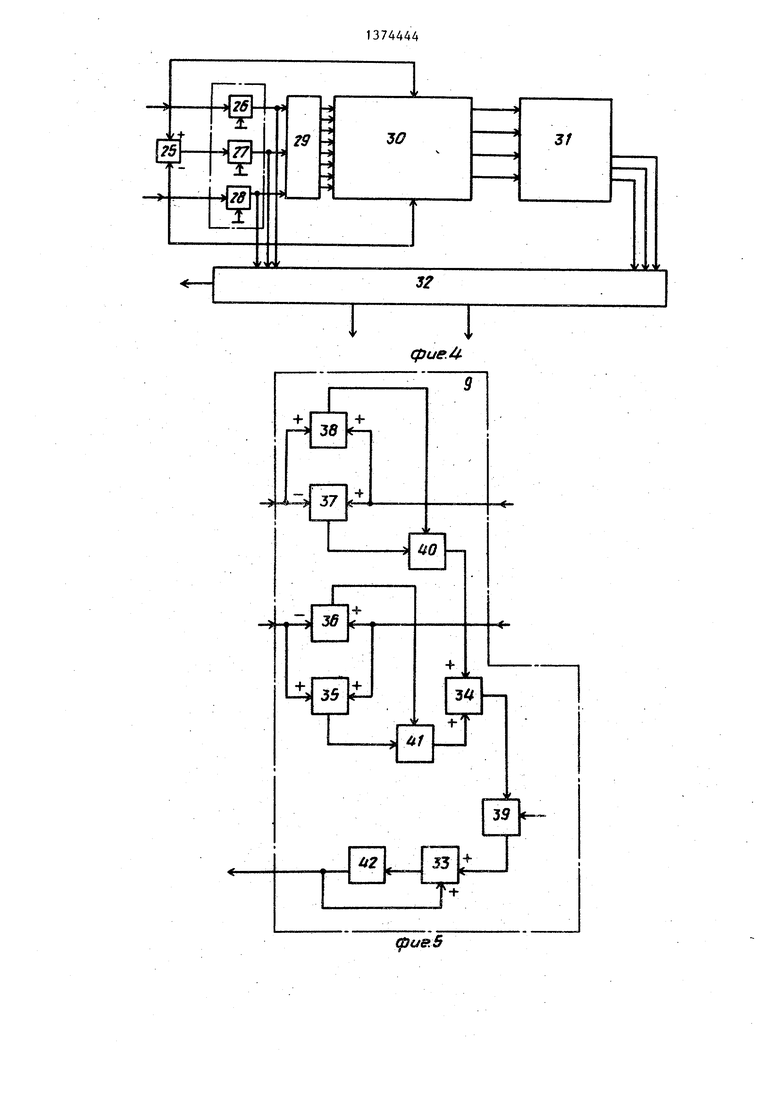

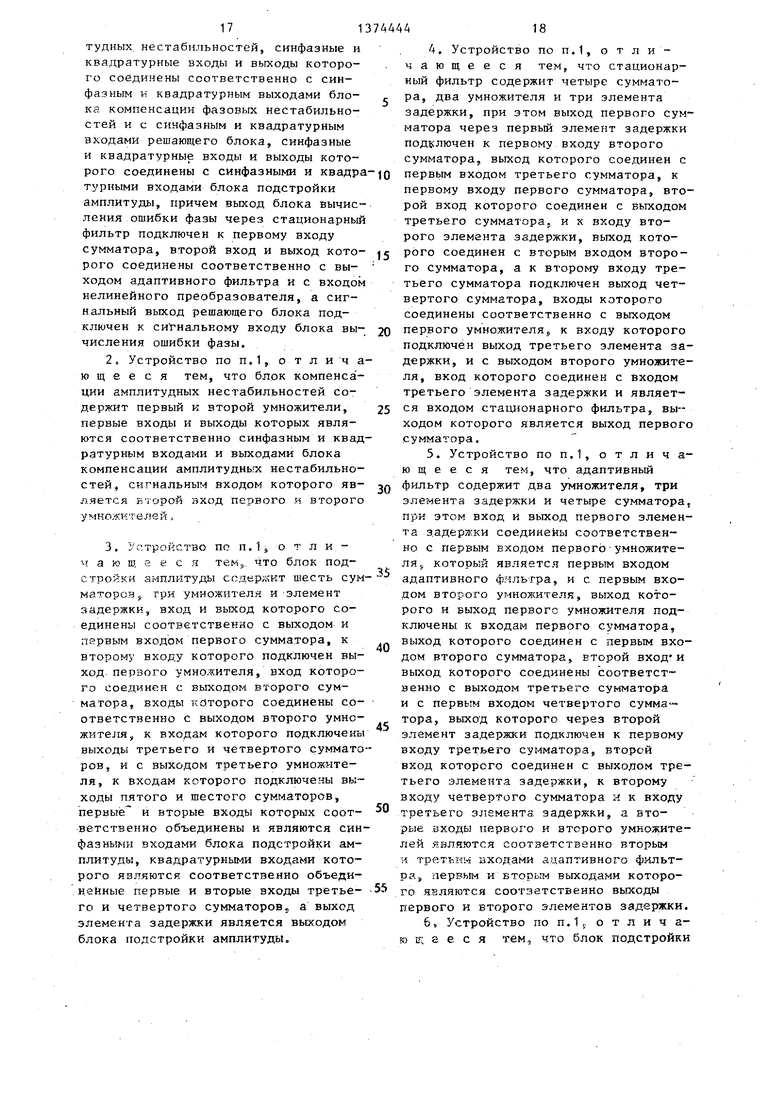

Блок 7 компенсации амплитудных нестабильностей содержит (фиг,3) первый и второй умножители 23-и 24,.

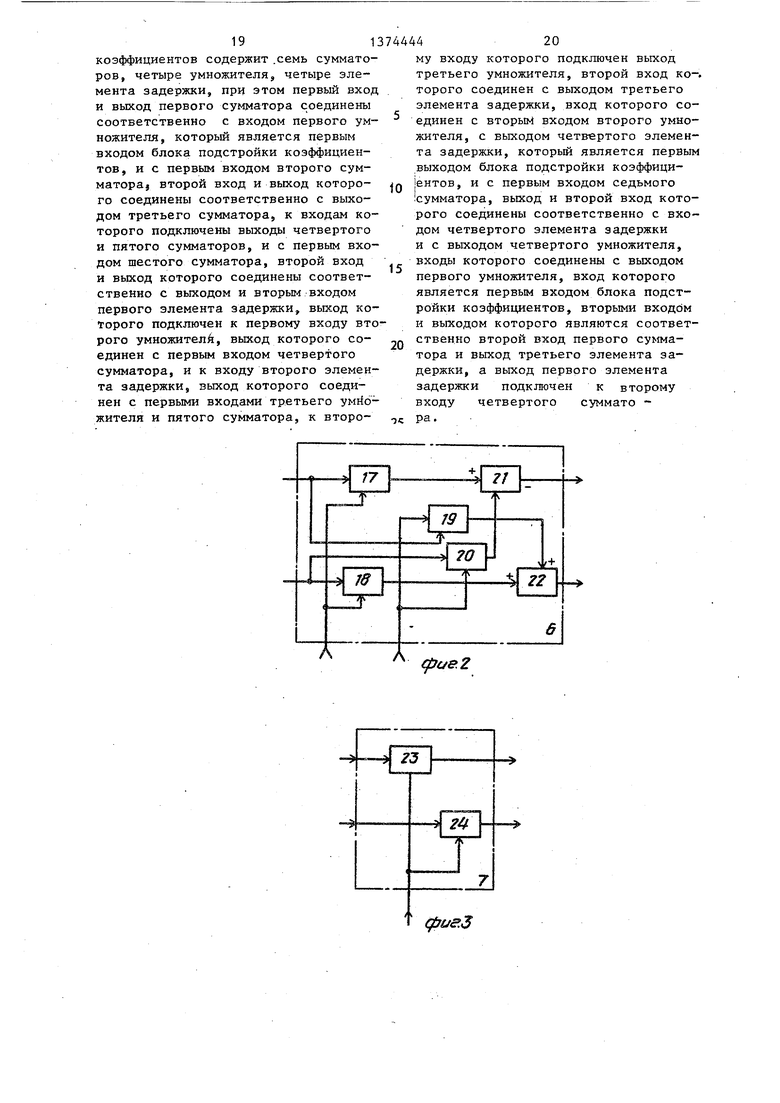

Решающий блок 8 содержит (фиг,4) сумиатор 25, первь й, второй и третий блоки сравнения 26--28, блок 29 хранения эталонов подактантов, блок 30 вычисления квадрата модуля разности расстояний между принятым и эталон- ныш-г сигналами, блок 31 сравнения и выбора наименьшей величины, блок 32 хранения эталонов сигналов.

первый и второй сумматоБлок 9 подстройки амплитуды со- даржит (фиг.5) первый, второй, тре- тий, четвертый, пятый и шестой сумматоры 33-38, первый и второй и тре™

тий умножители 39-41, элемент задержки 42,

Блок 1,0 вычисления ошибки фазы содержит (фиг,6) первый умножитель 43, сумматор 44, второй и третий умножители 45 и 46,

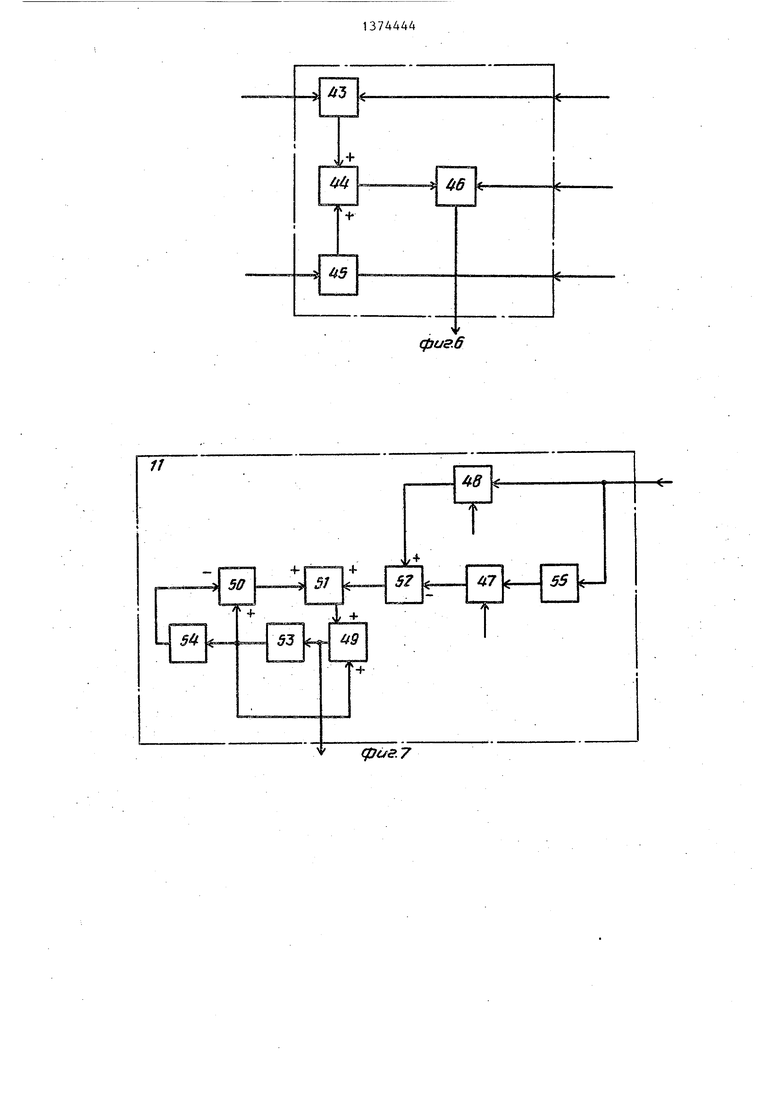

Стационарный ф1 Шьтр 11 содержит (фиг,7) первый и второй умножители

O 47 и 48, первый, второй, третий и четвертый сумматоры 49-52, первый и второй.,и третий элементы задержки 53-55.

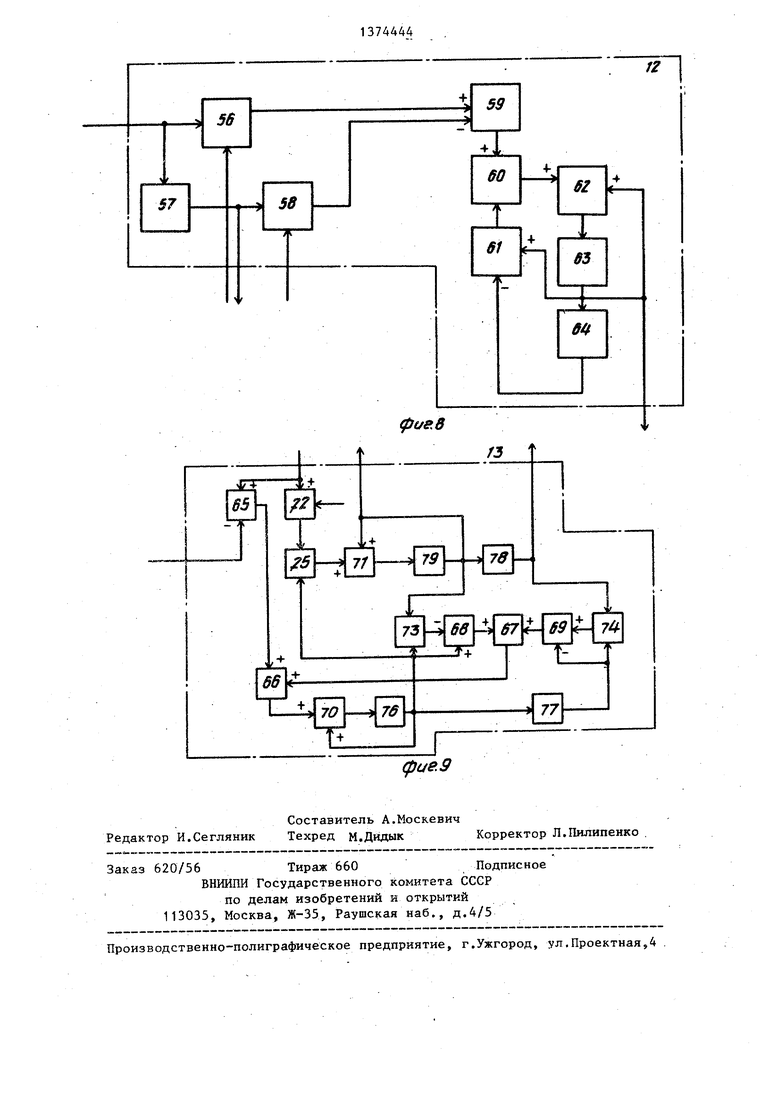

Адаптивный фильтр 12 содержит

5 (фиг,8) первьй умножитель 56, первый элемент задержки 57, второй умножитель 58, первый, второй, третий и четвертый сумматоры 59-62, .второй и третий элементы задержки 63 и 64.

0 Блок 13 подстройки коэффициентов содержит (фиг,9) первый, второЙ4 третий, четвертый, пятьй, шестой и седьмой сумматоры 65-71, первый, второй, третий и четвертый умножи5 тели 72-75, первый, второй, третий и четвертый элементы задержки 76-79, Устройство работает следующим образом.

В устройстве принятая смесь сигнала с шумом канала связи предварительно подстраивается по уровню во входном согласующем блоке 1, Это позволяет осуществить предварительную регулировку уровня сигнала при относительно медленных амплитудных флук- туациях. Входной отфильтрованный сигнал (здесь и далее под сигналом понимаем смесь полезного сигнала и шума канала связи) подается на фазовращатель 2 (фиг,1) для формирования, ортогонального входному,, сигнала (второго подканала), Фазовращатель 2 реализует сдвиг всех частотных составляющих входно1 о сигнала

0

5

x (t) Re а (t) exp -jy(t) + - n(t),

где R - оператор взятия реальной части комплексного произведения, заключенного в квадратных скобках; a(t) - комплексная запись информационных символов, прини- ма1сщих постоянные значения из с6 возможных па длительности тактового интервала Т 1/f ;

y(t) - мгновенная фаза принятого колебания;

n(t) - отфильтрованный шум канала связи, на угол fT/Z, Таким образом формируется сигнал вида

и х - девятиразрядные выборки сигнала синфазного и квадратурного подканалов на т-ом шаге стробирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство адаптивного приема дискретных сигналов с амплитудно-фазовой модуляцией | 1986 |

|

SU1309319A1 |

| Устройство для адаптивной синхронизации опорного колебания высокоскоростного модема | 1982 |

|

SU1099399A1 |

| Адаптивный корректор | 1979 |

|

SU790353A1 |

| Устройство синхронизации опорного колебания высокоскоростного модема | 1991 |

|

SU1800634A1 |

| Адаптивный корректор | 1979 |

|

SU866756A2 |

| Цифровой адаптивный корректор сигналов многократной фазовой модуляции | 1981 |

|

SU1012445A1 |

| ЦИФРОВОЙ АДАПТИВНЫЙ КОРРЕКТОР | 1983 |

|

RU2024199C1 |

| Устройство адаптивного приема дискретных сигналов | 1982 |

|

SU1113891A1 |

| Устройство адаптивной коррекции частотных искажений сигнала М-кратной фазовой модуляции | 1986 |

|

SU1405119A1 |

| Устройство для измерения линейных перемещений объекта | 1989 |

|

SU1740992A1 |

Изобретение относится к электросвязи и обеспечивает повышение помехоустойчивости за счет компенсации амплитудных и фазовых флуктуации сигнала. Устр-во содержит входной согласующий блок 1, фазовращатель 2, АЦП 3, полосовой корректор 4, блок 5 тактовой синхронизации, блок 6 компенсации фазовых нестабильностей, блок 7 компенсации амплитудных нестабильностей, решающий блок 8, блок 9 подстройки амплитуды, блок 10 вычисления ошибки фазы, стационарный фильтр 11, адаптивный фильтр 12,блок 13 подстройки коэф., сумматор 14, нелинейный преобразователь 15 и декодер 16. Введены блоки 7, 9, 11, 14. Поясняется работа блоков 7, 9, 11, 12, 13. 5 з.п. ф-лы, 9 ил.

X

4t) -x(t)

exp

-V

Указанное преобразование позволяет упростить практическую реализацию адаптивной полосовой коррекции, выполняемую полосовым корректором 4, Синфазный и квадратурный подканалы отфильтрованного сигнала строби- руются с удвоенной тактовой частотой (fg 2f, где f - частота стро- бирования; f - частота следования символов). В аналого-цифровом преобразователе 3 после квантования формируются две цифровые десятиразрядные последовательности выборок вход- ных сигналов, следующих с удвоенной тактовой частотой. Эти цифровые сигналы соответственно для синфазного (обозначаются индексом (С) и для квадратурного - индексом (к) подканалов фильтруются в полосовом корректоре. Процедура коррекции решена непосредственно в рабочей полосе частот канала связи, что позволяет существен но улучшить динамические характеристики системы демодуляции принятого сигнала. Это достоинство объясняется исключением большой абсолютной задержки, вносимой полосовым корректором 4, работающим в основной низкочастотной полосе частот. Кроме того, достигается определенное сокращение числа требуемых преобразований сигнала, и как следствие уменьшение соб- .ственных аппаратурных шумов. После коррекции обеих составлякнцих сигна ла (подканалов) девятиразрядные последовательности откорректированного сигнала подаются на блок 6 компенсации фазовых нестабильностей с тактовой частотой (f. f).

Математически описанные операции перехода к цифровому сигналу и полосовой коррекции с прореживанием удобно представить в виде

m

Д)

«,

(t m ТД) х, ,1,.,о.

г„

где В,

D .

И В. , п 2т,

комплексные коэффициенты полосового корректора 4.

X,

J X

m

В,

в;,J в ),

21+1 Z количество коэффициентов полосового корректора 4 (на практике обычно их число-равно 15); комплексная запись выходFI

ного прореженного сигнала.

Для нормального функционирования полосового корректора 4 на каждом тактовом интервале формируются сигналы управления его коэффициентами, а также подстроенные по фазе и частоте цифровые колебания sin tp и coscfn t где qi - оценка мгновенной фазы несущего колебания, генерируемая нелинейным преобразователем 15 на основе поступающей на его вход величины Ц.

Подстройка коэффициентов полосового корректора 4 осуществляется в соответствии с выражением

В

m-f t

В

- Ы Е X,

где

п 2т; М

1/32 весовой коэффициент,

Ёр €„ .

. комплексная ошибка, вырабатываемая решающим блоком 8 в соответствии с алгоритмом

е„ п А

а

где

а.

оценка информационного символа на п-ом тактовом интервале по критерию минимума IС л1

Блок 5 тактовой синхронизации обе спечивается формирование.; импульсов управления подаваемых на аналого- цифровой преобразователь 3. Блок 5 тактовой синхронизации работает по принципу управляемого делителя частоты. Рещение о добавлении или вычитании необходимого количества импульсов выносится на основании сигнала тактовой ошибки, вычисляемой по формуле

Rg в, ехр - jQ - В. ехр

,

-I - } 1 )

где В| и В.| - комплексные коэффициенты отводов полосового корректора А, близлежащие к так называемому центральному8 - набег фазы несущей

за время, равное интервалу дискретизаци Далее сигнал тактовой ошибки ьТ, обр абатьгаается в соответствии с алгоритмом

+ л 2 ЛТ,

О, добавляется импульс ,

О, импульс не добавляется.

О, вычитается импульс о

В блоке 6 компенсации фазовых не- стабильностей осуществляется перенос сигнала в основную (низкочастотную) полосу частот и устранение име- ющих место в каналах связи расхождений по фазе, частоте и фазовых дрожаний между несущим и местным (опорным) колебаниямиf т„е. осуществляется следующее преобразование сигнала:

V« г„ ехр

Щ.

Входные компоненты откорректированного сигнала (фиг.2) умножаются на цифровые сигналы cos q „ и з1пф„ в первом, в гором, третьем и четвертом умножителях 17-20. Причем, синфазная компонента Z умножается на cos qi„ в первом умножителе 17, а квадратурная Z во втор ом умножителе 18, Соответственно квадратурная компонента Z умножается на sirii в четвертом умножителе 20, а синфазная z в третьем умножителе

19, Выходы первого и .четвертого умножителей 17 и 20 вычитаются в первом сумматоре 21, а второго и третьего умножителей 18 и 19 во втором сумматоре 22 с учетом знаков, отмеченных на фиг.2. Выходы первого и второго сумматоров 21 и 22 являются выходами полученного цифрового сигнала и обозначаются для п-го тактового интервала соответственно Vj, и V. Выходные демодулированные (низкочастотные) компоненты сигнала, следующие с тактовой частотой, подаются- на блок 7 компенсации амплитудных нестабильностейг, где осуществляется устранение быстрых амплитудных флуктуации, и реализуется преобразование

где

Wn ,,

ilj, - коэффициент усиления на п-ом тактовом интервале, вырабатываемый блоком 9 подстройки амплитуды

R

П 4-(

Rr

(1)

0

5

0

5

0

где , . 1а.ГR

п +

1 г

амплитудная ошибка} коэффициенты усушения на соответствующих тактовых интервалах Сп+1,п);

/U - весовой коэффициент.

Проведение указанного преобразо вания в упомянутом ранее входном согласующем блоке 1 невозможно из-за того, что аналоговая система автома- ; тической регулировки уровня при попытках увеличить ее быстродействие (в эквиваленте - расшири 1Ь полосу фильтра в цепи ее подстройки) начинает следить за информационньии изменениями амплитуды принимаемого сигнала Только исключение информацкон- кого изменения амплитуды (иначе снятие модуляций), на практике достигаемое в решающем блоке 8 позволяет организовать быстродействующую и точную цифровую систему автоматической регулировки уровня. Использование же сигнала подстройки амплитуды от ре шающего блока 8 непосредствекио в упомянутом входном согласующем блоке 1 дает чрезвычайно инерционную систему, которая принципиально не способна отслеживать быстрые амплитудные флуктуации сигнала. Это легко заме.тить, так как в этом случае оказы- Бается, что полосовой корректор 4 включен в цепь управления регулятором и-его большая абсолютная задержка препятствует быстрому управлению.

Конкретиз ация преобразований над сигналами, осуществляемая в блоке 7

.компенсации амплитуды нестабильно- стей,приведена на фиг.З, где входные цифровые сигналы обоих подканалов V и V умножаются первым и вторым ум ножителями 23 и 2Д на подстраиваемый коэффициент усиления, формируемый блоком 9 подстройки амплитуды.

Подстраиваемый по уровню цифровой сигнал подается на решающий блок 8, который на основании входньж синфазной и квадратурной компонент выносит максимально правдоподобное решение о том, какой из возможных переданных символов присутствует на дан- ном (текущем) тактовом интервале

(фиг.4).

ск

Синфазная W и квадратурная W

составляклцие с выходов блока 7 компенсации амплитудных нестабилькостей подаются на сумматор 25, где определяется разностный сигнал и после его сравнения с нулевым порогом во второ блоке сравнения 27, а также после сравнения сигналов подканалов с нулевыми порогами в первом и третьем бло ках сравнения 26 и 28 формируется адрес на выбор четырех возможных эта-- лонных сигналов из выделенного под- октанта фазовой плотности. Выделение подоктанта происходит таким образом на основании значений входных цифровых сигналов W , Wj и их разности V W. В зоне выбранного подоктанта содержатся четыре эталона, причем каждый из них хранится в блоке 29 хранения эталонов подоктантов в виде двух чисел соответствующих его проекциям на декартовые оси координат. Выбранные указанным способом числа вместе

с входными цифровыми сигналам и W „ подаются на блок 30 вычис

W и

ления квадрата модуля разности расстояний между принятым и эталонными сигналами. В этом блоке 30 одновременно формируется восемь разностей между соответствукнцими выходными

сигналами W,

W

и аналогичными проекциями эталонов на сумматорах. По

Q

г

0 5

Q

0

5

0

5

следующим возведен1 ем, полученных от этих сумматоров сигналов в квадрат и покомпонентным суммированием формируется четыре сигнала, пропорциональные указанным квадратам модулей разностей сигналов. Эти сигналы сравниваются в блоке 3 сравнения i выбора наименьщей величнньь Результаты срао- нения в блоке 31 является формирование трех недостающих сигналов, которые BNsecTe с тремя си)-налами от всех блоков сравнения 26-28 позволяют однозначно выбрать из блока 32 хранения эталонов сигналов один из возможных принятых символов. Таким образом, вынесенное решение о принятом символе в виде двух компонент а „ и а вместе с хранимой величиной, обратной квадрату модуля этого символа появляется на соответствующих выходах решающего блока 8.

В блоке 9 подстройки амплитуды по выходным сигналам а п входным сигналам решающего блока 8- формируется сигнал на изменение уровня в блоке 7 компенсации амплитудных нестабильностей. Конкретные преобразования сигналов В блоке 9 подстройки амплитуды детализированы на фиг.З и включают шесть операций цифрового суммирования в сумь1атора : 33-38, три умножения умножи телями 39-41 и одну операцию задержки на длительность тактового интервала элементом задержки 42. В шестом и пятом сумматорах 38 и 37 осуществляется суммирование квадратурной комА kпоненты входного сигнала W и синфазной компоненты принятого символа 4 J, с соответствующими знаками. В четвертом, третьем сумматорах 36 и 35 аналогичные операции суммирования и вычитания проводятся для синс азной составляющей входного сигнала W и квадратурной компоненты принятого символа а. Выходные сигналы шестого и пятого сумматоров 38 и 37 умножаются во втором умножителе 40, а выходные сигналы четвертого и третьего сумматоров 36 и 35 умножаются в третьем умножителе 41 и после выпол- .нения умножений выходные сигналы второго и третьего умножителей 40 и 41 суммируются во втором сумматоре 34. Выходной сигнал второго сумматора 34 умножается на цифровой весовой множи- . тель |U 0,2, выбираемый из условия требуемого быстродействия системы регулирования амплитуды из диапазона возможных значений (О ш. О. Выходной сигнал первого умножителя 39 суммируется с сигналом подстройки, получаемым на предыдущем тактовом. интервале, в первом сумматоре 33, и выходной сигнал первого сумматора 33 подается на элемент задержки 42, осуществляющий задержку его до еле- дующего тактового интервала. Выходной сигнал элемента задержки 42 одновременно является и выходом блока 9 подстройки амплитуды.

Кратко описанные преобразования сигналов можно охарактеризовать как .определение амплитудного рассогласо- вания (ошибки) , т.е. определени разности квадратов модулей входного сигнала рейакяцей схемы - W, и оценки переданного на данном п-ом тактовом интервале символа а, с последующим

оператор мнимой части комплексного произведения стоящего в фигурньгх скобках. Полученный описанным способом сигнал фазовой ошибки направляется да лее в комбинированную схему, содервыполнением преобразований в соответствии с выражением (1). Начальные условия в (1) нулевые и обеспечивают-2$ стационарный фильтр 11, адап- ся при включении питания на устрой- тивный фильтр 12, блок 13 подстройки ство. Здесь символами W и а,, коэффициентов и сумматор 14. обозначены для краткости изложения Такой подход к решению задачи ком- одновременно обе компоненты этих сигналов.30

Одновременно с точной подстройкой амплитуды по входным Wf, и выходным

сигналам решающего блока 8 в блоке 10 вычисления ошибки фазы осуществляется умножение W , на а в первом умножителе 43 (фиг.6),а умножение W на а во втором умножителе 45. Выходы первого и второго умножителей 43 и 45 суммируются в суммато ре 44, а выходной сигнал умножается и третьем умножителе 46 на-нормирующий множитель 1/|а„| , формируемьй решающим блоком 8 по результату решения.

Иначе, более кратко, преобразования сигналов в блоке 10 можно определить как вычисление мнимой части комплексного произведения W,, W + + j W и a a + j al полагая,; что синфазная и квадратурная компоненты W и а определяют соответственно реальную и мнимую части этих комплексных чисел, а также операции нормировки на величину 1/ |а„1 . Последнее преобразование принципиально для систем, использукнцих ампли- т удную модуляцию, так как полученная

описанным способом оценка фазового

1 ft ii рассогласования зависит от а .

пенсации фазовых нестабильностей позволяет учесть, что в реальных каналах электросвязи и, в частности, каналах тональной частоты осутству- ет априорная информация о статистических характеристиках частотно-фазовых флуктуации, амплитуде и часто- 35 те-фазовых дрожаний. Кроме того, учитывает имеющие место на практике ограничения на точность обработки сигнала (конкретно здесь - наличие девятиразрядного представления чисел).

40

45

50

55

Отсутствие указанных априорных данных не позволяет провести разум- ньй выбор коэффициентов ( |ц и ш ) в стационарном фильтре 11, что приводит к двум возможным ухудшениям работы системы; если коэффициенты ш, и (Uj выбраны большими, т.е. с запасом, то это в эквиваленте означает, что полоса пропускания схемы большая, а значит сопутствующие шумы будут увеличивать фазовую нестабильность местного колебания, формируемого нелинейным преобразователен если коэффициенты li, и л малы, то вследствие узкополосности схемы, система обладает малой полосой захва- та и сийхронизма, что также неприемлемо для практики.

ю

37444410

Умножение на обратную величину устраняет этот вредный эффект. Таким образом, выходной сигнал блока 10 по с сути дела является сигналом ошибки между принятым сигналом и местным колебанием.

В блоке 10 вычиспетя ошибки фазы реализуется преобразование вида

. а„1

где

D -г

D® - нормирующие множители,

формируемые решающим блоком 8;

4 (в зависимости от того, какой принят информационный символ);

оператор мнимой части комплексного произведения стоящего в фигурньгх скобках. Полученный описанным способом сиг нал фазовой ошибки направляется да лее в комбинированную схему, содере

г. стационарный фильтр 11, адап- тивный фильтр 12, блок 13 подстройки коэффициентов и сумматор 14. Такой подход к решению задачи ком

стационарный фильтр 11, адап- тивный фильтр 12, блок 13 подстройки коэффициентов и сумматор 14. Такой подход к решению задачи ком-

пенсации фазовых нестабильностей позволяет учесть, что в реальных каналах электросвязи и, в частности, каналах тональной частоты осутству- ет априорная информация о статистических характеристиках частотно-фазовых флуктуации, амплитуде и часто- те-фазовых дрожаний. Кроме того, учитывает имеющие место на практике ограничения на точность обработки сигнала (конкретно здесь - наличие девятиразрядного представления чисел).

5

0

5

Отсутствие указанных априорных данных не позволяет провести разум- ньй выбор коэффициентов ( |ц и ш ) в стационарном фильтре 11, что приводит к двум возможным ухудшениям работы системы; если коэффициенты ш, и (Uj выбраны большими, т.е. с запасом, то это в эквиваленте означает, что полоса пропускания схемы большая, а значит сопутствующие шумы будут увеличивать фазовую нестабильность местного колебания, формируемого нелинейным преобразователен если коэффициенты li, и л малы, то вследствие узкополосности схемы, система обладает малой полосой захва- та и сийхронизма, что также неприемлемо для практики.

111

Таким образом, создается впечатление, что замена стационарного фильтра 11 эквивалентной адаптивной схемой позволяет в полном объеме решить поставленную задачу. Однако, как показывает практика, такая система излишне чувствительна к возможным кратковременным -искажениям (помехам). В результате имеет место раскачивание местного (опорного) колебания, что фактически означает усиление собственного (аппаратурного) фазового дрожания. Итак, лишь при больших величинах ошибок адаптивная система ведет себя приемлемо с точки зрения компенсации ошибки фазового рассогласования.

Предложенное объединение в комбинированную схему позволяет осущест- БИТЬ уверенную компенсацию больших величин фазовых ошибок за счет адаптивного изменения коэффициента усиления (полосы пропускания) в адаптивном фильтре 12. При достижении основного рабочего режима (синхронизма), т.е. при малых величинах фазовой ошибки, осуществляется автоматическое отключение адаптивного фильтра 12 и блока 13 за счет того, что величины ошибки на ее входе малы и не попадают в разрядную сетку, так как имеет место произведение двух чисел существенно меньших единицы.

Кроме того, хорошо компенсировать

фазовые нестабильности за счет выбора

малых коэффициентов ГЦ, и lU в стационарном фильтре 11.

Коротко сказанное можно охарактеризовать как попеременную работу схем. При больших величинах ошибок работают адаптивный фильтр 12 и блок 13, а при малых - стационарный фильт 11. Объединение сигналов на сумматоре 14 обеспечивает независимость реализации, указанных режимов работы блоков.

Сигнал фазовой ошибки (фиг.7) на п-ом тактовом интервале ( умножается во втором умножителе 48 на весовой коэффициент К, 0,05, а также задерживается на длительность тактового интервала третьим элементом задержки 55. Выходной сигнал третьего элемента задержки 55 (для предшествукнцего тактового интервала) умножае.тся на другой весовой коэффициент |Иг 0,03 в первом умножителе 47. Возможные пределы изменений

12

этих коэффициентов определяются устойчивостью стационарного фильтра 11 и равны О щ, fe 2, . Кроме того, должно выполняться условие |Ы, /Wj . Выходные сигналы первого и второго умножителей 47 и 48 вычитаются в четвертом сумматоре 52, образуя сигнал вида ( , (f fUiCf ,, ), а полученный во вторсж сумматоре 50 разностный сигнал (tf - ) гдеС и ср„, - отфильтрованные значения сигнала ошибки для п-го и (n-l)-ro тактовых интервалов, суммируются с выходным сигналом упомянутого четвертого сумматора 59 в третьем сумматоре 51. Результат сложения в третьем сумматоре 51, в свою очередь, суммируется в первом сумматоре 49 с выходным сигналом первого элемента задержки 53, обозначенного как qp . Выход перво- го сумматора 49 подается на вход первого элемента задержки 53 и одновременно является выходом всего стационарного фильтра 11. Выходной сигнал второго элемента задержки 54 подается на один из входов второго сумматора 50, а также на первый сумматор 49 и вход второго элемента задержки 54, выходной сигнал которого подается на другой вход второго сумматора 50. Более кратко описанные преобразования сигнала фазовой ошибки в стационарном фильтре 11 уместно определить выражением

0

5

5

0

fr,,- fn+4 r -tfn-,,., (2)

гд Cfnti

, Cfn, - значения мгновенной

фазы опорного колебания на соответствующих тактовых интервалах;

и, и |lJi - весовые коэффициенты; Ц п и (j „., - фазовые ошибки между несущим и предсказанным (местным) опор-, ным колебаниями на соответствующих тактовых интервалах.

Начальные условия в (2) нулевые, за исключением с 1/3 для несущей частоты f., 1800 Гц.

п

Сигнал фазовой ошибки (f одновременно (фиг.8) подается на первый умножитель 56 и первый элемент задерж1313

ки 57, Лосле умножения в первом умножителе 56 на переменный коэффициент К, формируемый с выхода четвертого элемента задержки 79, блока 13 подстройки коэффициентов (фиг.9) и умножения су „., с выхода первого элемента задержки 37 во втором умножителе 58 на поступающего с выхода третьего элемента задержки 78, результаты ум- ножений вычитаются в первом сумматоре 59, Выходной сигнал суммируется во втором сумматоре 60 с разностным сигналом, обозначенным как ((7„-1|„,) и формируемьм третьим сумматором 61, Выходной сигнал второго сумматора 60, в свою очередь, суммируется в четвертом сумматоре 62 с сигналом 9 п поступающим с выхода второго элемен

та задержки 63, Выход четвертого сум- 20 V , формируемого первым элементом

матора 62 подключен к входу упомянутого второго элемента задержки 63, Выходной сигнал адаптивного фильтра 12 определяется выходом второго элемента задержки 63 и обозначен символом Вых,1,.

Адаптивная подстройка коэффици- ентов усиления осуществляется в блоке 13 по сигналам фазовой ошибки ц и ., на соответствующих тактовых. интервалах, подаваемых соответствую-. щих тактовых, интервалах, подаваемых со входа и выхода первого элемента задержки 57 адаптивного фильтра 12.

Сигнал Фазовой ошибки СР пода- ется на входы третьего сумматора 61 и первого умножителя 72, В третьем сумматоре 61 определяется разность ( (jf п - Ч у1( ) фазовых ошибок на настоящем (п-ом) тактовом интервале и предшествующем (п-1)-ом, В первом умножителе 72 упомянутый сигнал фазовой ошибки умножается на весовой коэффициент Ш 1/64, после чего результирующий сигнал в четвертом умножителе 75 умножается на вспомогательный сигнал V , подаваемый также на первые входы второго умножителя 73, четвертого сумматора 68, второго элемента задержки 77, шестого сумматора 70 и формируемого с вы хода первого элемента задержки 76.- Выход шестого сумматора 70 соединен со входом первого элемента задержки 76, а на его второй вход подается су 1марный сигнал, формируемый вторым сумматором 66 и представляющий собой сумму упомянутого сигнала ((ff - Cv „-, ) и выходного сигнала

25

30

35

40

45

задержки 76, Выходной сигнал в тре тьем сумматоре 67 суммируется с вы ходным сигналом пятого сумматора 6 и формирует сигнал, подаваемый на второй сумматор 66. Выходной сигна второго элемента задержки 77, пред ставляющий собой вспомогательный с нал Vf,, (на П-1-ОМ тактовом интервале) подается на третий умножи тель 74, где он умножается на пере менный коэффициент К J, поступающ от третьего элемента задержки 78. Выходной сигнал третьего умножите ля 74 суммируется с V в пятом сумматоре 69 и подается на второй вход упомянутого ранее третьего су матора 67.

В результате описанных преобраз ваний сигналов формиуется последов тельное изменение во времени переменных коэффициентов усиления на d ответствующих шагах подстройки К и К„., . .

Кратко описанные преобразования сигналов удобно представить в виде выражений

К

П-(-

- 50

К.

V,

,

V.

Vn к л

- V.

55

+ К„., „.., + ( -(„„

Полученные описанным методом пе ременные коэффициенты усиления умножаются в первом и втором умножителях 56 и 58 адаптивного фильтра 12 соответственно на значения фазо вой ошибки и ., , образуя

4

14

третьего сумматора 67. Выходной сигнал четвертого умножителя 75 суммируется в седьмом сумматоре 71 с выходным сигналом четвертого элемента задержки 79, подаваемого одновременно на входы третьего элемента задерж- и второго умножителя 73, Полученный сигнал в седьмом сумматоре 71 подается на вход четвертого элемента задержки 79. Выходной сигнал третьего элемента задержки 78,представляющий собой переменньй коэффициент

усиления на (п-1) шаге К „, подается на второй умножитель 58 адаптивного фильтра 12 и третий умножитель 74, Выходной сигнал второго умножителя 73 в четвертом сумматоре 68 вычитается из .упомянутого сигнала

5

0

5

0

5

задержки 76, Выходной сигнал в третьем сумматоре 67 суммируется с выходным сигналом пятого сумматора 69 и формирует сигнал, подаваемый на второй сумматор 66. Выходной сигнал второго элемента задержки 77, представляющий собой вспомогательный сигнал Vf,, (на П-1-ОМ тактовом интервале) подается на третий умножитель 74, где он умножается на переменный коэффициент К J, поступающий от третьего элемента задержки 78. Выходной сигнал третьего умножителя 74 суммируется с V в пятом сумматоре 69 и подается на второй вход упомянутого ранее третьего сумматора 67.

В результате описанных преобразований сигналов формиуется последовательное изменение во времени переменных коэффициентов усиления на do- ответствующих шагах подстройки К и К„., . .

Кратко описанные преобразования сигналов удобно представить в виде выражений

К.

,

V.

50

V,

Vn к л

- V.

+ К„., „.., + ( -(„„

Полученные описанным методом переменные коэффициенты усиления умножаются в первом и втором умножителях 56 и 58 адаптивного фильтра 12 соответственно на значения фазовой ошибки и ., , образуя

сигналы вида ( и V., К „, . Эти сигналы вычитаются в первом суматоре 59, выходной сигнал которого суммируется во втором сумматоре 60 с выходным сигналом третьего сумматора 61. Выходной сигнал второго Сумматора подается на четвертый сумматор 62, формирующий сигнал мгновенной -фазы опорного колебания для будущего тактового интервала (|у,, . Этот сигнал через второй элемент заержки 63 подается на упомянутый четвертый сумматор 62 и третий сумматор 61 и одновременно является выодом адаптивного фильтра 12 (этот сигнал обозначен С| ). Кроме того, этот выходной сигнал второго элемента задержки 63 подается через третий элемент задержки 64 на другой вход третьего сумматора 61.

Кратко описанные преобразования сигналов в адаптивном фильтре 12 добно представить в виде выражения

Чп+ « +tf - Ср„, +

+ -к., ц)., .

Полученные таким образом значения мгновенной фазы опорного колебания суммируются в сумматоре 14 (фиг.1) подаются в нелинейный преобразователь 15, где на основе выходного сигнала сумматора 14

л

П +Ц ,.

осуществляется нелинейное преобразование кода числа вида

t-fr

sincf

-cosii

Реализуется это преобразование в нелинейном преобразователе 15 на основе постоянного запоминающего устройства (ПЗУ), содержащего 360 значений sincfn и coscf. Другой возможньй метод такого преобразования осно вьюается на круговой симметрии .

чений sin cf „ и cos С| подоктактам фазовой плоскости и использовании известных формул разложения в степенные ряды на интервале

W.

.-1Гпоследующим применением простейших логических операций над знаковыми разрядами чисел. Требуемые преобразо0

5

0

5

0

5

0

5

П

вания в этом месте сводятся к ряду умножений и суммирований и требуют . хранения в ПЗУ лишь сорока пяти восьмиразрядных чисел.

Формула изобретения

тудных. нестабнльностей, синфазные и

квадратурные входы и выходы которого соединены соответственно с синфазным к квадратурным выходами блока компенсации фазовых нестабильно- стей и с синфазным и квадратурным входами решающего блока, синфазные и квадратурные входы и выходы которого соединены с синфазными и квадра-jQ первь1м входом третьего сумматора, к турными входами блока подстройки амплитуды, причем выход блока вычисления ошибки фазы через стационарный фильтр подключен к первому входу сумматора, второй вход и выход кото- г рого соединены соответственно с вы- ходом адаптивного фильтра и с входом нелинейного преобразователя, а сигнальный выход решающего блока подключен к си гнальному входу блока вы- 20 числения ошибки фазы,

2, Устройство по П.1, от л и ч а- ю щ е е с я тем, что блок компенсации амплитудных нестабильностей содержит первый и второй умножители, первые входы и выходы которых являются соответственно синфазным и квадратурным входами и выходами блока компенсации амплитудных нестабильностей, сигнальным входом которого является кторой вход первого и второго умножителей.

первому входу первого сумматора, вто рой вход которого соединен с выходом третьего сумматора, и х входу второго элемента задержки, выход которого соединен с вторым входом второго сумматора, а к BTopoNry входу третьего сумматора подключен выход четвертого сумматора, входы которого соединены соответственно с выходом первого умножителя5 к входу которого подключён выход третьего элемента за держки, и с выходом второго умножите ля, вкод которого соединен с входом

третьего элемента задержки и являет- 25 ся входом стащюнарного фильтра, выходом которого является выход первог сумматора.

5, Устройство поп,1,отлича ю щ е е с я тем, что адаптивный фильтр содержит два умножителя, три элемента задержки и четыре сумматора при этом вход и выход первого элемен та задержки соединены соответственно с первым входом первого-умножите30

18

первь1м входом третьего сумматора, к

первому входу первого сумматора, второй вход которого соединен с выходом третьего сумматора, и х входу второго элемента задержки, выход которого соединен с вторым входом второго сумматора, а к BTopoNry входу третьего сумматора подключен выход четвертого сумматора, входы которого соединены соответственно с выходом первого умножителя5 к входу которого подключён выход третьего элемента задержки, и с выходом второго умножителя, вкод которого соединен с входом

третьего элемента задержки и являет- ся входом стащюнарного фильтра, выходом которого является выход первого сумматора.

5, Устройство поп,1,отлича- ю щ е е с я тем, что адаптивный фильтр содержит два умножителя, три элемента задержки и четыре сумматора, при этом вход и выход первого элемента задержки соединены соответственно с первым входом первого-умножите

5

0

5

0

5

ля 5 который является первым входом адаптивного фильтра, и с первым входом второго умножителя, выход которого и выход первого умножителя подключены к входам первого сумматора, выход которого соединен с первым входом второго сумматора, второй выход которого соединены соответственно с выходом третьего сумматора и с первь м входом четвертого суммн - тора, выход которого через второй элемент задержки подключен к первому входу третьего суг-шатора, второй вход которого соединен с выходом третьего элемента задержки, к второму входу четвертого сумматора н к входу третьего элемента задержки, а вторые входы первого и второго умножителей являются соответственно вторым и третьнн входами адаптивного фильтра, nepBhn i и вторьгм выходами которого являются соотзетственно выходы первого и второго элементов задержки, 6, Устройство по n,l5 о т л и ч а- ю щ S е с я тем, что блок подстройки

коэффициентов содержит .семь сумматоров, четыре умножителя, четыре элемента задержки, при этом первый вход и выход первого сумматора соединены соответственно с входом первого умножителя, который является первым входом блока подстройки коэффициентов, и с первым входом второго сумматора} второй вход и выход которо- го соединены соответственно с выходом третьего сумматора, к входам которого подключены выходы четвертого и пятого сумматоров, и с первым входом шестого сумматора, второй вход и выход которого соединены соответственно с выходом и вторым входом первого элемента задержки, выход которого подключен к первому входу второго умножители, выход которого со- единен с первым входом четвертого сумматора, и к входу второго элемента задержки, выход которого соединен с первыми входами третьего умйо- жителя и пятого сумматора, к второ-

му входу которого подключен выход третьего умножителя, второй вход ко- торого соединен с выходом третьего элемента задержки, вход которого соединен с вторым входом второго умножителя, с выходом четвертого элемента задержки, который является первым выходом блока подстройки коэффици- jeHTOB, и с первым входом седьмого сумматора, выход и второй вход которого соединены соответственно с входом четвертого элемента задержки и с выходом четвертого умножителя, входы которого соединены с выходом первого умножителя, вход которого является первым входом блока подстройки коэффициентов, вторыми входом и выходом которого являются соответственно второй вход первого сумматора и выход третьего элемента задержки, а выход первого элемента задержки подключен к второму входу четвертого суммато - ра.

Л

fffae.2

Н

фие.5

fPrl

23

И

W

31

Г 1

фиеЛ

J3

gjueS

11

50

51

U6

фигб

(±.

55

дза5.7

| Патент США 4320526, .кл | |||

| Ручной дровокольный станок | 1921 |

|

SU375A1 |

Авторы

Даты

1988-02-15—Публикация

1986-07-30—Подача