RsFC

(Л

Imfy,

KeFlPj

оо

О5 Ю

Щ(Р,}

N

гармонических функций, блоки умножения, регистры 7, 8, 10, 15- 18, 21, 22, 29 и 30, генератор 31 тактовых импульсов, делитель 32 частоты, блоки 3, 4 27 и 28 оперативной ти. В устройство введены блоки 33 и 34 управления знаком операнда, сумматоры 36 и 37, блоки 40 и 41 оперативной памяти, регистры 38, 39, 42 и 43 и блок 35 задержки. Длительность такта работы определения мгновенного спектра определяется в основном временем выполнения операции умножения. Вьтолнение операции управления знаком операнда, осуществляемое в одном такте с суммированием в сумматорах 36 и 37, не увеличивает длительности такта работы. В это же время за счет параллельного вычисления двух спектров период дискретизации анализируемого сигнала может быть уменьшен в 2 раза, что приводит к расширению частотного диапазона анализируемых сигналов. 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой анализатор мгновенного спектра комплексного сигнала | 1986 |

|

SU1406507A2 |

| Цифровой анализатор мгновенного спектра | 1986 |

|

SU1456904A2 |

| Цифровой анализатор мгновенного спектра | 1980 |

|

SU932419A1 |

| Цифровой анализатор мгновенного спектра | 1983 |

|

SU1095093A1 |

| Цифровой анализатор спектра фурье | 1976 |

|

SU614440A1 |

| Цифровой анализатор спектра | 1978 |

|

SU734579A1 |

| Цифровой генератор синусоидальных сигналов | 1984 |

|

SU1215162A1 |

| Цифровой генератор | 1986 |

|

SU1347164A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПСЕВДОСЛУЧАЙНОГО СИГНАЛА | 1989 |

|

SU1692272A1 |

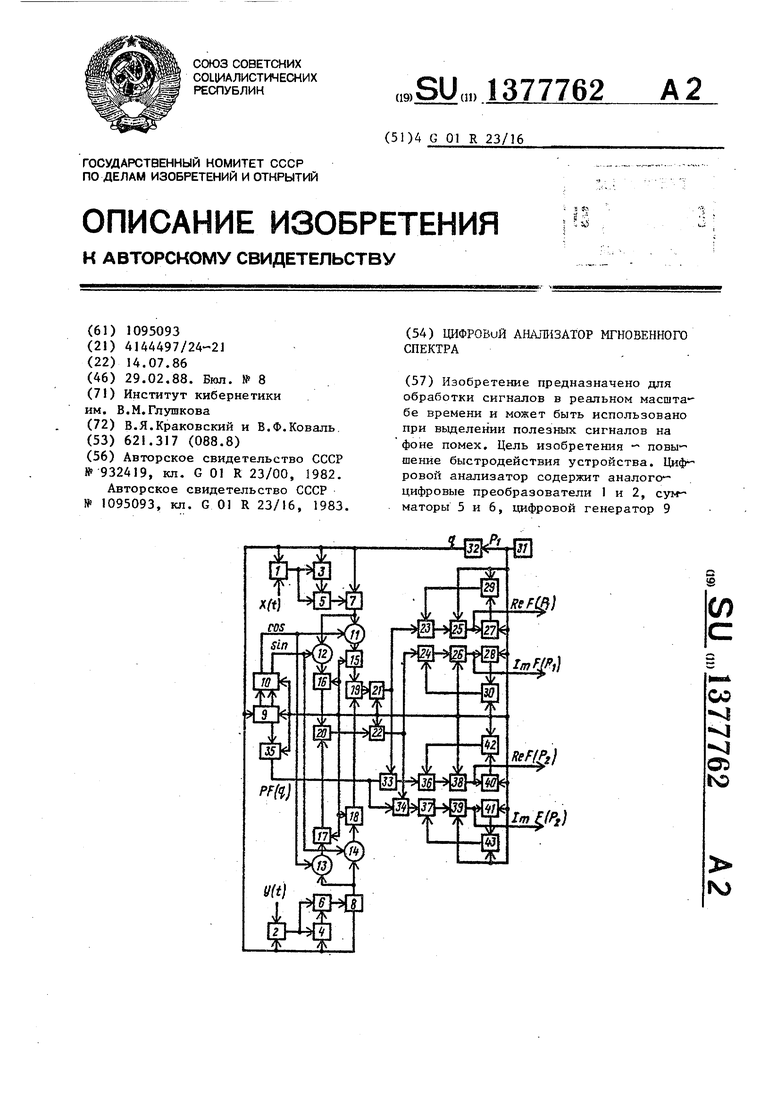

Изобретение предназначено для обработки сигналов в реальном масшта бе времени и может быть использовано при выделении полезных сигналов на фоне помех. Цель изобретения - повы шение быстродействия устройства. ровой анализатор содержит аналого-цифровые преобразователи 1 и 2, сум маторы 5 и 6, 1Ц1ФРОВОЙ генератор 9

1

Изобретение относится к цифровой вычислительной технике, предназначено для обработки.сигналов в реальном масштабе времени, может быть использовано в задачах выделения полезных сигналов на фоне помех и в спектральном анализе и является усовершенствованием изобретения по авт. св. № 1095093.

Цель изобретения - повышение быстродействия цифрового анализатора мгновенного спектра.

На чертеже представлена структурная схема цифрового анализатора мгно венного спектра.

Анализатор содержит два аналого- цифровых преобразователя (АЦП) 1 и 2, на входы которых поступает действи- тельная и мнимая составляющие входно- го комплексного сигнала, блоки 3 и 4 оперативной памяти (БОП), сумматоры 5 и б, первый 7 и девятый В регистры цифровой генератор 9 гармонических функций, второй регистр 10 для хране кия отсчетов этих функций, первый llj второй 12, третий 13 и четвертый 14 блоки умножения с десятым 15, одиннадцатым 16, двенадцатым 17 и тринадцатым 18 регистрами, .пятый 19 и шее- той 20 сумматоры с третьим 21 и четвертым 22 регистрами, второй 23 и третий 24 сумматоры с пятым 25 и шес тым 26 регистрами, второй 27 и третий 28 БОП с седьмзш 29 и восьмым 30 регистрами, генератор 31 тактовых импульсов с делителем 32 частоты.

Кроме того, устройства содержит вновь введенные первый 33 .и второй 34

5

.с

рп 25 зо

5

блоки управления знаком операнда, информационные входы которых соединены с выходами соответственно третьего 21 и четвертого 22 регистров, а управляющие входы объединены и подключены к выходу блока задержки 35, вход которого соединен с выходом первого разряда счетчика параметра частоты цифрового генератора 9 гармонических функций, а выходы юс подсоединены к первым входам соответственно седьмого 36 и восьмого 37 сумматоров. Выходы седьмого 36 и восьмого 37 сумматоров подсоединены соответственно через четырнадцатый 38 и пятнадцатый 39 регистры к информационным входам соответственно пятого 40 и шестого 41 блоков оперативной памяти; выходы регистров 38 и 39 являются вторыми выходами устройства. Выходы пятого. 40 и шестого 41 блоков оперативной памяти соединены соответственно через шестнадцатый 42 и семнадцатый 43 регистры с вторыми входами соответственно седьмого 36 и восьмого 37 сумматоров. Управляющие входы всех введенных регистров, блоков оперативной памяти и блока задержки соединены с выходом генератора 31 тактовых импульсов.

Анализатор работает следующим образом.

Генератор 31 тактовых импульсов и делитель 32 частоты управляют работой операционных блоков анализатора таким образом, что смена информации в АЦП.1 и 2, БОП 3 и 4, сумматорах 5 и 6, а также регистрах 7 и 8 проис-

ходит в N/2 раз реже, чем в остальных блоках анализатора.

Разрядность БОП 3 и 4 соответствую ет разрядности преобразователей 1 и 2 а число ячеек равно N. С приходом каждого запускающего импульса с Bbi хода делителя 32 частоты происходит запись составляющих приращения от- счета

/If f(q) - f(q-N) rx(q) - - x(q-N) + j y(q) - y(q-N),

где x(q) - отсчет анализируемого

сигнала; у(ч) отсчет квадратурной

составляющей анализируемого сигнала, в регистры 7 и 8.,

В блоки 3 и 4 записываются соот ветственно значения x(q) и y(q). Преобразователи 1 и 2 вырабатывают коды составляющих нового отсчета со- ответственно А x(q+l) и В, y(q+l) и подают их на входы блоков 3 и 4 и первые входы сумматоров 5 и 6, на вторые входы которых с выхо дов блоков 3 и 4 поданы значения А x(q-N-t-l) и В y(). Сумматоры 5 и 6 производят соответственно вычитания и В,В и результаты подают на информационные входы ре- гистров 7 и 8. В таком состоянии блоки остаются до прихода следую щего импульса с делителя 32 частоты, который записывает значения прираще- НИИ в регистры 7 и 8, и производятся вновь перечисленные операции. Разряд ность сумматоров 5 и 6, регистров 7 и 8 должна быть на один разряд больше разрядности АЦП 1 и 2.

Выход регистра 7 подается на пер- яые входы блоков П и 12 умножения, а выход регистра 8 - на первые входы блоков 13 и 14 умножения. На вторые входы блоков 11 и 13 умножения с пер вого выхода регистра 10 последовательно во времени поступает значение действительной составляющей весового коэффициента С, а на вторые входы блоков 12 и 14 умножения с второго выхода регистра 10 последовательно в времени поступает значение мнимой состсшляющей весового коэффициента S. Эти составляющие весовых коэффи-

Запись информации в регистры 21 и 22 производится синхронно следующим тактовым импульсом. Вычисленное значение приращения спектра лГл(Р,) с выходов регистров 21 и 22 подается соответственно на первые входы сумматоров 23 и 24 и одновременно через блоки 33 и 34 управления знаком операнда подается соответственно на первые входы сумматоров 36 и 37. Причем в блоках 33 и 34 знак приращения (Pi) или сохраняется при q четном, или меняется на противоположный при q нечетном. Признак четности снимается с выхода блока 35 задержки, вход которого соединен с выходом первого разряда счетчика параметра частоты блока цифрового генератора 9 гармонических функций. Необходимость введения блока 35 задержки обусловлена конвейерным характером обработки информации в предлагаемом устройстве, так как номер гармоники, приращение спектра для которой выставлено на выходах регистров 21 и 22, отстает на три от номера гармоники, значение q для которой выставлено на выходах счетчика.параметра частоты цифрового генератора 9 гармонических функций. Соответственно в блоке 35 задержки производится задержка выдачи признациентов вырабатывает дифровой генера-55 ка четности PF(q) на три периода дейтор 9 гармонических функций и подает на информационные входы регистр.а 10. При этом с помощью генератора 31 так-

ствия импульсов с выхода генератора 31 тактовых импульсов. Конструктивно блок 35 задержки может представлять

5

0

5

0

35 40

45 50

0

товых импульсов работа схемы синхронизирована таким образом, что с приходом каждого тактового импульса в регистр 10 записываются значения С и S, а генератор 9 начинает вырабатывать следующую пару коэффициентов. Разделительные регистры вьтолняют функции сверхоперативных запоминающих устройств.

Значения произведений с выходов блоков 11-14 умножения подаются на. информационные входы регистров 15- 18 соответственно. Запись информации в эти регистры производится следующим тактовым импульсом.

Выходы регистров 15 и 1В подаются на входы сумматора 19, где образуется их сумма, которая подана на информационный вход регистра 21. Выходы регистров 16 и 17 подаются на входы сумматора 20, где образуется их ал- гербаическая сумма, которая подается на информационный вход регистра 22.

Запись информации в регистры 21 и 22 производится синхронно следующим тактовым импульсом. Вычисленное значение приращения спектра лГл(Р,) с выходов регистров 21 и 22 подается соответственно на первые входы сумматоров 23 и 24 и одновременно через блоки 33 и 34 управления знаком операнда подается соответственно на первые входы сумматоров 36 и 37. Причем в блоках 33 и 34 знак приращения (Pi) или сохраняется при q четном, или меняется на противоположный при q нечетном. Признак четности снимается с выхода блока 35 задержки, вход которого соединен с выходом первого разряда счетчика параметра частоты блока цифрового генератора 9 гармонических функций. Необходимость введения блока 35 задержки обусловлена конвейерным характером обработки информации в предлагаемом устройстве, так как номер гармоники, приращение спектра для которой выставлено на выходах регистров 21 и 22, отстает на три от номера гармоники, значение q для которой выставлено на выходах счетчика.параметра частоты цифрового генератора 9 гармонических функций. Соответственно в блоке 35 задержки производится задержка выдачи призна55 ка четности PF(q) на три периода действия импульсов с выхода генератора 31 тактовых импульсов. Конструктивно блок 35 задержки может представлять

собой З- разрядный сдвиговый регистр, содержащий всего три триггера.

На вторые вкоды сумматоров 23 и

24,а также сумматоров 36 и 37 пода ются соответственно выходы регистров 29 и 30, а также соответственно ре гистров 42 и 435 в которых записаны соответствующие значения действитель ных и мнимых составляющих спектра со- ответственно первого и второго под диапазонов, полученных на предыдущем шаге скольже шя,

Суммирование в сумматорах 23 и 24, а также в сумматорах 36 и 37 произ водится с учетом масштабного множителя 1/N, а так как N 2, где п - целое, то учет этого масштабного множи теля осуществляется путем соответст вующего сдвига на п разрядов. На выходе сумматора 23 получается сумма действительной составляющей спектра первого поддиапазона, которая подает ся на информационный вход регистра

Запись в регистры 25, 26, 38 и 39 производится следующим тактовым импульсом. С выходов регистров 25 и 26 значения отсчетов мгновенного спектра первого поддиапазона поступают на первый выход анализатора и одновременно на информационные входы соответственно БОП 27 и 28. С выходов регистров 38 и 39 значения отсчетов мгновенного спектра второго поддиапазона поступают на второй выход анализатора и одновременно на информационные входы соответственно БОП 40 и 41.

Следующим тактовым импульсом в регистры 29, 30, 42 и 43 с выходов БОП 27, 28, 40 и 41 записываются следующие значения отсчетов. Ьнсло ячеек памяти в каждом из БОП 27, 28, 40 и 41 равно N/2,- 2. Следует иметь в виду, что в тот момент времени, когда на выход анализатора поданы отсчеты гармоник с номерами Р.и Pj (записанные в регистрах 25j 26, 38 и 39)

на регистрах 21, 22, 29, 30, 42 и 43 установлены операнды, соответствующие номерам гармоник Р, + 1 и Рг + 1, на - выходах регистров 15-18, БОП 27, 28, 40 и 41 устанавливаются операнды, соответствующие номерам гармоник PI + 2 и P l + 2, на выходах регистров 7, 8 и 10 устанавливаются

Q операнды, соответствующие номерам гармоник Р, +ЗиР/( + Зи, наконец, цифровой генератор 9 гармонических функций готовл в этот момент весовые коэффициенты, соответствующие но-

. меру гармоники Р +4иР2+4.

Заметим, что общий .объем памяти не возрос, так как емкость БОП 27 и 28 умевьщилась в два раза. Кроме того, разрядность делителя 32 частоQ ты уменьшилась на один разряд.

Заметим также, что номера гармоник в первом и втором поддиапазонах,для которых одновременно выдаются отсчеты спектра, связаны соотноше шем v 5 PI + N/2.

Длительность такта работы конвейерного устройства определения мгновенного спектра определяется в основ- ; ном временем выполнения операции умножения в блоках 11-14, так что выполнение дополнительной операции управления знаком операнда в блоках 33 и 34, осуществляемое в одном такте с cy миpoвaниeм в сумматорах 36 и 37, не увеличит длительности такта работы. В то же время за счет параллельного вычисления двух спектров период дискретизации анализируемого с гнала может быть уменьшен в два раза, что приводит к -такому же расширению частотного диапазона анализируемых сигналов ,

Фор м у ла изобретения

5

Цифровой анализатор мгновенного

спектра по авт. св. № 1095093, отличающий ся тем, что, с целью повьщ1ения его быстродействия, в него введены два блока управления знаком операнда, два сумматора, два блока оперативной памяти, четыре регистра и блок задержки, причем выходы третьего и четвертого регистров соединены с первыми входами соответст- 5 венно седьмого и восьмого сумматоров через соответственно первый и второй блоки управления знаком операнда, выходы этих сумматоров соединены с вхо-

0

5

0

0

713777628

дами соответственно пятого и шестого гистры, управляющие входы блоков упблоков oneiiaTHBHoft памяти через соот равления знаком операнда соединены с

ветственно четьфнадцатый и пятнадца-выходом блока задержки, вход которо - тый регистры, выходы этих регистров , го соединен с выходом первого разря-являются вторыми выходами устройства,Д счетчика параметра частоты цифро выходы пятого и шестого блоков опера -вого генератора гармонических функтивной памяти соединены с вторыми ций, а управляющие входы всех введен- входами соответственно седьмого и регистров, блоков оперативной павосьмого сумматоров через соответст - tnпяти и блока задержки соединены с вы

венно шестнадцатый и семнадцатый ре- ходом генератора тактовых импульсов.

| Цифровой анализатор мгновенного спектра | 1980 |

|

SU932419A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой анализатор мгновенного спектра | 1983 |

|

SU1095093A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-02-28—Публикация

1986-07-14—Подача