Изобретение относится к специализированным средствам измерительной техники, предназначенным для определения спектральных свойств ложных сигналов в задачах идентификации объ- актов, например в технической диагностике, радиосвязи, океанологии.

Цель изобретения - упрощение анализатора за счет формирования кодов произведений в одном счетчике импуль- сов и использования процедуры записи-считывания кодов произведений в буферный блок памяти.

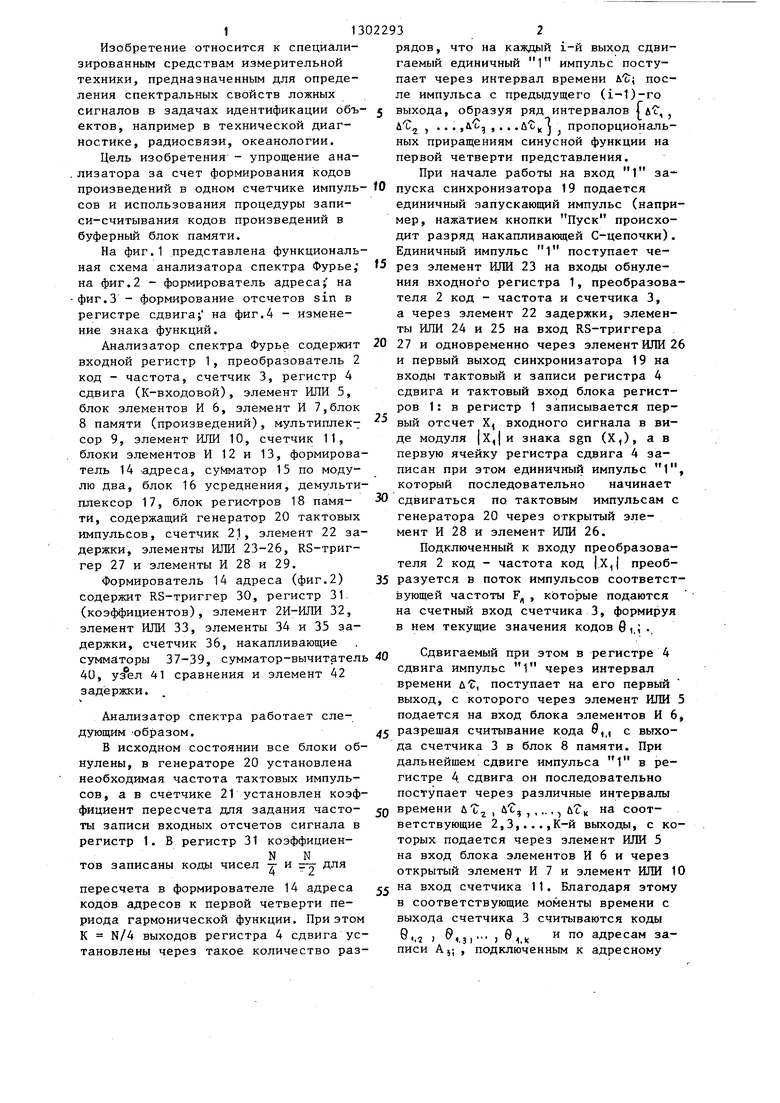

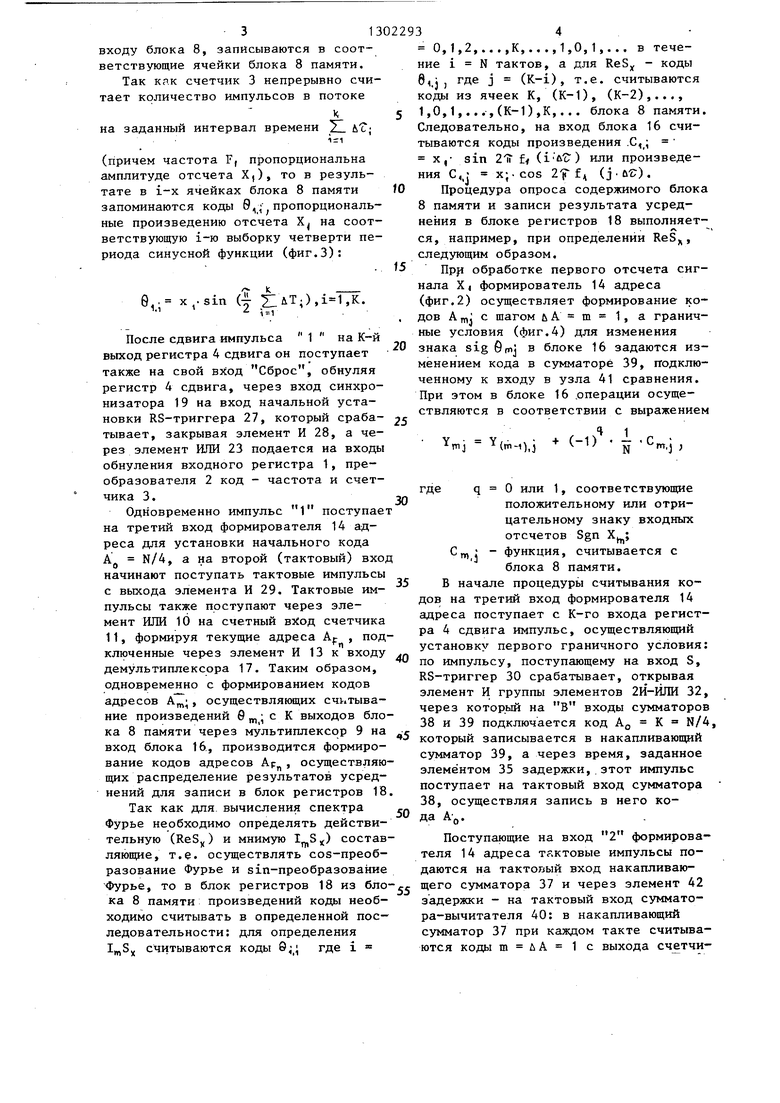

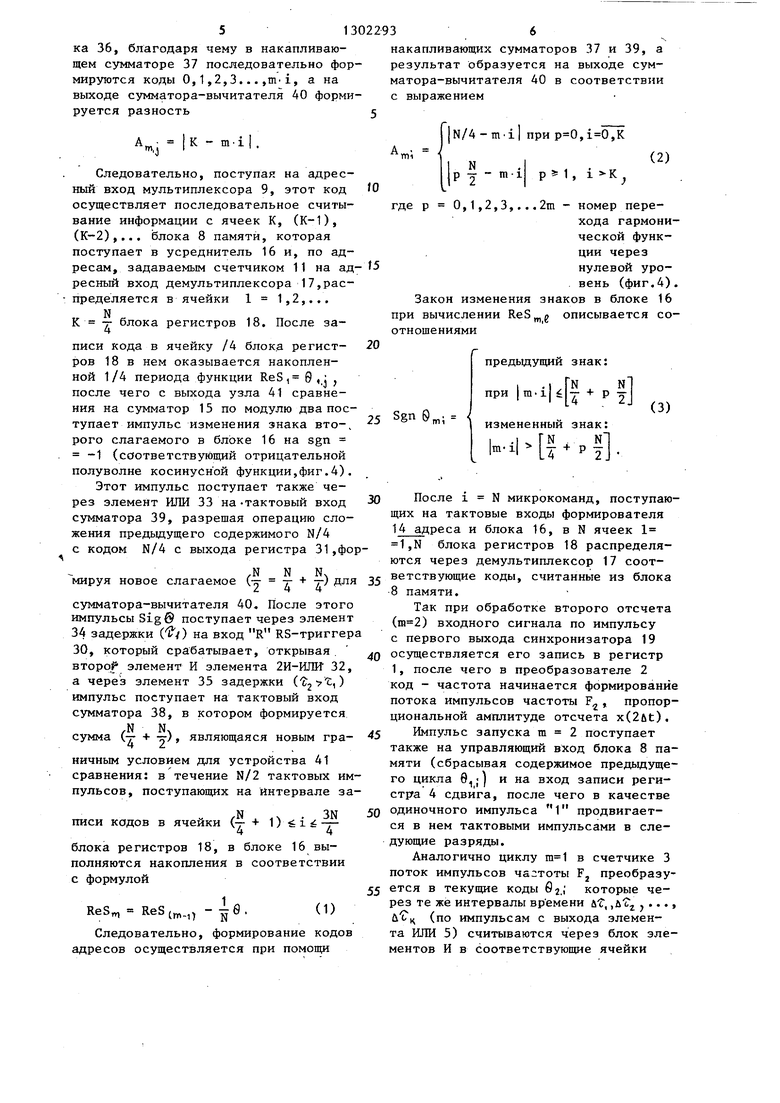

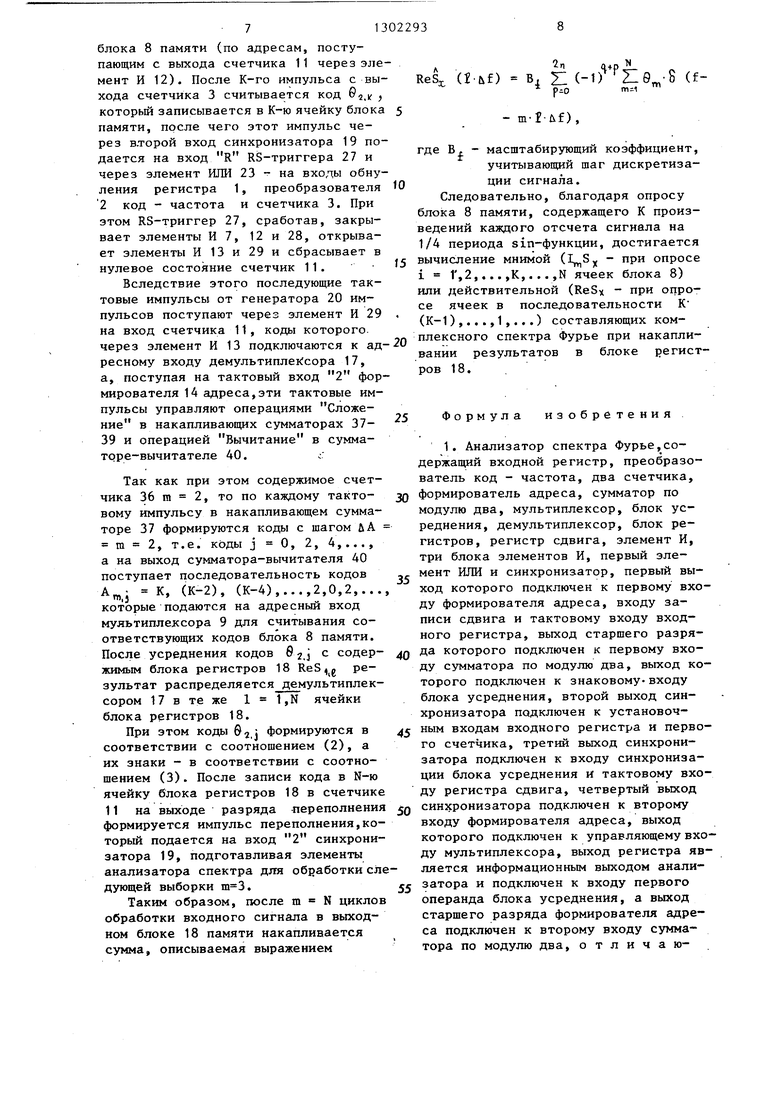

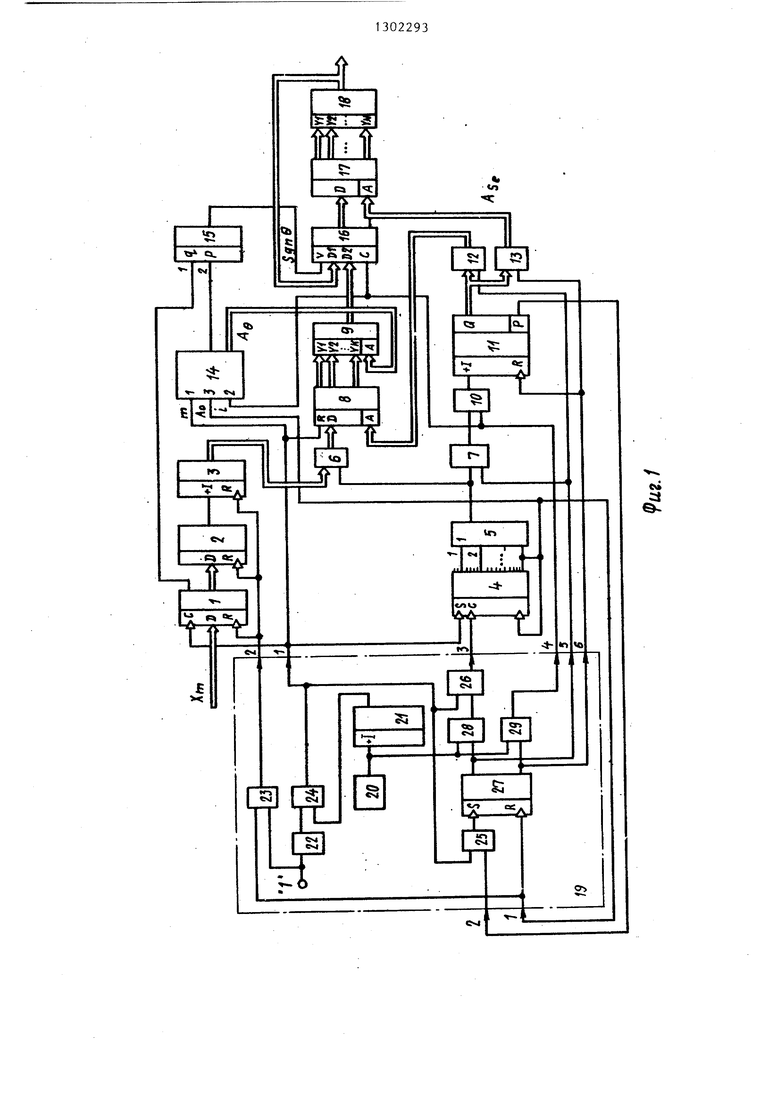

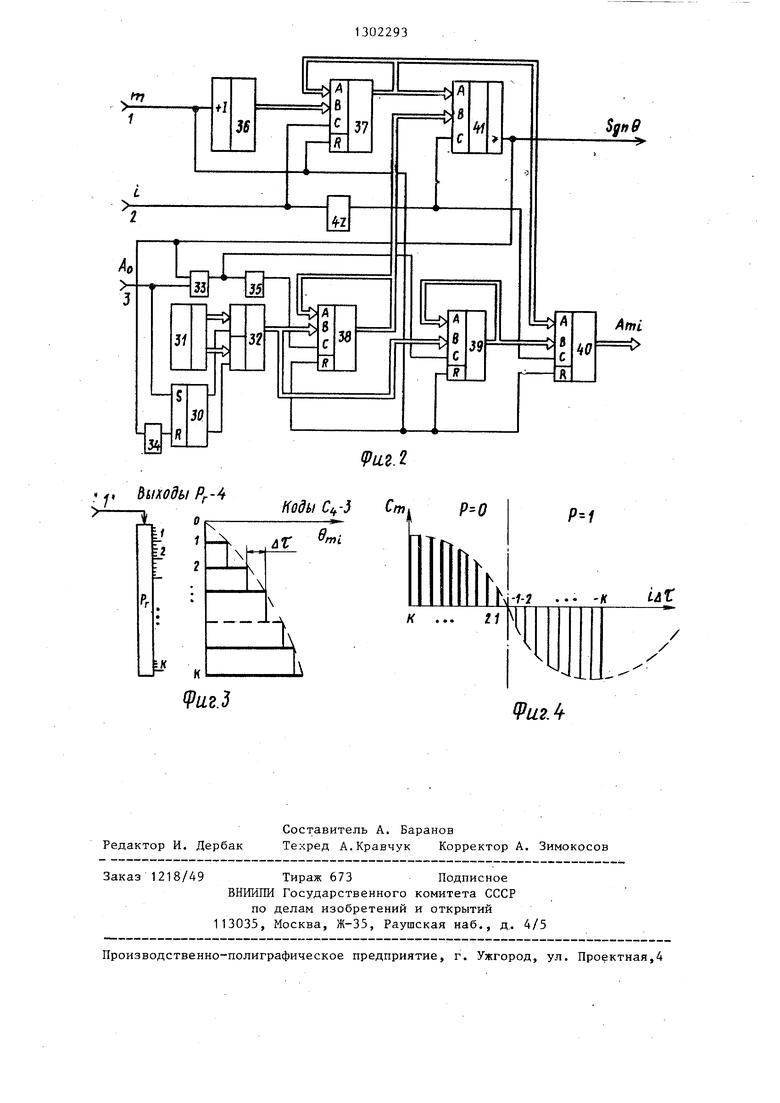

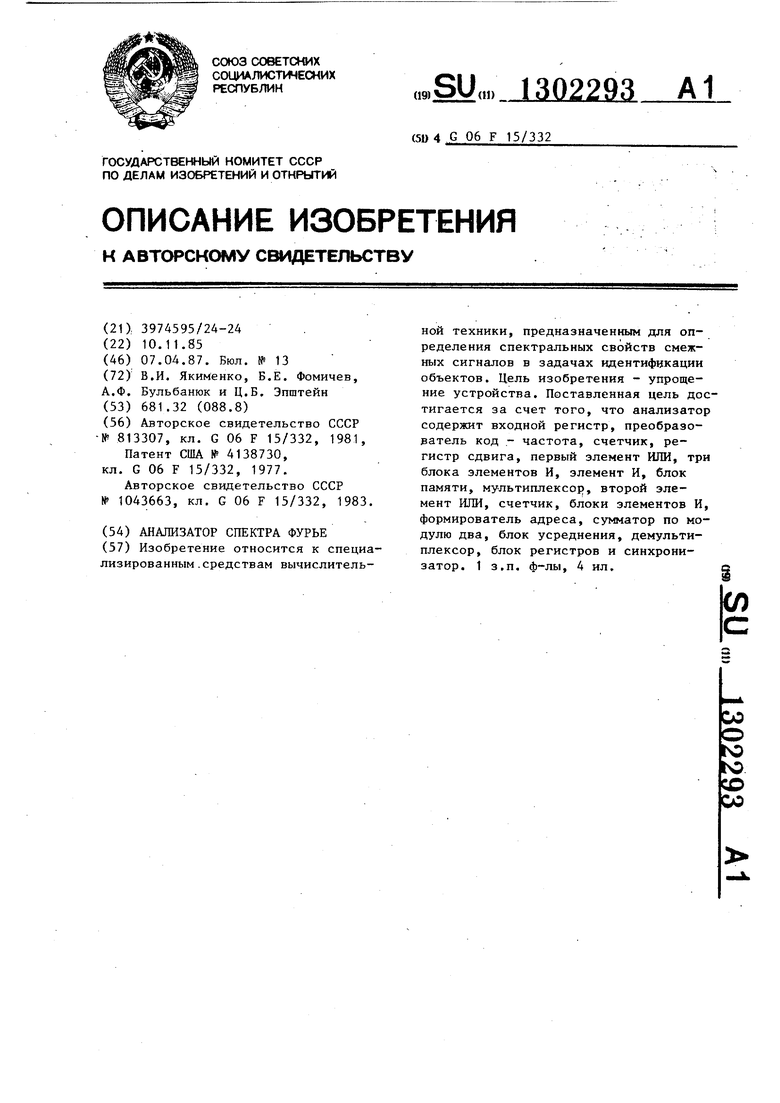

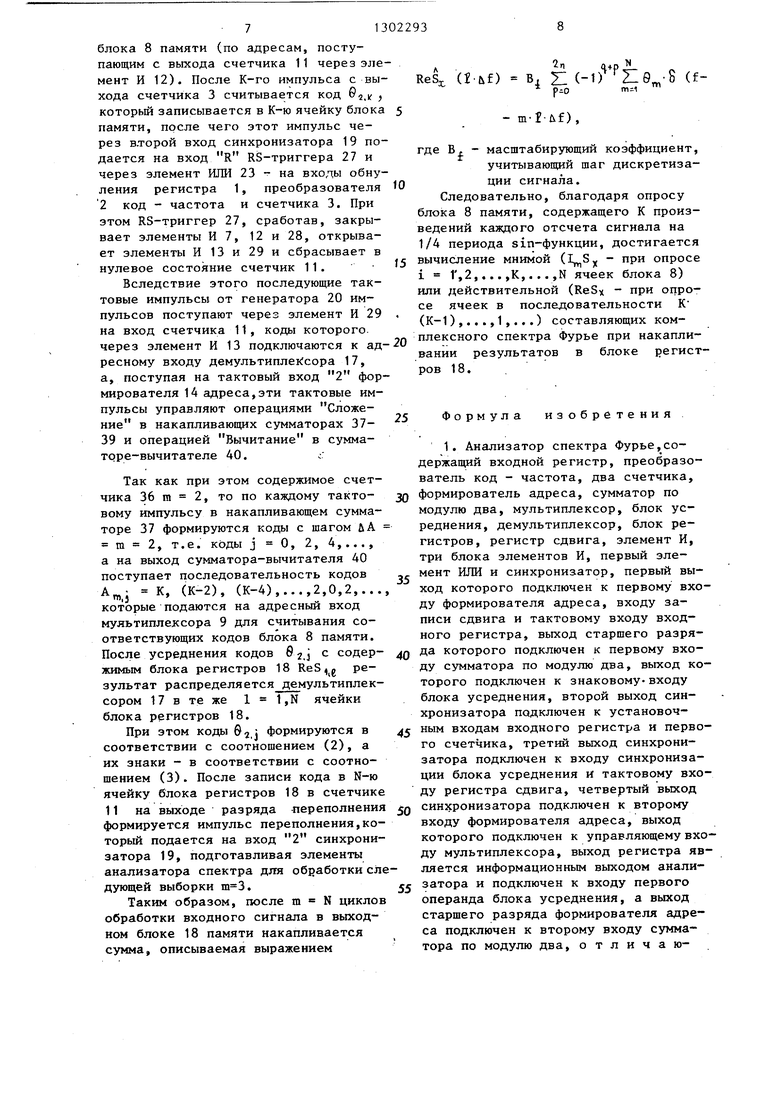

На фиг.1 представлена функциональная схема анализатора спектра Фурье, на фиг.2 - формирователь адреса; на фиг.З - формирование отсчетов sin в регистре сдвига; на фиг,4 - изменение знака функций.

Анализатор спектра Фурье содержит входной регистр 1, преобразователь 2 код - частота, счетчик 3, регистр 4 сдвига (К-входовой), элемент ИЛИ 5, блок элементов И 6, элемент И 7,блок 8 памяти (произведений), мультиплек- сор 9, элемент ИЛИ 10, счетчик 11, блоки элементов И 12 и 13, формирователь 14 -адреса, сумматор 15 по модулю два, блок 16 усреднения, демульти- плексор 17, блок регис-тров 18 памя- ти, содержащий генератор 20 тактовых импульсов, счетчик 21, элемент 22 задержки, элементы ИЛИ 23-26, RS-триг- гер 27 и элементы И 28 и 29.

Формирователь 14 адреса (фиг.2) содержит RS-триггер 30, регистр 31 (коэффициентов), элемент 2И-ИЛИ 32, элемент ИЛИ 33, элементы 34 и 35 задержки, счетчик 36, накапливающие сумматоры 37-39, сумматор-вычитатель 40, 41 сравнения и элемент 42 задержки.

Анализатор спектра работает следующим Образом.

В исходном состоянии все блоки обнулены, в генераторе 20 установлена необходимая частота тактовых импульсов, а в счетчике 21 установлен коэффициент пересчета для задания часто- ты записи входных отсчетов сигнала в регистр 1. В регистр 31 коэффициенN N тов записаны коды чисел -т- и :rj для

пересчета в формирователе 14 адреса кодов адресов к первой четверти периода гармонической функции. При этом К N/4 выходов регистра 4 сдвига установлены через такое количество разрядов , что на каждый i-й выход сдвигаемый единичный 1 импульс поступает через интервал времени после импульса с предыдущего (i-l)-ro выхода, образуя ряд интервалов Гл с, Л с ) . . пропорциональных приращениям синусной функции на первой четверти представления.

При начале работы на вход 1 запуска синхронизатора 19 подается единичный запускающий импульс (например, нажатием кнопки Пуск происходит разряд накапливающей С-цепочки). Единичный импульс 1 поступает через элемент ИЛИ 23 на входы обнуления входного регистра 1, преобразователя 2 код - частота и счетчика 3, а через элемент 22 задержки, элементы ИЛИ 24 и 25 на вход RS-триггера 27 и одновременно через элемент ИЛИ 26 и первый выход синхронизатора 19 на входы тактовый и записи регистра 4 сдвига и тактовый вход блока регистров 1: в регистр 1 записывается первый отсчет Х входного сигнала в виде модуля |х,| и знака sgn (X,), а в первую ячейку регистра сдвига 4 записан при этом единичный импульс 1, который последовательно начинает сдвигаться по тактовым импульсам с генератора 20 через открытый элемент И 28 и элемент ИЛИ 26.

Подключенный к входу преобразователя 2 код - частота код |.Х,( преобразуется в поток импульсов соответствующей частоты F , которые подаются на счетный вход счетчика 3, формируя в нем текущие значения кодов 0,,;.

Сдвигаемый при этом в регистре 4 сдвига импульс 1 через интервал времени дТ, поступает на его первый выход, с которого через элемент ИЛИ 5 подается на вход блока элементов И 6, разрешая считывание кода 0,,, с выхода счетчика 3 в блок 8 памяти. При дальнейшем сдвиге импульса 1 в регистре 4 сдвига он последовательно поступает через различные интервалы

времени й С , л.

Лс,

на соответствующие 2,3К-й выходы, с которых подается через элемент ИЖ 5 на вход блока элементов И 6 и через открытый элемент И 7 и элемент ИЛИ 10 на вход счетчика 11. Благодаря этому в соответствующие моменты времени с выхода счетчика 3 считываются коды

«.2 ) 13) ® 1,к и по адресам записи А,; , подключенным к адресному

входу блока 8, записываются в соответствующие ячейки блока 8 памяти.

Так как счетчик 3 непрерывно считает количество импульсов в потоке

Ч на заданный интервал времени J дТ;

in

(причем частота F, пропорциональна амплитуде отсчета X,), то в результате в i-x ячейках блока В памяти запоминаются коды 9,; пропорциональные произведению отсчета Х на соответствующую i-ю выборку четверти периода синусной функции (фиг.З):

6.. X -sin ( ЛТ;),,К.

ные условия (фиг.4) для изменения .20 знака sig 6rnj в блоке 16 задаются изменением кода в сумматоре 39, подключенному к входу в узла 41 сравнения. При этом в блоке 16 .операции осущеПосле сдвига импульса 1 на К-й выход регистра 4 сдвига он поступает также на свой вход Сброс, обнуляя регистр 4 сдвига, через вход синхронизатора 19 на вход начальной установки RS-триггера 27, который сраба- 25 соответствии с выражением тывает, закрывая элемент И 2В, а через элемент ИЛИ 23 подается на входы j обнуления входного регистра 1, преобразователя 2 код - частота и счетчика 3.

Одновременно импульс 1 поступает на третий вход формирователя 14 адреса для установки начального кода

Y

(.j

,j }

30

где

О или 1, соответствующие положительному или отрицательному знаку входных отсчетов Sgn функция, считывается с блока В памяти. Б начале процедуры считывания кодов на третий вход формирователя 14 адреса поступает с К-го входа регистра 4 сдвига импульс, осуществляющий установку первого граничного условия: по импульсу, поступающему на вход S, RS-триггер 30 срабатывает, открывая элемент И группы элементов 2И-ЙЛИ 32, через который на В входы сумматоров

35

Ад N/4, а на второй (тактовый) вход начинают поступать тактовые импульсы с выхода элемента И 29. Тактовые импульсы также поступают через элемент ИЛИ 10 на счетный вХод счетчика 11, формируя текущие адреса А , подключенные через элемент И 13 к входу демультиплексора 17. Таким образом, одновременно с формированием кодов адресов А„;, осуществляющих считывание произведений б с К выходов бло0

О или 1, соответствующие положительному или отрицательному знаку входных отсчетов Sgn функция, считывается с блока В памяти. Б начале процедуры считывания кодов на третий вход формирователя 14 адреса поступает с К-го входа регистра 4 сдвига импульс, осуществляющий установку первого граничного условия: по импульсу, поступающему на вход S, RS-триггер 30 срабатывает, открывая элемент И группы элементов 2И-ЙЛИ 32, через который на В входы сумматоров

оп 38 и 39 подключается код А- К N/4,

ка 8 памяти через мультиплексор 9 на „ о

«„„,„ ле. „„„„.„ л,„„„„ который записывается в накапливающий

сумматор 39, а через время, заданное

вход блока 16, производится формирование кодов адресов Ар, осуществляю- 1ЦИХ распределение результатов усреднений для записи в блок регистров 1В.

элементом 35 задержки,.зтот импульс поступает на тактовый вход сумматора

Так как для вычисления спектра „ 8, осуществляя запись в него ко па А Фурье необходимо определять действи- о

тельную (ReS) и мнимую ) состав- Поступающие на вход 2 формирова- ляющие, т.е. осуществлять cos-преоб- теля 14 адреса т.ктовые импульсы по- разование Фурье и sin-преобразование даются на тактовый вход накапливаю- фурье, то в блок регистров 18 из щего сумматора 37 и через элемент 42 ка В памяти произведений коды необходимо считывать в определенной пос- ледоватепьности: для определения

задержки - на тактовый вход суммато- ра-вычитателя 40: в накапливающий сумматор 37 при каждом такте считываются кода: m Д А 1 с выхода счетчиI S считываются коды где i

О,1,2,.,.,К,.,.,1,0,1,... в течение i N тактов, а для ReS - коды , где j (к-i), т.е. считываются коды из ячеек К, (К-1), (К-2),..., 5 1,0,1,...,(К-1),К,... блока 8 памяти. Следовательно, на вход блока 16 считываются коды произведения .С,; X,- sin 27 f (i & () или произведения C,,j x;.cos 2 |Г f (j.u€:).

Процедура опроса содержимого блока В памяти и записи результата усреднения в блоке регистров 1В выполняется, например, при определении ReS, следующим образом.

Прр обработке первого отсчета сигнала Х формирователь 14 адреса (фиг.2) осуществляет формирование кодов А „,; с шагом л А m 1, а граничШ

15

ные условия (фиг.4) для изменения 0 знака sig 6rnj в блоке 16 задаются изменением кода в сумматоре 39, подключенному к входу в узла 41 сравнения. При этом в блоке 16 .операции осуще соответствии с

Y

(.j

соответствии с выражением j

где

0

О или 1, соответствующие положительному или отрицательному знаку входных отсчетов Sgn функция, считывается с блока В памяти. Б начале процедуры считывания кодов на третий вход формирователя 14 адреса поступает с К-го входа регистра 4 сдвига импульс, осуществляющий установку первого граничного условия: по импульсу, поступающему на вход S, RS-триггер 30 срабатывает, открывая элемент И группы элементов 2И-ЙЛИ 32, через который на В входы сумматоров

Поступающие на вход 2 формирова- теля 14 адреса т.ктовые импульсы по- даются на тактовый вход накапливаю- щего сумматора 37 и через элемент 42

задержки - на тактовый вход суммато- ра-вычитателя 40: в накапливающий сумматор 37 при каждом такте считываются кода: m Д А 1 с выхода счетчика 36, благодаря чему в накапливающем сумматоре 37 последовательно формируются коды О,1,2,3...,т i, а на выходе сумматора-вычитателя 40 формируется разность

A,j IK - m.il.

Следовательно, поступая на адресный вход мультиплексора 9, этот код осуществляет последовательное считывание информации с ячеек К, (К-1), (К-2),... блока 8 памяти, которая поступает в усреднитель 16 и, по адресам, задаваемым счетчиком 11 на ад ресный вход демультиплексора 17,распределяется в ячейки 1 1,2,...

N

К -т- блока регистров 18. После записи кода в ячейку /4 блока регист- ров 18 в нем оказывается накопленной 1/4 периода функции ReS, 9,; , после чего с выхода узла 41 сравнения на сумматор 15 по модулю два поступает импульс изменения знака ВТО-, рого слагаемого в блоке 16 на sgn -1 (соответствующий отрицательной полуволне косинусной функции,фиг.4). Этот импульс поступает также через элемент ИЛИ 33 на-тактовый вход сумматора 39, разрешая операцию сложения предыдущего содержимого N/4 с кодом N/4 с выхода регистра 31,фо/N N N. мируя новое слагаемое Т Т/ Д-

сумматора-вычитателя 40, После этого импульсы Sig© поступает через элемент 34 задержки () на вход R RS-триггер 30, который срабатывает, открывая . BTopof элемент И элемента 2И-ИЛИ 32, а через элемент 35 задержки () импульс поступает на тактовый вход сумматора 38, в котором формируется

/ N N.

сумма Ст + о- являющаяся новым гра-

ничным условием для устройства 41 сравнения: в течение N/2 тактовых импульсов, поступающих на интервале заN 3N писи кодов в ячейки (т + 1) i и -г4 4

блока регистров 18, в блоке 16 выполняются накопления в соответствии с формулой

ReS ReS.,, - в.

(1)

Следовательно, формирование кодов адресов осуществляется при помощи

накапливающих сумматоров 37 и 39, а результат образуется на выходе сумматора-вычитателя 40 в соответствии с выражением

|N/4-m.il ,,К

N р -у - m-i

рЯ,

(2)

где р О,1,2,3,...2т - номер перехода гармонической функции через нулевой уро- . вень (фиг.4).

Закон изменения знаков в блоке 16 при вычислении описывается соотношениями

предьщущий знак:

{

1 -IxPN N при |m. Р 2

(3)

измененный знак:

т r4czric:nnoiri опсд-хх

.1 . fN . Nl Р 2j.

После i N микрокоманд, поступающих на тактовые входы формирователя 14 адреса и блока 16, в N ячеек 1 1,N блока регистров 18 распределяются через демультиплексор 17 соответствующие коды, считанные из блока 8 памяти.

Так при обработке второго отсчета () входного сигнала по импульсу с первого выхода синхронизатора 19 осуществляется его запись в регистр 1, после чего в преобразователе 2 код - частота начинается формирование потока импульсов частоты F, пропорциональной амплитуде отсчета x(2ut).

Р1мпульс запуска m 2 поступает также на управляющий вход блока 8 памяти (сбрасывая содержимое предьщуще- го цикла в,;) и на вход записи реги- 4 сдвига, после чего в качестве одиночного импульса 1 продвигается в нем тактовыми импульсами в сле- дуюпще разряды.

Аналогично циклу в счетчике 3 поток импульсов частоты F преобразуется в текущие коды 02.i которые через те же интервалы вр емени лС, juC j ..., й с ц (по импульсам с выхода элемента ИЛИ 5) считываются через блок элементов И в соответствующие ячейки

блока 8 памяти (по адресам, поступающим с выхода счетчика 11 через элемент И 12). После К-го импульса с выхода счетчика 3 считывается код б., , который записывается в К-ю ячейку блока памяти, после чего этот импульс через второй вход синхронизатора 19 подается на вход R RS-триггера 27 и через элемент ИЛИ 23 - на входы обнуления регистра 1, преобразователя 2 код - частота и счетчика 3. При этом RS-триггер 27, сработав, закрывает элементы И 7, 12 и 28, открывает элементы И 13 и 29 и сбрасывает в нулевое состояние счетчик 11.

Вследствие этого последующие тактовые импульсы от генератора 20 импульсов поступают через элемент И 29 на вход счетчика 11, коды которого. через элемент И 13 подключаются к адресному входу демультиплек:сора 17, а, поступая на тактовый вход 2 формирователя 14 адреса,эти тактовые импульсы управляют операциями Сложение в накапливающих сумматорах 37- 39 и операцией Вычитание в сумма- торе-вычитателе 40. с:

Так как при этом содержимое счетчика 36 га 2, то по каждому такто- вому импульсу в накапливающем сумматоре 37 формируются коды с шагом ЛА m 2, т.е. коды j 0, 2, 4,..., а на выход сумматора-вычитателя 40 поступает последовательность кодов А„- К, (К-2), (К-4),...,2,0,2,..., которые подаются на адресный вход мультиплексора 9 для считывания соответствующих кодов блока 8 памяти. После усреднения кодов б.о содер- жимым блока регистров 18 ReS g результат распределяется демультиплек- сором 17 в те же 1 1,N ячейки блока регистров 18.

При этом коды BI формируются в соответствии с соотношением (2), а их знаки - в соответствии с соотношением (3). После записи кода в N-ю ячейку блока регистров 18 в счетчике 11 на выходе разряда переполнения формируется импульс переполнения,который подается на вход 2 синхронизатора 19, подготавливая элементы анализатора спектра для обработки следующей выборки .

Таким образом, после m N циклов обработки входного сигнала в выходном блоке 18 памяти накапливается сумма, описываемая выражением

2п Q+pN

ReS., (I-bf) В, Z: ( (f PIO

- ),

где В, - масштабирующий коэффициент, учитывающий шаг дискретизации сигнала.

Следовательно, благодаря опросу блока 8 памяти, содержащего К произведений каждого отсчета сигнала на 1/4 периода sin-функции, достигается вычисление мнимой (, - при опросе i 1,2,... ,К,. .. ,N ячеек блока 8) или действительной (ReSx - при опросе ячеек в последовательности К (К-1),...,1,...) составляющих комплексного спектра Фурье при накапливании результатов в блоке регистров 18.

Формула изобретения

1. Анализатор спектра Фурье,содержащий входной регистр, преобразователь код - частота, два счетчика, формирователь адреса, сумматор по модулю два, мультиплексор, блок усреднения, демультиплексор, блок регистров, регистр сдвига, элемент И, три блока элементов И, первый элемент ИЛИ и синхронизатор, первый выход которого подключен к первому входу формирователя адреса, входу записи сдвига и тактовому входу входного регистра, выход старшего разряда которого подключен к первому входу сумматора по модулю два, выход которого подключен к знаковому-входу блока усреднения, второй выход синхронизатора подключен к установочным входам входного регистра и первого счетчика, третий выход синхронизатора подключен к входу синхронизации блока усреднения и тактовому входу регистра сдвига, четвертый выход синхронизатора подключен к второму входу формирователя адреса, выход которого подключен к управляющему входу мультиплексора, выход регистра является информационным выходом анализатора и подключен к входу первого операнда блока усреднения, а выход старшего разряда формирователя адреса подключен к второму входу сумматора по модулю два, отличающ и и с я TeMj что, с целью упрощения, он содержит блок памяти и второй элемент ИЛИ, выход которого подключен к первым входам первого блока элементов И и элемента И, выходы ко- торых подключены соответственно к информационному входу бло ка памяти и первому входу первого элемента ИЛИ, выход которого подключен к счетному входу второго счетчика, информацион- ный выход которого подключен к первым входам второго и третьего блоков элементов И, выходы которых подключены к адресному входу блока памяти и управляющему входу демультиплексо- ра соответственно,выходы которого подключены к соответствующим информацион- ньм входам блока регистров,выход входного регистра подключен к информационному входу преобразователя код - часто- та,выход которого подключен к счетному входу первого счетчика, информационный выход которого подключен к второму входу первого блока элементов И выходы разрядов блока памяти подклю- чены к соответствующим информационным входам Мультиплексора, выход которого подключен к входу второго операнда блока усреднения, выход которого подключен к информационному входу де- мультиплексора, выход переноса второго счетчика подключен к входу запуска синхронизатора, пятый выход которого подключен к вторым входам элемента И и второго блока элементов И, выходы разрядов регистра сдвига подключены к соответствующим входам второго элемента ИЛИ, шестой выход синхронизатора подключен к второму входу третьего блока элементов И и уста- новочному входу второго счетчика, первый, второй и третий выходы синхронизатора подключены соответственно к управляющему входу блока памяти, установочному входу первого счетчика и второму вхОду первого блока элементов ИЛИ, выход старшего разряда регистра сдвига подключен к установочному входу регистра сдвига, входу останова синхронизатора и к третьему входу формирователя адреса, а информационный вход входного регистра является информационным входом анализатора.

2, Анализатор по п.1, отличающийся TeMj что формирователь адреса содержит счетчик, три накап.;ивающих сумматора, узел сравнения, три элемента задержки, сумма- тор-вычитатель, элемент 2И-ШШ, элемент ШШ, RS-триггер и регистр,выходы первого и второго разрядов ко- торогг подключена соответственно к первому и второму входу элемента 2И-ИЛИ, выход которого подключен к входам первого и второго накапливаю- |ЩИХ сумматоров, выходы которых подключены соответственно к первому входу узла сравнения и первому входу операнда сумматора-вычитателя,второй вход операнда которого соединен с вторым входом узла сравнения и подключен к выходу третьего накапливающего сумматора, информационный вход которого подключен к информационному выходу счетчика, выход первого элемента задержки подключен к входам синхронизации сумматора-вычитателя и узла сравнения, выход которого является выходом старшего разряда формирователя и подключен к входу второго элемента задержки и первому входу

элемента ИЛИ, выход которого подклю- I

чен к входу синхронизации второго накапливающего сумматора и входу третьего элемента задержки, выход которого подключен к входу синхронизации первого накапливающего сумматора, установочный вход которого соединен с установочными входами второго и

третьего накапливающих сумматоров,

I

сумматора-вычитателя, счетным входом

счетчика и является первым входом формирователя, вторым входом которого являются соединенные между собой вход синхронизации третьего накапливающего сумматора и вход первого элемента задержки, третий и четверJ

тый входы элемента 2И-ИЛИ подключены соответственно к прямому и инверсному выходам RS-Tprfrrepa, R-вход которого подключен к выходу второго элемента задержки, а S-вход RS-триггера соединен с вторым входом элемента ИЛИ и является третьим входом формирователя, выходом которого является выход сумматора-вычитателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ранговый обнаружитель сигналов | 1981 |

|

SU970291A1 |

| Цифровой формирователь спектра | 1984 |

|

SU1171804A1 |

| Анализатор спектра Фурье | 1987 |

|

SU1387010A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| Цифровой многофазный генератор | 1990 |

|

SU1750032A1 |

| Устройство для преобразования Фурье | 1984 |

|

SU1195358A1 |

| Коррелометр | 1989 |

|

SU1644159A1 |

| СИСТЕМА НАВИГАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 1992 |

|

RU2022356C1 |

Изобретение относится к специализированным .средствам вычислительной техники, предназначенным для определения спектральных свойств смежных сигналов в задачах идентификации объектов. Цель изобретения - упрощение устройства. Поставленная цель достигается за счет того, что анализатор содержит входной регистр, преобразователь код - частота, счетчик, регистр сдвига, первый элемент ИЛИ, три блока злементов И, элемент И, блок памяти, мультиплексор, второй элемент ИЛИ, счетчик, блоки элементов И, формирователь адреса, сумматор по модулю два, блок усреднения, демульти- плексор, блок регистров и синхронизатор. 1 з.п. ф-лы, 4 ил. (Л С

e«

:a (риг. 2

. , Bifxodt,/ Р..-4,. , г

xj, Hodti Cm

fill

ji

лТ РГ

(Риг.З

Редактор И. Дербак

Составитель А. Баранов

Техред А.Кравчук Корректор А. Зимокосов

Заказ 1218/49 Тираж 673 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

Р- О

Р--1

}

llh .

-/f

Ut

21

/

/

/

fPu2.4

| Дискретно-аналоговый фурье-преоб-РАзОВАТЕль | 1979 |

|

SU813307A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой Фурье-преобразователь | 1982 |

|

SU1043663A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-07—Публикация

1985-11-10—Подача