Изобретение относится к нелинейным корректирующим устройствам, компенсирующих влияние ограничения, и может быть использовано в системах автоматического управления с исполнительным механизмом (приводом), имеющим ограничение, например, в системах управления подвижными объектами.

Цель изобретения - расширение функциональных возможностей за счет yae личения диапазона компенсации помех входного сигнала.

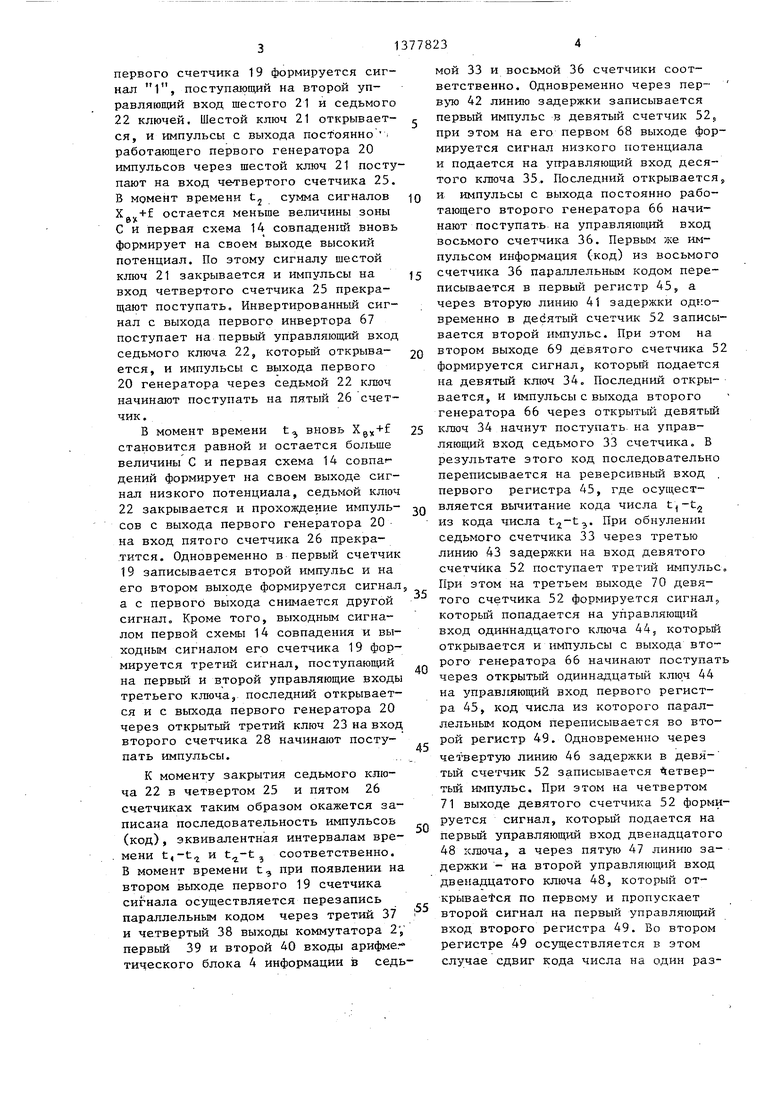

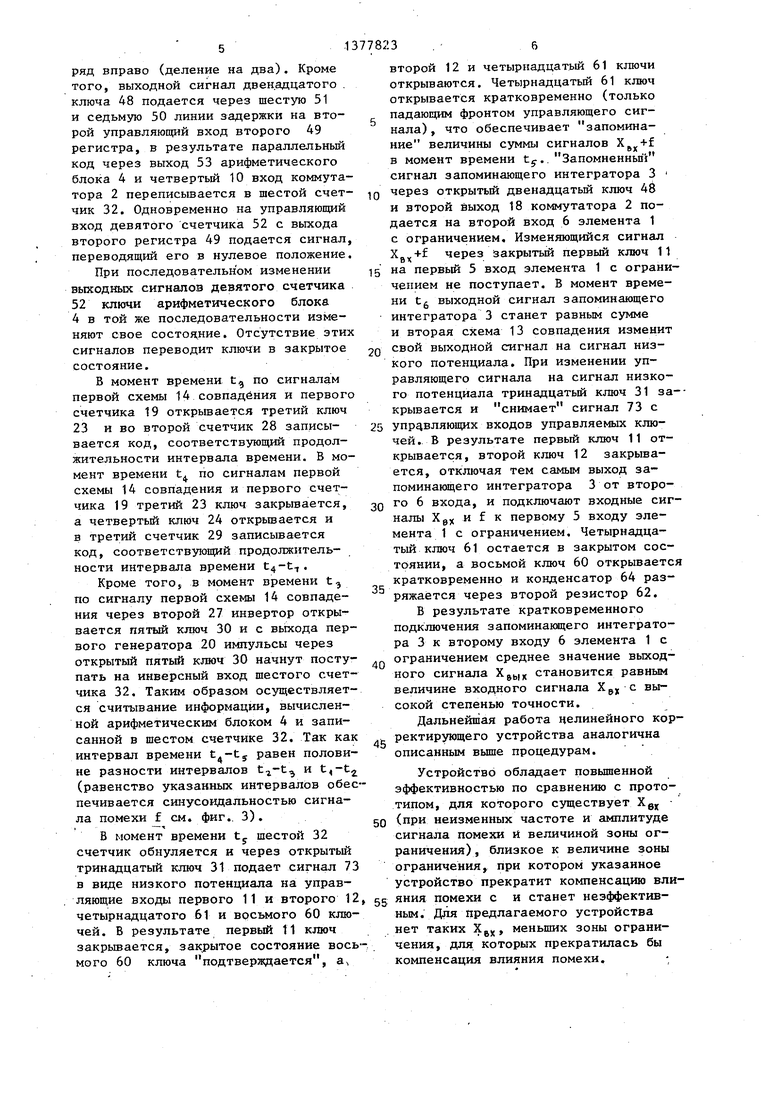

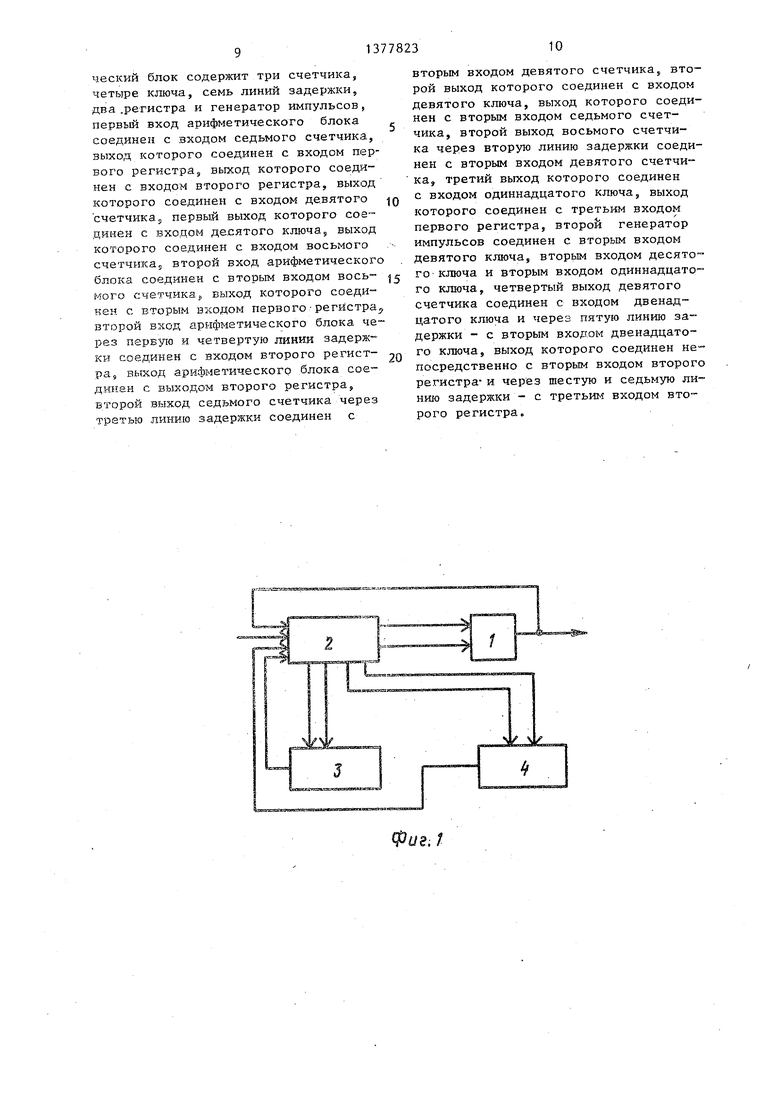

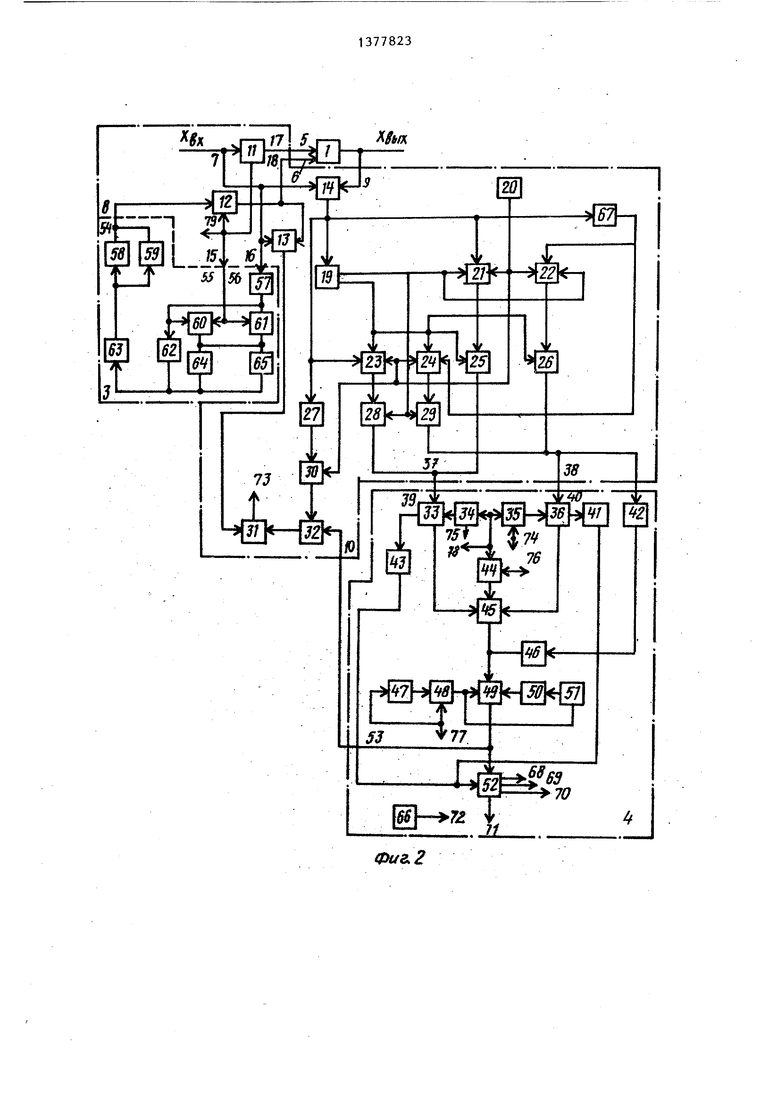

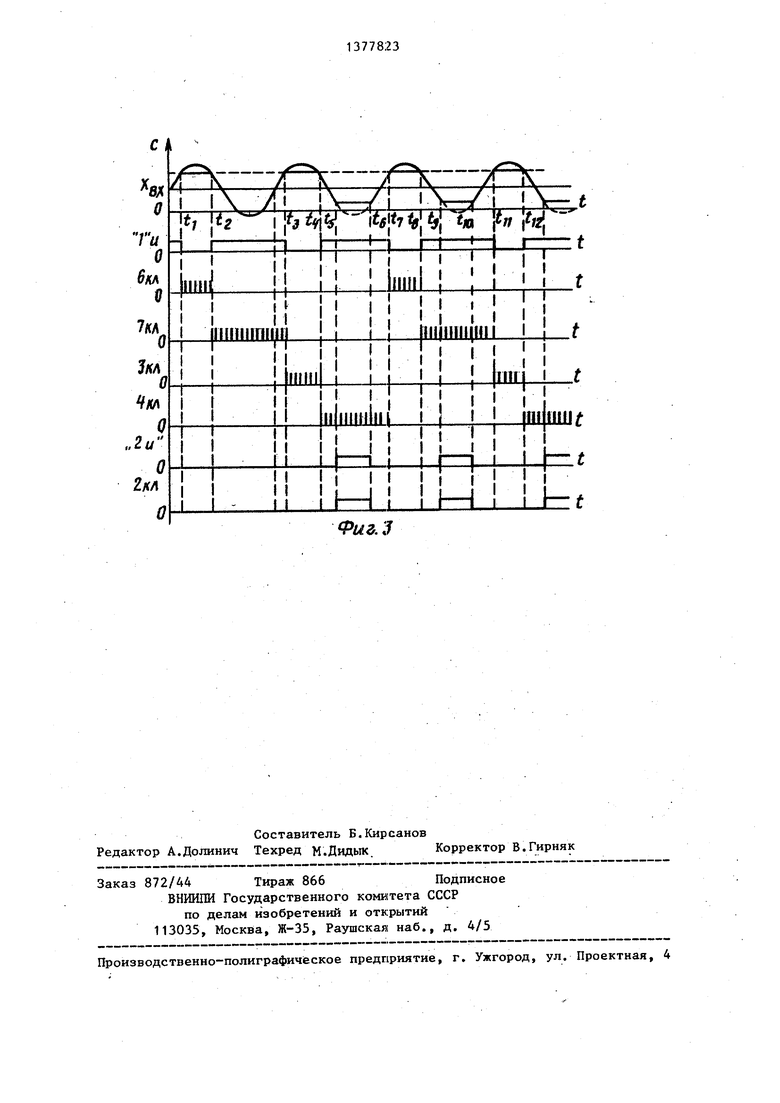

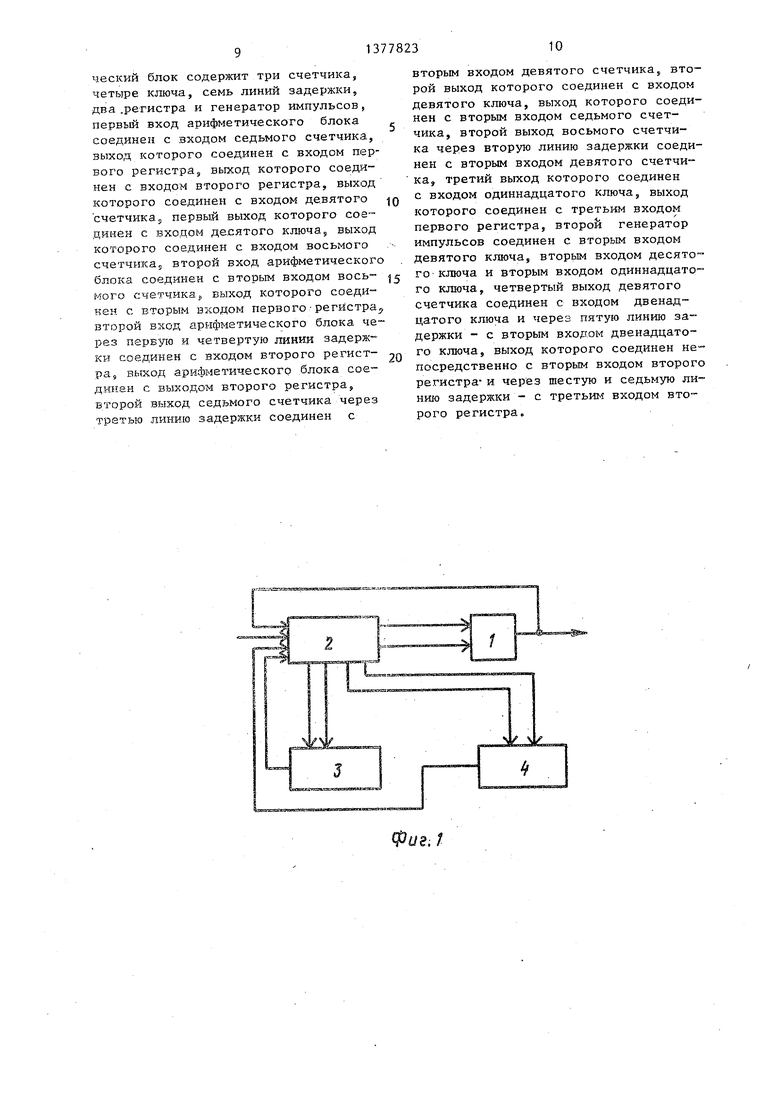

На фиг. 1 представлена функциональная схема устройства; на фиг.2 - блок-схема устройства-, на фиг.З - временная диаграмма.

Нелинейное корректирующее устройство (фиг. 1 и 2) содержит элемент 1 с ограничением, коммутатор 2, интегратор 3 и арифметический блок 4, первый 5 и второй 6 входы элемента 1 с ограничением, первый вход 7 коммутатора 2, второй 8 вход коммутатора 2, третий 9 вход коммутатора 2, четвертый 10 вход коммутатора, первый 11 ключ, второй 12 ключ, вторая 13 и первая 14 схемы совпадения, шестой 15 и пятый 16 выходы коммутатора, первый 17 и второй 18 выходы коммутатора 2, первьш счетчик 19, первый

генератор 20 импульсов, шестой 21, седьмой 22, третий 23 и четвертый 24 ключи, четвертый 25 и пятый 26 счет-- чики, второй 27 инвертор, -второй 28 и третий 29 счетчики, пятый 30 и три надцатый 31 ключи, щестой 32 и седьмой 33 счетчики, девятый 34 и десятый 35 ключи, восьмой 36 счетчик, третий 37 и четвертый 38 выходы коммутатора 2, первый 39 и второй 40 входы арифметического блока 4, вторая 41 и первая 42 и третья 43 линии задержки, одиннадцатый 44 ключ, первьш 45 регистр, четвертая 46 и пятая 47 линии задержки, двенадцатый 48 ключ, второй 49 регистр, /седьмая 50 и щестая 51 линии задержки, девятый 52 счетчик, выход 53 арифметического блока 4, выход 54 интегратора 3, пер вый 55 и второй 56 входы интегратора 3, первый 57 резистор, второй 58 усилитель постоянного тока, четвертый 59 резистор, восьмой 60 и четырнадцатый 61 ключи, второй 62 резистор, третий 63 резистор, конденсатор 64, первый 65 усилитель постоянного тока, второй 66 генератор импульсов, первый 67 инвертор, первый 68, второй 695 третий 70 и четвертый

71 выходы, выход 72 второго 66 генератора импульсов, выход .73 тринадцатого 31 ключа, первый 74 вход де5 сятого 35 ключа, первьй 75 вход девятого 34 ключа, первый 76 вход одиннадцатого 44 ключа, первый 77 вход двенадцатого 48 ключа, второй 78 вход одиннадцатого ключа и второй 79 вход

Ш первого 11 ключа.

Одиннадцатый ключ 44 представляет собой стандартный электронный ключ. Вторая схема 13 совпадения является логическим элементом И.

15 Первый счетчик 19 реализован в виде суммирующего двухразрядного счетчика. Первьй генератор 20 импульсов реализован в виде мультивибратора с коллектором - базовой

20 связью. Вторая-линия 41 задержки является формирователем задержанных импульсов. Первый регистр 45 представляет собой реверсивный счетчик. Нелинейное корректирующее устрой25 ство работает следующим образом.

В исходном положении первый ключ 11 открыт, второй 12, четвертый 24, пятый 30, седьмой 22, девятый 34, одиннадцатый 44, восьмой 60 ключи

30 закрыты, все счетчики находятся в нулевом состоянии (во всех разрядах записаны О), все регистры - в нулевом состоянии (во всех разрядах записаны О), все регистры - в нулевом состоянии, конденсатор 64 раз35

ряжен.

Через первый 7 вход коммутатора 2 первый ключ 11 и первый выход 17 коммутатора 2 входной сигнал Xj

вместе с сигналом помехи (фиг. 2) поступает на первый вход 5 элемента 1 с ограничением, а также на первый управляющий вход первой схемы 14 совпадения и через пятый выход 16

коммутатора 2 на второй вход 56 запоминающего интегратора 3. Выходной сигнал Х, ., элемента 1 с ограниче л

нием через третий 9 вход коммутатора 2 поступает на второй управляющий

вход первой схемы 14 совпадений. В момент времени t, сумма сигналов Xgj+f становится равна, а затем больше значения зоны С (см. фиг. 3) и первая схема 14 совпадения скачком

уменьщает потенциал на своем выходе до нуля. По этому сигналу в первый счетчик 19 записывается первый импульс, а щестой 21 ключ готовится

открыться. При этом на первом выходе

первого счетчика 19 формируется сигнал 1, поступающий на второй управляющий вход шестого 21 и седьмого 22 ключей. Шестой ключ 21 открывается, и импульсы с выхода постоянно i работающего первого генератора 20 импульсов через шестой ключ 21 поступают на вход четвертого счетчика 25. В момент времени t сумма сигналов X,.,+f остается меньше величины зоны

В Л

С и первая схема 14 совпадений вновь формирует на своем выходе высокий потенциал. По этому сигналу шестой ключ 21 закрывается и импульсы на вход четвертого счетчика 25 прекращают поступать. Инвертированный сигнал с выхода первого инвертора 67 поступает на первый управляющий вход седьмого ключа 22, которьй открывается, и импульсы с выхода первого 20 генератора через седьмой 22 ключ начинают поступать на пятый 26 счетчик.

В момент времени t вновь становится равной и остается больше величины С и первая схема 14 совпа - дений формирует на своем выходе сигнал низкого потенциала, седьмой ключ 22 закрывается и прохождение импульсов с выхода первого генератора 20 на вход пятого счетчика 26 прекратится. Одновременно в первый счетчик 19 записывается второй импульс и на его втором выходе формируется сигнал а с первого выхода снимается другой сигнал. Кроме того, выходным сигналом первой схемы 14 совпадения и выходным сигналом его счетчика 19 формируется третий сигнал, поступающий на первый и второй управляющие входы третьего ключа, последний открывается и с выхода первого генератора 20 через открытый третий ключ 23 на вход второго счетчика 28 начинают поступать импульсы.

К моменту закрытия седьмого ключа 22 в четвертом 25 и пятом 26 счетчиках таким образом окажется записана последовательность импульсов (код), эквивалентная интервалам времени и соответственно. В момент времени t при появлении на втором выходе первого 19 счетчика сигнала осуществляется перезапись параллельным кодом через третий 37 и четвертый 38 выходы коммутатора 2, первый 39 и второй 40 входы арифме. тического блока 4 информации в седь

5

0

5

0

5

0

5

0

5

мой 33 и восьмой 36 счетчики соответственно. Одновременно через пер- вую 42 линию задержки записывается первый импульс в девятый счетчик 52 при этом на его первом 68 выходе формируется сигнал низкого потенциала и подается на управляющий вход десятого ключа 35. Последний открывается, и импульсы с выхода постоянно работающего второго генератора 66 начинают поступать на управляющий вход восьмого счетчика 36. Первым же импульсом информация (код) из восьмого счетчика 36 параллельным кодом переписывается в первый регистр 45, а через вторую линию 41 задержки одновременно в деёятый счетчик 52 записывается второй импульс. При этом на втором выходе 69 девятого счетчика 52 формируется сигнал, который подается на девятый ключ 34, Последний открывается, и импульсы с выхода второго генератора 66 через открытый девятый ключ 34 начнут поступать на управ- ляюш;ий вход седьмого 33 счетчика. В результате этого код последовательно переписывается на реверсивный вход первого регистра 45, где осуществляется вычитание кода числа t,-t из кода числа . При обнулении седьмого счетчика 33 через третью линию 43 задержки на вход девятого счетчика 52 поступает третий импульс. При этом на третьем выходе 70 девятого счетчика 52 формируется сигнал, который попадается на управляющий вход одиннадцатого ключа 44, которьй открывается и импульсы с выхода второго генератора 66 начинают поступать через открытьй одиннадцатый ключ 44 на управляющий вход первого регистра 45, код числа из которого параллельным кодом переписывается во второй регистр 49. Одновременно через четвертую линию 46 задержки в девя- тый счетчик 52 записывается йетвер- тьй импульс. При этом на четвертом 71 выходе девятого счетчшса 52 формируется сигнал, которьй Подается на первьй управляющий вход двенадцатого 48 ключа, а через пятую 47 линию задержки - на второй управляющий вход двенадцатого ключа 48, который от- крывае ся по первому и пропускает второй сигнал на первый управляющий вход второго регистра 49. Во втором регистре 49 осуществляется в этом случае сдвиг кода числа на один разряд вправо (деление на два). Кроме того, выходной сигнал двен.адцатого . ключа 48 подается через шестую 51 и седьмую 50 линии задержки на второй управляющий вход второго 49 регистра, в результате параллельный код через выход 53 арифметического блока 4 и четвертый 10 вход коммутатора 2 переписывается в шестой счетчик 32. Одновременно на управляющий вход девятого счетчика 52 с вьпсода второго регистра 49 подается сигнал, переводящий его в нулевое положение.

При последовательном изменении выходных сигналов девятого счетчика 52 ключи арифметического блока 4 в той же последовательности изменяют свое состояние. Отсутствие этих сигналов переводит ключи в закрытое состояние.

В момент времени t по сигналам первой схемы 14 совпадения и первого счетчика 19 открывается третий ключ 23 и во второй счетчик 28 записывается код, соответствующий продолжительности интервала времени. В момент времени t по сигналам первой схемы 14 совпадения и первого счетчика 19 третий 23 ключ закрьшается, а четвертый ключ 24 открьшается и а третий счетчик 29 записывается код, соответствующий продолжительности интервала времени t4-t,.

Кроме того, в момент времени t по сигналу первой схемы 14 совпадения через второй 27 инвертор открывается пятый ключ 30 и с выхода первого генератора 20 импульсы через открытый пятый ключ 30 начнут поступать на инверсный вход шестого счетчика 32. Таким образом осуществляется считывание информации, вычисленной арифметическим блоком 4 и записанной в шестом счетчике 32. Так как интервал времени t.-ty равен половине разности интервалов и (равенство указанных интервалов обеспечивается сш усоидальностью сигнала помехи f см. фиг.. 3).

I -- д

В момент времени t шестой 32 счетчик обнуляется и через открытый тринадцатый ключ 31 подает сигнал 73 в виде низкого потенциала на управ0

5

0

5

0

второй 12 и четырнадцатый 61 ключи открываются. Четырнадцатый 61 ключ открывается кратковременно (только падающим фронтом управляющего сигнала) , что обеспечивает запоминание величины суммы сигналов в момент времени ty.. Запомненньп сигнал запоминающего интегратора 3 через открытый двенадцатый ключ 4Й и второй выход 18 коммутатора 2 подается на второй вход 6 элемента 1 с ограничением. Изменяющийся сигнал через закрытый первый ключ 11 на первый 5 вход элемента 1 с ограничением не поступает. В момент времени t выходной сигнал запоминающего интегратора 3 станет равным сумме и вторая схема 13 совпадения изменит свой выходной сигнал на сигнал низкого потенциала. При изменении управляющего сигнала на сигнал низкого потенциала тринадцатый ключ 31 за-- крывается и снимает сигнал 73 с управляющих входов управляемых ключей. В результате первый ключ 11 открывается, второй ключ 12 закрывается, отключая тем самым выход запоминающего интегратора 3 от второго 6 входа, и подключают входные сиг5

0

5

0

налы Xgx и f к первому 5 входу элемента 1 с ограничением. Четырнадцатый ключ 61 остается в закрытом состоянии, а восьмой ключ 60 открывается кратковременно и конденсатор 64 разряжается через второй резистор 62.

В результате кратковременного подключения запоминакмцего интегратора 3 к второму входу 6 элемента 1 с ограничением среднее значение выходного сигнала становится равным величине входного сигнала Х, с высокой степенью точности.

Дальнейшая работа нелинейного корректирующего устройства аналогична описанным выше процедурам.

Устройство обладает повышенной эффективностью по сравнению с прототипом, для которого существует Xg (при неизменных частоте и амплитуде сигнала помехи и величиной зоны ограничения) , близкое к величине зоны ограничения, при котором указанное устройство прекратит компенсацию вли

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель временных интервалов | 1982 |

|

SU1034012A1 |

| Устройство для сбора и обработки информации при голосовании | 1983 |

|

SU1117649A2 |

| Генератор псевдослучайных процессов | 1984 |

|

SU1261087A1 |

| СПОСОБ УПРАВЛЕНИЯ ХАРАКТЕРИСТИКАМИ ПОЛЯ ПОРАЖЕНИЯ ОСКОЛОЧНО-ФУГАСНОЙ БОЕВОЙ ЧАСТИ РАКЕТЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2011 |

|

RU2484419C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧ НЕЛИНЕЙНОГО СТОХАСТИЧЕСКОГО ПРОГРАММИРОВАНИЯ | 1991 |

|

RU2006933C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 1999 |

|

RU2168763C2 |

| Устройство для формирования признаков распознаваемых образов | 1986 |

|

SU1328830A1 |

| Устройство для вычисления полинома | 1980 |

|

SU885997A1 |

| Устройство для измерения и контроля технологических параметров | 1983 |

|

SU1136116A1 |

| Радиоприемное устройство с компенсацией фазового сдвига | 1984 |

|

SU1166319A1 |

Изобретение относится к нелинейным корректирующим устройствам, компенсирующим влияние ограничения, и может быть использовано в системах автоматического управления с исполнительным механизмом (приводом),имеющим ограничение, например в системах управления подвижными объектами.Целью изобретения является расширение функциональных возможностей за счет увеличения диапазона компенсации помех входного сигнала. Устройство содержит элемент с ограничением, коммутатор, интегратор и арифметический . блок. Сущность изобретения заключается в повышении величины входного сигнала, который может без искажения передраться на выход элемента с ограничением за счет удачно выбранной логики функционирования корректирующего устройства. 3 ил. 3 3.п. ф-лы, о сл

ляющие входы первого 11 и второго 12, gg яния помехи с и станет неэффективным. Для предлагаемого устройства нет таких Х, меньших зоны ограничения, для которых прекратилась бы компенсация влияния помехи.

четырнадцатого 61 и восьмого 60 ключей. В результате первый 11 ключ закрывается, закрытое состояние вось-, мого 60 ключа подтверждается, a

Формула изобретения

и интегратор, выход которого соединен с вторым вхбдом коммутатора, третий вход которого соединен с выходом элемента с ограничением и является выходом устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет увеличения диапазона компенса- ции помех входного сигнала, дополнительно введен арифметический блок, выход которого соединен с четвертым входом коммутатора, первый и второй выходы которого соединены с соответствующими входами элемента с ограничением, третий и четвертый выходы коммутатора соединены соответственно с первым и вторым входами арифметического блока, а пятый и шестой выходы коммутатора соединены соответственно с вторым и первьм входами интегратора.

и соединен с вторым входом второго ключа и вторым входом первого кшоча, третий вход коммутатора соединен с вторым входом первой схемы совпадения, выход которой соединен с входами второго инвертора третьего ключа, Jпервого счетчика, шестого ключа и первого инвертора, выход которого (Соединен с входом седьмого ключа и входом четвертого ключа, выход которого соединен с входом третьего счетчика, выход которого соединен.с четвертым выходом коммутатора, выход второго инвертора соединен с входом

0

5

пятого ключа, выход которого соединен с входом шестого счетчика, выход которого соединен с входом тринадцатого ключа, второй вход которого .соединен с выходом второй схемы совпадения, второй вход шестого счетчика соединен.с четвертым входом коммутатора, первый выход первого счетчика соединен с первым входом второго счетчика, вторым входом третьего счетчика, вторым входом шестого ключа и вторым входом седьмого ключа, первый генератор импульсов

5 соединен с третьим входом шестого ключа, третьим входом седьмого ключа, вторым входом третьего ключа, вторым входом четвертого ключа и вторым входом пятого ключа, второй выход первого счетчика соединен с третьим входом третьего ключа, третьим . входом четвертого ключа, первым входом четвертого счетчика и первым входом пятого счетчика, выход которого соединен с четвертым выходом коммутатора, выход седьмого ключа соединен с вторым входом пятого счетчика, выход второго счетчика соеди- . нен с третьим выходом коммутатора, который соединен с выходом четвертого счетчика.

с входом первого усилителя постоянного тока и через конденсатор соединен с выходом первого усилителя постоянного тока, выход которого в свою 5 очередь соединен с общей точкой второго и третьего резисторов.

5

0

5

0

чающееся

тем, что арифметический блок содержит три счетчика, четыре ключа, семь линий задержки, два .регистра и генератор импульсов, первый вход арифметического блока соединен с входом седьмого счетчика, выход которого соединен с входом первого регистраэ выход которого соединен с входом второго регистра, выход которого соединен с входом девятого счетчикаJ первый выход которого соединен с входом десятого ключаj выход которого соединен с входом восьмого счетчика, второй вход арифметического блока соединен с вторым входом вось- мого счетчикаS выход которого соединен с вторым входом первого регистра, второй вход арифметического блока через первую и четвертую линии задержки соединен с входом второго регнет- pa, выход арифметического блока соединен с выходом второго регистра, второй седьмого счетчика через третью линию задержки соединен с

вторым входом девятого счетчикаj второй выход которого соединен с входом девятого ключа, выход которого соединен с вторым входом седьмого счетчика, второй выход восьмого счетчика через вторую линию задержки соединен с вторьм входом девятого счетчика, третий выход которого соединен с входом одиннадцатого ключа, выход которого соединен с третьим входом первого регистра, второй генератор импульсов соединен с вторым входом девятого ключа, вторьм входом десятого ключа и вторым входом одиннадцатого ключа, четвертый выход девятого счетчика соединен с входом двенадцатого ключа и через пятую линию задержки - с вторым входом двенадцатого ключа, выход которого соединен непосредственно с вторым входом второго регистра- и через шестую и седьмую линию задержки - с третьим входом второго регистра.

Г м

Фиг. 2

Риг. 3

| Авторское свидетельство СССР № 599625, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Авторское свидетельство СССР 1025250, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-02-28—Публикация

1986-05-08—Подача