Изобретение относится к автомати- ,ке и вычислительной технике и может быть использовано для обработки изображений.

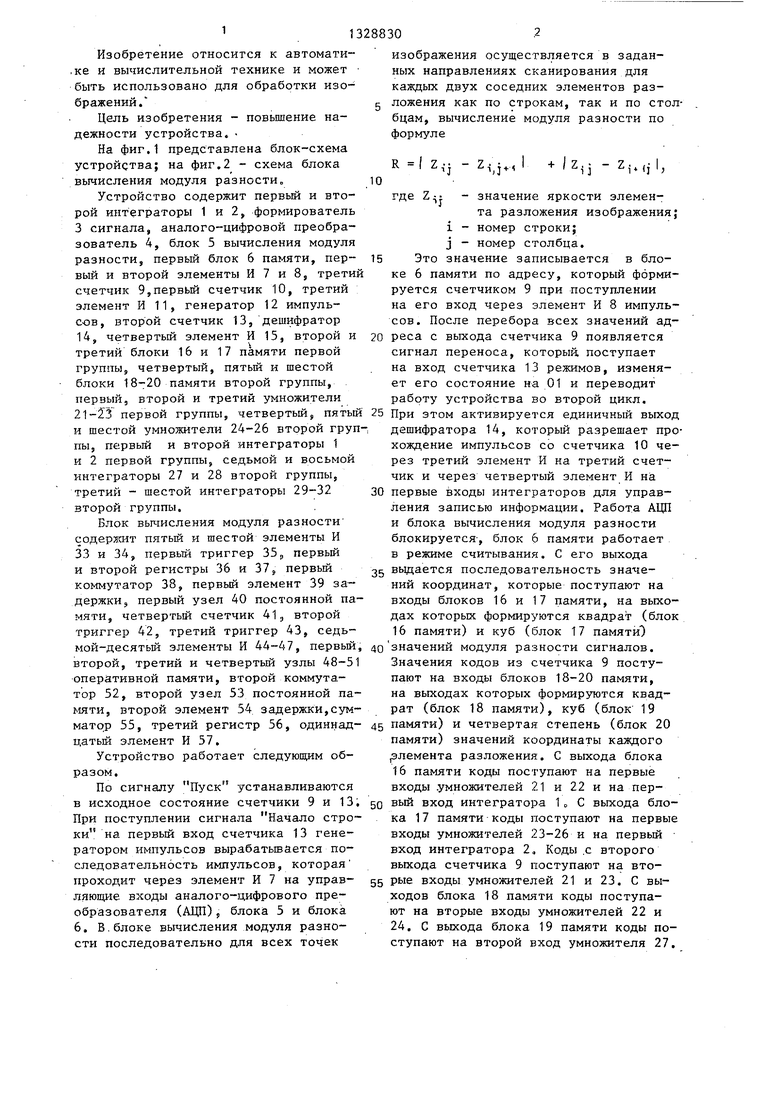

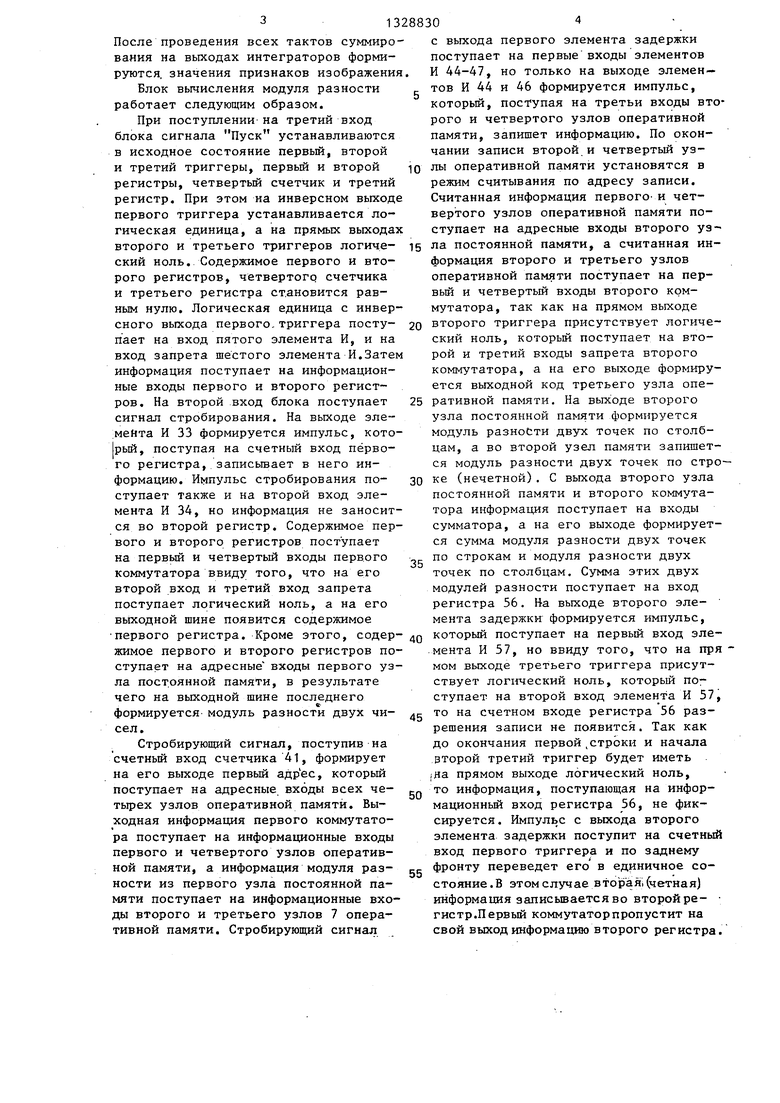

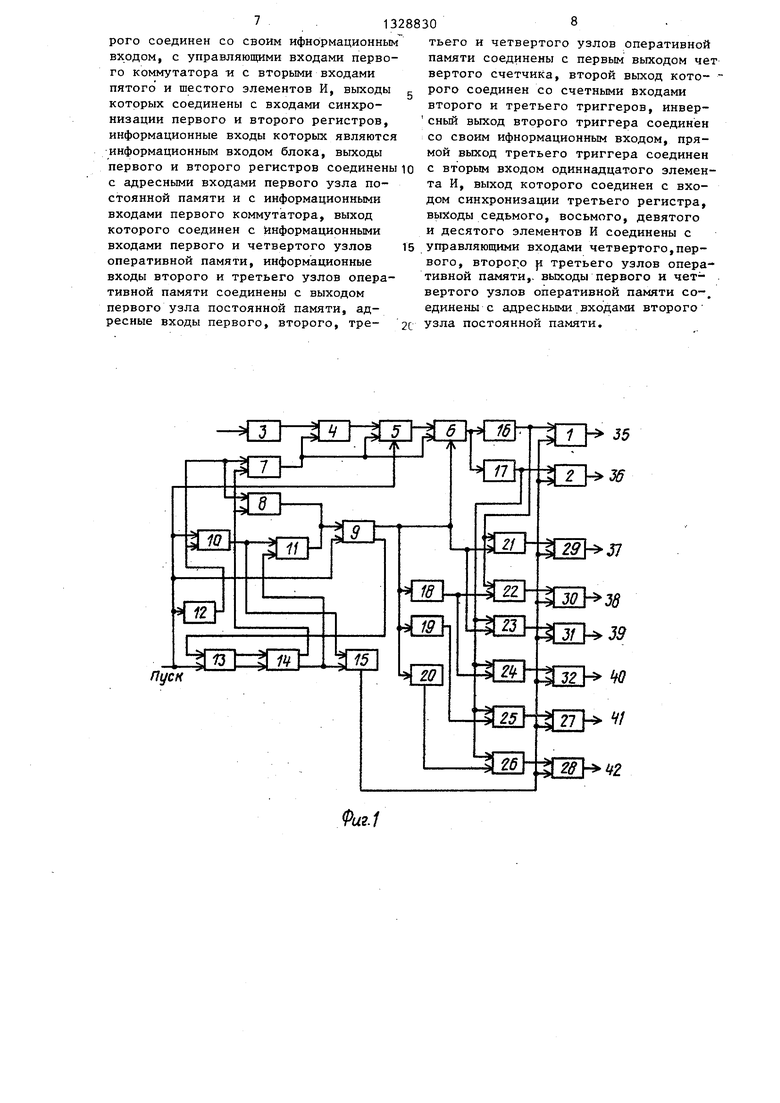

Цель изобретения - повышение надежности устройства. На фиг.1 представлена блок-схема устройства; на фиг.2 - схема блока вычисления модуля разности

Устройство содержит первьш и второй интеграторы 1 и 2, формирователь 3 сигнала, аналого-цифровой преобразователь 4, блок 5 вычисления модуля разности, первый блок 6 памяти, первый и второй элементы И 7 и 8, третий счетчик 9,первый счетчик 10, третий элемент И 11, генератор 12 импульсов, второй счетчик 13, дешифратор

изображения осуществляется в заданных направлениях сканирования для каждых двух соседних элементов раз- g ложения как по строкам, так и по столбцам, вычисление модуля разности по формуле

R

10

М где Z.

- м

+ 1

ii i (j J

15

- значение яркости элемента разложения изображения; i - номер строки; j - номер столбца. Это значение записывается в блоке 6 памяти по адресу, который формируется счетчиком 9 при поступлении на его вход через элемент И 8 импульсов. После перебора всех значений ад14, четвертый элемент И 15, второй и 20 реса с выхода счетчика 9 появляется

V

третий блоки 16 и 17 памяти первой группы, четвертый, пятьш и шестой блоки 18-20 памяти второй группы, первый, второй и третий умножители

сигнал переноса, который, поступает на вход счетчика 13 режимов, изменяет его состояние на 01 и переводит работу устройства во второй цикл.

21-23 первой группы, четвертый, пятый 25 При этом активируется единичный выход и шестой умножители 24-26 второй груп-, дешифратора 14, который разрешает пропы, первый и второй интеграторы 1 и 2 первой группы, седьмой и восьмой интеграторы 27 и 28 второй группы, третий - шестой интеграторы 29-32 второй группы.

Блок вычисления модуля разности содержит пятый и шестой элементы И 33 и 34, первьтй триггер 35 р первый и второй регистры 36 и 37, первый коммутатор 38, первьш элемент 39 задержки, первый узел 40 постоянной памяти, четвертьш счетчик 41, второй триггер 42, третий триггер 43, седьхождение импульсов со счетчика 10 через третий элемент И на третий счетчик и через четвертый элемент И на

30 первые входы интеграторов для управления записью информации. Работа АЦП и блока вычисления модуля разности блокируется-, блок 6 памяти работает в режиме считывания. С его выхода

35 выдается последовательность значений координат, которые поступают на входы блоков 16 и 17 памяти, на выходах которых формируются квадрат (блок 16 памяти) и куб (блок 17 памятиО

мой-десятьй элементы И 44-47, первьй, 40 значений модуля разности сигналов, второй, третий и четвертый узлы 48-51 Значения кодов из счетчика 9 посту- оперативной памяти, второй коммутатор 52, второй узел 53 постоянной папают на входы блоков 18-20 памяти, на выходах которых формируются квадрат (блок 18 памяти), куб (блок 19

мяти, второй элемент 54 задержки,сумпают на входы блоков 18-20 памяти, на выходах которых формируются квадрат (блок 18 памяти), куб (блок 19

матор 55, третий регистр 56, одиннад- 45 памяти) и четвертая степень (блок 20

памяти) значений координаты каждого лемента разложения. С выхода блока 16 памяти коды поступают на первые входы умножителей 21 и 22 и на перцатьш элемент И 57.

Устройство работает следующим образом.

По сигналу Пуск устанавливаются в исходное состояние счетчики 9 и 13. 50 вый вход интегратора 1„ С выхода бло- При поступлении сигнала Начало стро- ка 17 памяти коды поступают на первые

памяти) значений координаты каждого лемента разложения. С выхода блока 16 памяти коды поступают на первые входы умножителей 21 и 22 и на перки на первый вход счетчика 13 генератором импульсов вырабатьшается последовательность импульсов, которая проходит через элемент И 7 на управляющие входы аналого-цифрового преобразователя (АЦП) f блок;а 5 и блока 6. В.блоке вычисления модуля разности последовательно для всех точек

изображения осуществляется в заданных направлениях сканирования для каждых двух соседних элементов раз- ложения как по строкам, так и по столбцам, вычисление модуля разности по формуле

R

М где Z.

- м

+ 1

ii i (j J

- значение яркости элемента разложения изображения; i - номер строки; j - номер столбца. Это значение записывается в блоке 6 памяти по адресу, который формируется счетчиком 9 при поступлении на его вход через элемент И 8 импульсов. После перебора всех значений адсигнал переноса, который, поступает на вход счетчика 13 режимов, изменяет его состояние на 01 и переводит работу устройства во второй цикл.

хождение импульсов со счетчика 10 через третий элемент И на третий счетчик и через четвертый элемент И на

30 первые входы интеграторов для управления записью информации. Работа АЦП и блока вычисления модуля разности блокируется-, блок 6 памяти работает в режиме считывания. С его выхода

35 выдается последовательность значений координат, которые поступают на входы блоков 16 и 17 памяти, на выходах которых формируются квадрат (блок 16 памяти) и куб (блок 17 памятиО

значений модуля разности сигналов, Значения кодов из счетчика 9 посту-

пают на входы блоков 18-20 памяти, на выходах которых формируются квадрат (блок 18 памяти), куб (блок 19

вый вход интегратора 1„ С выхода бло ка 17 памяти коды поступают на первы

памяти) значений координаты каждого лемента разложения. С выхода блока 16 памяти коды поступают на первые входы умножителей 21 и 22 и на первходы умножителей 23-26 и на первый вход интегратора 2, Коды .с второго выхода счетчика 9 поступают на вто- 55 рые входы умножителей 21 и 23. С выходов блока 18 памяти коды поступают на вторые входы умножителей 22 и 24. С выхода блока 19 памяти коды поступают на второй вход умножителя 27.

После проведения всех тактов суммирования на выходах интеграторов формируются, значения признаков изображени

Блок вычисления модуля разности работает следующим образом.

При поступлении на третий вход блока сигнала Пуск устанавливаются в исходное состояние первый, второй и третий триггеры, первьш и второй регистры, четвертый счетчик и третий регистр. При этом на инверсном выход первого триггера устанавливается логическая единица, а на прямых выходах второго и третьего триггеров логиче- ский ноль. Содержимое первого и второго регистров, четвертого счетчика и третьего регистра становится рав- ньм нулю. Логическая единица с инверсного выхода первого.триггера посту- пает на вход пятого элемента И, и на вход запрета шестого элемента И.Затем информация поступает на информационные входы первого и второго регистров. На второй вход блока поступает сигнал стробирования. На выходе эле- ;мейта И 33 формируется импульс, кото- |рый, поступая на счетный вход первого регистра, записьгоает в него информацию. Импульс стробирования по- ступает также и на второй вход элемента И 34, но информация не заносится во второй регистр. Содержимое первого и второго регистров поступает на первый и четвертый входы первого коммутатора ввиду того, что на его второй вход и третий вход запрета поступает логический ноль, а на его выходной шине появится содержимое первого регистра. Кроме этого, содер- жимое первого и второго регистров поступает на адресные входы первого узла постоянной памяти, в результате чего на выходной шине последнего формируется модуль разности двух чи- сел.

Стробирующий сигнал, поступив на счетный вход счетчика 41, формирует на его выходе первый адр ес, который поступает на адресные входы всех че- тырех узлов оперативной памяти. Выходная информация первого коммутатора поступает на информационные входы первого и четвертого узлов оперативной памяти, а информация модуля раз- ности из первого узла постоянной памяти поступает на информационные входы второго и третьего узлов 7 оперативной памяти. Стробирующий сигнал

5 0 5 о Q g

5

с выхода первого элемента задержки поступает на первые входы элементов И 44-47, но только на выходе элементов И 44 и 46 формируется импульс, который, поступая на третьи входы второго и четвертого узлов оперативной памяти, запишет информацию. По окончании записи второй и четвертый узлы оперативной памяти установятся в режим считывания по адресу записи. Считанная информация первого- и четвертого узлов оперативной памяти поступает на адресные входы второго узла постоянной памяти, а считанная информация второго и третьего узлов оперативной памяти поступает на первый и четвертый входы второго коммутатора, так как на прямом выходе второго триггера присутствует логический ноль, который поступает на второй и третий входы запрета второго коммутатора, а на его выходе формируется выходной код третьего узла оперативной памяти. На выходе второго узла постоянной памяти формируется модуль разности двух точек по столбцам, а во второй узел памяти запишется модуль разности двух точек по строке (нечетной), С выхода второго узла постоянной памяти и второго коммутатора информация поступает на входы сумматора, а на его выходе формируется сумма модуля разности двух точек по строкам и модуля разности двух точек по столбцам. Сумма этих двух модулей разности поступает на вход регистра 56. На выходе второго элемента задержки формируется импульс, который поступает на первый вход эле- .мента И 57, но ввиду того, что на пря мом выходе третьего триггера присутствует логический ноль, который поступает на второй вход элемен та И 57, то на счетном входе регистра 56 разрешения записи не появится. Так как до окончания первой строки и начала второй третий триггер будет иметь ,на прямом выходе логический ноль, то информация, поступающая на информационный вход регистра 56, не фиксируется. Импульс с выхода второго элемента задержки поступит на счетный вход первого триггера и по заднему фронту переведет его в единичное состояние. В этом случае вторая (четная) информация записывается во второй ре- гистр.Первый коммутатор пропустит на свой выход информацию второго регистра.

ормула

5 зоб

1328830

р е т е и и я

д т в р

1 , Устройство для формирования признаков распознаваемых образов, со- дер жащее формирователь сигналов,вход которого является информационным входом устройства, а вьгход соединен с ннформдционньм входом аналого-цифрового преобразователя5 четьфе элемента Из 1 ри счетчика, дешифратор, гене ратор импульсов, шесть блоков памяти, шесть умножителей, и восемь интеграторов, управляющие входы которых соединены с выходом четвертого элемента И, первые входы первого и второго умножителей и информационный яход первого интегратора соединены с аьгходом второго блока памяти первые .;хг)дь третьего, четвертого, пятого а шестого умнолштелей и информацион- ньш вход второго интегратора соединены с выходом третьего блока памяти, чьгходы интеграторов являются выхода- i-itj. устройства 5 информационные входы В торого и третьего блоков памяти соединены с выходом первого блока памяти, вторые входы первого и третьего умнох-нтелей и адресные входы первого, четвертого, пятого и шестого бло- сов памяти соединены с первым выходом третьего счетчика, выход четвертого б,пока памяти соединен с вторыми входами второго и четвертого умножи- гелей, выход пятого блока памяти соединен с вторым входом пятого умножи- 35 ра является выходом блока,информацителя, вьгход metjToro блока памяти соединен с вторым входом шестого умножителя ;. выходы первого, второго,третьего, четвертого, пятого и шестого умножителей соединены с информацион- пьп-ш входами третьего, четвертого, гштого шестого, седьмого и восьмого интеграторов, выход первого элемента И соединен с ylIpaвляющи ш входами аналого-цифрового преобразователя и первого блока памяти, первые входы TiepBOro и второго элементов И и информационный вход первого счетчика соедине ны с выходом генератора им- ггульсоЗр управляюище входы первого и -второго счетчиков и генератора импуль- ; я являются входом Пуск устройст- :оа; 1эторые входы первого и второго :лпеыеитон Н соединены с первым выхо- , . ,7 :Пинфратора5 первые входы тре- гьего и четвертого элементов И соеди- .е;;ь; с выходом первого счетчика, вторые зходы тре гьего и четвертого .эле- bseviTOB И соединены с- вторым выходом

оиньш вход третьего регистра соединен с выходом сумматора, первый и второй входы которого соединены соответственно с выходами второго узла

40 постоянной памяти и второго коммутатора, прямой выход второго триггера соединен с первыми входами седьмого, восьмого, девятого и десятого элементов, И и с входами управления вто45 рого коммутатора, первьй и второй информационные входы которого соединены с выходами второго и тре тьего узлов оперативной памяти, первые входы пя- того и шестого элементов И, вход rtep50 вого элемента задержки и счетный вход четвертого счетчика являются входом Стробирование блока, выход первого элемента задержки соединен с вторыми входами седьмого, восьмого, девятого

55 и десятого элементоп И и с входом второго элемента за,дер жки, выход которого соединен с первым входом одиннадцатого элемента И и со счетным входом первого триггера, выход котодешифратора, информационный вход третьего счетчика соединен с выходами второго и третьего элементов И, второй вход третьего счетчика соединен

с входом Пуск устройства, второй выход третьего счетчика соединен с управляющим входом второго счетчика, , первый выход которого соединен с первым входом дешифратора, второй вход

которого соединен с вторым выходом второго счетчика, от-личающе- е с я тем, что, с целью повышения надежности устройства, в него введен блок вычисления модуля разности, информационный вход которого соединен с выходом аналого-1.щфрового преобразователя, вход Стробирование соединен с выходом первого элемента И, а выход соединен с ифнормационным входом первого блока памяти.

2. Устройство по п ю щ е е с я тем, что

1 , о т л и ч а

блок вычисления пятый, шемодуля разности содержит , стой, седьмой, восьмой, девятьй, десятый и одиннадцатый элементы И, три регистра, три триггера, два коммутатора, два узла постоянной памяти, четыре узла оперативной памяти,два элемента задержки, сумматор и четвертый счетчик, входы установки первого, второго и третьего триггеров,первого, второто и третьего .регистров и четвертого счетчика соединены с входом Пуск блока, выход третьего регистоиньш вход третьего регистра соединен с выходом сумматора, первый и второй входы которого соединены соответственно с выходами второго узла

40 постоянной памяти и второго коммутатора, прямой выход второго триггера соединен с первыми входами седьмого, восьмого, девятого и десятого элементов, И и с входами управления вто45 рого коммутатора, первьй и второй информационные входы которого соединены с выходами второго и тре тьего узлов оперативной памяти, первые входы пя- того и шестого элементов И, вход rtep50 вого элемента задержки и счетный вход четвертого счетчика являются входом Стробирование блока, выход первого элемента задержки соединен с вторыми входами седьмого, восьмого, девятого

55 и десятого элементоп И и с входом второго элемента за,дер жки, выход которого соединен с первым входом одиннадцатого элемента И и со счетным входом первого триггера, выход которого соединен со своим ифнормационным входом, с управляющими входами первого коммутатора -и с вторыми входами пятого и шестого элементов И, выходы которых соединены с входами синхронизации первого и второго регистров, информационные входы которых являются информационньм входом блока, выходы первого и второго регистров соединены с адресными входами первого узла постоянной памяти и с информационными входами первого коммутатора, выход которого соединен с йнформационньми входами первого и четвертого узлов оперативной памяти, информационные входы второго и третьего узлов оперативной памяти соединены с выходом первого узла постоянной памяти, адресные входы первого, второго, тре-

тьего и четвертого узлов оперативной памяти соединены с первым выходом че вертого счетчика, второй вькод кото- рого соединен со счетными входами второго и третьего триггеров, инвер- сный выход второго триггера соединён со своим ифнормационным входом, прямой выход третьего триггера соединен с вторым входом одиннадцатого элемента И, выход которого соединен с входом синхронизации третьего регистра, выходы седьмого, восьмого, девятого и десятого элементов И соединены с управляющими входами четвертого,первого, второг.о р третьего узлов оперативной памяти,- выходы первого и чет- вертого узлов оперативной памяти со-. единены с адресными входами второго узла постоянной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения систем линейных алгебраических уравнений | 1990 |

|

SU1721613A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Анализатор спектров | 1982 |

|

SU1023341A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Устройство для вычисления логических производных многозначных данных | 1990 |

|

SU1837277A1 |

| Устройство для поиска координат точки экстремума функции двух переменных | 1981 |

|

SU966703A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для реализации быстрого преобразования Фурье | 1984 |

|

SU1233166A1 |

| Устройство управления для процессора быстрого преобразования Фурье | 1984 |

|

SU1270775A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

Изобретение относится к области автоматики и вычислительной техники и может использоваться для обработки изображений. Введение в устройство блока вычисления модуля разности позволяет повысить надежность распознавания образов. 2 ип. оо to 00 00 оо

Пусн

1 - 35

SJ

| Патент США № 3863218, кл.- 340146, 3, опублик | |||

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Устройство для формирования признаков распознаваемых образов | 1983 |

|

SU1145355A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-08-07—Публикация

1986-03-27—Подача