индексный регистр 17, введен цифровой генератор 1 функции одной переменной. В описании изобретения приведены примеры выполнения первого, второго и третьего арифметических блоков,а также счетчика цикла и коммутатора. Введение цифрового генера1

Изобретение относится к импульсной технике.

Целью изобретения является расширение функциональных.возможностей за счет управления видом автокорреляционной функции генерируемого процесса.

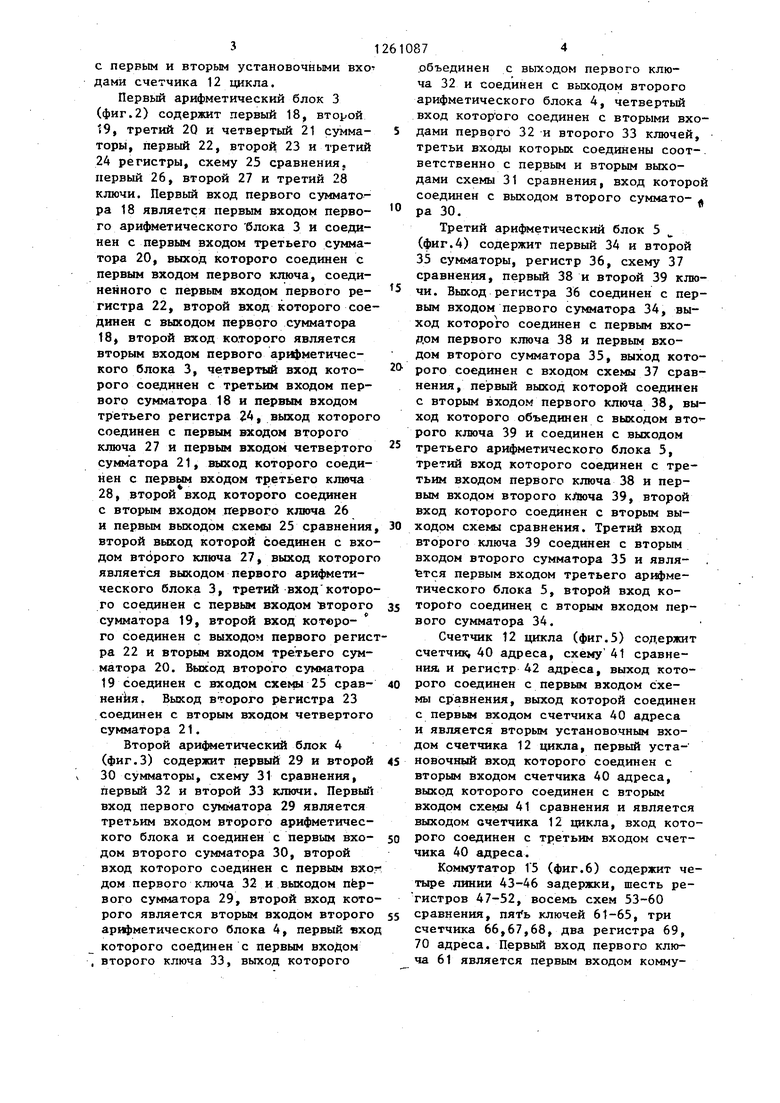

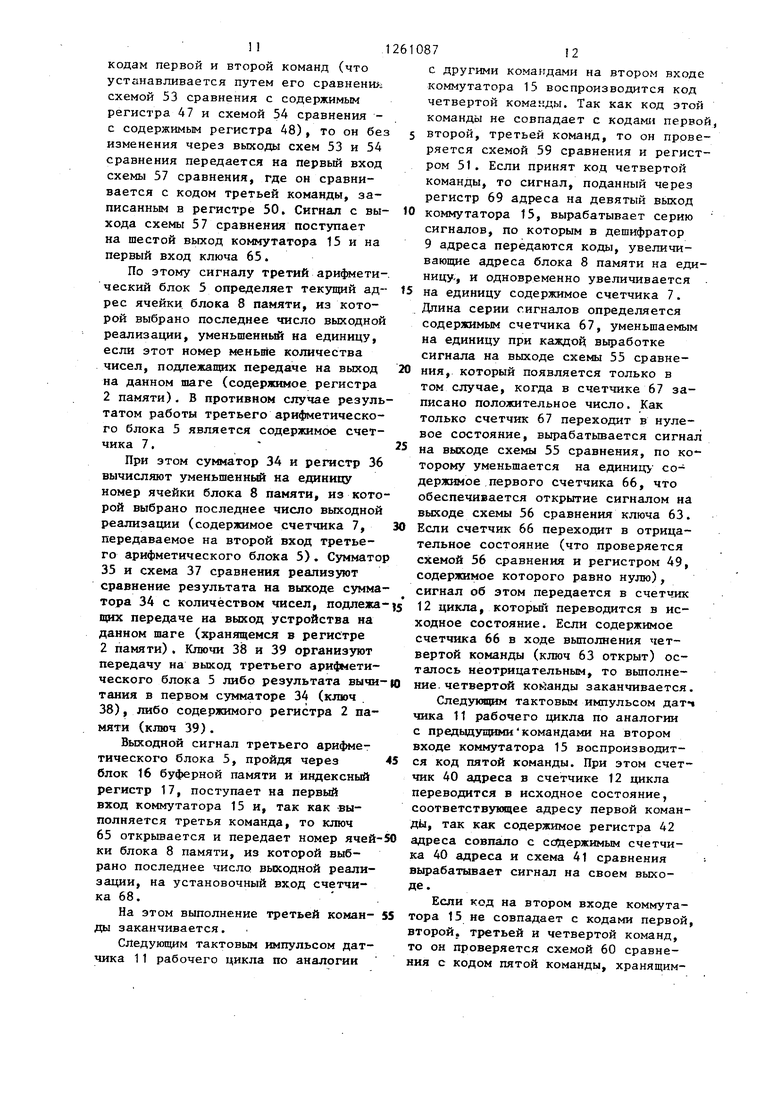

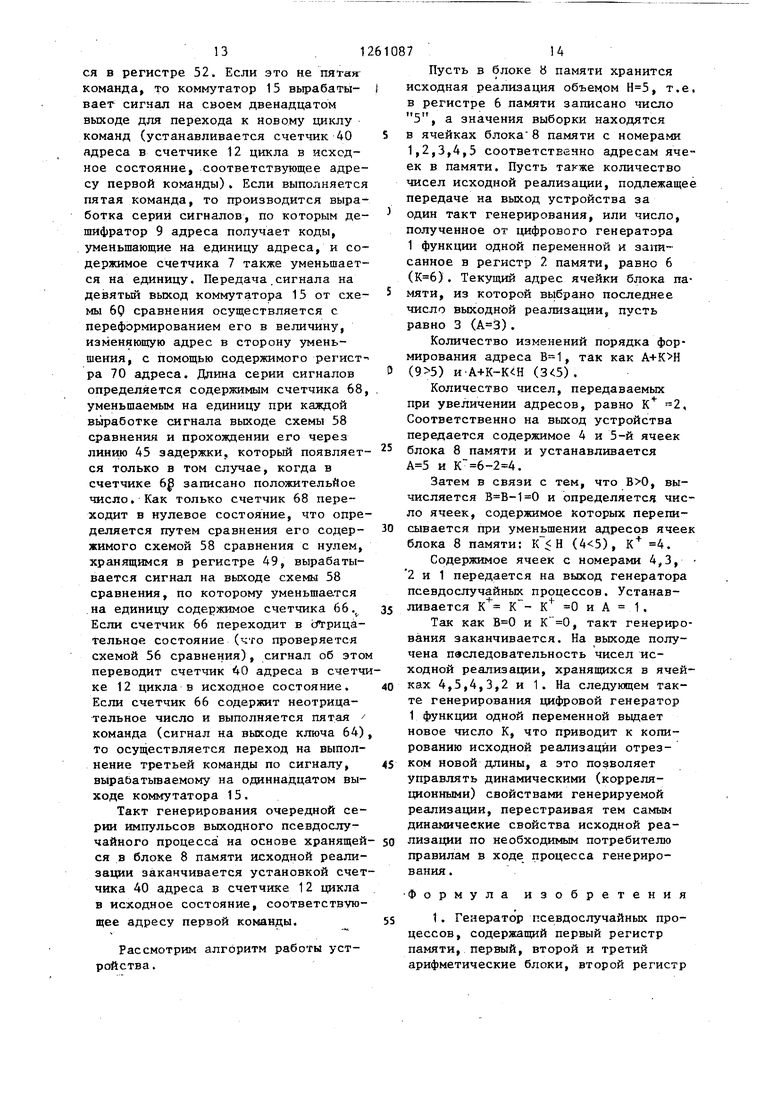

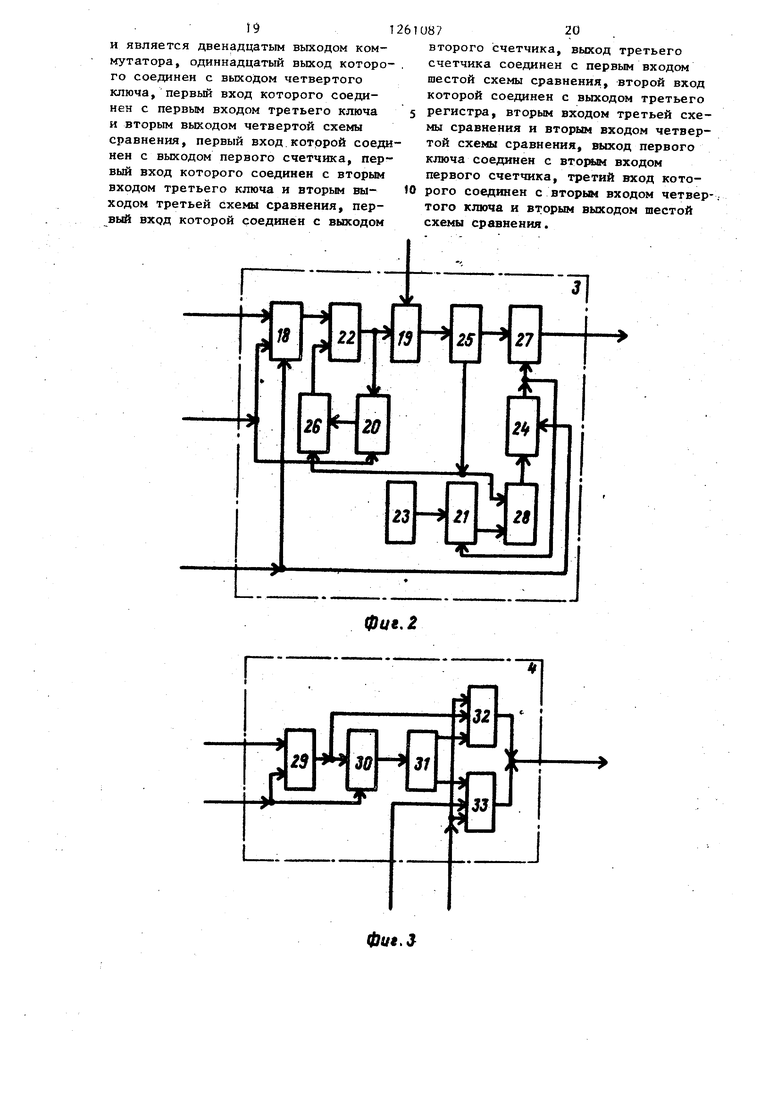

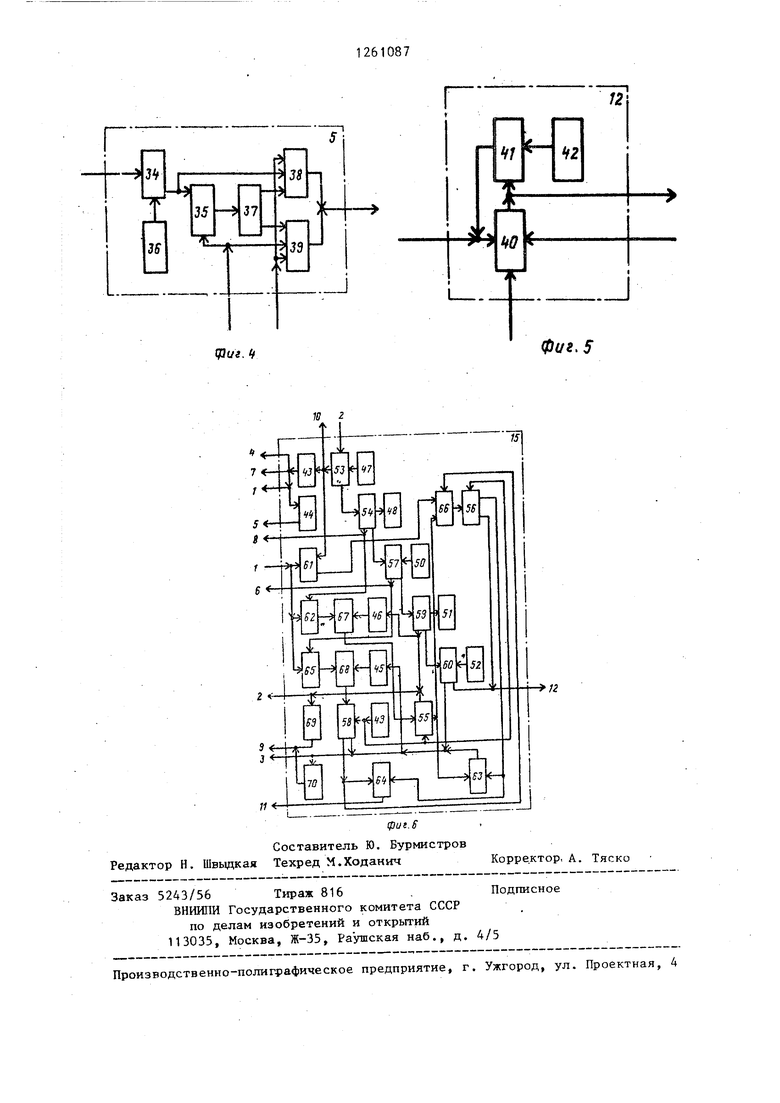

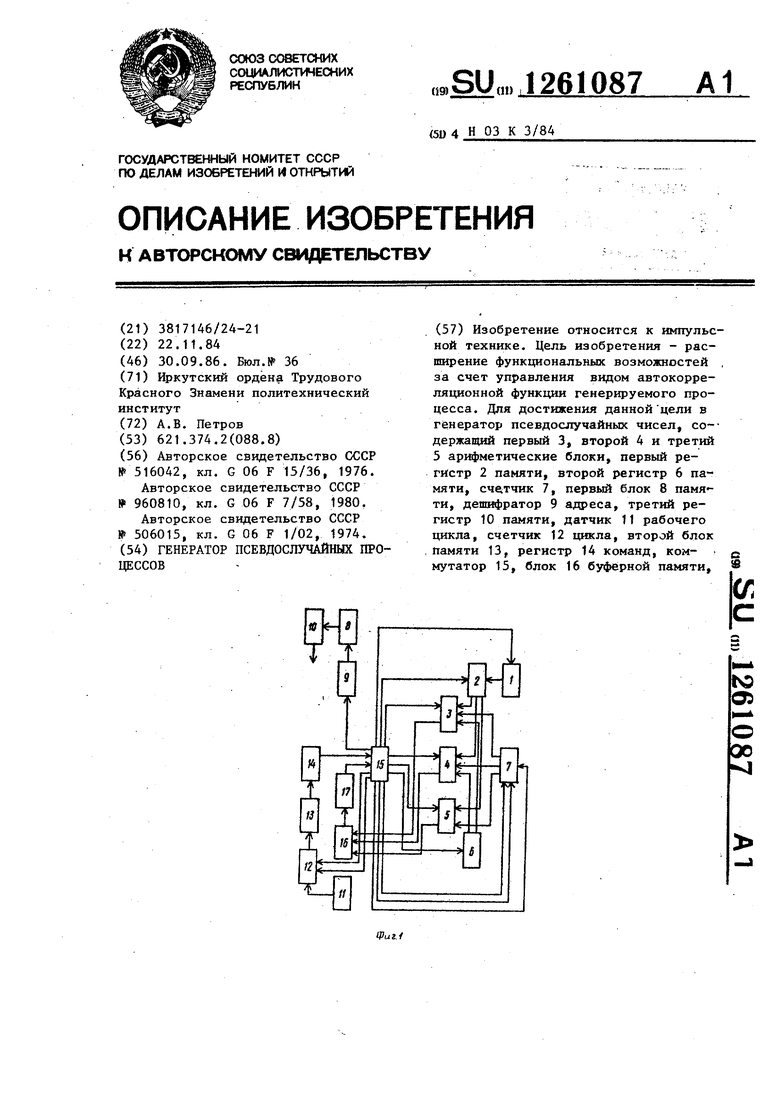

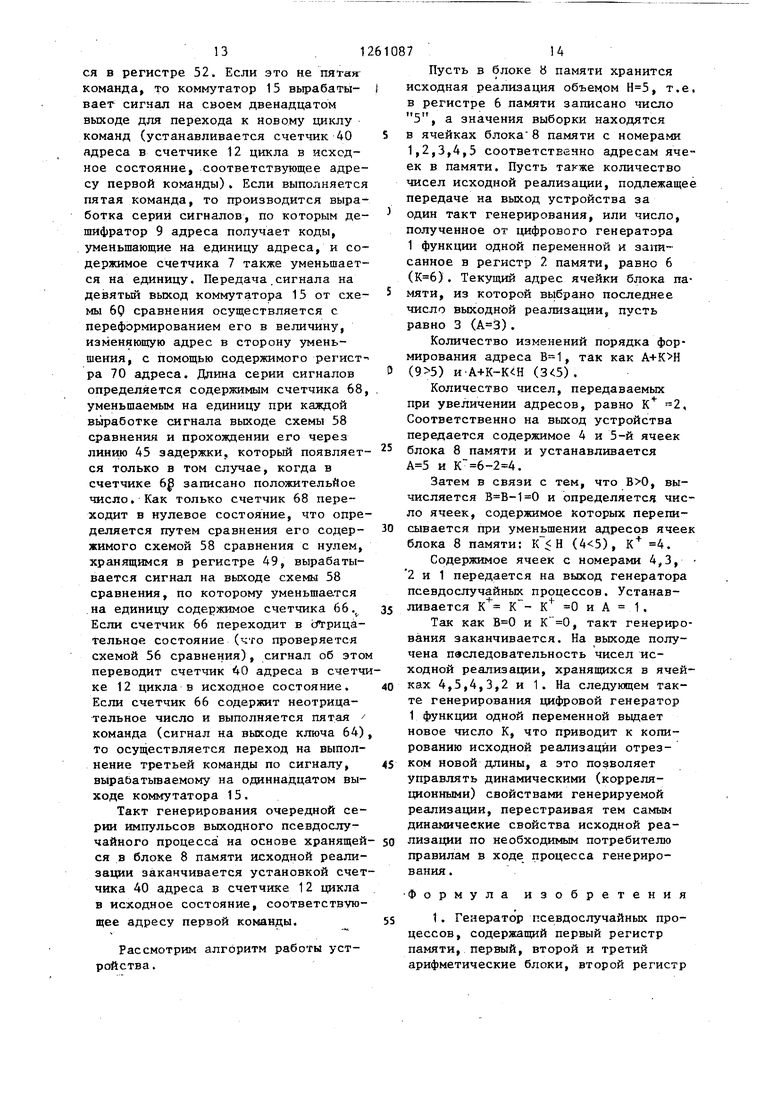

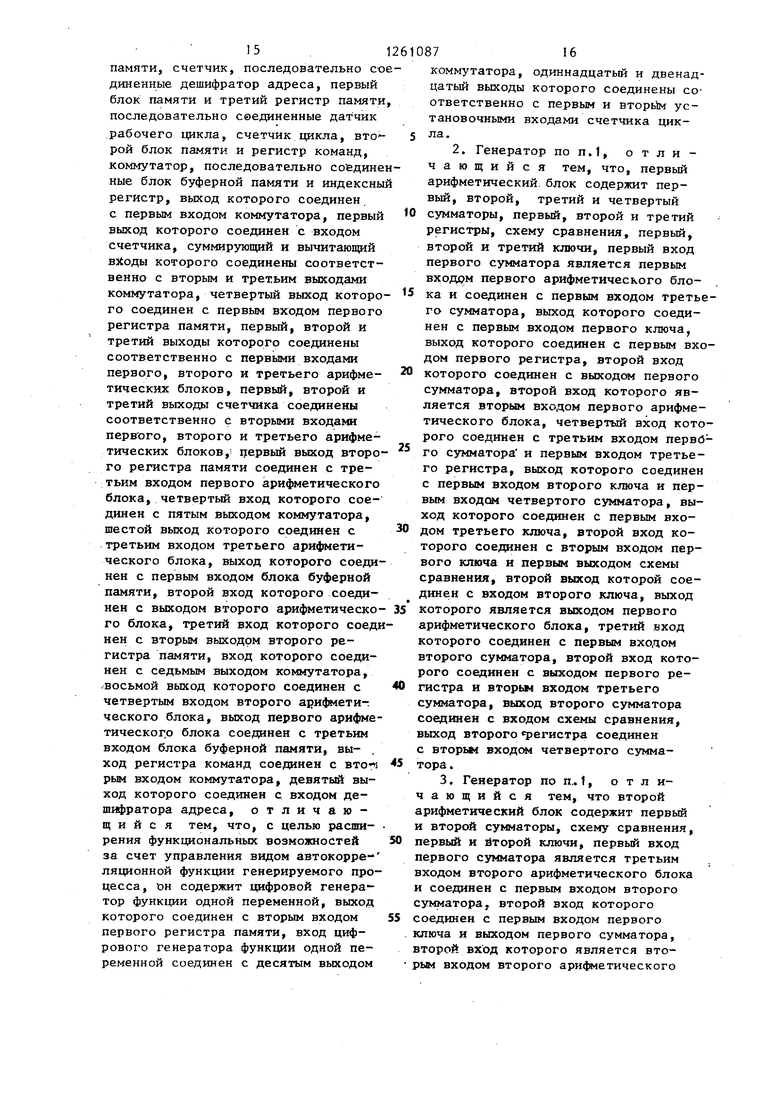

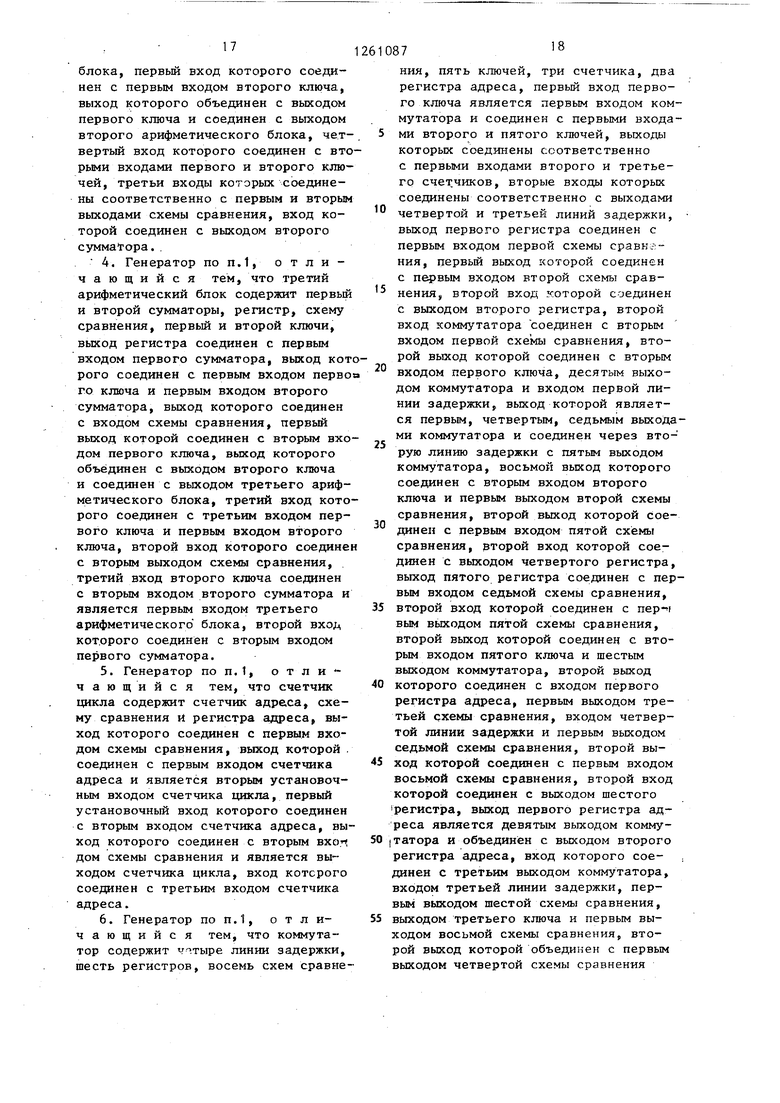

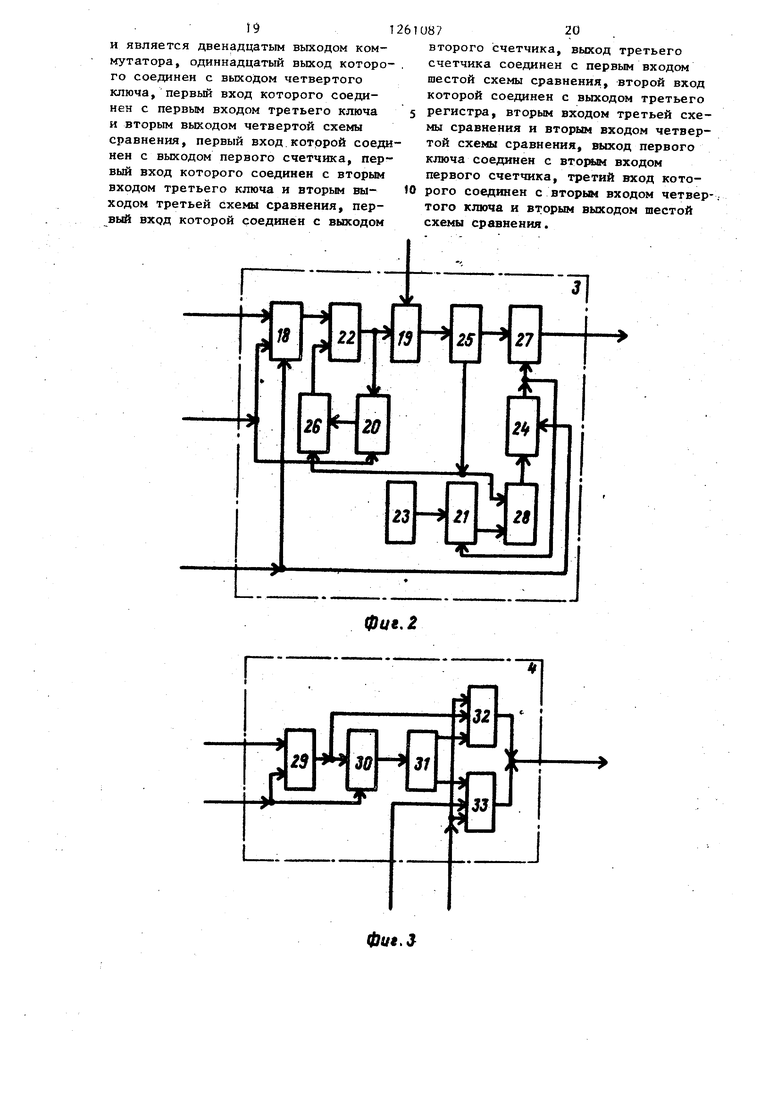

На фиг.1 представлена структурная схема генератора псевдослучайных процессов; на фиг.2 - схема первого арифметического блока; на фиг.З - то же, второго блокаj на фиг.4 - третьего блока, на фиг.5 - счетчик цикла; на фиг.6 - коммутатор.

Генератор псевдослучайных процессов (фиг.1) содержит цифровой ге- нератор 1 функции одной переменной, первый регистр 2 памяти, первый 3, второй 4 и третий 5 арифметические блоки, второй регистр 6 памяти, .счет чик 7, первый блок 8 памяти, дешифратор 9 адреса, третий регистр 10 памяти, датчик 11 рабочего цикла, счетчик 12 цикла, второй блок 13 памяти, регистр 14 команд, коммутатор 15,блок 16 буферной памяти, индексный регистр 17. Выход дешифратора 9 адреса соединен с входом первого блока 8 памяти, выход которого соединен с входом третьего регистра 10 памяти. Выход датчика 11 рабочего цикла соединен с входом счетчика 12 цикла, выход которого соединен с входом второго блока 13 памяти, выход которого соединен с входом регистра 14 команд. Выход блока 16 буферной памяти соединен с входом индексного регистра 17, выход которого соединен с первым входом коммутатора 15, первый выход.которого соединен с входом счетчика 7, суммирующий и вычитающий входы которого соединены соответственно с вторым

тора одной переменной позволяет управлять динамическими свойствами генерируемой реализации, перестраивая тем самым их по необходимым потребителю правилам в ходе процесса генерирования. 6 з.п. ф-лы, 6 ил.

2

и третьим выходами коммутатора 15, четвертый выход которого соединен с первым входом первого регистра 2 памяти, первый, второй и третий вы- 5 .ходы которого соединены соотватст- венно с первыми входами первого 3, ;второго 4 и третьего 5 арифметических блоков. Первый, второй и третий выходы счетчика 7 соединены соот- 10 ветственно с вторыми входами первого 3, второго 4 и третьего 5 арифметических блоков. Первый выход второго регистра 6 памяти соединен с. третьим входом первого ари4 1етического 15 блока 3, четвертый вход которого

соединен с пятым выходом коммутатора 15, шестой выход которого соединен с третьим входом третьего арифметического блока 5, выход которого сое- 2Q дивен с первым входом блока 16 буферной памяти, второй вход которого соединен с выходом второго арифметического блока 4, третий вход которого соединен с вторым выходом 25 второго регистра 6 памяти, вход которого соединен с седьмым выходом коммутатора 15, восьмой выход которого соединен с четвертым входом второго арифметического блока 4. бы- 30 ход первого арифметического блока 3 соединен с третьим входом блока 16 буферной памяти. Выход регистра 14 команд соединен с вторым входом коммутатора 15, выход которого

35 соединен с входом дешифратора 9 адреса. Выход цифрового генератора 1 функции одной переменной соединен с вторым входом первого регистра 2 памяти. Вход цифрового генератора

40 1 функции одной переменной соединен с десятым выходом коммутатора 15, одиннадцатый и двенадцатый выходы которого соединены соответственно

с первым и вторым установочными вхо дами счетчика 12 цикла.

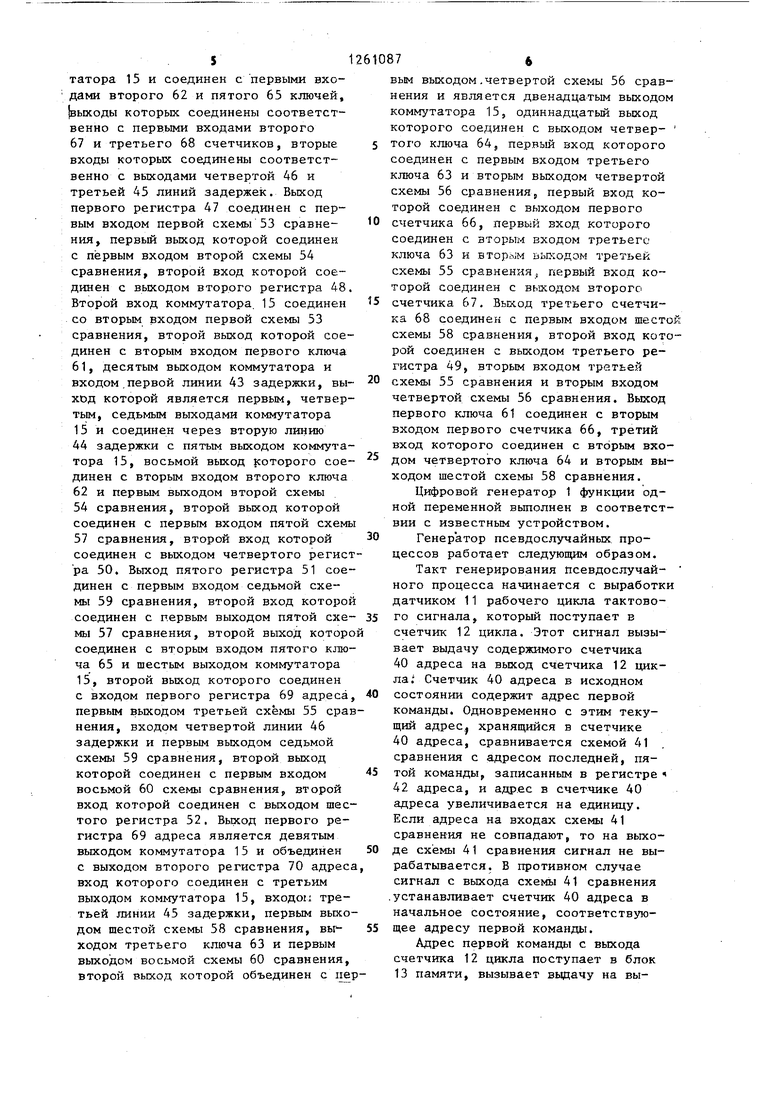

Первый арифметический блок 3 (фиг.2) содержит первый 18, второй t9, третий 20 и четвертый 21 сумматоры, первый 22, второй 23 и третий 24 регистры, схему 25 сравнения, первый 26, второй 27 и третий 28 ключи. Первый вход первого сумматора 18 является первым входом первого арифметического блока 3 и соединен с первым входом третьего сумматора 20, выход которого соединен с первым входом первого ключа, соединенного с первым входом первого регистра 22, второй вход которого соединен с выходом первого сумматора 18, второй вход ко-торого является вторым входом первого ар1 фметичес- кого блока 3, четвертый вход которого соединен с третьим входом первого сумматора 18 и первым входом третьего регистра 2А, выход которого соединен с первым входом второго ключа 27 и первым входом четвертого сумматора 21, выход которого соединен с первым входом третьего ключа 28, второй вход которого соединен

26

С вторым входом первого ключа и первым выходом схемы 25 сравнения, второй выход которой соединен с входом второго ключа 27, выход которого является выходом первого арифметического блока 3, третий вход которого соединен с первым входом второго сумматора 19, второй вход котвро- го соединен с выходом первого регистра 22 и вторым входом третьего сумматора 20. Выход второго сумматора 19 соединен с входом 25 сравнения. Выход второго регистра 23 соединен с вторым входом четвертого сумматора 21.

Второй арифметический блок 4 (фиг.З) содержит первый 29 и второй 30 сумматоры, схему 31 сравнения, первый 32 и второй 33 ключи. Первый вход первого сумматора 29 является третьим входом второго арифметического блока и соединен с первым входом второго сумматора 30, второй вход которого соединен с первым вхо дом первого ключа 32 и выходом первого сумматора 29, второй вход которого является вторым входом второго арифметического блока 4, первый схо которого соединен с первым входом второго ключа 33, выход которого

10

15

20

25

2610874

.объединен с выходом первого ключа 32 и соединен с вьпсодом второго арифметического блока 4, четвертый вход которого соединен с вторыми входами первого 32 и второго 33 ключей, третьи входы которых соединены соответственно с первым и вторым выходами схемы 31 сравнения, вход которой соединен с выходом второго суммато- ра 30.

Третий арифметический блок 5 (фиг.4) содержит первый 34 и второй 35 сумматоры, регистр 36, схему 37 сравнения, первый 38 и второй 39 ключи. Выход регистра 36 соединен с первым входом первого сумматора 34, выход которого соединен с первым входом первого ключа 38 и первым входом второго сумматора 35, выход которого соединен с входом схемы 37 сравнения, первый выход которой соединен с вторым входом первого ключа 38, выход которого объединен с выходом вто рого ключа 39 и соединен с выходом третьего арифметического блока 5, третий вход которого соединен с третьим входом первого ключа 38 и первым входом второго ключа 39, второй вход которого соединен с вторым выходом схемы сравнения. Третий вход второго ключа 39 соединен с вторым входом второго сумматора 35 и является первым входом третьего арифметического блока 5, второй вход которого соединен с вторым входом первого сумматора 34.

Счетчик 12 цикла (фиг.5) содержит счетчику 40 адреса, схему 41 сравнения, и регистр 42 адреса, выход которого соединен с первым входом схемы сравнения, выход которой соединен с перв№ входом счетчика 40 адреса И является вторьтм установочным входом счетчика 12 цикла, первый установочный вход которого соединен с вторым входом счетчика 40 адреса, выход которого соединен с вторым входом схемы 41 сравнения и является выходом счетчика 12 цикла, вход которого соединен с третьим входом счетчика 40 адреса.

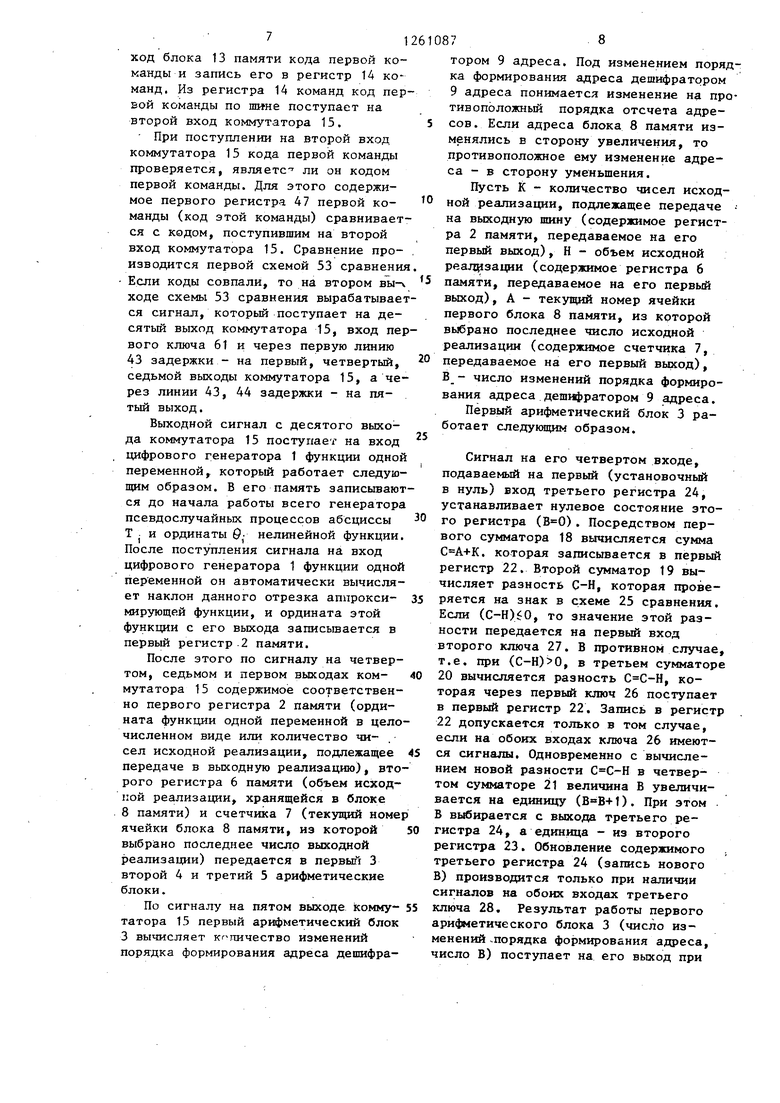

Коммутатор 15 (фиг.6) содержит четыре линии 43-46 задержки, шесть ре- тистров 47-52, восемь схем 53-60 сравнения, пят ь ключей 61-65, три счетчика 66,67,68, два регистра 69, 70 адреса. Первый вход первого ключа 61 является первым входом комму30

35

40

45

50

55

татора 15 и соединен с первыми входами второго 62 и пятого 65 ключей, выходы которых соединены соответственно с первыми входами второго 67 и третьего 68 счетчиков, вторые входы которых соединены соответственно с выходами четвертой 46 и третьей 45 линий задержек. Выход первого регистра 47 соединен с первым входом первой схемы 53 сравнения, первый выход которой соединен с первым входом второй схемы 54 сравнения, второй вход которой соединен с выходом второго регистра 48, Второй вход коммутатора. 15 соединен со вторым входом первой схемы 53 сравнения, второй выход которой соединен с вторым входом первого ключа 61, десятым выходом коммутатора и входом.первой линии 43 задержки, выход которой является первым, четвертым, седьмым выходами коммутатора 15 и соединен через вторую линию 44 задержки с пятым выходом коммутатора 15, восьмой выход которого соединен с вторым входом второго ключа 62 и первым выходом второй схемы 54 сравнения, второй выход которой соединен с первым входом пятой схемы 57 сравнения, второй вход которой соединен с выходом четвертого регистра 50. Вьпсод пятого регистра 51 соединен с первым входом седьмой схемы 59 сравнения, второй вход которой соединен с первым выходом пятой схе- мы 57 сравнения, второй выход которо соединен с вторым входом пятого ключа 65 и шестым выходом коммутатора 15, второй выход которого соединен с входом первого регистра 69 адреса первым выходом третьей схемы 55 сравнения, входом четвертой линии 46 задержки и первым выходом седьмой схемы 59 сравнения, второй выход которой соединен с первым входом восьмой 60 схемы сравнения, второй вход которой соединен с выходом шестого регистра 52, Вьрсод первого регистра 69 адреса является девятым выходом коммутатора 15 и объединен с выходом второго регистра 70 адрес вход которого соединен с третьим выходом коммутатора 15, входом третьей линии 45 задержки, первым выходом шестой схемы 58 сравнения, ходом третьего ключа 63 и первым выходом восьмой схемы 60 сравнения, второй выход которой объединен с iie

0

0

5

вым выходом.четвертой схемы 56 сравнения и является двенадцатым выходом коммутатора 15, одиннадцатый выход которого соединен с выходом четвер- того ключа 64 5 пе.рвьш вход которого соединен с первым входом третьего ключа 63 и вторым выходом четвертой схемы 56 сравнения, первый вход которой соединен с выходом первого счетчика 66, первый вход которого соединен с вторым входом третьего ключа 63 и вторл м выходом третьей схемы 55 сравнения, первый вход которой соединен с выходом второго 5 счетчика 67. Вьпсод третьего счетчика 68 соединен с первым входом шестой схемы 58 сравнения, второй вход которой соединен с выходом третьего регистра 49, вторым входом третьей схемы 55 сравнения и вторым входом четвертой схемы 56 сравнения. Выход первого ключа 61 соединен с вторым входом первого счетчика 66, третий вход которого соединен с вторым вхо- 5 дом четвертого ключа 64 и вторым выходом шестой схемы 58 сравнения.

Цифровой генератор 1 функции одной переменной вьшолнен в соответствии с известным устройством.

Генератор псевдослучайных процессов работает следующим образом.

Такт генерирования псевдослучай- ного процесса начинается с выработки датчиком 11 рабочего цикла тактового сигнала, который поступает в счетчик 12 цикла. Этот сигнал вызывает выдачу содержимого счетчика 40 адреса на выход счетчика 12 цикла. Счетчик 40 адреса в исходном состоянии содержит адрес первой команды. Одновременно с этим текущий адреС| хранящийся в счетчике 40 адреса, сравнивается схемой 41 сравнения с адресом последней, пятой команды, записанньм в регистре 42 адреса, и адр.ес в счетчике 40 адреса увеличивается на единицу. Если адреса на входах схемы 41 сравнения не совпадают, то на выходе схемы 41 сравнения сигнал не вырабатывается. В противном случае сигнал с выхода схемы 41 сравнения .устанавливает счетчик 40 адреса в начальное состояние, соответствующее адресу первой команды.

Адрес первой команды с выхода счетчика 12 цикла поступает в блок 13 памяти, вызывает выдачу на вы0

5

0

ход блока 13 памяти кода первой команды и запись его в регистр 14 команд. Из регистра 14 команд код первой команды по поступает на второй вход коммутатора 15.

При поступлении на второй вход коммутатора 15 кода первой команды проверяется, являете ли он кодом первой команды. Для этого содержимое первого регистра 47 первой ко- манды (код этой команды) сравнивается с кодом, поступившим на второй вход коммутатора 15. Сравнение про- изводится первой схемой 53 сравнения Если коды совпали, то на втором вы-v ходе схемы 53 сравнения вырабатывается сигнал, который поступает на десятый выход коммутатора 15, вход первого ключа 61 и через первую линию 43 задержки - на первый, четвертый, седьмой выходы коммутатора 15, а через линии 43, 44 задержки - на пятый выход.

Выходной сигнал с десятого выхода коммутатора 15 поступает на вход цифрового генератора 1 функции одной переменной, который работает следующим образом. В его память записьшают ся до начала работы всего генератора псевдослучайных процессов абсциссы Т и ординаты б- нелинейной функции. После поступления сигнала на вход цифрового генератора 1 функции одной переменной он автоматически вычисляет наклон данного отрезка аппрокси- мирующей функции, и ордината этой функции с его выхода записьшается в первый регистр .2 памяти.

После этого по сигналу на четвертом, седьмом и первом выходах ком- мутатора 15 содержимое соответственно первого регистра 2 памяти (ордината функции одной переменной в целочисленном виде или количество чн- . сел исходной реализации, подлежащее передаче в выходную реализацию), второго регистра 6 памяти (объем исходной реализации, хранящейся в блоке 8 памяти) и счетчика 7 (текущий номе ячейки блока 8 памяти, из которой выбрано последнее число выходной реализации) передается в первый 3 второй 4 и третий 5 арифметические блоки.

По сигналу на пятом выходе комму- татора 15 первый арифметический блок 3 вычисляет кг пичество изменений порядка формирования адреса дешифра5

5

5

0

тором 9 адреса. Под изменением порядка формирования адреса дешифратором 9 адреса понимается изменение на противоположный порядка отсчета адресов. Если адреса блока 8 памяти изменялись в сторону увеличения, то противоположное ему изменение адреса - в сторону уменьшения.

Пусть К - количество чисел исходной реализации, подлежащее передаче на выходную шину (содержимое регистра 2 памяти, передаваемое на его первый выход), Н - объем исходной реахц1зации (содержимое регистра 6 памяти, передаваемое на его первый выход), А - текущий номер ячейки первого блока 8 памяти, из которой выбрано последнее число исходной реализации (содержимое счетчика 7, передаваемое на его первый выход), Б - число изменений порядка формирования адреса дешифратором 9 адреса.

Первый арифметический блок 3 работает следукнцим образом.

Сигнал на его четвертом входе, подаваемый на первый (установочный в нуль) вход третьего регистра 24, устанавливает нулевое состояние этого регистра (). Посредством первого сумматора 18 вычисляется сумма . которая записывается в первый регистр 22. Второй сумматор 19 вычисляет разность С-Н, которая проверяется на знак в схеме 25 сравнения. Если (С-Н)О, то значение этой разности передается на первый вход второго ключа 27. В противном случае, т.е. при (С-Н)0, в третьем сумматоре 20 вычисляется разность , которая через первый ключ 26 поступает в первый регистр 22. Запись в регистр 22 допускается только в том случае, если на обоих входах ключа 26 имеются сигналы. Одновременно с вычислением новой разности в четвертом сумматоре 21 величина В увеличивается на единицу (). При этом В выбирается с выхода третьего регистра 24, а единица - из второго регистра 23. Обновление содержимого . третьего регистра 24 (запись нового В) производится только при наличии сигналов на обоих входах третьего ключа 28. Результат работы первого арифметического блока 3 (число изменений -порядка формирования адреса, число В) поступает на его выход при

аличии сигналов на обоих входах торого ключа 27.

Выходной информационньй сигнал первого арифметического блока 3 поступает на вход блока 16 буферной па- j мяти и, пройдя через него и индексный регистр 17, поступает на первые входы первого 61, второго 62 и пятого 65,ключей коммутатора 15 Так как выполняется первая команда, то 10 первый ключ 61 открывается и передает число изменений порядка формирования адресов блока 8 памяти (выход первого арифметического блока 3) на первый вход счетчика 66, устанав;|и- 15 вая его в новое состояние.

На этом выполнение первой команды заканчивается.

Следующим тактовым сигналом датчика 11 рабочего цикла из счетчика 20 40 адреса в счетчике 12 цикла текущий адрес (адрес второй команды) передается на выход счетчика 12 цикла и на вход схемы 41 сравнения. Содержимое счетчика 40 адреса увеличивает-25 ся на единицу. Так как текущий адрес на входе схемы 41 сравнения не совпадает с адресом пятой (последней) команды, хранящимся в регистре 42 адреса, то сигнал на выходе схемы 41 30 сравнения не вырабатывается.

Адрес второй команды с выхода счетчика 12 цикла поступает в блок 13 памяти, вызывает вьщачу на вькод этого блока кода второй команды и 35 запись его в регистр 14 команд, из которого код второй команды поступает в коммутатор .15.

Так как код этой команды на входе не соответствует коду первой коман- 40 ды (это устанавливается путем сравнения его схемой 53 сравнения с содержимым регистра 47 первой команды), То он без изменения через первый выход схемы 53 сравнения передается 45 на первый вход схемы 54 сравнения, где сравнивается с кодом второй команды, записанным в регистре 48 и подаваемым на второй вход схемы 54 сравнения. На первом выходе схемы 50 54 сравнения воспроизводится сигнал, который поступает на восьмой выход, коммутатора 15 и на второй вход ключа 62 коммутатора 15.

По сигналу на восьмом выходе ком- 55 мутатора 15 второй арифметический блок 4 вычисляет количество ячеек блока 8 памяти, содержимое которых

передается через регистр 10 памяти на выходную шину устройства при увеличении адресов блока В памяти. Для этого из содержимого регистра 6 памяти (объем исходной реализации) вычитается содержимое счетчика 7 (номер ячейки) блока памяти, из которой выбрано последнее число выходной реализации). Результат вычитания выдается на выход второго арифметического блока 4 при условии, что он меньше количества ячеек, содержимое которых подлеж1 т передаче на выходы устройства, (содержимое регистра 6 памяти). В противном случае результатом работы второго арифметического блока 4 является содержимое регистра 2 памяти.

При э том сумматор 29 осуществляет вычисление разности между объемом реализации (содержимое регистра 6 памяти, передаваемое на третий вход второго арифметического блока 4) и номером последней использованной ячейки блока 8 памяти (содержимое счетчика 7, передаваемое на второй вход второго арифметического блока 4). Второй сумматор 30 и схема 31 сравнения производят сравнение результата вычитания с объемом исходной реализации. Ключи 32 и 33 орг ганизуют передачу на второй вход блока 16 буферной памяти либо результата вычитания в первом сумматоре 29 (ключ 32), либо содержимого регистра 2 памяти (ключ 33),

Выходной сигнал второго арифметического блока 4 поступает на вход блока 16 буферной памяти и, пройдя через него и индексный регистр 17, поступает на первые входы ключей 61, 62 и 65. Так как вьшолняется вторая команда, то ключ 62, открьшается и передает количество чисел, записанных в блоке 8 памяти, содержимое которых передается через регистр 10 памяти на выход устройства при увеличении адресов блока 8 памяти, на установочный вход счетчика 67.

На этом выпЬлнение второй команды заканчивается.

Следующим тактовым импульсом датчика 11 рабочего, цикла, по аналогии с предьщущими командами, на втором входе коммутатора 15 воспроизводит- ся код третьей команды.

Так как код команды на втором входе коммутатора 15 не соответствует

кодам первой и второй команд (что устанавливается путем его сравнен ; схемой 53 сравнения с содержимым регистра 47 и схемой 54 сравнения - с содержимым регистра 48), то он без изменения через выходы схем 53 и 54 сравнения передается на первый вход схемы 57 сравнения, где он сравнивается с кодом третьей команды, записанным в регистре 50. Сигнал с выхода схемы 57 сравнения поступает на шестой выход коммутатора 15 и на первый вход ключа 65.

По этому сигналу третий ари жети-. ческий блок 5 определяет текущий адрес ячейки блока 8 памяти, из которой выбрано последнее число выходной реализации, уменьшенный на единицу, если этот номер меньше количества

на данном шаге (содержимое регистра 2 памяти), В противном случае результатом работы третьего арифметического блока 5 является содержимое счетчика 7.

При этом сумматор 34 и регистр 36 вычисляют уменьшенный на единицу номер ячейки блока 8 памяти, из которой выбрано последнее число выходной реализации (содержимое счетчика 7, передаваемое на второй вход третьего арифметического блока 5). Сумматор 35 и схема 37 сравнения реализуют сравнение результата на выходе сумма

тора 34 с количеством чисел, подлежа-J5 12 цикла, который переводится в ис- щих передаче на выход устройства на данном шаге (хранящемся в регистре 2 памяти) . Ключи 38 и 39 организзгют передачу на выход третьего арифметического блока 5 либо результата вычи-|0 тания в первом сумматоре 34 (ключ 38), либо содержимого регистра 2 памяти (ключ 39).

Выходной сигнал третьего арифметического блока 5, пройдя через 45 блок 16 буферной памяти и индексный регистр 17, поступает на первый вход коммутатора 15 и, так как выполняется третья команда, то ключ

ходное состояние. Если содержимое счетчика 66 в ходе выполнения четвертой команды (ключ 63 открыт) осталось неотрицательным, то вьшолне- ние. четвертой команды заканчивается. Следукщим тактовым импульсом дат- чика 11 рабочего хщкла по аналогии с предьщущими командами на втором входе коммутатора 15 воспроизводится код пятой команды. При этом счетчик 40 адреса в счетчике 12 цикла переводится в исходное состояние, соответствующее адресу первой коман- дЬ1, так как содержимое регистра 42

65 открьшается и передает номер ячей-50 адреса совпало с содержимым счетчики блока 8 памяти, из которой выбрано последнее число выходной реализации, на установочный вход счетчика 68.

На этом выполнение третьей коман- ды заканчивается.

следующим тактовым импульсом датчика 11 рабочего цикла по аналогии

с другими командами на втором входе коммутатора 15 воспроизводится код четвертой команды. Так как код этой команды не совпадает с кодами первой, второй, третьей команд, то он проверяется схемой 59 сравнения и регистром 51. Если принят код четвертой команды, то сигнал, поданный через регистр 69 адреса на девятый выход

коммутатора 15, вырабатывает серию сигналов, по которым в дешифратор 9 адреса передаются коды, увеличивающие адреса блока 8 памяти на единицу,, и одновременно увеличивается .

на единицу содержимое счетчика 7. Длина серии сигналов определяется содержимым счетчика 67, уменьшаемым на единицу при каждо выработке сигнала на выходе схемы 55 сравнения, который появляется только в

том случае, когда в счетчике 67 записано положительное число. Как только счетчик 67 переходит в нулевое состояние, вырабатывается сигнал на выходе схемы 55 сравнения, по которому уменьшается на единицу содержимое первого счетчика 66, что обеспечивается открытие сигналом на выходе схемы 56 сравнения ключа 63. Если счетчик 66 переходит в отрицательное состояние (что проверяется схемой 56 сравнения и регистром 49, содержимое которого равно нулю), сигнал об этом передается в счетчик

12 цикла, который переводится в ис-

ходное состояние. Если содержимое счетчика 66 в ходе выполнения четвертой команды (ключ 63 открыт) осталось неотрицательным, то вьшолне- ние. четвертой команды заканчивается Следукщим тактовым импульсом дат чика 11 рабочего хщкла по аналогии с предьщущими командами на втором входе коммутатора 15 воспроизводится код пятой команды. При этом счетчик 40 адреса в счетчике 12 цикла переводится в исходное состояние, соответствующее адресу первой коман дЬ1, так как содержимое регистра 42

ка 40 адреса и схема 41 сравнения вырабатывает сигнал на своем выходе .

Если код на втором входе коммутатора 15 не совпадает с кодами первой, второй, третьей и четвертой команд, то он проверяется схемой 60 сравнения с кодом пятой команды, хранящим13 .

ся в регистре 52. Если это не пятаяг команда, то коммутатор 15 вьфабаты- вает сигнал на своем двенадцатом выходе для перехода к новому циклу команд (устанавливается счетчик 40 адреса в счетчике 12 цикла в исходное состояние, соответствующее адресу первой команды). Если выполняетс пятая команда, то производится выработка серии сигналов, по которым дешифратор 9 адреса получает коды, уменьшающие на единицу адреса, и содержимое счетчика 7 также уменьшается на единицу. Передача.сигнала на девятый выход коммутатора 15 от схемы 69 сравнения осуществляется с переформированием его в величину, изменяющую адрес в сторону уменьшения, с помощью содержимого регист ра 70 адреса. Длина серии сигналов определяется содержимым счетчика 68 уменьшаемым на единицу при каждой выработке сигнала выходе схемы 58 сравнения и прохождении его через линию 45 задержки, который появляется только в том случае, когда в счетчике 6g записано положительйое число, Как только счетчик 68 переходит в нулевое состояние, что определяется путем сравнения его содер- жимого схемой 58 сравнения с нулем, хранящимся в регистре 49, вырабатывается сигнал на выходе схемы 58 сравнения, по которому уменьшается на единицу содержимое счетчика 66. Если счетчик 66 переходит в сГгрица- тельное состояние (что проверяется схемой 56 сравнения), сигнал об это переводит счетчик 40 адреса в счетч

ке 12 цикла в исходное состояние. Если счетчик 66 содержит неотрицательное число и выполняется пятая - команда (сигнал на выходе ключа 64), то осуществляется переход на выполнение третьей команды по сигнал-у, вырабатьтаемому на одиннадцатом выходе коммутатора 15.

Такт генерирования очередной серии импульсов выходного псевдослучайного процесса на основе хранящей- ся в блоке 8 памяти исходной реализации заканчивается установкой счетчика 40 адреса в счетчике 12 цикла в исходное состояние, соответствующее адресу первой команды.

Рассмотрим алгоритм работы устройства .

14

0

5

0 5

0

5

Пусть в (Злоке 8 памяти хранится исходная реализация объемом , т.е. в регистре 6 памяти записано число 5, а значения выборки находятся в ячейках блока 8 памяти с номерами 1,2,3,4,5 соответственно адресам ячеек в памяти. Пусть также количество чисел исходной реализации, подлежащее передаче на выход устройства за один такт генерирования, или число, полученное от цифрового генератора 1 функции одной переменной и записанное в регистр 2 памяти, равно 6 (). Текущий адрес ячейки блока памяти, из которой выбрано последнее число выходной реализации, пусть равно 3 ().

Количество изменений порядка формирования адреса , так как () И-А+К-К4Н ().

Количество чисел, передаваемых при увеличении адресов, равно К 2, Соответственно на вькод устройства передается содержимое 4 и 5-й ячеек блока 8 памяти и устанавливается и .

Затем в связи с тем, что , вычисляется и определяется число ячеек, содержимое Которых переписывается при уменьшении адресов ячеек блока 8 памяти: К Н (), К 4.

Содержимое ячеек с номерами 4,3, 2 и 1 передается на выход генератора псевдослучайных процессов. Устанавливается К к - К 0 и А 1 .

Так как и , такт генерирования заканчивается. На выходе получена пэспедовательность чисел исходной реализации, хранящихся в ячейках 4,5,4,3,2 и 1. На следующем такте генерирования цифровой генератор 1 функции одной переменной вьщает новое число К, что приводит к копированию исходной реализации отрезком новой длины, а это позволяет управлять динамическими (корреляционными) свойствами генерируемой реализации, перестраивая тем самым динамические свойства исходной реализации по необходимым потребителю правилам в ходе процесса генерирования .

Формула изобретения

1. Генератор псевдослучайных процессов, содержащий первый регистр памяти, первый, второй и третий арифметические блоки, второй регистр

151261087

яти, счетчик, последовательно соеенные дешифратор адреса, первый к памяти и третий регистр памяти, следовательно сеединенные датчик

бочего цикла, счетчик цикла, вто й блок памяти и регистр команд, ммутатор, последовательно соединене блок буферной памяти и индексный гистр, выход которого соединен, первым входом коммутатора, первый од которого соединен с входом

to

ко ца от та ла

ч ар вы

су ре вт пе вх ка го не вы до ко су ля ти ро го го с вы хо до тор во ср дин кот ари кот вто рог гис сум сое вых с в тор

счетчика, суммирующий и вычитающий которого соединены соответственно с вторым и третьим выходами коммутатора, четвертый выход которого соединен с первым входом первого регистра памяти, первый, второй и третий выходы которого соединены соответственно с первыми входами первого, второго и третьего арифметических блоков, первый, второй и третий выходы счетчика соединены соответственно с вторыми входами перв ого, второго и третьего арифметических блоков, первый выход второго регистра памяти соединен с третьим входом первого арифметического блока, четвертый вход которого соединен с пятым выходом коммутатора, шестой выход которого соединен с третьим входом третьего арифметического блока, выход которого соединен с первым входом блока буферной памяти, второй вход которого соединен с выходом второго арифметическо го блока, третий вход которого соеднен с вторым выходом второго регистра памяти, вход которого соединен с седьмым выходом коммутатора, .восьмой выход которого соединен с четвертым входом второго арифметического блока, выход первого арифметического блока соединен с третьим входом блока буферной памяти, вы- . ход регистра команд соединен с втог рым входом коммутатора, девятый выход которого соединен с входом дешифратора адреса, отличающийся тем, что, с целью расширения функциональных возможностей за счет управления видом автокорреляционной функции генерируемого процесса, t)H содержит цифровой генератор функции одной переменной, выход которого соединен с вторым входом первого регистра памяти, вход цифрового генератора функции одной переменной соединен с десятым выходом

to

16

коммутатора, одиннадцатый и двенадцатый выходы которого соединены соответственно с первым и BTopbtM установочными входами счетчика цикла,

2. Генератор по п.1, отличающийся тем, что, первый арифметический, блок содержит первый, второй, третий и четвертый

15

20

25

30

35 40

5

0

5

сумматоры, первый, второй и третий регистры, схему сравнения, первый, второй и третий ключи, первый вход первого сумматора является первым входам первого арифметического блока и соединен с первым входом третьего сумматора, выход которого соединен с первым входом первого ключа, выход которого соединен с первым входом первого регистра, второй вход которого соединен с выходом первого сумматора, второй вход которого является вторым входом первого арифметического блока, четвертый вход которого соединен с третьим входом первб- го сумматора и первым входом третьего регистра, выход которого соединен с первым входом второго ключа и первым входом четвертого сумматора, выход которого соединен с первым входом третьего ключа, второй вход которого соединен с вторым входом первого ключа и первым выходом схемы сравнения, второй выход которой соединен с входом второго ключа, выход которого является выходом первого арифметического блока, третий вход которого соединен с первым входом второго сумматора, второй вход которого соединен с выходом первого регистра и вторьм входом третьего сумматора, выход второго сумматора соединен с входом схемы сравнения, выход второго «регистра соединен с вторым входом четвертого сумматора .

3. Генератор по п.. 1, отличающийся тем, что второй арифметический блок содержит первый и второй сумматоры, схему сравнения, первый и йторой ключи, первый вход первого сумматора является третьим входом второго арифметического блока и соединен с первым входом второго сумматора, второй вход которого соединен с первым входом первого ключа и выходом первого сумматора, второй вход которого является вторым входом второго арифметического

блока, первый вход которого соединен с первым входом второго ключа, выход которого объединен с выходом первого ключа и соединен с выходом второго арифметического блока, четвертый вход которого соединен с вторыми входами первого и второго ключей, третьи входы которых соединены соответственно с первым и вторым выходами схемы сравнения, вход которой соединен с выходом второго сумматора..

4. Генератор поп.1, отличающийся тем, что третий арифметический блок содержит первый и второй сумматоры, регистр, схему сравнения, первый и второй ключи, выход регистра соединен с первым входом первого сумматора, выход котрого соединен с первым входом перво го ключа и первым входом второго сумматора, выход которого соединен с входом схемы сравнения, первый выход которой соединен с вторьм входом первого ключа, вькод которого объединен с выходом второго ключа и соединен с выходом третьего арифметического блока, третий вход которого соединен с третьим входом первого ключа и первым входом второго ключа, второй вход которого соедине с вторым выходом схемы сравнения, третий вход второго ключа соединен с вторым входом второго сумматора и является первым входом третьего арифметического блока, второй вход которого соединен с вторым входом первого сумматора.

5.Генератор по п.1, о т л и - чающийся тем, что счетчик цикла содержит счетчик адреса, схему сравнения и регистра адреса, выход которого соединен с первым входом схемы сравнения, выход которой . соединен с первым входом счетчика адреса и является вторым установочным входом счетчика цикла, первый установочный вход которого соединен с вторым входом счетчика адреса, выход которого соединен с вторым вхо.: дом схемы сравнения и является выходом счетчика цикла, вход которого соединен с третьим входом счетчика адреса.

6.Генератор по п.1, отличающийся тем, что коммутатор содержит у-тыре линии задержки, шесть регистров, восемь схем сравне0

5

0

5

0

5

0

5

ния, пять ключей, три счетчика, два регистра адреса, первый вход первого ключа является первым входом коммутатора и соединен с первыми входами второго и пятого ключей, выходы которых соединены соответственно с первыми входами второго и третьего счет.чиков, вторые входы которых соединены соответственно с выходами четвертой и третьей линий задержки, выход первого регистра соединен с первым входом первой схемы сравн,-:- ния, первый выход которой соединен с первым входом второй схемы сравнения, второй вход которой соединен с выходом второго регистра, второй вход коммутатора соединен с вторым входом первой схемы сравнения, второй выход которой соединен с вторым входом первого ключа, десятым выходом коммутатора и входом первой линии задержки, вьпсод которой является первым, четвертым, седьмым выходами коммутатора и соединен через вто- рую линию задержки с пятым выходом коммутатора, восьмой выход которого соединен с вторым входом второго ключа и первым выходом второй схемы сравнения, второй выход которой соединен с первым входом пятой схемы сравнения, второй вход которой соединен с выходом четвертого регистра, выход пятого регистра соединен с первым входом седьмой схемы сравнения, второй вход которой соединен с nep- i вым выходом пятой схемы сравнения, второй выход которой соединен с вторым входом пятого ключа и шестым выходом коммутатора, второй выход которого соединен с входом первого регистра адреса, первым выходом третьей схемы сравнения, входом четвертой линии задержки и первым выходом седьмой схемы сравнения, второй выход которой соединен с первым входом восьмой схемы сравнения, второй вход которой соединен с выходом шестого регист|ра, выход первого регистра ад- реса является девятым выходом комму- |Татора и объединен с выходом второго регистра адреса, вход которого соединен с третьим выходом коммутатора, входом третьей линии задержки, первым выходом шестой схемы сравнения, выходом третьего ключа и первым выходом восьмой схемы сравнения, второй выход которой объединен с первым выходом четвертой схемы сравнения

19

и является двенадцатым выходом коммутатора, одиннадцатый выход которого соединен с выходом четвертого ключа, первый вход которого соединен с первым входом третьего ключа и вторым выходом четвертой схемы сравнения, первый вход котррой соеди иен с выходом первого счетчика, первый вход которого соединен с вторым входом третьего ключа и вторым выходом третьей схемы сравнения, первый вход которой соединен с выходом

второго счетчика, выход третьего счетчика соединен с первым входот4 шестой схемы сравнения, второй вход которой соединен с выходом третьего 5 регистра, вторым входом третьей схемы сравнения и вторым входом четвертой схемы сравнения, выход первого ключа соединен с вторым входом первого счетчика, третий вход кото- 10 рого соединен с вторьш входом четвертого ключа и вторым выходом шестой схемы сравнения.

Г

f

ou

г5ИН

фц1,2

32

1

t I

30

31

33

I

ф1/«. J

ф(/г. If

Фиг. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Многопроцессорная вычислительная система | 1979 |

|

SU751238A1 |

| Адаптивный передатчик телеметрической информации | 1985 |

|

SU1282185A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство управления контролем | 1985 |

|

SU1285471A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2018 |

|

RU2708956C2 |

Изобретение относится к импульсной технике. Цель изобретения - расширение функциональных возможностей , за счет управления видом автокорреляционной функции генерируемого процесса. Для достижения данной цели в генератор псевдослучайных чисел, со-- держапрй первый 3, второй 4 и третий 5 арифметические блоки, первый регистр 2 памяти, второй регистр 6 памяти, счетчик 7, первый блок 8 памяти, депшфратор 9 адреса, третий регистр 10 памяти, датчик 11 рабочего цикла, счетчик 12 цикла, второй блок памяти 13, регистр 14 команд, ком- мутатор 15, блок 16 буферной памяти. с (Л С

/г

фие.е

Составитель Ю. Бурмистров Редактор Н. Швыдкая Техред М.Ходанич Корректор, А. Тяско

Заказ 5243/56 Тираж 816 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Генератор случайных чисел | 1974 |

|

SU516042A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор псевдослучайных процессов | 1980 |

|

SU960810A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой генератор функций времени | 1974 |

|

SU506015A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-30—Публикация

1984-11-22—Подача