со

«

00

оо to

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам для считьшания информации, и может быть использова- но для ввода графических и фотографических изображений в ЭВМ.

Целью изобретения является повьше- ние точности устройства.

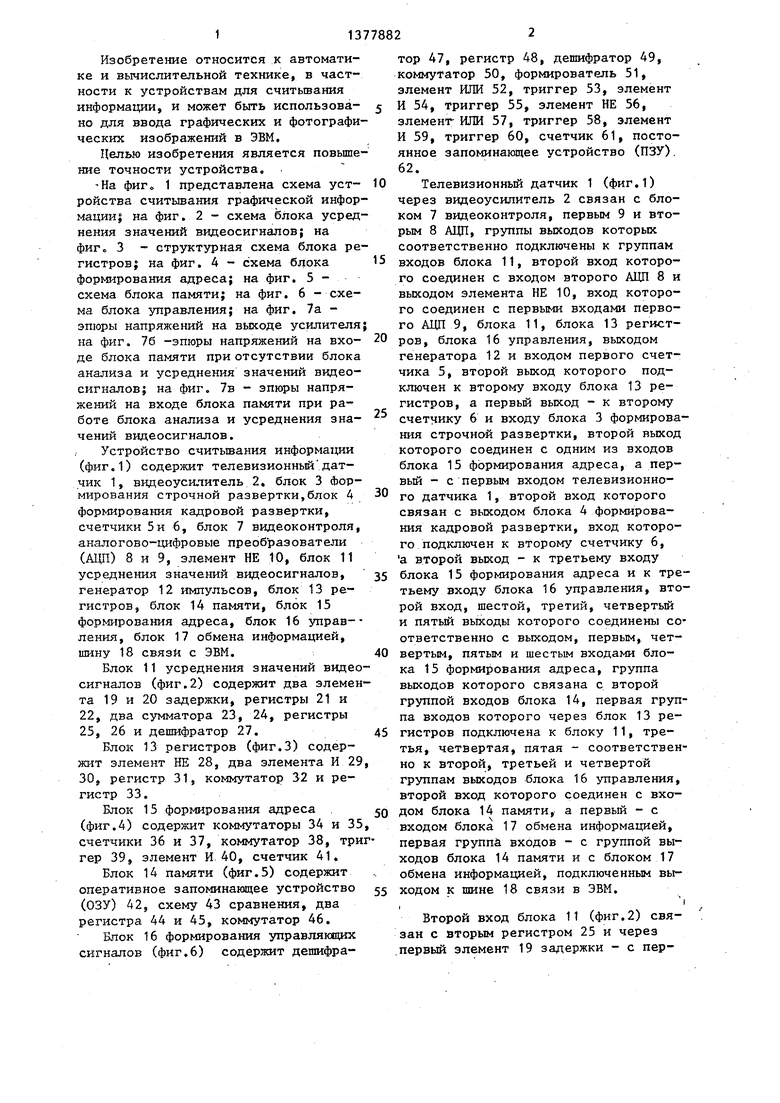

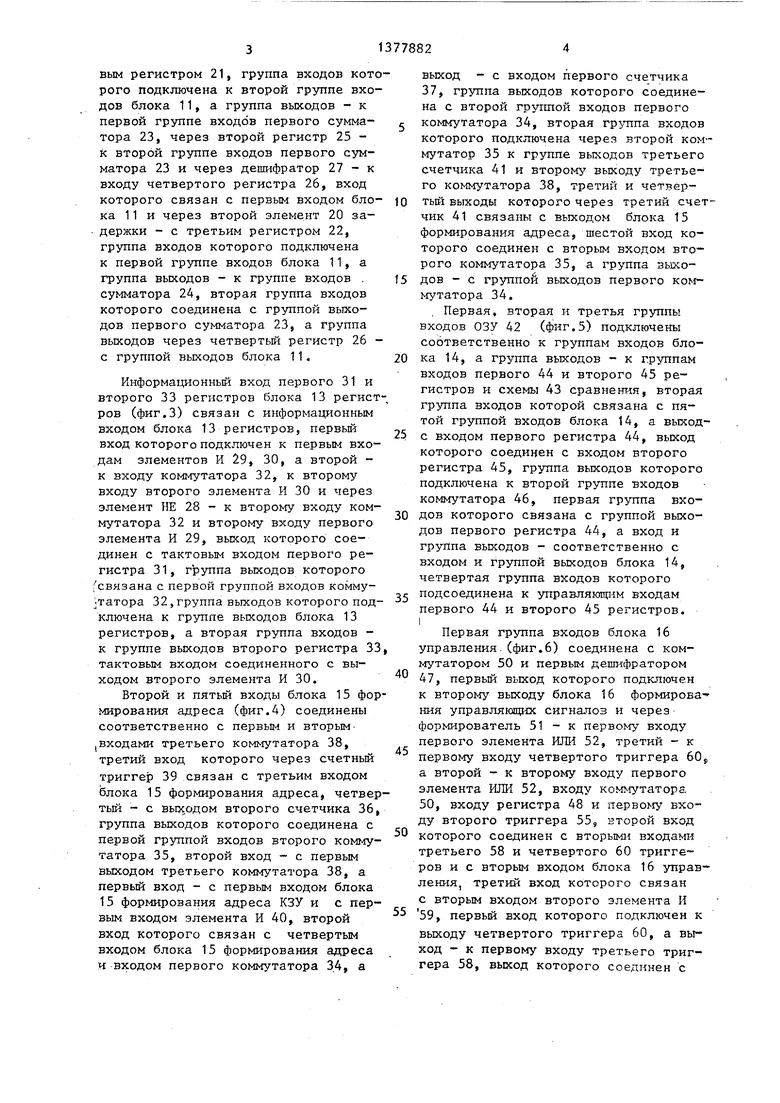

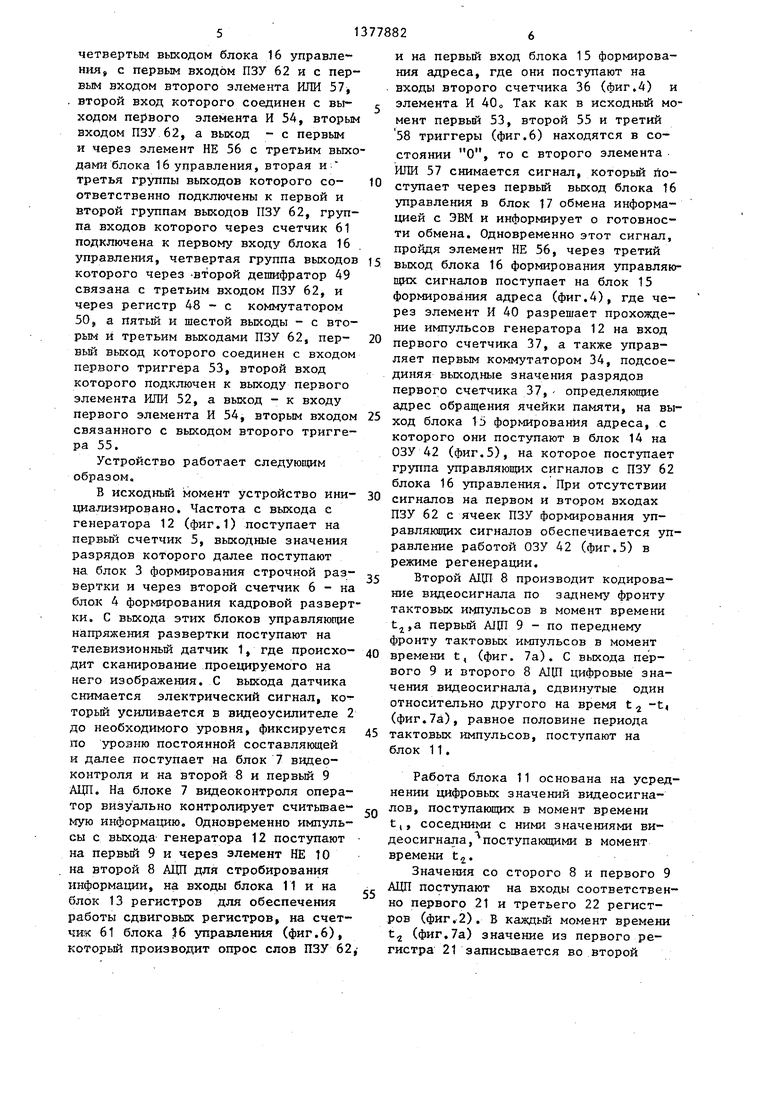

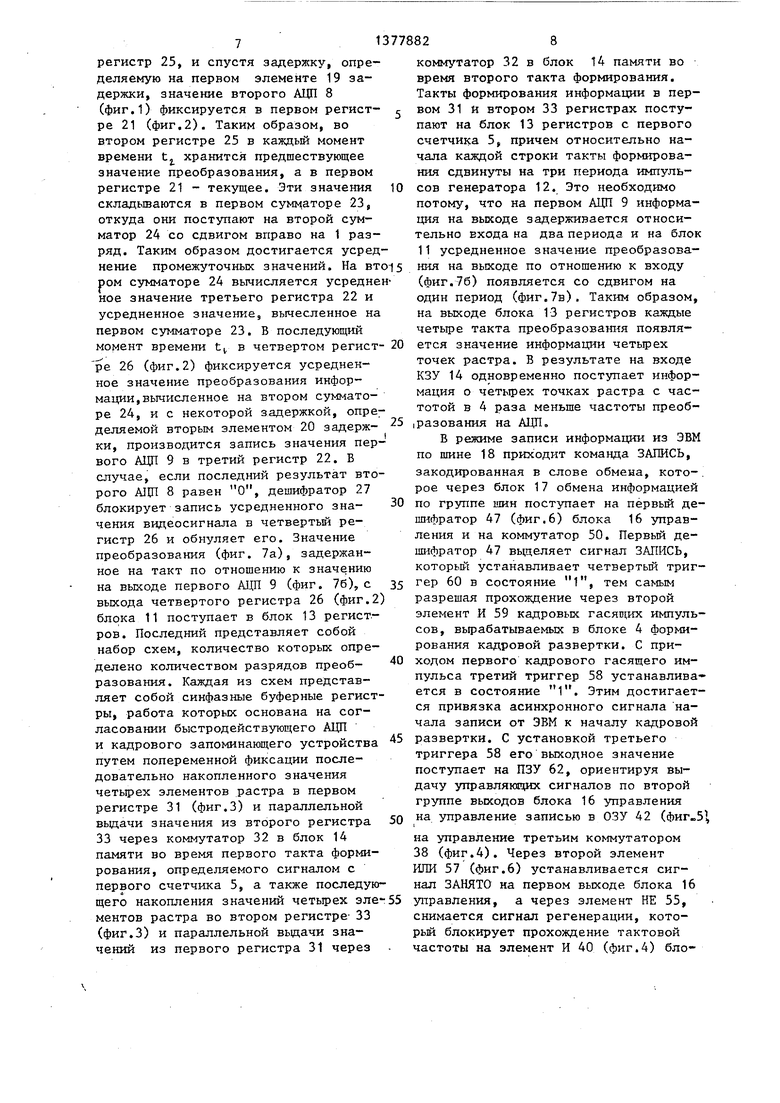

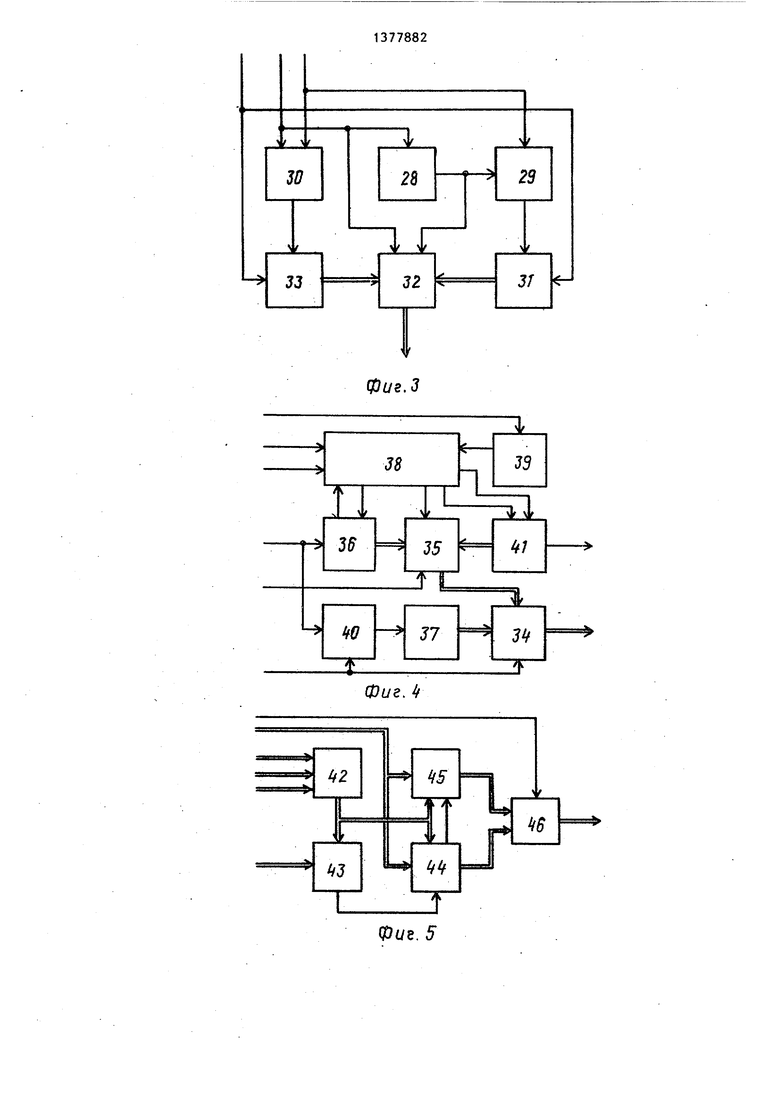

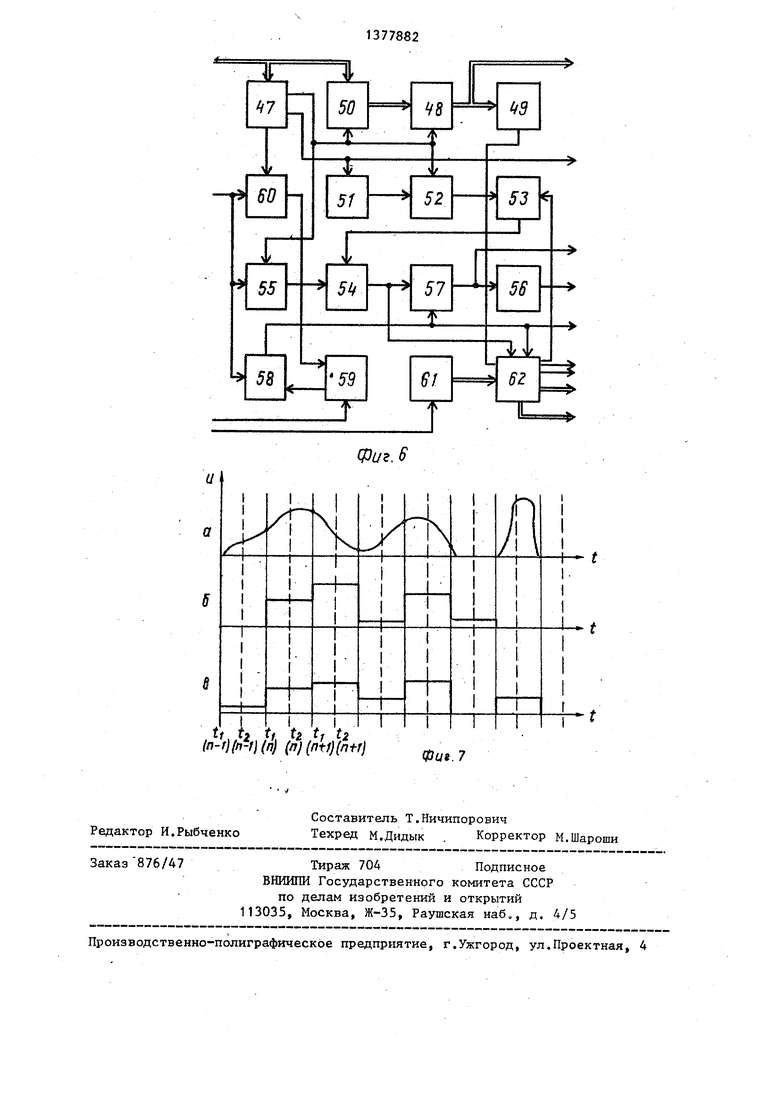

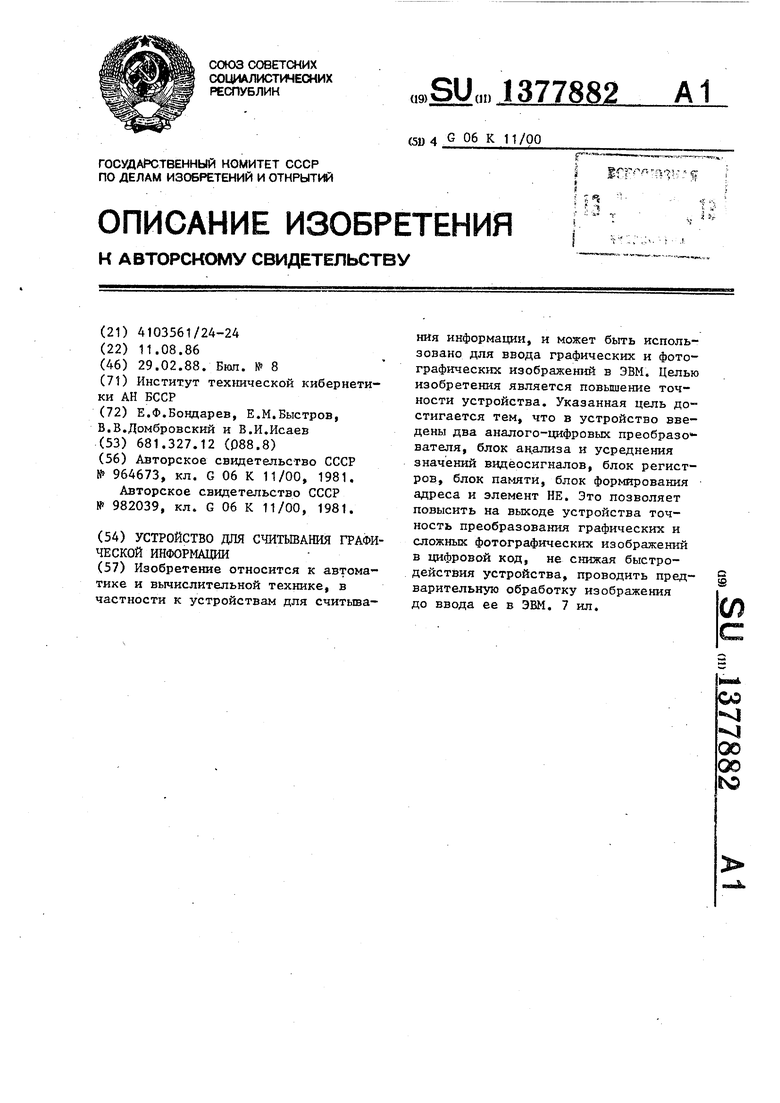

-На фиг, 1 представлена схема уст- ройства считывания графической инфор- мации; на фиг. 2 - схема блока усреднения значений видеосигналов; на фиг. 3 - структурная схема блока регистров; на фиг. А - схема блока формирования адреса; на фиг. 5 - схема блока памяти; на фиг. 6 - схема блока з равления; на фиг. 7а - эпюры напряжений на выходе усилителя} на фиг. 76 -эпюры напряжений на вхо- де блока памяти при отсутствии блока анализа и усреднения значений видеосигналов; на фиг. 7в - эпюры напряжений на входе блока памяти при работе блока анализа и усреднения зна- чений видеосигналов.

Устройство считьгоания информации (фиг.1) содержит телевизионный датчик 1, видеоусилитель 2. блок 3 бор- мирования строчной развертки,блок А формирования кадровой развертки, счетчики 5и 6, блок 7 видеоконтроля, аналогово-цифровые преоб разователи (АЦП) 8 и 9, элемент НЕ 10, блок 11 усреднения значений видеосигналов, Генератор 12 импульсов, блок 13 регистров, блок 14 памяти, блок 15 формирования адреса, блок 16 управ-- ления, блок 17 обмена информацией, шину 18 связи с ЭВМ.

Блок 11 усреднения значений видеосигналов (фиг.2) содержит два элемента 19 и 20 задержки, регистры 21 и 22, два сумматора 23, 24, регистры 25, 26 и дешифратор 27.

Блок 13 регистров (фиг.З) содержит элемент НЕ 28, два элемента И 29, 30, регистр 31, коммутатор 32 и регистр 33.

Блок 15 формирования адреса . (фиг.4) содержит коммутаторы 34 и 35, счетчики 36 и 37, коммутатор 38, триггер 39, элемент И 40, счетчик 41,

Блок 14 памяти (фиг.З) содержит оперативное запоминающее устройство (ОЗУ) 42, схему 43 сравнения, два регистра 44 и 45, коммутатор 46.

Блок 16 формирования управляющих сигналов (фиг.6) содержит дешифратор 47, регистр 48, дешифратор 49, коммутатор 50, формирователь 51, элемент ИЛИ 52, триггер 53, элемент И 54, триггер 55, элемент НЕ 56, элемент ИЛИ 57, триггер 58, элемент И 59, триггер 60, счетчик 61, постоянное запоминающее устройство (ПЗУ). 62.

Телевизионный датчик 1 (фиг.1) через видеоусилитель 2 связан с блоком 7 видеоконтроля, первым 9 и вторым 8 АЦП, группы выходов которых соответственно подключены к группам входов блока 11, второй вход которого соединен с входом второго АЦП 8 и выходом элемента НЕ 10, вход которого соединен с первыми входами первого АЦП 9, блока 11, блока 13 регистров, блока 16 управления, выходом генератора 12 и входом первого счетчика 5, второй вькод которого подключен к второму входу блока 13 регистров, а первый выход - к второму счетчику 6 и входу блока 3 формирования строчной развертки, второй выход которого соединен с одним из входов блока 15 формирования адреса, а первый - с первым входом телевизионного датчика 1, второй вход которого связан с выходом блока 4 формирования кадровой развертки, вход которого подключен к второму счетчику 6, а второй выход - к третьему входу блока 15 формирования адреса и к третьему входу блока 16 управления, второй вход, шестой, третий, четвертый и пятый выходы которого соединены соответственно с выходом, первым, четвертым, пятым и шестым входами блока 15 формирования адреса, группа вькодов которого связана с второй группой входов блока 14, первая группа входов которого через блок 13 регистров подключена к блоку 11, третья, четвертая, пятая - соответственно к второй, третьей и четвертой группам выходов блока 16 управления, второй вход которого соединен с входом блока 14 памяти, а первый - с входом блока 17 обмена информацией, первая группа входов - с группой выходов блока 14 памяти и с блоком 17 обмена информацией, подключенным выходом к шине 18 связи в ЭВМ. ,

Второй вход блока 11 (фиг.2) связан с вторым регистром 25 и через .первый элемент 19 задержки - с первым регистром 21, группа входов которого подключена к второй группе входов блока 11, а группа выходов - к первой группе входов первого сумматора 23, через второй регистр 25 - к второй группе входов первого сумматора 23 и через дешифратор 27 - к входу четвертого регистра 26, вход которого связан с первым входом блока 1 1 и через второй элемент 20 задержки - с третьим регистром 22, группа входов которого подключена к первой группе входов блока 11, а группа выходов - к группе входов . сумматора 24, вторая группа входов которого соединена с группой выходов первого сумматора 23, а группа выходов через четвертьй регистр 26 - с группой выходов блока 11«

Информационньй вход первого 31 и второго 33 регистров блока 13 регистров (фиг.З) связан с информационным входом блока 13 регистров, первьй вход которого подключен к первым входам элементов И 29, 30, а второй - к входу коммутатора 32, к второму входу второго элемента И 30 и через элемент НЕ 28 - к второму входу коммутатора 32 и второму входу первого элемента И 29, выход которого соединен с тактовым входом первого регистра 31, группа выходов которого связана с первой группой входов комму- татора 32,группа выходов которого подключена к группе выходов блока 13 регистров, а вторая группа входов - к группе выходов второго регистра 33 тактовым входом соединенного с выходом второго элемента И 30.

Второй и пятый входы блока 15 формирования адреса (фиг.4) соединены соответственно с первым и вторым- (Входами третьего коммутатора 38, третий вход которого через счетньй триггер 39 связан с третьим входом блока 15 формирования адреса, четвертьй - с выходом второго счетчика 36, группа выходов которого соединена с первой группой входов второго коммутатора 35, второй вход - с первым выходом третьего коммутатора 38, а первьй вход - с первым входом блока 15 формирования адреса КЗУ и с первым входом элемента И 40, второй вход которого связан с четвертым входом блока 15 формирования адреса и входом первого коммутатора 34, а

0

5

0

5

0

5

0

5

0

5

выход - с входом первого счетчика 37, группа выходов которого соединена с второй гругшой входов первого коммутатора 34, вторая группа входов которого подключена через второй коммутатор 35 к группе выходов третьего счетчика 41 и второму выходу третьего коммутатора 38, третий и четвертьй выходы которого через третий счетчик 41 связаны с выходом блока 15 формирования адреса, шестой вход которого соединен с вторым входом второго коммутатора 35, а группа выходов - с группой выходов первого коммутатора 34.

Первая, вторая и третья группы входов ОЗУ 42 (фиг.5) подключены собтветственно к группам входов блока 14, а группа выходов - к группам входов первого 44 и второго 45 регистров и схемы 43 сравнения, вторая группа входов которой связана с пятой группой входов блока 14, а выход- с входом первого регистра 44, выход которого соединен с входом второго регистра 45, группа выходов которого подключена к второй группе входов коммутатора 46, первая группа входов которого связана с группой выходов первого регистра 44, а вход и группа выходов - соответственно с входом и группой выходов блока 14, четвертая группа входов которого подсоединена к управляющим входам первого 44 и второго 45 регистров.

Первая группа входов блока 16 управления.(фиг.6) соединена с коммутатором 50 и первым дешифратором 47, первьй выход которого подключен к второму выходу блока 16 формирова- ния управляющее сигналов и через формирователь 51 - к первому входу первого элемента ИЛИ 52, третий - к первому входу четвертого триггера 60 а второй - к второму входу первого элемента ИЛИ 52, входу коммутатора. 50, входу регистра 48 и первому входу второго триггера 55, второй вход которого соединен с вторыми входами третьего 58 и четвертого 60 триггеров и с вторым входом блока 16 управления, третий вход которого связан с вторым входом второго элемента И 59, первьй вход которого подключен к выходу четвертого триггера 60, а выход - к первому входу третьего триггера 58, выход которого соединен с

четвертым вькодом блока 16 управления, с первым входом ПЗУ 62 и с первым входом второго элемента ИЛИ 57 второй вход которого соединен с выходом первого элемента И 54, вторым входом ПЗУ 62, а выход - с первым и через элемент НЕ 56 с третьим выходами блока 16 управления, вторая и третья группы выходов которого соответственно подключены к первой и второй группам выходов ПЗУ 62, группа входов которого через счетчик 61 подключена к первому входу блока 16 управления, четвертая группа вькодов которого через -второй дешифратор 49 связана с третьим входом ПЗУ 62, и через регистр 48 - с коммутатором 50, а пятый и шестой выходы - с вторым и третьим выходами ПЗУ 62, первый выход которого соединен с входом первого триггера 53, второй вход которого подключен к выходу первого элемента ШШ 52, а выход - к входу первого элемента И 54, вторым входом связанного с выходом второго триггера 55.

Устройство работает следующим образом.

В исходньй момент устройство ини- циализировано. Частота с выхода с генератора 12 (фиг.1) поступает на первый счетчик 5, выходные значения разрядов которого далее поступают на блок 3 формирования строчной раз- вертки и через второй счетчик 6 - на блок 4 формирования кадровой развертки. С выхода этих блоков управляющие напряжения развертки поступают на телевизионный датчик 1, где происходит сканирование проецируемого на него изображения. С выхода датчика снимается электрический сигнал, ко- торый усиливается в видеоусилителе 2 до необходимого зФовня, фиксируется по уровню постоянной составляющей и далее поступает на блок 7 видеоконтроля и на второй 8 и первый 9 АЦП, На блоке 7 видеоконтроля оператор визу ально контролирует считываемую информацию. Одновременно импульсы с выхода генератора 12 поступают на первый 9 и через элемент НЕ 10 на второй 8 АЦП для стробирования информации, на входы блока 11 и на блок 13 регистров для обеспечения работы сдвиговых регистров, на счет- чиж 61 блока .16 управления (фиг,6), который производит опрос слов ПЗУ 62

0

5

0

5

О

0

5

0

5

и на первый вход блока 15 формирования адреса, где они поступают на входы второго счетчика 36 (фиг.4) и элемента И 40о Так как в исходный момент первый 53, второй 55 и третий 58 триггеры (фиг.6) находятся в состоянии О, то с второго элемента ИЛИ 57 снимается сигнал, который rto- ступает через первый выход блока 16 управления в блок 17 обмена информацией с ЭВМ и информирует о готовности обмена. Одновременно этот сигнал, пройдя элемент НЕ 56, через третий выход блока 16 формирования управляющих сигналов поступает на блок 15 формирования адреса (фиг.4), где через элемент И 40 разрешает прохождение импульсов генератора 12 на вход первого счетчика 37, а также управляет первым коммутатором 34, подсоединяя выходные значения разрядов первого счетчика 37,- определяющие адрес обращения ячейки памяти, на выход блока 15 формирования адреса, с которого они поступают в блок 14 на ОЗУ 42 (фиг.5), на которое поступает группа управляющих сигналов с ПЗУ 62 блока 16 управления. При отсутствии сигналов на первом и втором входах ПЗУ 62 с ячеек ПЗУ формирования управляющих сигналов обеспечивается управление работой ОЗУ 42 (фиг.5) в режиме регенерации.

Второй АЦП 8 производит кодирование видеосигнала по заднему фронту тактовых импульсов в момент времени tj,a первый АЦП 9 - по переднему фронту тактовых импульсов в момент времени t, (фиг. 7а). С выхода первого 9 и второго 8 АЦП цифровые значения видеосигнала, сдвинутые один относительно другого на время t -t« (фиг,7а), равное половине периода тактовых импульсов, поступают на блок 11.

Работа блока 11 основана на усреднении цифровых значений видеосигналов, поступающих в момент времени t,, соседними с ними значениями видеосигнала,поступающими в момент времени t.

Значения со сторого 8 и первого 9 АЦП поступают на входы соответственно первого 21 и третьего 22 регистров (фиг.2), В каждый момент времени t (фиг,7а) значение из первого регистра 21 записьшается во второй

регистр 25, и спустя задержку, определяемую на первом элементе 19 задержки, значение второго АЦП 8 (фиг,1) фиксируется в первом регист- ре 21 (фиг,2). Таким образом, во втором регистре 25 в каждый момент времени tj, хранится предшествующее значение преобразования, а в первом регистре 21 - текущее. Эти значения складьшаются в первом сумматоре 23, откуда они поступают на второй сумматор 24 со сдвигом вправо на 1 разряд. Таким образом достигается усреднение промежуточных значений. На вт ром сумматоре 24 вычисляется усредненое значение третьего регистра 22 и усредненное значение, вычесленное на первом сумматоре 23. В последующий момент времени t,, в четвертом регист- ре 26 (фиг.2) фиксируется усредненное значение преобразования информации, вычисленное на втором сумматоре 24, и с некоторой задержкой, определяемой вторым элементом 20 задержки, производится запись значения первого АЦП 9 в третий регистр 22. В случае, если последний результат второго АЦП 8 равен О, дешифратор 27 блокирует запись усредненного значения видеосигнала в четвертьй регистр 26 и обнуляет его. Значение преобразования (фиг. 7а), задержанное на такт по отношению к значению на выходе первого АЦП 9 (фиг. 76), с выхода четвертого регистра 26 (фиг.2) блока 11 поступает в блок 13 регистров. Последний представляет собой набор схем, количество которых определено количеством разрядов преобразования. Калсдая из схем представляет собой синфазные буферные регистры, работа которых основана на согласовании быстродействующего АЦП и кадрового запоминающего устройства путем попеременной фиксации последовательно накопленного значения четырех элементов растра в первом регистре 31 (фиг.З) и параллельной выдачи значения из второго регистра 33 через коммутатор 32 в блок 14 памяти во время первого такта формирования, определяемого сигналом с первого счетчика 5, а также последую

г 0 5 00

0

5

0

5

коммутатор 32 в блок 14 памяти во время второго такта формирования. Такты формирования информации в первом 31 и втором 33 регистрах поступают на блок 13 регистров с первого счетчика 5, причем относительно начала каждой строки такты формирования сдвинуты на три периода импульсов генератора 12. Это необходимо потому, что на первом АЦП 9 информация на выходе задерживается относительно входа на два периода и на блок 11 усредненное значение преобразования на выходе по отношению к входу (фиг.76) появляется со сдвигом на один период (фиг.7в). Таким образом, на выходе блока 13 регистров каждые четыре такта преобразоваш-гя появляется значение информации четырех точек растра. В результате на входе КЗУ 14 одновременно поступает информация о четырех точках растра с частотой в 4 раза меньще частоты преоб- |разования на АЦП„

В режиме записи информации из ЭВМ по шине 18 приходит команда ЗАПИСЬ, закодированная в слове обмена, кото-, рое через блок 17 обмена информацией по группе шин поступает на первый дешифратор 47 (фиг,6) блока 16 управления и на коммутатор 50. Первый дешифратор 47 вьщеляет сигнал ЗАПИСЬ, который устанавливает четвертый триггер 60 в состояние 1, тем самым разрешая прохождение через второй элемент И 59 кадровых гасящих импульсов, вырабатываемых в блоке 4 формирования кадровой развертки. С приходом первого кадрового гасящего импульса третий триггер 58 устанавливается в состояние 1. Этим достигается привязка асинхронного сигнала начала записи от ЭВМ к началу кадровой развертки. С установкой третьего триггера 58 его выходное значение поступает на ПЗУ 62, ориентируя выдачу управляющих сигналов по второй группе выходов блока 16 управления на управление записью в ОЗУ 42 (

на управление третьим коммутатором 38 (фиг.4). Через второй элемент ИДИ 57 (фиг.6) устанавливается сигнал ЗАНЯТО на первом выходе блока 16

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| ТЕПЛОВИЗОР НА ОСНОВЕ "СМОТРЯЩЕЙ" МАТРИЦЫ ФОРМАТА 256Х256 | 2011 |

|

RU2454022C1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ТЕЛЕВИЗИОННЫХ ОПТИЧЕСКИХ СИСТЕМ | 1991 |

|

RU2010448C1 |

| Устройство для обработки видеоинформации | 1988 |

|

SU1640714A1 |

| Устройство для ввода и вывода цветной графической информации | 1986 |

|

SU1348873A1 |

| Устройство для ввода и вывода цветной графической информации | 1985 |

|

SU1315964A1 |

| Устройство для ввода и вывода изображений объектов | 1990 |

|

SU1829045A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР УСРЕДНЕННОЙ МОЩНОСТИ НЕСТАЦИОНАРНОЙ НАГРУЗКИ | 1992 |

|

RU2060542C1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам для считьгоания информации, и может быть использовано для ввода графических и фотографических изображений в ЭВМ. Целью изобретения является повышение точности устройства. Указанная цель достигается тем, что в устройство введены два аналого-цифровых преобразо - вателя, блок ак.ализа и усреднения значений видеосигналов, блок регистров, блок памяти, блок формирования адреса и элемент НЕ. Это позволяет повысить на выходе устройства точность преобразования графических и сложных фотографических изображений в цифровой код, не снижая быстродействия устройства, проводить предварительную обработку изображения до ввода ее в ЭВМ. 7 ил. с S (Л

щего накопления значений четьфех эле-55 управления, а через элемент НЕ 55,

ментов растра во втором регистре- 33 (фиг.З) и параллельной вьщачи значений из первого регистра 31 через

снимается сигнал регенерации, кото- рьй блокирует прохождение тактовой частоты на элемент И 40 (фиг.4) бло

снимается сигнал регенерации, кото- рьй блокирует прохождение тактовой частоты на элемент И 40 (фиг.4) бло

ка 15 формирования адреса. На первом коммутаторе ЗА выходное значение адреса обращезшя к ячейке памяти подключается к второму ког- мутатору 35, на первую группу входов которого поступает значение с второго счетчика 36, на вторзто группу входов поступает значение с третьего счетчй-

триггеры устанавливаются в исходное состояние, тем самым снимая управляющие сигналы занятости устройства, а следовательно, выставляя сигнал регенерации, коммутируя третий коммутатор 38 (фиг.4) и управляя ПЗУ 62 (фиг.5), определяя работу ОЗУ 42 (фиг.5) посредством управляющих сигка 41 и младший разряд адреса с тре- 10 налов с ПЗУ 62 (фиг.5) в режиме регетьего коммутатора 38. Управление переключением групп шин осуществляется по сигналу с ПЗУ 62 (фиг.6). Таким образом, второй счетчик 36 (фиг.А)

нера1щи, как было описано вьппе.

I ,

В режиме чтения информации из ЭВМ по группе шин поступает команда

определяет адрес строк ОЗУ 42 (фиг.5) 15 ЕНИЕ, закодированная в слове обмеа третий счетчик 41 определяет адрес столбцов ОЗУ 42. В режиме записи третий комментатор 38 (фиг.4) подключает младший разряд адреса столбцов памяти к счетному триггеру 39. Это необходимо потому, что с использованием стандартной телевизионной камеры изображе}ще читается за два полукадра, В первом полукадре, когда счетньй триггер 39 находится в исходном состоянии запись в память определена в четные столбцы, с приходом второго полукадра кадровым гасящим импульсом счетньш триггер 39 устанавливается в состояние 1, тем самым определяя запись в нечетные столбцы памяти. В режиме записи, памяти и чтения из памяти условия формирования адреса неоднозначны. В режиме записи третий коммутатор 38 подключает на счетный вход третьего счетчика 41 строчные гасящие импуль- сЫр йа сбросовый вход - кадровый гасящий импульс информации, а на сбросовый вход второго счетчика 36 - строчные гасящие импульсы. С начала формирования управляющих сигналов записи и адресов ОЗУ 42 (фиг.5), на вход которого поступает цифровое значение информации, усредненное в блоке 11 (фиг,1) и сбуферргрованное в блоке 13 регистров, происходит запись информации в ячейки памяти, причем запись производится с частотой, в 4 раза меньшей частоты- тактирова-- ния с учетом задержки информации с телевизионного датчика 1 на первом АЩ 9 5 на блоке 11 и задержки на 4 периода тактовой частоты (накопления первых .четырех точек растра) в блоке 13 регистров. С переполнением третьего счетчика 41 (фиг.4) на .его выходе вьграбатывается сигнал, по которому четвертый 60 (фиг.6) и третий 58

триггеры устанавливаются в исходное состояние, тем самым снимая управляющие сигналы занятости устройства, а следовательно, выставляя сигнал регенерации, коммутируя третий коммутатор 38 (фиг.4) и управляя ПЗУ 62 (фиг.5), определяя работу ОЗУ 42 (фиг.5) посредством управляющих сигналов с ПЗУ 62 (фиг.5) в режиме регенера1щи, как было описано вьппе.

I ,

В режиме чтения информации из ЭВМ по группе шин поступает команда

0

5

0

5

0

5

0

5

на, которая вьщеляется на первом дешифраторе 47 (фиг.6), устанавливая второй триггер 55 и через первьй элемент ИЛИ 52 первый триггер 53. Одновременно с приходом этой команды в слове обмена выделяется значение порога цифрования при двухуровневом вводе информации об изображении в ЭВМ, которое, пройдя коммутатор 50, фиксируется в регистре 48. Значение порога цифрования по четвертой группе шин поступает на схему 43 сравнения блока ,14 (фиг, 5), С установкой первого 53 и второго 55 триггеров (фиг.6) с первого элемента И 54 вьцтеляется сигнал, по которому через второй элемент ИЛИ 57 устанавливается сигнал занятости устройства и далее через элемент НЕ 55 снимается сигнал регенерации, который также поступает на ЛЗУ 62, тем самым определяя вьщачу управляющих сигналов с ПЗУ 62 на работу ОЗУ 42 (фиг.5) в режиме чтения информации, а также формируя управляющие сигналы, которые поступают на регистры 44 и 45 буферирования данных для ЭВМ, Значение порога цифрования, хранимого в .регистре 48 (фиг.6), дешифруется на втором дешифраторе 49, тем самым определяя посредством ПЗУ 62 формирование управляющих сигналов регистров 44 и 45 (фиг,5), Это необходимо потому, что при двухуровневом преобразовании информации об изображении B. регистрах 44 и 45 последовательно формируются данные из 16 точек растра, хранимых в 16 х 8 ячейках памяти ОЗУ 42. Причем каждая точ- ,ка растра сравнивается в схеме 43 сравнения с пороговым значением и результат сравнения поступает на вход первого регистра 44, связанного с вторым регистром 45, которые работают в режиме сдвига. В режиме передачи многоградационного изображения на втором дешифраторе 49 (фиг,6) регистрируется О значение, а данные формируются параллельной записью (двух точек растра) в первый 44 и вт рой 45 регистры (фиг.5). Формирование адреса оперативной памяти происходит аналогично, только третий коммутатор 38 (фиг.4) в отсутствие сигнала записи организует работу третьего счетчика 41 так, что на его счетный вход поступает переполнение второго счетчика 36, на счетньй вход которого, в свою очередь, поступает сигнал, вырабатьшаемьй на ПЗУ 62 (фиг.6). Второй 36 и третий 41 (фиг, счетчики сбрасьтают по команде ЧТЕНИЕ.

По окончании формирования слова обмена из ПЗУ 62 (фиг.6) вьщеляется сигнал, который устанавливает первый триггер 53 в исходное состояние,тем самым снимая через первьй элемент И 54 сигнал управления считьшанием с ПЗУ 62, а через второй элемент ИЛИ 57 сигнал занятости устройства и далее через элемент НЕ 55 устанавливая сигнал регенерации. По окончании занятости устройства ЭВМ по шине 18 через блок 17 производит опрос информации с устройства. На первом дешифраторе 47 блока 16 (фиг,6) выделяется сигнал опроса, по окончании которого на формирователе 51 выделяеся задний фронт этого сигнала, по которому устанавливается первьй триггер 53 в состояние 1, тем самым формируя следующее слово обмена и т.д. По окончании считывания информации из ОЗУ 42 на третьем счетчике 41 формируется сигнал, по которому второй триггер 55 устанавливается в исходное состояние, блокируя прохождение управляюпщх сигналов с первого триггера 53 через первьй элемент И 54 и тем самым прекращая обращение к ОЗУ для формирования очередных: сло обмена.

За все время обращения к ОЗУ 42 первьй счетчик 37 (фиг,4), определяющий ячейки регенерации памяти, блокируется таким образом, что новый цикл регенерации начинается с ячейки, адрес которой определен накопленным значением первого счетчика 37. Этим

0

s

0

5

0

5

0

5

0

достигается регенерация всех ячеек памяти в необходимое время.

Формула изо б.р е т е н и я

Устройство для считывания графической информации, содержащее телеви- зионньй датчик, выход которого соединен с входом видеоусилителя, выход которого подключен к информационным входам первого аналого-цифрового преобразователя и блока видеоконтроля, последовательно соединенный первьй и второй счетчики, выходы которых подключены соответственно к управляющим входам блоков формирования строчной и кадровой разверток, первые выходы которых соединены соответственно с входами управления разверткой телевизионного датчика, генератор импульсов, выход которого подключен к счетному входу первого счетчика, и блок управления, выходы первой группы которого соединены с информационными входами блока обмена информацией, выход которого является выходом устройства, о .т л и- чающееся тем, что, с целью повышения точности устройства, оно содержит второй цифроаналоговьй преобразователь, блок усреднения значений видеосигналов, блок регистров, блок памяти, блок формирования адреса и элемент НЕ, выход генерато- ра импульсов подключен к стробирующе- му входу первого цифроаналогового преобразователя, тактовым входам блока усреднения значений видеосигналов, блока регистров и блока управления и через элемент НЕ - к стро- бирующим входам блока усреднения значений видеосигналов и второго аналого-цифрового преобразователя, информационный вход которого соединен с выходом видеоусилителя, выходы первого и второго аналого-цифровых преобразователей подключены соответственно к входам первой и второй групп блока усреднения значений видеосигналов, выходы которого соединены с информационными входами блока регистров, управляющий вход которого подключен к соответствующему выходу первого счетчика, а выходы блока регистров соединены с адресным входом блока памяти, первьй информационный вход которого подключен к информационным выходам блока

формирования адреса, первый управляющий, второй и третий информационные входы блока памяти соединены со- (ответственно с выходами второй, третьей и четвертой групп блока управления, первый выход которого подключен к управляющему входу блока обмена информацией, а второй выход - к второму управлянщему входу блока памяти, третий, четвертый, пятый и шестой выходы блока управления соединены соответственно с четвертым, пятым, шестым и первым управляющими

Фиг. 2

входами блока формирования адреса, второй управлякщий вход которого подключен к второму выходу блока формирования строчной развертки, второй выход блока формирования кадровой развертки соединен с третьим зшравляющим входом блока формирования адреса и вторым управляющим входом блока управления, первьй управляющий вход которого подключен к управлякяцему выходу блока формирования адреса.

Фиг. f

Фие.З

Фиг.

Фи.5

tt Г. tf tz tj t2

ln-r)((ii) (n){ntijinfrl

Фиг. 6

Фие.7

| Устройство для считывания изображений | 1981 |

|

SU964673A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для считывания информации | 1981 |

|

SU982039A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-28—Публикация

1986-08-11—Подача