оо оо

Изобретение относится к аналого- цифровым преобразователям и может использоваться для ввода информации в цифровые вычислительные машины.

Целью изобретения является повышение помехоустойчивости устройства

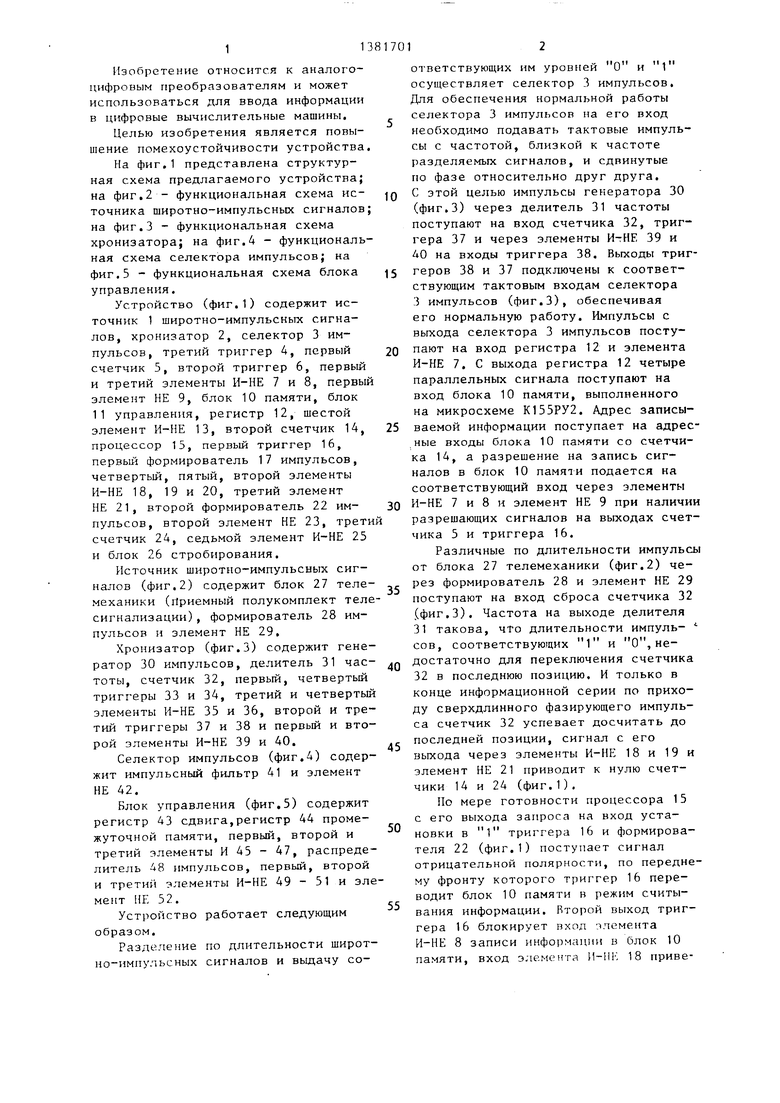

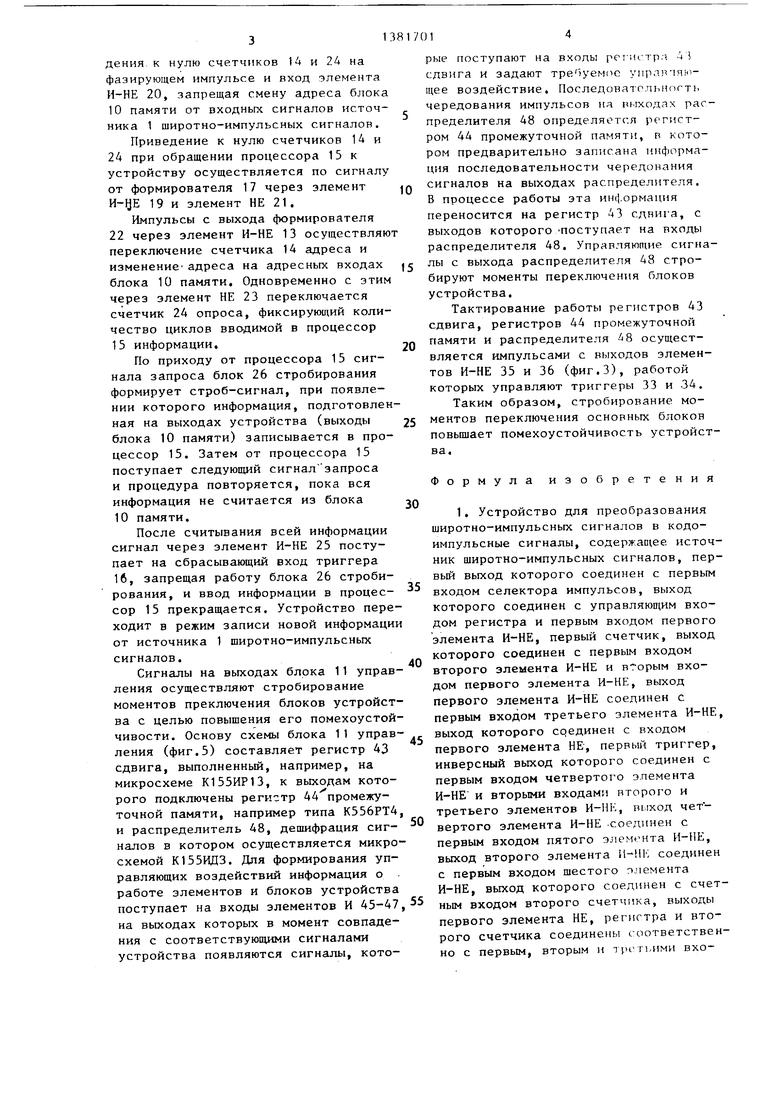

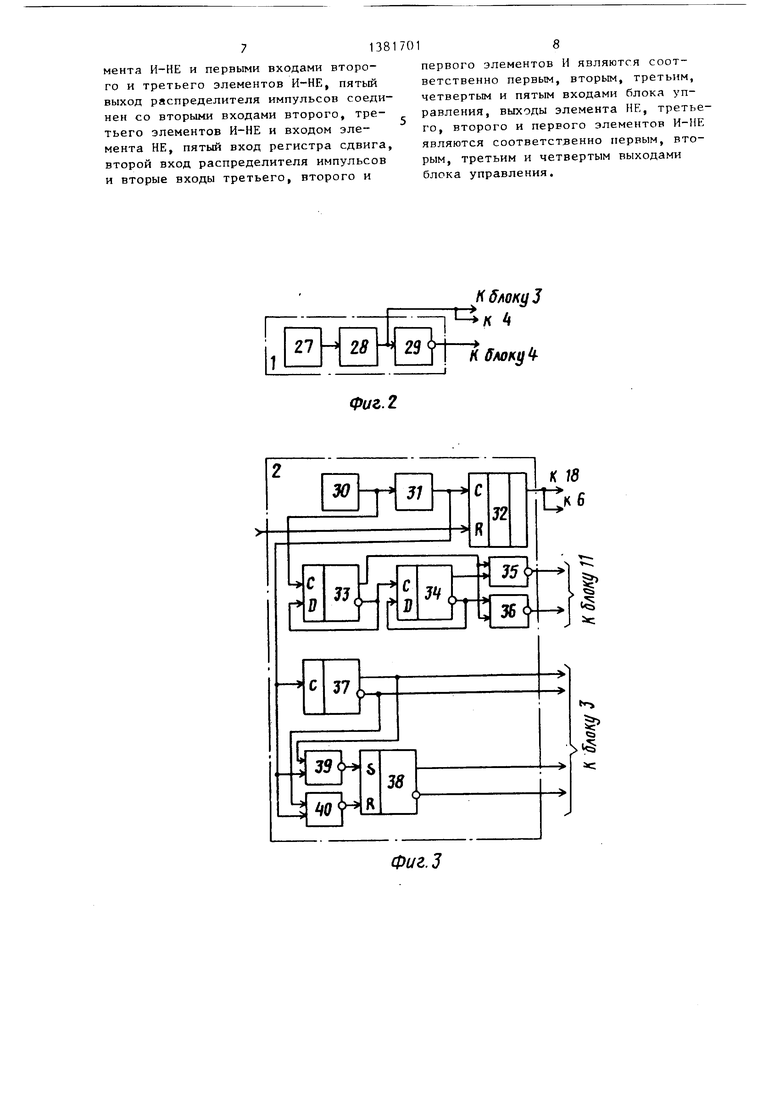

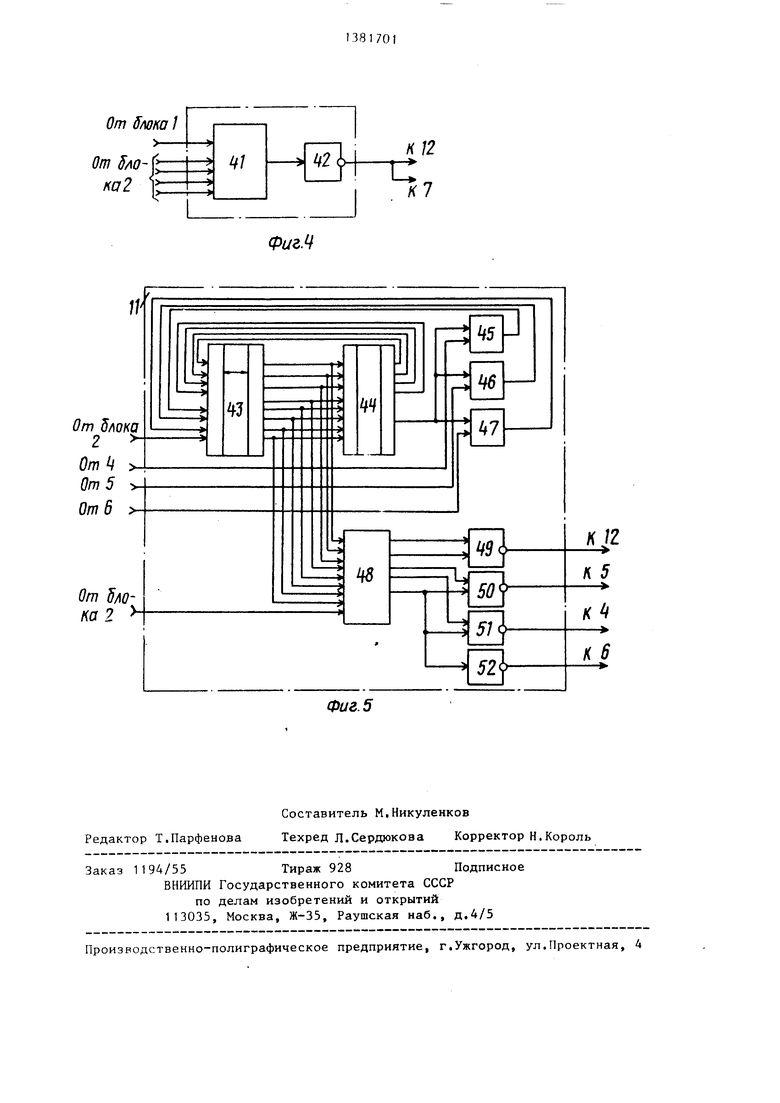

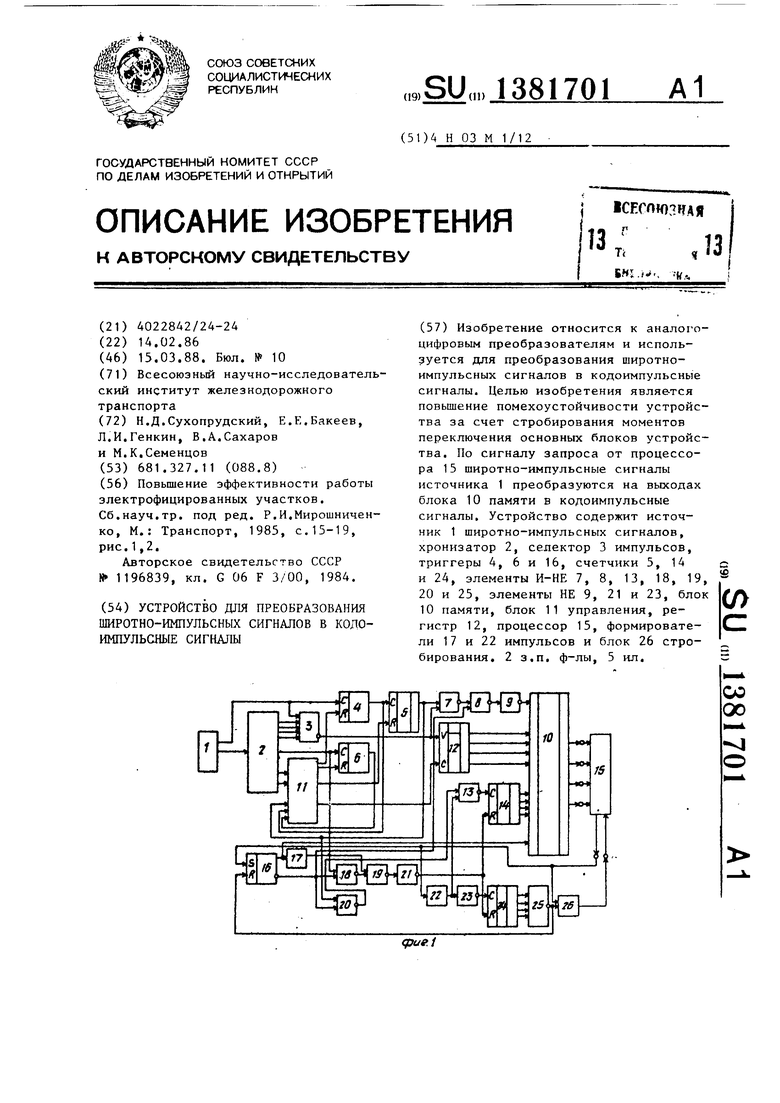

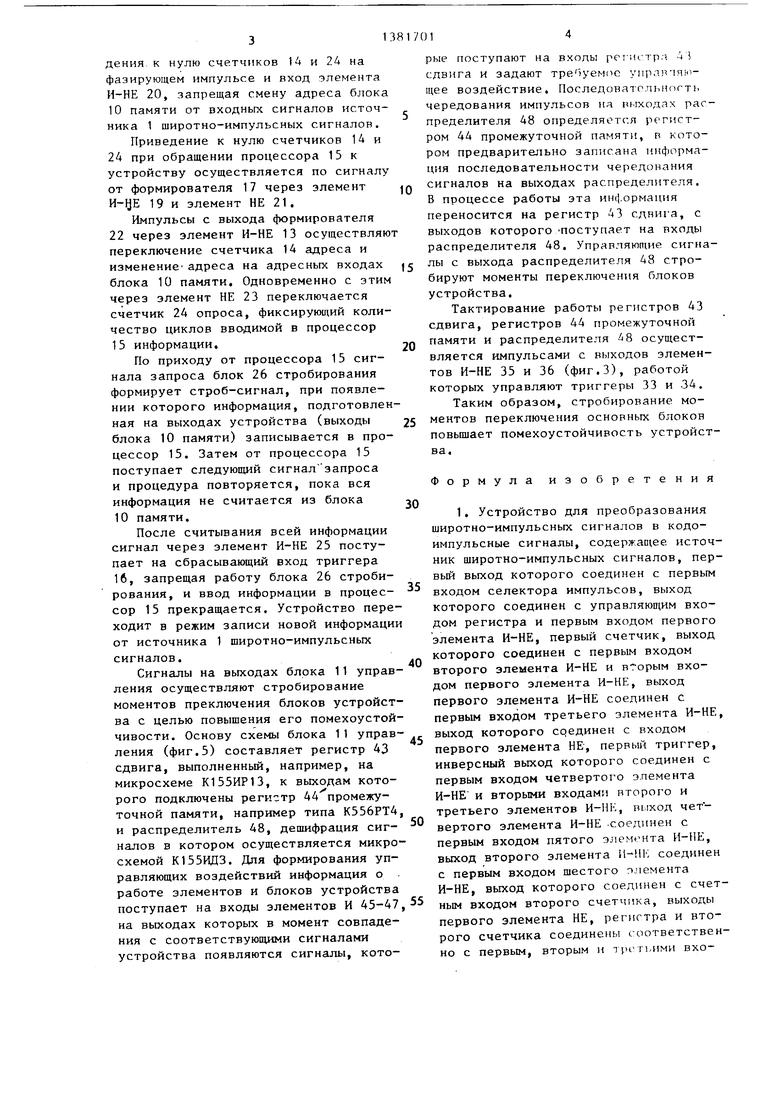

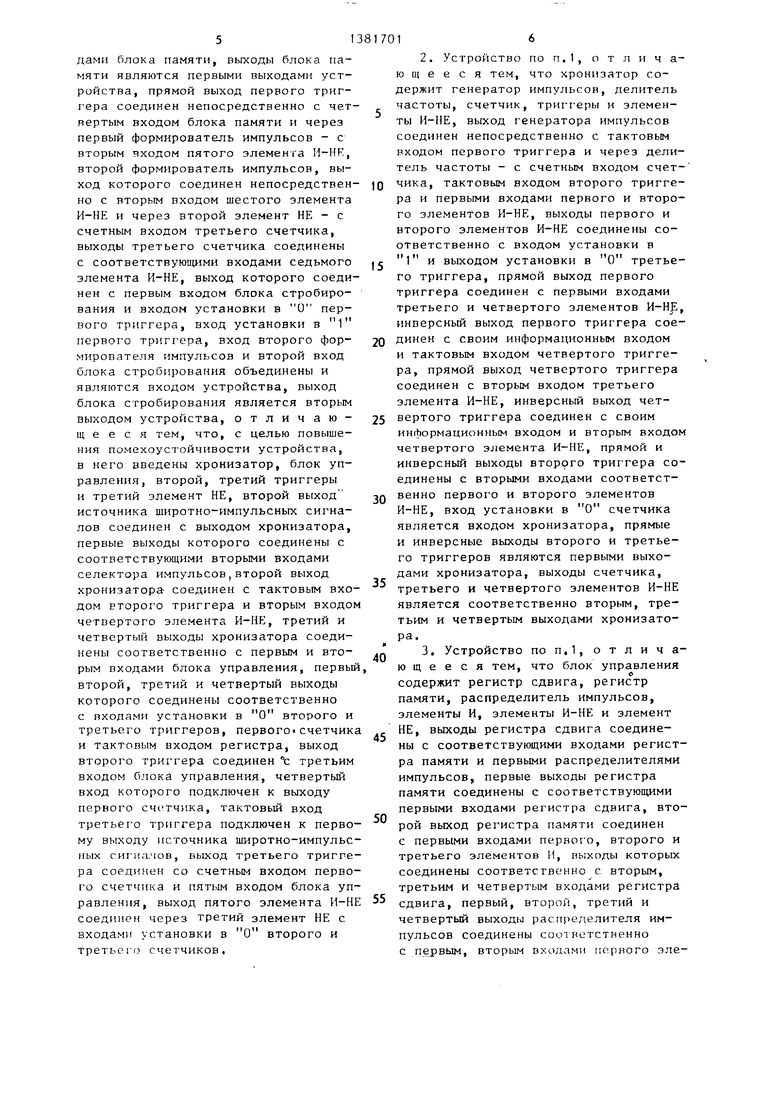

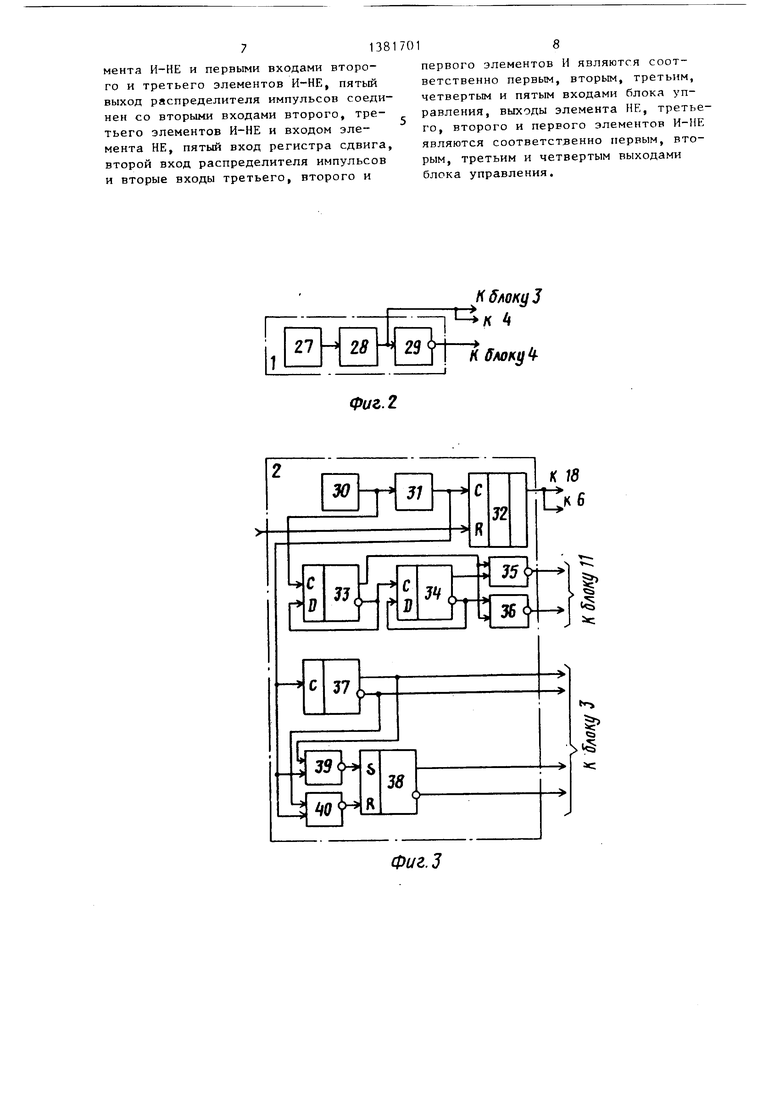

На фиг.1 представлена структурная схема предлагаемого устройства; на фиг.2 - функциональная схема источника широтно-импульсных сигналов на фиг.З - функциональная схема хронизатора; на фиг.4 - функциональная схема селектора импульсов; на фиг.З - функциональная схема блока управления.

Устройство (фиг.1) содержит источник 1 широтно-импульсных сигналов, хронизатор 2, селектор 3 импульсов, третий триггер 4, первый счетчик 5, второй триггер 6, первый и третий элементы И-НЕ 7 и 8, первый элемент НЕ 9, блок 10 памяти, блок 11 управления, регистр 12, шестой элемент И-НЕ 13, второй счетчик 14, процессор 15, первый триггер 16, первый формирователь 17 импульсов, четвертый, пятый, второй элементы И-НЕ 18, 19 и 20, третий элемент НЕ 21, второй формирователь 22 импульсов, второй элемент НЕ 23, трети счетчик 24, седьмой элемент И-НЕ 25 и блок 26 стробирования.

Источник широтно-импульсных сигналов (фиг.2) содержит блок 27 телемеханики (приемный полукомплект телесигнализации) , формирователь 28 импульсов и элемент НЕ 29,

Хронизатор (фиг.З) содержит генератор 30 импульсов, делитель 31 частоты, счетчик 32, первый, четвертый триггеры 33 и 34, третий и четвертый элементы И-НЕ 35 и 36, второй и третий триггеры 37 и 38 и первый и второй элементы И-НЕ 39 и 40.

Селектор импульсов (фиг.4) содержит импульсньш фильтр 41 и элемент НЕ 42.

Блок управления (фиг,5) содержит регистр 43 сдвига,регистр 44 промежуточной памяти, первый, второй и третий элементы И 45 - 47, распределитель 48 импульсов, первый, второй и третий элементы И-НЕ 49 - 51 и элемент НЕ 52.

Устройство работает следующим образом.

Разделение по длительности широтно-импульсных сигналов и вьщачу со.

13817012

ответствующих им уровней О и 1 осуществляет селектор 3 импульсов. Для обеспечения нормальной работы селектора 3 импульсов на его вход необходимо подавать тактовые импуль0

5

0

5

0

5

0

5

0

5

сы с частотой, близкой к частоте разделяемых сигналов, и сдвинутые по фазе относительно друг друга. С этой целью импульсы генератора 30 (фиг.З) через делитель 31 частоты поступают на вход счетчика 32, триггера 37 и через элементы ИтНЕ 39 и 40 на входы триггера 38. Выходы триггеров 38 и 37 подключены к соответствующим тактовым входам селектора 3 импульсов (фиг.З), обеспечивая его нормальную работу. Импульсы с выхода селектора 3 импульсов поступают на вход регистра 12 и элемента И-НЕ 7. С выхода регистра 12 четыре параллельных сигнала поступают на вход блока 10 памяти, выполненного на микросхеме К155РУ2. Адрес записываемой информации поступает на адресные входы блока 10 памяти со счетчика 14, а разрешение на запись сигналов в блок 10 памяти подается на соответствующий вход через элементы И-НЕ 7 и 8 и элемент НЕ 9 при наличии разрешающих сигналов на выходах счетчика 5 и триггера 16.

Различные по длительности импульсы от блока 27 телемеханики (фиг.2) через формирователь 28 и элемент НЕ 29 поступают на вход сброса счетчика 32 (фиг.З). Частота на выходе делителя

31такова, что длительности импуль- сов, соответствующих 1 и О,недостаточно для переключения счетчика

32в последнюю позицию. И только в конце информационной серии по приходу сверхдлинного фазирующего импульса счетчик 32 успевает досчитать до последней позиции, сигнал с его выхода через элементы И-НЕ 18 и 19 и элемент НЕ 21 приводит к нулю счетчики 14 и 24 (фиг.1).

По мере готовности процессора 15 с его выхода запроса на вход установки в 1 триггера 16 и формирователя 22 (фиг.1) поступает сигнал отрицательной полярности, по переднему фронту которого триггер 16 переводит блок 10 памяти в режим считывания информации. Второй выход триггера 16 блокирует вход элемента И-НЕ 8 записи информации в блок 10 памяти, вход элемента И-НК 18 приведения к нулю счетчиков 14 и 2Д на фазирующем импульсе и вход элемента И-НЕ 20, запрещая смену адреса блока 10 памяти от входных сигналов источника 1 широтно-импульсных сигналов.

Приведение к нулю счетчиков 14 и 24 при обращении процессора 15 к устройству осуществляется по сигналу от формирователя 17 через элемент И-ЦЕ 19 и элемент НЕ 21.

Импульсы с выхода формирователя 22 через элемент И-НЕ 13 осуществляют переключение счетчика 14 адреса и изменение адреса на адресных входах блока 10 памяти. Одновременно с этим через элемент НЕ 23 переключается счетчик 24 опроса, фиксирующий количество циклов вводимой в процессор 15 информации.

По приходу от процессора 15 сигнала запроса блок 26 стробирования формирует строб-сигнал, при появлении которого информация, подготовленная на выходах устройства (выходы блока 10 памяти) записывается в процессор 15. Затем от процессора 15 поступает следующий сигнал запроса и процедура повторяется, пока вся информация не считается из блока 10 памяти.

После считывания всей информации сигнал через элемент И-НЕ 25 поступает на сбрасывающий вход триггера 16, запрещая работу блока 26 стробирования, и ввод информации в процессор 15 прекращается. Устройство переходит в режим записи новой информации от источника 1 широтно-импульсных сигналов.

Сигналы на выходах блока 11 управления осуществляют стробирование моментов преключения блоков устройства с целью повышения его помехоустойчивости. Основу схемы блока 11 управления (фиг.5) составляет регистр 43 сдвига, выполненный, например, на микросхеме К155ИР13, к выходам которого подключены регистр 44 промежуточной памяти, например типа К556РТ4, и распределитель 48, дешифрация сигналов в котором осуществляется микросхемой К155ИДЗ. Для формирования управляющих воздействий информация о . работе элементов и блоков устройства поступает на входы элементов И 45-47, на выходах которых в момент совпадения с соответствующими сигналами устройства появляются сигналы, кото

0

5

0

5

0

5

0

5

рые поступают на входы рег;и-тра 4 i сдвига и задают тре )уемос )- щее воздействие. Последоватольиогть чередования импульсов на пмходах распределителя 48 определяется регистром 44 промежуточной памяти, п котором предварительно записана информация последовательности чередования сигналов на выходах распределителя, В процессе работы эта ин4.ормация переносится на регистр 43 сднига, с выходов которого Поступает на входы распределителя 48. Управляюп(ие сигналы с выхода распределителя 48 стро- бируют моменты переключения блоков устройства.

Тактирование работы регистров 43 сдвига, регистров 44 промежуточной памяти и распределителя 48 осуществляется импульсами с выходов элементов И-НЕ 35 и 36 (фиг.З), работой которых управляют триггеры 33 и 34.

Таким образом, стробирование моментов переключения основных блоков повышает помехоустойчивость устройства.

Формула изобретения

1. Устройство для преобразования широтно-импульсных сигналов в кодо- импульсные сигналы, coдepжaD ee источник широтно-импульсных сигналов, первый выход которого соединен с первым входом селектора импульсов, выход которого соединен с управляюпщм входом регистра и первым входом первого элемента И-НЕ, первый счетчик, выход которого соединен с первым входом второго элемента И-НЕ и вгорым входом первого элемента И-НЕ, выход первого элемента И-НЕ соединен с первым входом третьего элемента И-НЕ, выход которого соединен с входом первого элемента НЕ, первый триггер, инверсный выход которого соединен с первым входом четвертого элемента И-НЕ и вторыми входами второго и третьего элементов И-ИЕ, БИХОД четвертого элемента И-НЕ соединен с первым входом пятого элемента И-НЕ, выход второго элемента И-ПК соединен с первым входом шестого элемента И-НЕ, выход которого соединен с счетным входом второго счетчика, выходы первого элемента НЕ, регистра и второго счетчика соединены соответственно с первым, вторым и 1рстьими входамп блока памяти, выходы блока памяти являются первыми выходами устройства, прямой выход первого триггера соединен непосредственно с четвертым входом блока памяти и через первый формирователь импульсов - с вторым входом пятого элемента И-HF, второй формирователь импульсов, выход которого соединен непосредственно с вторым входом шестого элемента И-НЕ и через второй элемент НЕ - с счетным входом третьего счетчика, выходы третьего счетчика соединены с соответствующими входами седьмого элемента И-НЕ, выход которого соединен с первым входом блока стробиро- вания и входом установки в О первого триггера, вход установки в 1 первого трип-ера, вход второго формирователя импульсов и второй вход блока стробирования объединены и являются входом устройства, выход блока стробирования является вторым выходом устройства, отличающееся тем, что, с целью повышения помехоустойчивости устройства, в него введены хронизатор, блок управления, второй, третий триггеры и третий элемент НЕ, второй выход источника широтно-импульсных сигналов соединен с выходом хронизатора, первые выходы которого соединены с соответствующими вторыми входами селектора импульсов,второй выход хронизатора соединен с тактовым входом второго триггера и вторым входом четвертого элемента И-НЕ, третий и четвертый выходы хронизатора соединены соответственно с первым и вторым входами блока управления, первый второй, третий и четвертый выходы которого соединены соответственно с входами установки в О второго и третьего триггеров, первого счетчика и тактовым входом регистра, выход второго триггера соединен t третьим входом блока управления, четвертый вход которого подключен к выходу первого счетчика, тактовый вход третьего триггера подключен к первому выходу источника широтно-импульсных сигчьчлов, выход третьего триггера соединен со счетным входом первого счетчика и пятым входом блока управления, выход пятого элемента И-НЕ соединен через третий элемент НЕ с входами установки в О второго и третьего счетчиков.

,

10

15

20

817016

2.Устройство по п,1, о т л и ч а- ю щ е е с я тем, что хронизатор содержит генератор импульсов, делитель частоты, счетчик, триггеры и элементы И-НЕ, выход генератора импульсов соединен непосредственно с тактовым входом первого триггера и через делитель частоты - с счетным входом счет- чика, тактовым входом второго триггера и первыми входами первого и второго элементов И-НЕ, выходы первого и второго элементов И-НЕ соединены соответственно с входом установки в

1 и выходом установки в О третьего триггера, прямой выход первого триггера соединен с первыми входами третьего и четвертого элементов И-Н|, инверсный выход первого триггера соединен с своим информационным входом и тактовым входом четвертого триггера, прямой выход четвертого триггера соединен с вторым входом третьего элемента И-НЕ, инверсный выход четвертого триггера соединен с своим информационным входом и вторым входом четвертого элемента И-НЕ, прямой и инверсный выходы второго триггера соединены с вторыми входами соответственно первого и второго элементов И-НЕ, вход установки в О счетчика является входом хронизатора, прямые и инверсные выходы второго и третьего триггеров являются первыми выходами хронизатора, выходы счетчика, третьего и четвертого элементов И-НЕ является соответственно вторым, третьим и четвертым выходами хронизатора.

3,Устройство по п,1, отличающееся тем, что блок

25

30

35

40

45

50

55

управления

с

содержит регистр сдвига, регистр памяти, распределитель импульсов, элементы И, элементы И-НЕ и элемент НЕ, выходы регистра сдвига соединены с соответствующими входами регистра памяти и первыми распределителями импульсов, первые выходы регистра памяти соединены с соответствующими первыми входами регистра сдвига, второй выход регистра памяти соединен с первыми входами первого, второго и третьего элементов И, выходы которых соединены соответственно с вторым, третьим и четвертым входами регистра сдвига, первый, второй, третий и четвертый выходы распределителя импульсов соединены сосп ветстненно с первым, вторым входами парного эле7138

мента И-НЕ и первыми входами второго и третьего элементов И-НЕ, пятый выход распределителя импульсов соединен со вторыми входами второго, третьего элементов И-НЕ и входом элемента НЕ, пятый вход регистра сдвига, второй вход распределителя импульсов и вторые входы третьего, второго и

17018

первого элементов И являются соответственно первым, вторым, третьим, четвертым и пятым входами блока управления, выходы элемента НЕ, третьего, второго и первого элементов И-НЕ являются соответственно первым, вторым, третьим и четвертым выходами блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Многоканальное устройство для передачи сигналов приращений | 1982 |

|

SU1103276A1 |

| Устройство магнитной записи-воспроизведения импульсных сигналов | 1983 |

|

SU1068985A1 |

| Многофазный импульсный стабилизатор напряжения | 1990 |

|

SU1700545A1 |

| Устройство для приема и обработки команд телеуправления | 1989 |

|

SU1667137A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Селектор импульсных сигналов | 1982 |

|

SU1058043A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Устройство для телеконтроля | 1990 |

|

SU1732366A1 |

| Устройство для приема и обработки избыточных сигналов | 1983 |

|

SU1152017A2 |

Изобретение относится к аналого- цифровым преобразователям и используется для преобразования широтно- импульсных сигналов в кодоимпульсные сигналы. Целью изобретения является повышение помехоустойчивости устройства за счет стробирования моментов переключения основных блоков устройства. По сигналу запроса от процессора 15 широтно-импульсные сигналы источника 1 преобразуются на выходах блока 10 памяти в кодоимпульсные сигналы. Устройство содержит источник 1 широтно-импульсных сигналов, хронизатор 2, селектор 3 импульсов, триггеры 4, 6 и 16, счетчики 5, 14 и 24, элементы И-НЕ 7, 8, 13, 18, 19, 20 и 25, элементы НЕ 9, 21 и 23, блок 10 памяти, блок 11 управления, регистр 12, процессор 15, формирователи 17 и 22 импульсов и блок 26 стробирования. 2 з.п. ф-лы, 5 ил. (Л

Фиг. 2

Фиг.З

ФигМ

Фиг. 5

| Повьпиение эффективности работы электрофицированных участков | |||

| Сб.науч.тр | |||

| под ред | |||

| Р.И.Мирошниченко, М.: Транспорт, 1985, с.15-19, рис.1,2 | |||

| Устройство для ввода информации | 1984 |

|

SU1196839A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-15—Публикация

1986-02-14—Подача