Изобретение относится к вычислительной технике и может быть использо&ано в информационно-измерительных системах, в которых взаимосвязь устройств осуществляется через общую ши ну, минишину. Известно устройство для сопряжения ЦВМ с внешним накопителем, содержащее блок управления, регистр сдвига, блок временной синхронизации , счетчик, преобразователь интервёшов времени в код, блок разделения Г1. Однако указанное устройство осуществляет контроль информации и цикл грамкм её следования в процессе счисывания и записи информации на внешний накопитель с участием ЦВМ, что снижает зффективное быстродействие последнего. Наиболее близким к предлагаемому по технической сущности и достигаемому результату является устройство для сопряжения ЦВМ с периферийными устройствами, содержащее блок усилителей сигналов связи с ЦВМ, блок усилителей сигналов связи с периферийными устройствами, блок дешифрации адреса, коммутатор, блок выдачи прерывания, блок фop шpoвaния четно ти, триггер разрешения прерывания, схему ИС Однако в известном устройстве отсутствует возможность организации асинхронной передачи информации при работе с синхронными внешними накопителями, что снижает скорость обмена при работе с синхронными периферийными устройствами. Цель изобретения - повышение скорости обмена при работе с синхронными периферийными устройствами и повышение помехоустойчивости. Поставленная цель достигается тем, что в устройство для сопряжения цифровой вычислительнбй машины с периферийными устройствами,содержащее блок хранения управляющих слов, первый информационный выход которого соединен с информационным входом коммутатора, дешифратор адреса,первый выход которого соединен с первым запускающим входом блока управления обменом, блок прерывания, блок формирования четности, блок усилителей и элемент И, причем второй выход дешифратора адреса .соединен с первым входом элемента И и с управляющим входом ком 1утатора, третий и четвертый выходы дешифратора адреса соедипены соответственго с синхронизирующим входом блока прерывания и с адресным входом блока хранения упра ляющих слов, второй и третий информационные выходы которого соединены соответственно с информационным входом блока формирования четности и с первым входом блока усилителей,разрешающий выход блока прерывания соединен с первым признаковым входом коммутатора, выход которого соединеь с вторым входом блока усилителей, .первый задающий выход блока управления обменом соединен с управляющим входом блока хранения управляющих слов, выход конца операции блока управления обменом, выход элемента И, выход блока прерывания, вход дешифратора адреса, вход сброса блока управления обменом, разрешающий вход блока прерывания, первый информационный вход блока хранения управляюЕ1ИХ слов соединены соответственно с третьим - пятым входами и с первым .четвертым выходами блока усилителей, вход-выход которого соединен с первым входом-выходом устройства, введены блок управления сеансом связи,регистр циклического контроля,ре :гистр адреса и блок буферной памяти, 1причем первый - четвертый информационные входы блока управления сеансом связи соединены с выходами соответственно регистра циклического ко роля, блока буферной памяти, регистр адресу и блока формирования четности первый - четвертый информационные выходы блока управления сеансом связ соединены соответственно с информаци онным входом регистра циклического контроля, с информационным входом ре гистра циклического контроля, с информационньзм входом блока буферной памяти, с вторым информационным входом блока хранения управляющих- слов первый, второй, третий стробирующие выходы блока управления сеансом связи соединены с управляющими входами соответственно регистра циклического контроля, регистра адреса и блока бу ферной памяти, задающий выход блока управления сеансом связи соединен с первым управляющим входом блока формирования четности и со сдвиговым входом блока хранения управляющих слов, выход требования блока управления сеансом йвязи соединен с вторы признаковым входом коммутатора и с вторым запускаюсоим входом блока управления обменом, выход конца операции блока управления сеансом связи соединен с запросными входами блока прерывания, блока управления обменом и с третьим признаковым входом комму татора, выход направления обмена бло ка управления сеансомс1зяэи соединен с вторым управляющим входом блока стробирования четности и с режимным входом блока управления обменом, второй и третий задающие выходы которого со.единены соответственно с входом сброса и с входом готовности блока управления сеансом связи, выход ошибки и вход-выход которого соединены соответственно с входом элемента И и с вторым в ходом-выход ом устройства.. Блок управления сеансом связи содержит память микрокоманд, регистр адреса микрокоманды, регистр микрокоманды/дешифратор микрокоманд,первый и второй коммутаторы, регистр сдвига, счетчик, регистр адреса сверхоперативной памяти, сверхоперативную память, распределитель импульсов,селектор условий, четыреэлемента И, два элемента И, узел приемо-передаю1-дих усилителей, причем выход первого коммутатора Соединен с информационныr/M входами регистра сдвига, счетчика сверхоперативной памяти, и с первым информационным входом регистра.адреса микрокоманды, первый-выход селектора условий соединен с первыми входами первого и второго элементов И, с вторым информационным входом регистра адреса микрокоманды и с информационным входом регистра адреса сверхоперативной памяти, с вторым входом второго элемента И и с вторым стробирующим выходом блока, второй выход селектора условий, первый признаковый выход второго коммутатора и первый выход дешифратора микрокоманд соединены соответственно с первым, вторым и третьим входами распределителя импульсов, первый выход которого соединен с управляющим входом дешифратора микрокоманд, второй выход распределителя импульсов соединен с управляющими входами регистра микрокоманды, регистра адреса микрокоманды, регистра: адреса, сверхоперативной памяти, счетчика, регистра сдвига и сверхоперативной памяти, выход регистра адреса микрокоманды соединен с входом памяти микрокоманд, выход которой соединен с информационным входом регистра микрокоманды и с первым информационным входом первого коммутатора, второй, третий и четвертый информационные входы которого соединены с выходами соответственно сверхоперативной памяти, счетчика и регистра сдвига, .первый выход регистра микрокоманды соединен с первым информационным входом дешифратора микрокоманды и с управляющим входом первого коммутатора, второй и третий выходы регистра микрокоманды соединены с вторыми информационными входами соответственно дешифратора микрокоманд и регистра адреса микрокоманды, второй выход дешифратора микрокоманд соединен с входом второго коммутатора, второй признаковый выход которого соединен с первыми входами третьего и четвертого элементов И, вторые выходы соединены соотБвтственно с первым и вторьлм выходами узла 1;риемопередающих усилителей, первый, второй и.третий информационные выходы и информационный вxo -выxoд второго коммутатора соединены соответственно с первым, вторым, третьим информационными выходами блока и с первым входом-выходом узла приемо-передаквдих усилителей, третий выход которого соединен с первым входом селектора условий, второй, третий и четвертый выходы селектора условий соединены соответственно с первым, вторым и третьим информационными входами блока, первый узла приемо-передаюцих усилителей соединен с вторым входом первого элемента И, выход которого и выход второго 31лемента И через первый элемент ИЛИ соединены с первым стробирующим выходом блока,выходы третьего и четвертого элементов И через второй элемент ИЛИ соединены с третьим стробирующим выходом блока, выход регистра адреса сверхоперативной Пс1мяти соединен с адресным входом сверхоперативной памяти,% группа входов-выходов блока является второй группой входов-выходов узла приемопередающих усилителей, четвертыйдевятый выходы и второй, третий, четвертый входы узла приемо-передающих усилителейсоединены соответст.венно с выходамиошибки блока, направления обмена блока, конца операции блока, требования блока, с задаюгцим выходом блока, с четвертым информационным выходом блока, с входом сброса блока, с входом готовности блока и с четвертым информационным входом блока.

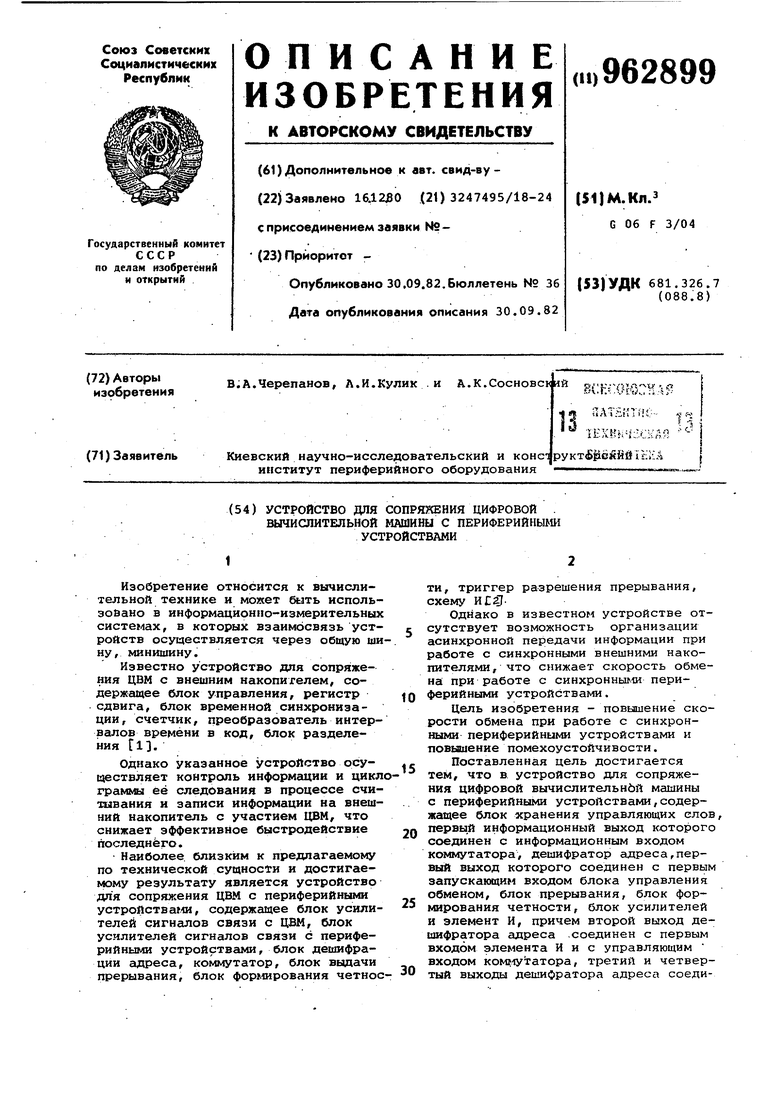

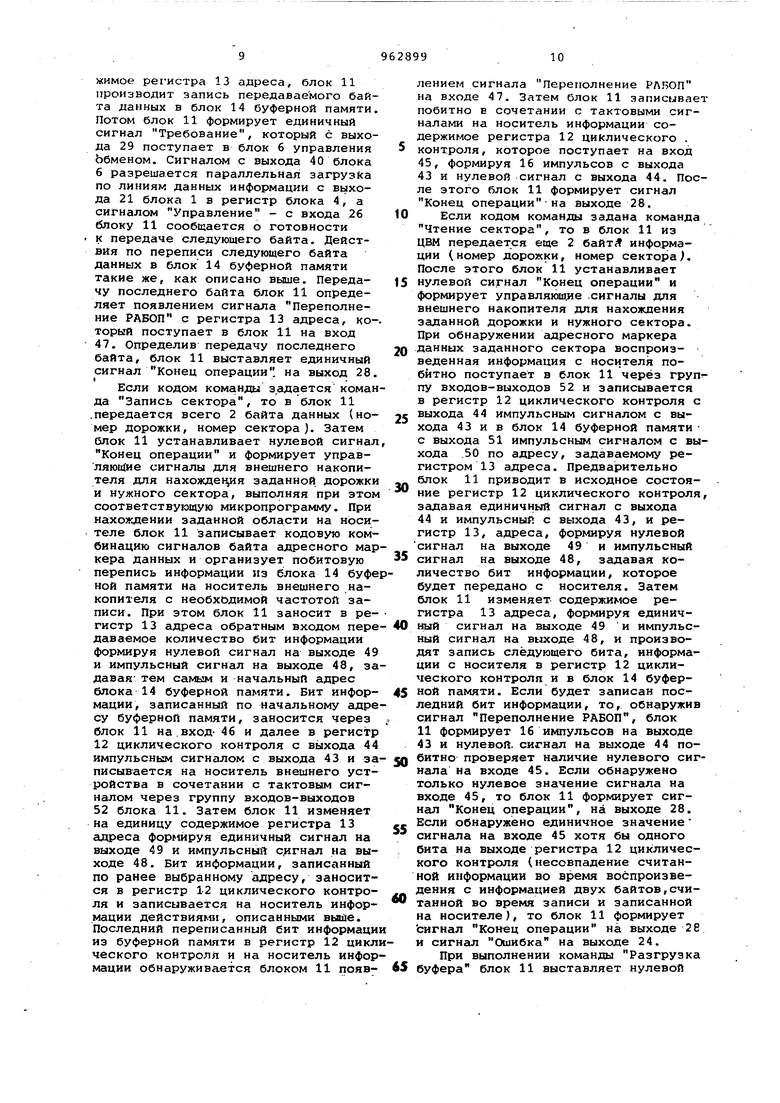

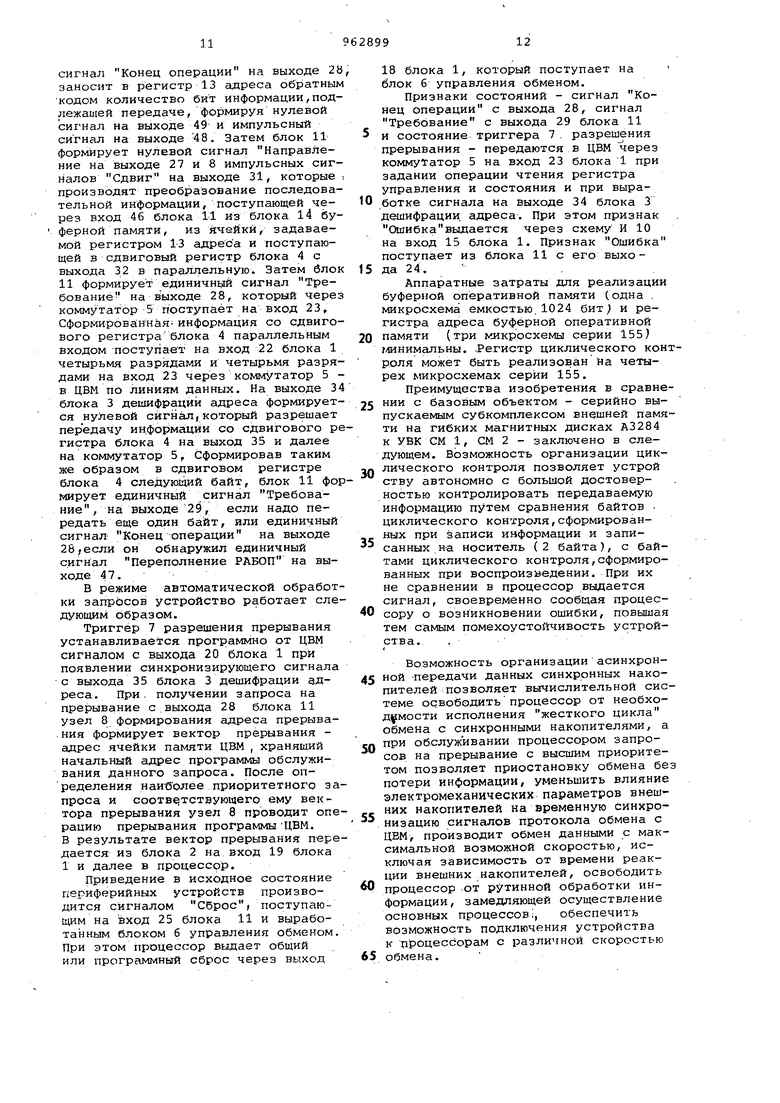

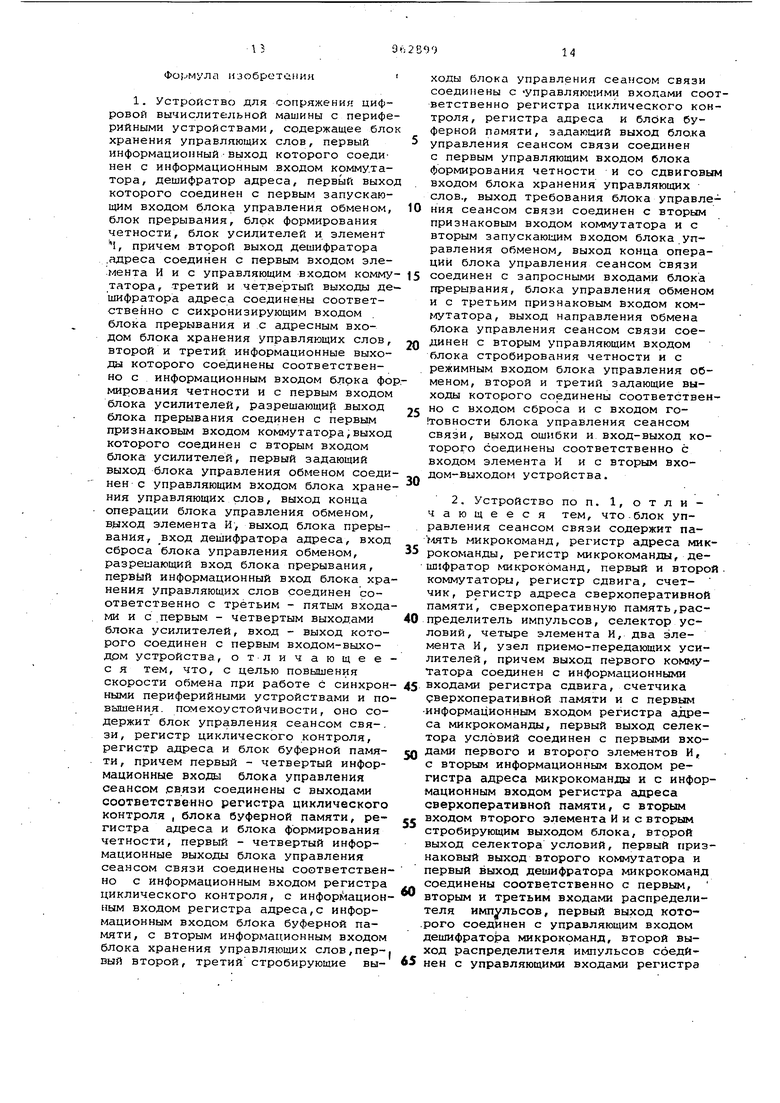

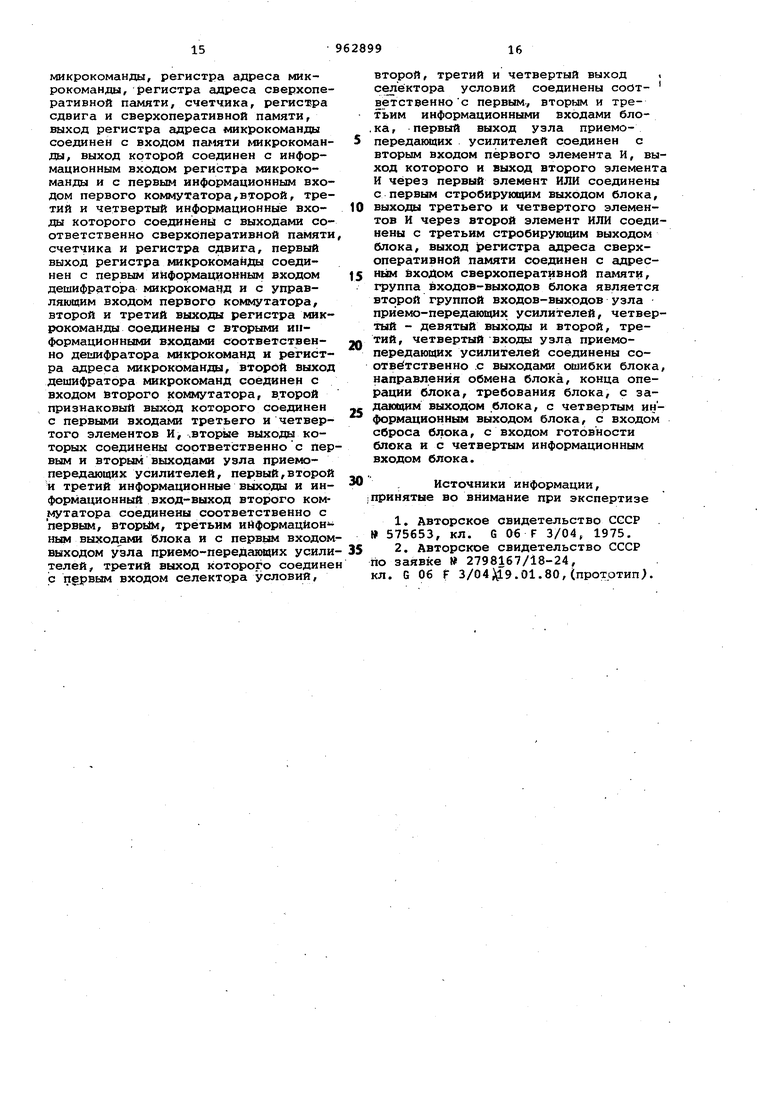

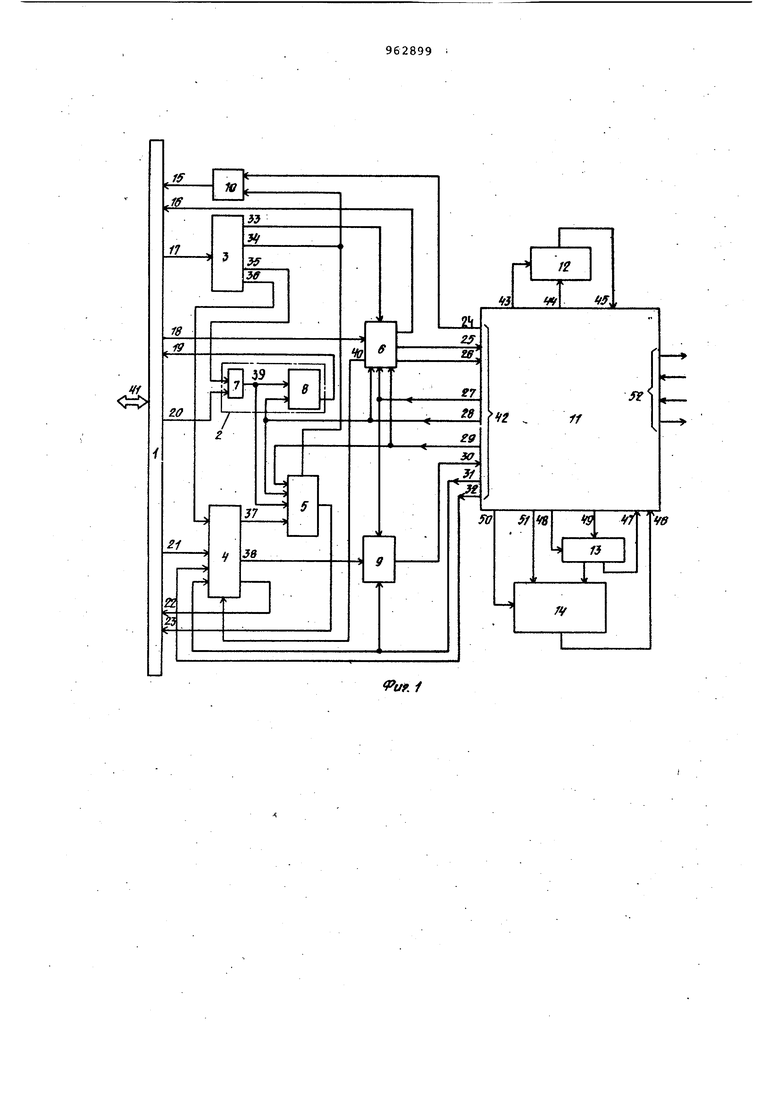

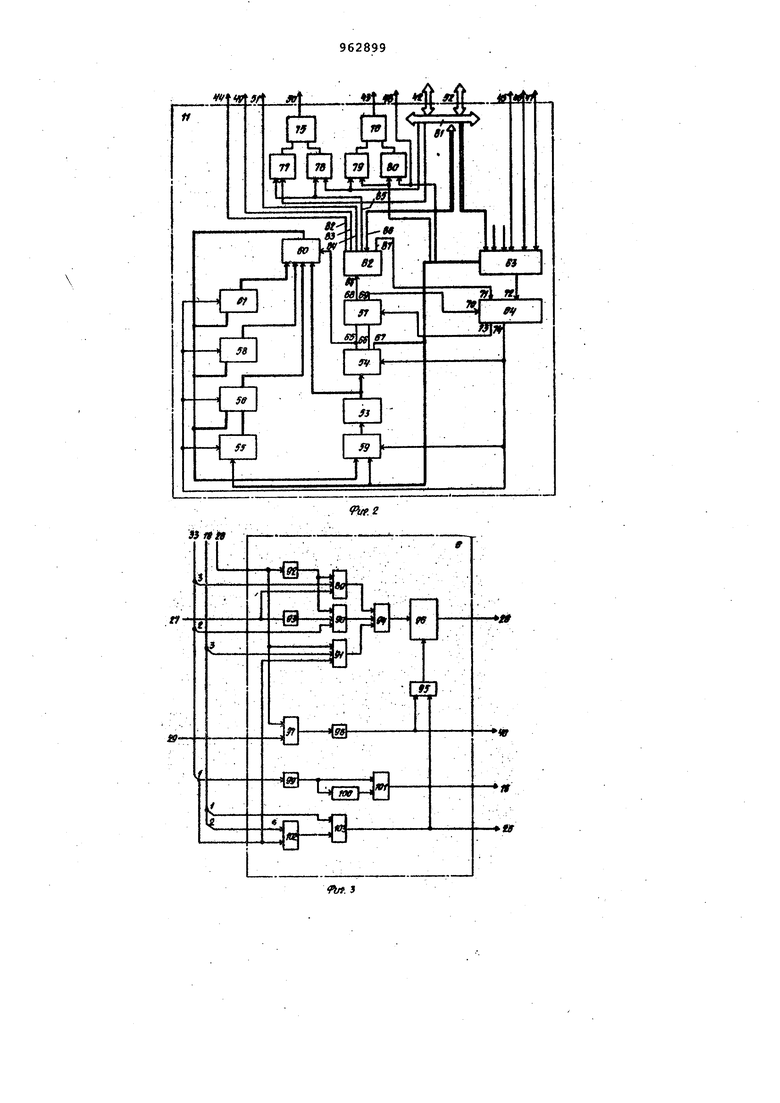

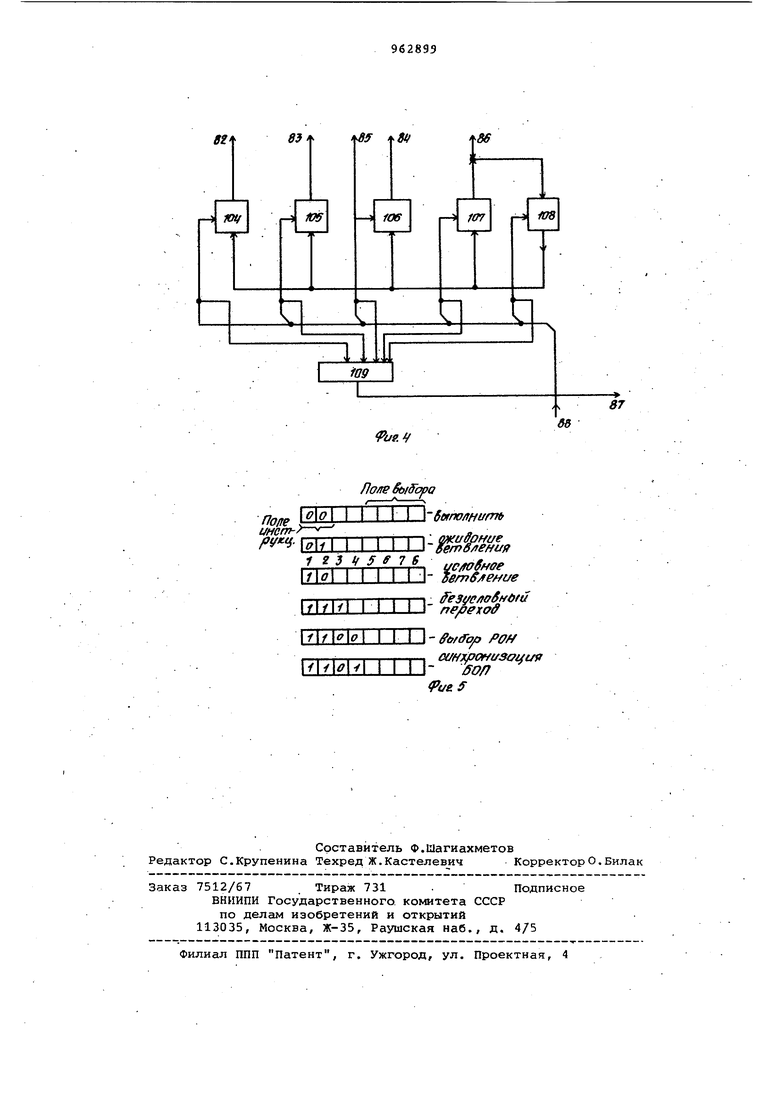

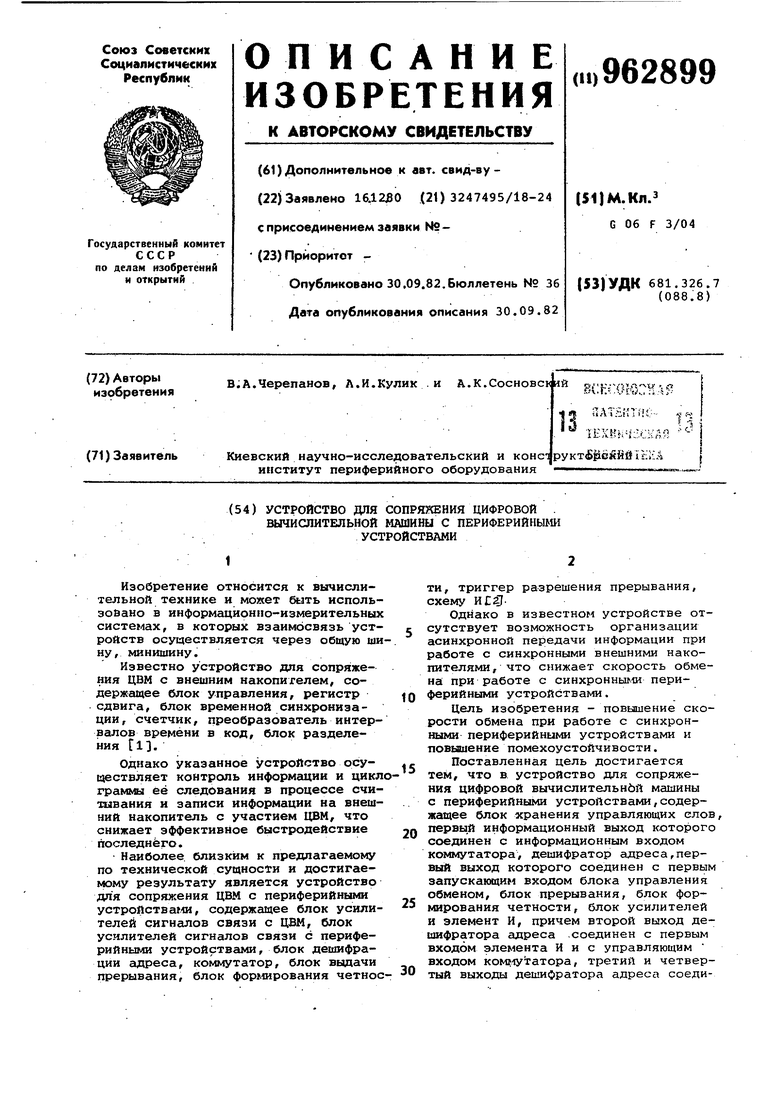

На фиг. 1 представлена структурная схема устройства; на фиг. 2 тто же,, блока управления сеансом связи,- на фиг. 3 - то же, блока управления обменом; на фиг. 4 - то же,второго коммутатора блока управления сеансом связи; на фиг. 5 - форматы микрокоманд.

Устройство для сопряжения цифровой вычислительной меоиины с периферийными устройствагчи (фиг. I) содержит блок 1 усилителей j блок 2 прерыван1я, дешифратор 3 адреса, блок 4 хранения управляющих слов, коммутатор 5, блок б управления обменом, в составе блока прерываний - триггер 7 и узел 8 фор/ рования адреса прерывания, далее устройство содержит блок 9 формирования четности, элемент И 10, блок 11 управления сеансом связи, регистр 12 циклического контроля, регистр 13 адреса, блок 14 буферной памяти, входы и рыходы блока усилителей, четвертый вход 15, третий вход 16, первый выход 17, второй выход ,18, пятый вход 19, третий выход 20, четвертый выход 21, первый вход .22/второй вход 23,

входы и выходы управления сеансом связи: выход 24 сяиибки, выход 25 сброса, вход 26 готовности, выход 27 направления обмена, выход 28 конца операции, выход 29 требования, четвертый информационный вход 30, задающий выход 31, четвертый информационный выход 32, первый 33, второй 34, третий 35, четвертый 36 выходы дешифратора адреса, первый 37 и второй 38 инфор0мационные выходы блока хранения управляющих слов, выход 39 триггера блока прерывания, задающий выход 40 блока управления обменом, первый вход-выход 41 устройства, входы и выхода блока управления сеансом связи:

5 труппу 42 входов и выходов, первый стробирующий выход 43, первый информационный выход 44, первый информационный вход 45, второй и третий информационные входы 46 и 47,

0 второй стробирующий выход 48, второй информационный выход 49, третий стробирующий выход 50, третий информационный выход 51 и вторую группу 52 входов-выходов устройства.

5

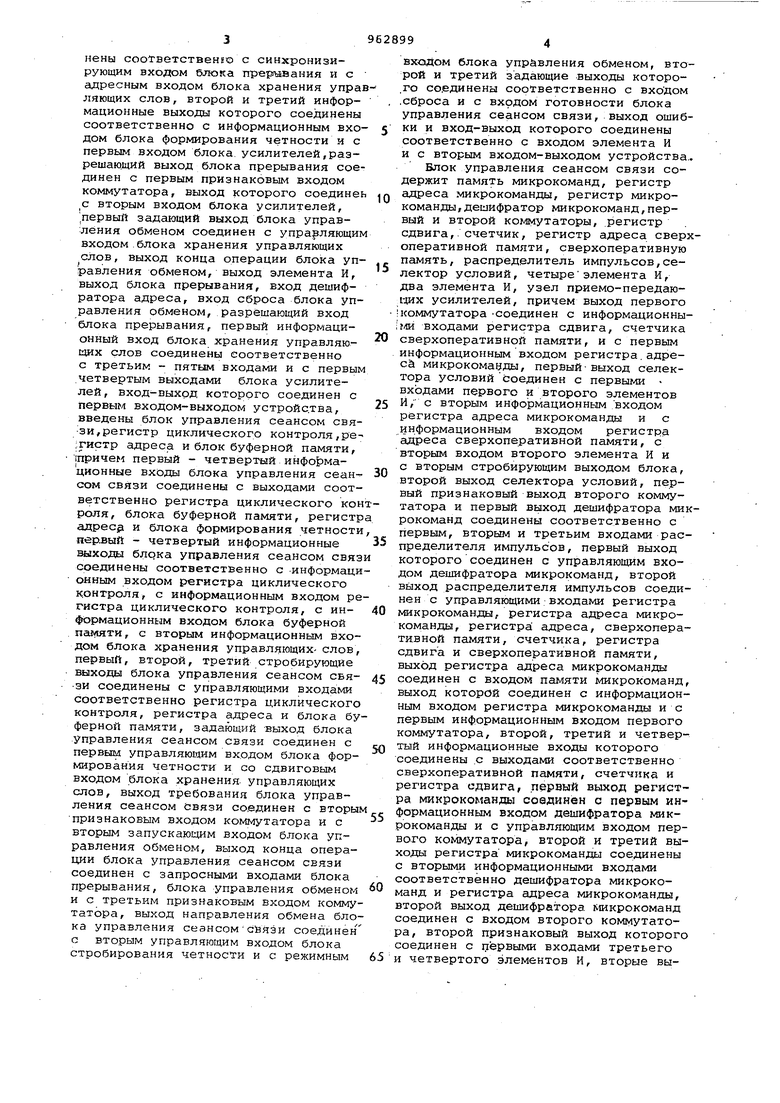

Блок управления сеансом связи (фиг. 2) содержит память 53 микрокоманд, регистр 54 микрокоманды, регистр 55 адреса сверхоперативной памяти,сверхоперативную память 56, дешифратор .57

О микрокоманды, счетчик 58, регистр 59 . адреса микрокоманды, первый коммутатор б6, регистр 61 сдвига, второй коммутатор 62, селектор 63 условий, рас.пределитель 64 импульсов, выходы 65 -

5 67 регистра микрО1$оманды, выходы 68 69 дешифратора микрокоманды, входы 70-72 и выходы 73, 74 распределителя импульсов, элементы ИЛИ 75 и 76, эле1и енты И 77-80, узел .81 приемо-пере-.

0 дающих усилителей, информационные выходы второго коммутатора: первый 82, второй 83, первый признаковый выход 84, третий информационный выход 85, вход-выход 86, второй признаковый выход 87, вход 88.

5

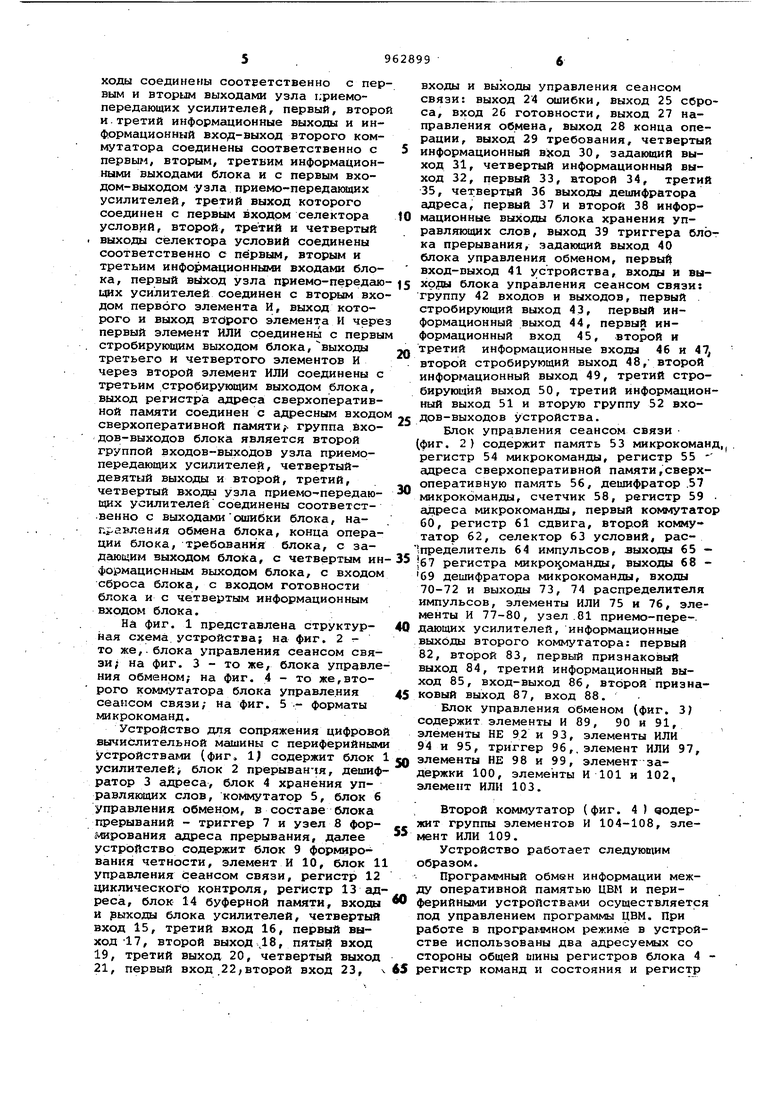

Блок управления обменом (фиг. 3) содержит элементы И 89, 90 и 91, элементы НЕ 92 и 93, элементы ИЛИ 94 и 95, триггер 96,,элемент ИЛИ 97, элементы НЕ 98 и 99, элемент за0держки 100, элементы И 101 и 102, элемент ИЛИ 103.

Второй коммутатор (фиг. 4 ) додержит группы элементов И 104-108, эле5мент ИЛИ 109.

Устройство работает следующим образом.

Программный обмен информации между оперативной памятью ЦВМ и пери0ферийными устройствами осуществляется под управлением программы ЦВМ. При работе в программном режиме в устройстве использованы два адресуемых со стороны общей шины регистров блока 4 5регистр команд и состояния и регистр данных. Программным путем можно загружать и считывать информацию из адресуемых регистров. Обращение к любо му из них производится следующим образом. Процессор выставляет на линии адреса адрес регистра, на линии кода операции - код чтения либо записи. Если производится запись, на линии данных, соединенной с выходом 21, вы тавляется загружаемая информация.Пос ле этого выставляется сигнал синхронизации общей шины. Блок 3 дешиф-. рует адрес и код операции общей шины поступающие в него с выхода 17 блока ;1,и выставляет соответствующий сигна на выход 36 обращения к регистрам .Пр записи информацияв регистр блока 4 поступает с выхЪда 21 блока 1, причтении информацией, из регистра блока поступает параллельно группу входов-выходов41 через вход 22 блока 1 и через коммутатор 5 и вход 23 бло ка 1. Блок 3 сигн-ализирует блоку 6 о вы полнении операции по выходу 33,после чегоблок 6 вырабатывает ответный синхронизирующий сигнал, поступающий на группу входов-вУходов 41 с входа 16 блока 1.Процессор,приняв этот сигнал, заканчивает операцию по общей шине или минишине. I Если производится обращение к регис тру периферийного устройства., бло 3 дешифрует адрес данного перифе-рийного устройства, принимаемый с выхода 17 блока 1, и сигналом с выхо да 33. запускает блок, 6. Блок 6 сигналом с выхода 40 разрешает занесение в регистр команды блока 4 номера периферийного устройства и кода функ ции. При этом блок 6 сигналом Управ ление,.поступающим на вход 26 бло1ка 11, сообщает периферийному устрой ству о готовности принятой информаци к передаче на периферийное устройств Регистр команд и состояний и регистр ранныхпериферийных устройств реали.зованы на общем вольсьмирядном ; .сдвиговом регистре. .Направление . передачи информации между устройством сопряжения и периферийными устройствами определяется сигналом Направление, поступающим с выхода 27 блока 1.1. Единичное значение сигнала 1аправление означает передачу информации из устройства сопряжения, нулевое - в устройство сопр.яжёния из периферийного устройства.Единичное значение сигнала Конец операции, поступающее с выхода 28 блок 11 указывает на то, что периферийное устройство не работает и ждет команду от процессора. ЦВМ. Для передачи кода команды, занесенного в регистр блока 4, на периферийное устройство необходимо, чтобы сигнал Направление с выхода 27 блока 11 был единич йым и сигнал Конец операции с выхода 28 блока 11 тоже был единичные. Периферийное устройство в ответ на сигнал Управление, поступивший на вход 26 блока 11, выдает импульсный сигнал Сдвиг, с выхода 31блока 11, который производит преобразование информации, записанной в параллельном коде в сдвиговый регистр блока 4, в последовательную. Последовательная информация с выхода 38 блока 4, проходя через блок 9 формирования четности, поступает на вход 30блока 11 и далее на периферийное устройство, которое формирует 8 сигналов Сдвиг, поступающих с выхода 31блока 11 для полного принятия кода команды и бита четности для JCOHTроля передачи информации. Принятыйбайт кода команды и проконтролировав безошибочность его передачи, блок 11 управления дешифрует код команды. Если задана команда Загрузка буфера, то..блок 11 переходит к выполнению микропрограммы,соответствующей алгоритму выполнения команды. При этом блок 11 заносит врегистр 13 адреса обратным кодом передаваемое количество бит информации,формируя нулевой сигнал на выходе 49 и имцульсный сигнал на выходе 48 после чего блок 11 выставляет нулевой сигнал Конец операции на выход 28 и формирует единичный сигнал Требова-. ние на выходе 29, который поступает в блок 6 управления обменом. Сигналом с выхода 40 блок -6 разрешает параллельную загрузку по линиям данных. информации, поступающих на выход 21 блока 1 и в регистр блока 4, а сигналом Управление - поступающих на вход 26 блока il, этому блоку сообщается о готовности информации к передаче, сигналом Данные на.вход 30 блока 11 передаётся старший разряд байта данных. Блок 11 в ответ на появление сигнала Управление формирует импульсный сигнал на выходе 50 и переписывает старший разряд байта с выхода 51 в блок 14 буферной памяти по адресу, задаваемому регистром 13 адреса. Затем блок 11 изменяет содержимое регистра 13 адреса на единицу, формируя единичный сигнал на выходе 49 и импульсный сигнал на выходе 48. Импульсный сигнал Сдвиг с выхода 31 блока 11 производит сдвиг информации в сдвиговом регистре блока 4 хранения управляющих слов.На линии сигнала Данные теперь находится следующий разряд, передаваемого байта данных, который записывается в блок 14 буферной памяти импульсным сигналом с выхода 50 блока 11 по адресу, увеличенному на единицу. Формируя еще 5 сигналов Сдвиг и поочередно изменяя содержимое регистра 13 адреса, блок 11 производит запись передаваемого байта данных в блок 14 буферной памяти. Потом блок 11 формирует единичный сигнал Требование, который с выхода 29 поступает в блок 6 управления Ьбменом. Сигналом с выхода 40 блока 6 разрешается параллельная загрузка по линиям данных информации с выхода 21 блока 1 в регистр блока 4, а сигналом Управление - с входа 26 блоку 11 сообщается о готовности к передаче следующего байта. Действия по переписи следующего байта данных в блок 14 буферной памяти такие же, как описано выше. Передачу последнего байта блок 11 определяет появлением сигнала Переполнение РАБОП с регистра 13 адреса, который поступает в блок 11 на вход 47. Определив передачу последнего байта, блок 11 выставляет единичный сигнал Конец операции, на выход 28.

Если кодом команды задается команда Запись сектора, то в блок 11 .передается всего 2 байта данных (номер дорожки, номер сектора). Затем блок 11 устанавливает нулевой сигнал Конец операции и формирует управляюйие сигналы для внешнего накопителя для нахождения заданной дорожки и нужного сектора, выполняя при этом соответствующую микропрограмму. При нахождении заданной области на носителе блок 11 записывает кодовую комбинацию сигналов байта адресного маркера данных и организует побитовую перепись информации из блока 14 буфеной памяти на носитель внешнего накопителя с необходимой частотой записи. При этом блок 11 заносит в регистр 13 адреса обратным входом передаваемое количество бит информации формируя нулевой сигнал на выходе 49 и импульсный сигнал на выходе 48, задавая тем самым и начальный адрес блока 14 буферной памяти. Бит информации, записанный по начальному адресу буферной памяти, заносится через блок 11 на.вход- 46 и далее в регистр 12 циклического контроля с выхода 44 импульсным сигньшом с выхода 43 и записывается на носитель внешнего устройства в сочетании с тактовым сигналом через группу входов-выходов 52 блока 11. Затем блок 11 изменяет На единицу содержимое регистра 13 адреса формируя единичный сигнал на выходе 49 и импульсный с,игнал на выходе 48. Вит информации, записанный по ранее выбранному адресу, заносится в регистр 12 циклического контроля и записывается на носитель информации действиями, описанными выше. Последний переписанный бит информаци из буферной памяти в регистр 12 циклческого контроля и на носитель информации обнаруживается блоком 11 появлением сигнала Переполнение РЛВОП на входе 47. Затем блок 11 записывает побитно в сочетании с тактовыми сигналами на носитель информации содержимое регистра 12 циклического . контроля, которое поступает на вход 45, формируя 16 импульсов с выхода

43и нулевой сигнал с выхода 44. После этого блок 11 формирует сигнал Конец операции -на выходе 28.

Если кодом команды задана команда Чтение сектора, то в блок 11 из ЦВМ передается еще 2 байтЛ информации (номер дорожки, номер сектора). После этого блок 11 устанавливает нулевой си.гнал Конец операции и формирует управляюш.ие .сигналы для внешнего накопителя для нахождения заданной дорожки и нужного сектора. При обнаружении адресного маркера данных заданного сектора воспроизведенная информация с носителя побйтно поступает в блок 11 через группу входов-выходов 52 и записывается в регистр 12 циклического контроля с выхода 44 импульсным сигналом с вы5хода 43 и в блок 14 буферной памяти с выхода 51 импульсным сигналом с выхода .50 по адресу, задаваемому регистром 13 адреса. Предварительно блок 11 приводит в исходное состоя0ние регистр 12 циклического контроля, задавая единичный сигнал с выхода

44и импульсный с выхода 43, и регистр 13, адреса, формируя нулевой

сигнал на выходе 49 и импульсный

5 сигнал на выходе 48, задавая количество бит информации, которое будет передано с носителя. Затем блок 11 изменяет содержимое регистра 13 адреса, формируя единич0ный сигнал на выходе 49 и импульсный сигнал на выходе 48, и производят запись следующего бита, информации с носителя в регистр 12 циклического контроля и в блок 14 буферной памяти. Если будет записан пос5ледний бит информации, то,. обнаружив сигнал Переполнение РАБОП, блок 11 формирует 16 импульсов на выходе 43 и нулевой, сигнал на выходе 44 побитно проверяет наличие нулевого сиг0нала на входе 45. Если обнаружено только нулевое значение сигнала на входе 45, то блок 11 формирует сигнал Конец операции, на выходе 28. Если обнаружено единичное значение

5 сигнала на входе 45 хотя бы одного бита на выходе регистра 12 циклического контроля (несовпадение считанной информации во время воспроизведения с информацией двух байтов,считанной во время записи и записанной на носителе), то блок 11 формирует сигнал Конец операции на выходе 28 и сигнгил Ошибка на выходе 24.

При выполнении команды Разгрузка

5 буфера блок 11 выставляет нулевой сигнал Конец операции на выходе 2 заносит в регистр 13 адреса обратны КОДОМ количество бит информации,под лежащей передаче, формируя нулевой сигнал на выходе 49 и импульсный сигнал на выходе 48. Затем блок 11 формирует нулевой сигнал Направление на выходе 27 и 8 импульсных сиг налов Сдвиг на выходе 31, которые производят преобразование последова тельной информации, поступающей через вход 46 блока 11 из блока 14 бу ферной памяти, из ячейки, задаваемой регистром 13 адреса и поступающей в сдвиговый регистр блока 4 с выхода 32 в Параллельную. Затем бло 11 формирует единичный сигнал Требование на выходе 28, который чере комму-татор 5 поступает на вход 23, Сформированная- информация со сдвиго вого регистра блока 4 параллельным входом поступает на вход 22 блока 1 четырьмя разрядами и четырьмя разря дами на вход 23 через коммутатор 5 в ЦВМ по линиям данных. На выходе 3 блока 3 дешифраций адреса формирует ся нулевой сигнал,который разрешает передачу информации со сдвигового р гистра блока 4 на выход 35 и далее на коммутатор 5, Сформировав таким же образом в сдвиговом регистре блока 4 следующий байт, блок 11 фо мирует единичный сигнал Требование , на: выходе 29 , если надо передать еще один байт, или единичный сигнал Конец операции на выходе он обнаружил единичный сигнал Переполнение РАБОП на выходе 47. В режиме автоматической обработ ки запросов устройство работает сле дующим образом. Триггер 7 разрешения прерывания устанавливается программно от ЦВМ сигналом с выхода 20 блока 1 при появлении синхронизирующего сигнала с выхода 35 блока 3 дешифрации адреса. При. получении запроса на прерывание с,выхода 28 блока 11 узел 8 формирования адреса прерывания формирует вектор прерывания адрес ячейки памяти ЦВМ , хранящий начальный адрес программы обслуживания данного запроса. После определения наи-более приоритетного за проса и соответствующего ему вектора прерывания узел 8 проводит опе рацию прерывания программы ЦВМ. В результате вектор прерывания пере дается из блока 2 на вход 19 блока 1 и далее в процессор. Приведение в исходное состояние периферийных устройств производится сигналом Сброс, поступающим на вход 25 блока 11 и выработанным блоком 6 управления обменом. При этом процессор выдает общий или программный сброс через выход 18 блока 1, который поступает на блок б управления обменом. Признаки СОСТОЯНИЙ - сигнал Конец операции с выхода 28, сигнал Требование с выхода 29 блока 11 и состояние триггера 7. разрешения прерывания - передаются в ЦВМ ерез коммутатор 5 на вход 23 блока 1 при задании операции чтения регистра управления и состояния и при выработке сигнала на выходе 34 блока 3 дешифрации, адреса. При этом признак Ошибка выдается через схему И 10 на вход 15 блока 1. Признак Ошибка поступает из блока 11 с его выхода 24. Аппаратные затраты для реализации буферной оперативной памяти (одна . ivMKpocxeMa емкостью. 1024 бит и регистра адреса буферной оперативной памяти (три микросхемы серии 155) г/мнимальны. .Регистр циклического контроля может быть реализован На четырех микросхемах серии 155. Преимущества изобретения в сравнении с базовым объектом - серийно выпускаемым субкомплексом внешней памяти на гибких магнитных дисках А3284 к УВК СМ 1, СМ 2 - заключено в следующем. Возможность организации циклического контроля позволяет устрой ству автономно с большой достоверностью контролировать передаваемую информацию путем сравнения байтов . циклического контроля,сформированных при записи информации и записанных н-а носитель (2 байта), с байтами циклического контроля,сформированных при воспроизведении. При их не сравнении в процессор выдается сигнал, своевременно сообщая процессору о возникновении ошибки, повышая тем самым помехоустойчивость устройства., . Возможность организации асинхронной -передачи данных синхронных накопителей позволяет вычислительной системе освободитьпроцессор от необход| мости исполнения жесткого цикла обмена с синхронными накопителями, а при обслуживании процессором запросов на прерывание с высшим приоритетом позволяет приостановку обмена без потери информации, уменьшить влияние электромеханических; параметров внешних накопителей на временную синхронизацию сигналов протокола обмена с ЦВМ, производит обмен данными с максимальной возможной скоростью, исключая зависимость от времени реакции внешних накопителей, освободить процессор ОТ рутинной обработки информации , замедляющей осуществление основных процессов;, обеспечить возможность подключения устройства к процессорам с различной скоростью обмена.

Формула нзобретоиия

1. Устройства для сопряжения цифровой вычислительной машины с периферийными устройствами, содержащее блок хранения управляющих слов, первый информационныйвыход которого соединен с информационным входом коммутатора, дешифратор адреса, первый выход которого соединен с первым запускающим входом блока управления обменом, блок прерывания, блок формирования четности, блок усилителей и элемент Ч, причем второй выход дешифратора .адреса соединен с первым входом элемента И и с управляющим входом коммутатора , третий и четвертый выходы дешифратора адреса соединены соответственно с сихронизирующим входом блока прерывания и с адресным входом блока хранения управляющих слов, второй и третий информационные выходы которого соединены соответственно с информационным входом блока формирования четности и с первым входом блока усилителей, разрешающий выход блока прерывания соединен с первым признаковым входом коммутатора,выход которого соединен с вторым входом блока усилителей, первый задающий выход блока управления обменом соединен с управляющим входом блока хранения управляющих слов, выход конца операции блока управления обменом, вуход элемента И, выход блока прерывания, вход дешифратора адреса, вход сброса блока управления обменом, разрешающий вход блока прерывания, первый информационный вход блока хранения управляющих слов соединен соответственно с третьим - пятым входагли и с первым - четвертым выходами блока усилителей, вход - выход которого соединен с первым входом-выходом устройства, отличающеес я тем, что, с целью повышения скорости обмена при работе с синхронными периферийными устройствами и повышения, помехоустойчивости, оно содержит блок управления сеансом свя-. зи, регистр циклического контроля, регистр адреса и блок буферной памяти, причем первый - четвертый информационны е входы блока управления сеансом связи соединены с выходами соответственно регистра циклического контроля , блока буферной памяти, регистра адреса и блока формирования четности, первый - четвертый информационные выходы блока управления сеансом связи соединены соответственно с информационным входом регистра циклического контроля, с инфор 11ационкым входом регистра адреса,с информационным входом блока буферной памяти, с вторым информационным входом блока хранения управляющих слов,пер-, вый второй, третий стробирующие выходы блока управления сеансом связи соединены с -управляющими входами соответственно регистра циклического контроля, регистра адреса и блока буферной памяти, задающий выход бло.ка управления сеансом связи соединен с первым управляющим входом блока формирования четности и со сдвиговым входом блока хранения управляющих слов., выход требования блока управле0ния сеансом связи соединен с вторым признаковым входом коммутатора и с вторым запускающим входом блока управления обменоМу выход конца операций блока управления сеансом связи

5 соединен с запросными входами блока прерывания, блока управления обменом и с третьим признаковым входом коммутатора, выход направления обмена блока управления сеансом связи соединен с вторым управляющим входом

0 блока стробирования четности и с рея(имным входом блока управления обменом, второй и третий задающие выходы которого соединены соответственно с входом Сброса и с входом го5товности блока управления сеансом связи, выход ошибки и вход-выход которого соединены соответственно с входом элемента И и с вторым входом-выходом устройства.

0

2. Устройство по п. 1, отличающееся тем, что-блок управления сеансом связи содержит паглять микрокоманд, регистр адреса мик5рокоманды, регистр микрокоманды, дешифратор микрокоманд, первый и второй коммутаторы, регистр сдвига, счетчик, регистр адреса сверхоперативной памяти, сверхоперативную память,рас0пределитель импульсов, селектор условий , четыре элемента И, два элемента И, узел приемо-передающих усилителей, причем выход первого комму татора соединен с информационными входами регистра сдвига, счетчика

5 сверхоперативной памяти и с первью. информационным входом регистра адреса микрокоманды, первый выход селектора условий соединен с первыми входами первого и второго элементов И,

0 с вторым информационным входом регистра адреса микрокоманды и с информационным входом регистра адреса сверхоперативной памяти, с вторым входом второго элемента И и с вторым

5 стробирующим выходом блока, второй выход селектора условий, первый признаковый выход второго коммутатора и первый выход дешифратора микрокоманд соединены соответственно с первым,

0 вторым и третьим входами распределителя ИМПУЛЬСОВ, первый выход кото.рого соединен с управляющим входом дешифратора микрокоманд, второй выход распределителя импульсов соеди5нен с управляющими входами регистра

микрокоманды, регистра адреса микрокоманды, регистра адреса сверхоперативной памяти, счетчика, регис-рра сдвига и сверхоперативной памяти, выход регистра адреса микрокоманды соединен с входом памяти микрокоманды, выход которой соединен с информационным входом регистра микрокоманды и с первым информационным входом первого коммутатора,второй, третий и четвертый информационные входы которого соединены с выходами соответственно сверхоперативной памяти счетчика и регистра сдвига, первый выход регистра микрокоманды соединен с первым информационным входом дешифрато1ра микрокоманд и с управляющим входом первого коммутатора, второй и третий выходы регистра микрокоманды соединены с вторыми информационными входами соответственно деишфратора микрокоманд и регистра адреса микрокоманды, второй выход дешифратора микрокоманд соединен с входом второго коммутатора, второй признаковый выход которого соединен с первыми входами третьего и четвертого элементов И, .вторые выходы которых соединены соответственно с первым и вторым выходами узла приемопередающих усилителей, первый,второй и третий информационные выходы и информа1(ионный вход-выход второго ком мутатора соединены соответственно с первым, BTopblM, третьим ийформацйон ным выходами блока и с первым входомвыходом уэла приемо-передающих усили телей, третий выход которого соедине с первым входом селектора условий.

второй, третий и четвертый выход селектора условий соединены соответстееннос первым-, вторым и третьим информационными входами бло,ка, первый выход узла приемопередающих усилителей соединен с вторым входом первого элемента И, выход которого и выход второго элемент И через первый элемент ИЛИ соединены с первым стробирующим выходом блока, выходы третьего и четвертого элементов И через второй элемент ИЛИ соединены с третьим стробирующим выходом блока, выход регистра адреса сверхоперативной Пс1мяти соединен с адресHEJM ЁхоДом сверхоперативной памяти, группа входов-выходов блока является второй группой входов-выходов узла приемо-передающих усилителей, четвертый - девятый выходы и второй, третий, четвертый входы узла приемопередающих усилителей соединены соответственно .с выходами ошибки блока направления обмена блока, конца операции блока, требования блока, с задающим выходом блока, с четвертым информсщионным выходом блока, с входом сброса блока, с входом готовности блока и с четвертым информационным входом блока.

Источники информации, :принятые во внимание при экспертизе

1.Авторское свидетельство СССР 575653, кл, G 06 F 3/04, 1975,

2.Авторское свидетельство СССР по заявке 2798167/18-24,

кл. G 06 F 3/04J 9.01.80,(прототип).

..J«iM.M

iCl

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Устройство для сопряжения цифровой вы-чиСлиТЕльНОй МАшиНы C пЕРифЕРийНыМи уСТРОй-СТВАМи | 1979 |

|

SU840874A1 |

| Устройство для сопряжения ЦВМ с внешними устройствами | 1989 |

|

SU1784840A1 |

| Микропрограммное устройство для сопряжения процессора с абонентами | 1987 |

|

SU1539787A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для управления обменом информацией накопителя на магнитной ленте с электронно-вычислительной машиной | 1983 |

|

SU1128245A1 |

| Устройство для сопряжения процессора с периферийными устройствами | 1985 |

|

SU1359780A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

9) «a

tf

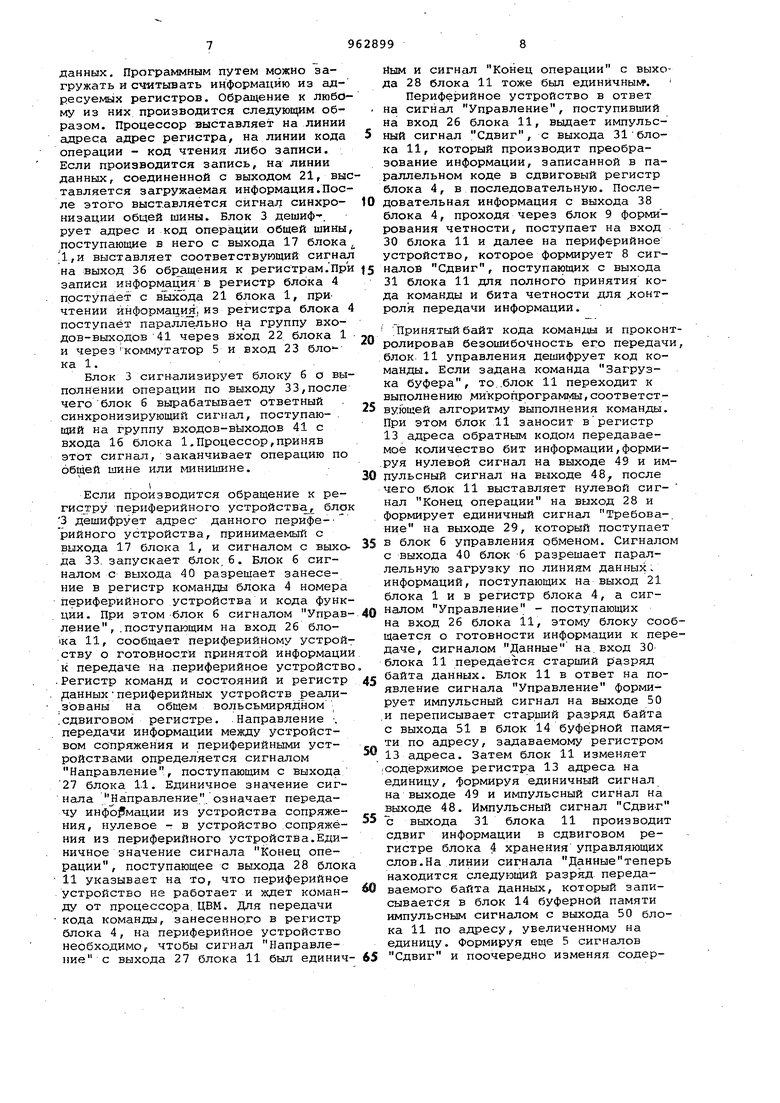

По/ie I I ff r naн/ffT№ t/HGfTf

kl/1 I I I I I

Ч

I I I I 1 I- semS/fe t/e

I I I I fesycffoSffOtu I I I I I ne exoff

I I II-ffwfo PO

. I I I I I I I . ci/HxpOffu3otfifii I I Л- ол

68

Uff.t/

Лоле SbtSt a

Pu&ff

Авторы

Даты

1982-09-30—Публикация

1980-12-16—Подача