Изобретение относится к электротехнике и может быть использовано в ка- . честве источника вторичного электропитания электротехнической и радиоэлектронной аппаратуры различного назначения.

Цель изобретения - повышение надежности многофазного импульсного стабилизатора путем обеспечения симметрии управляющих импульсов на входах силовых каналов в статических и переходных режимах.

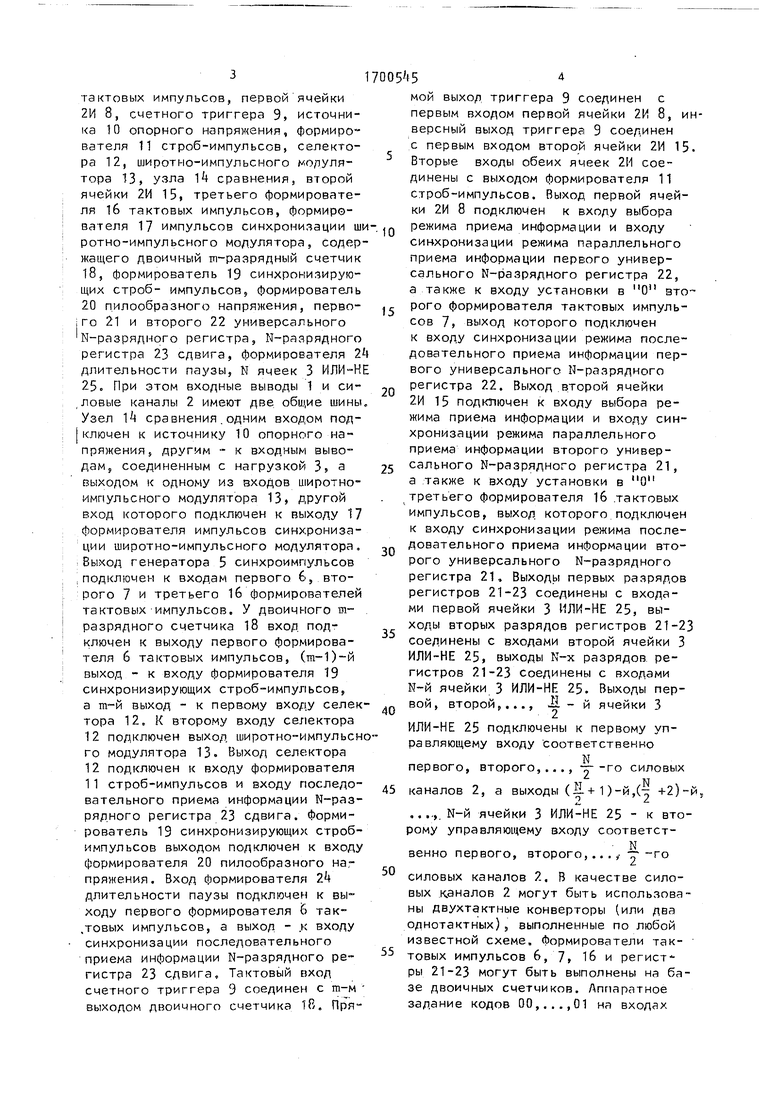

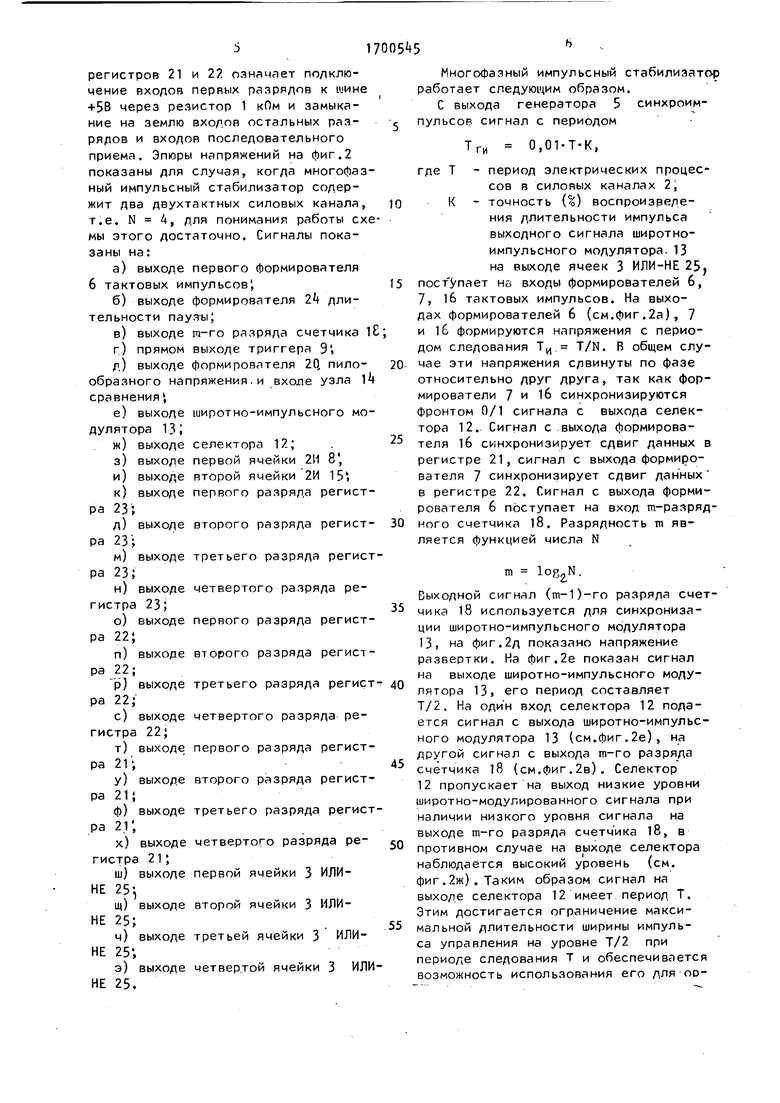

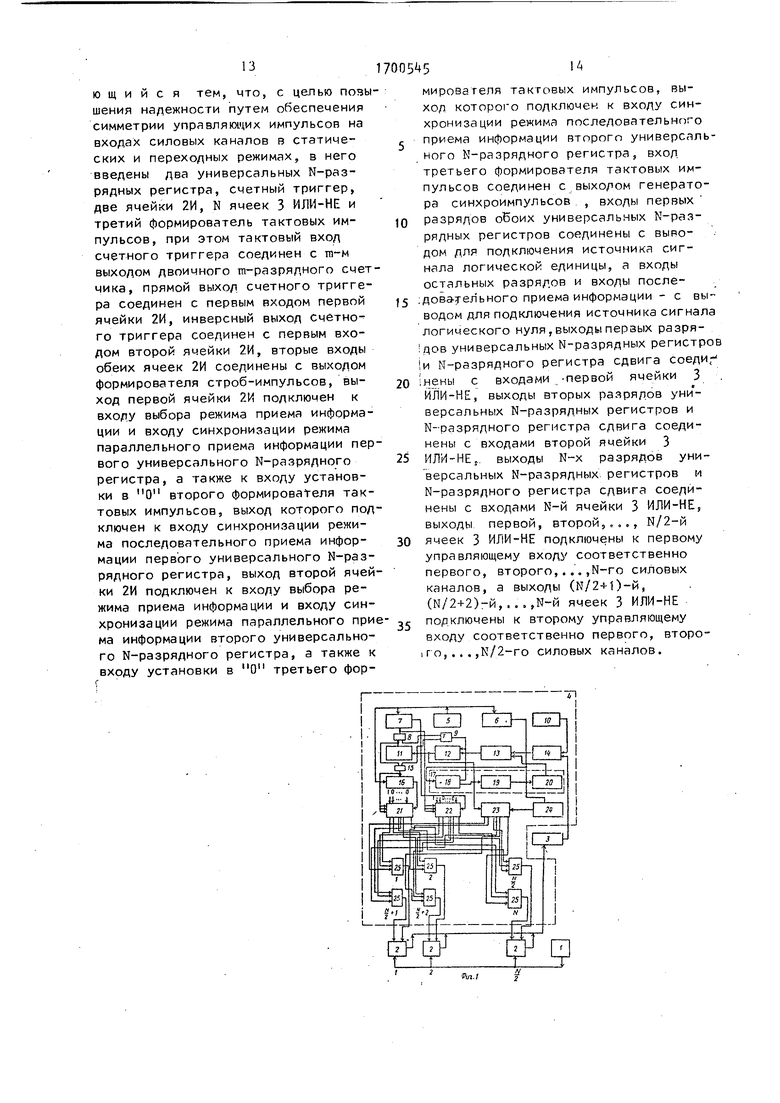

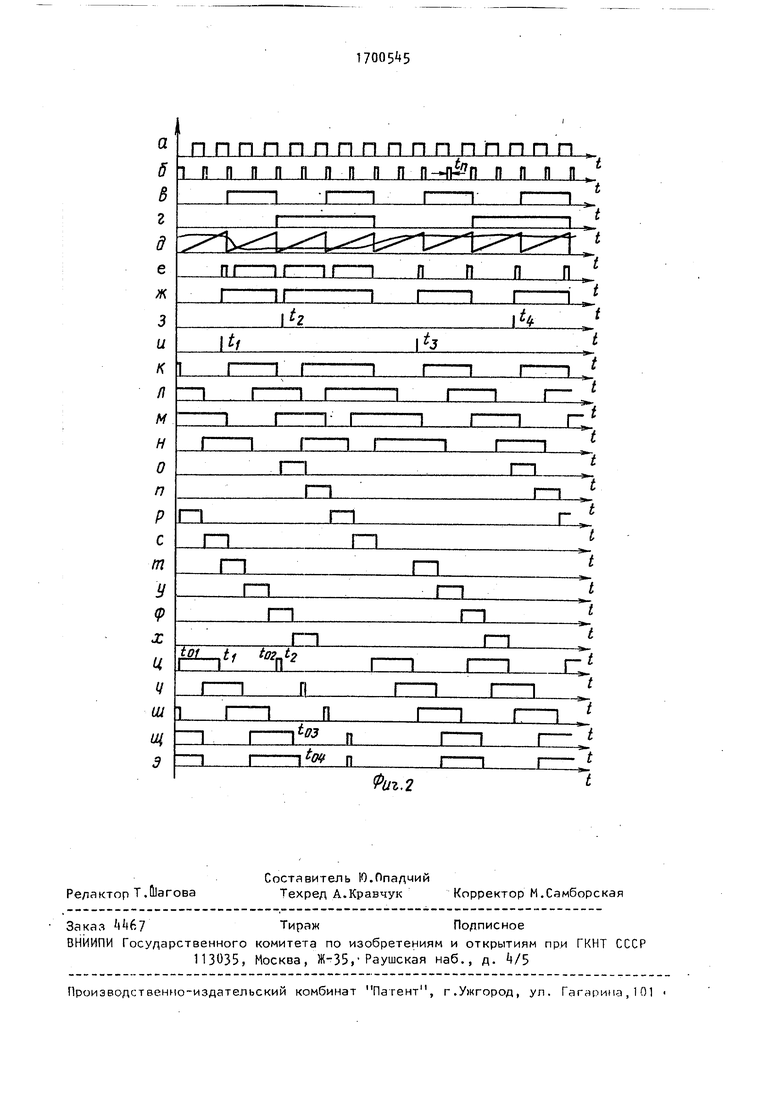

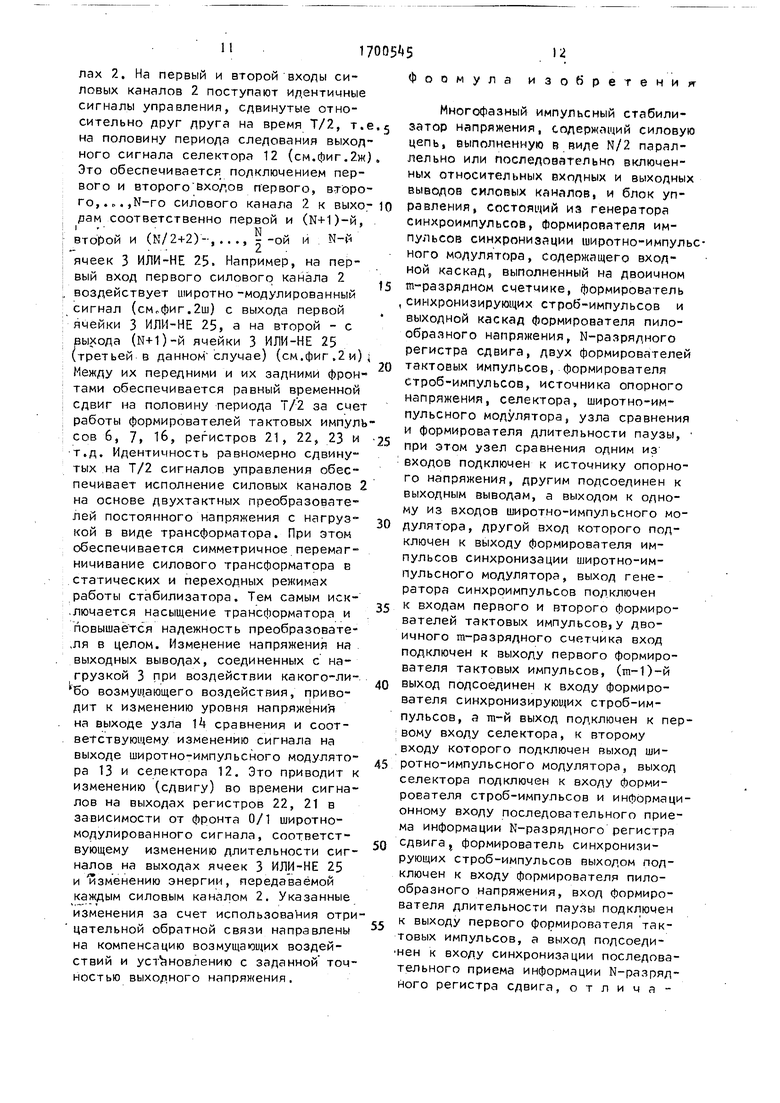

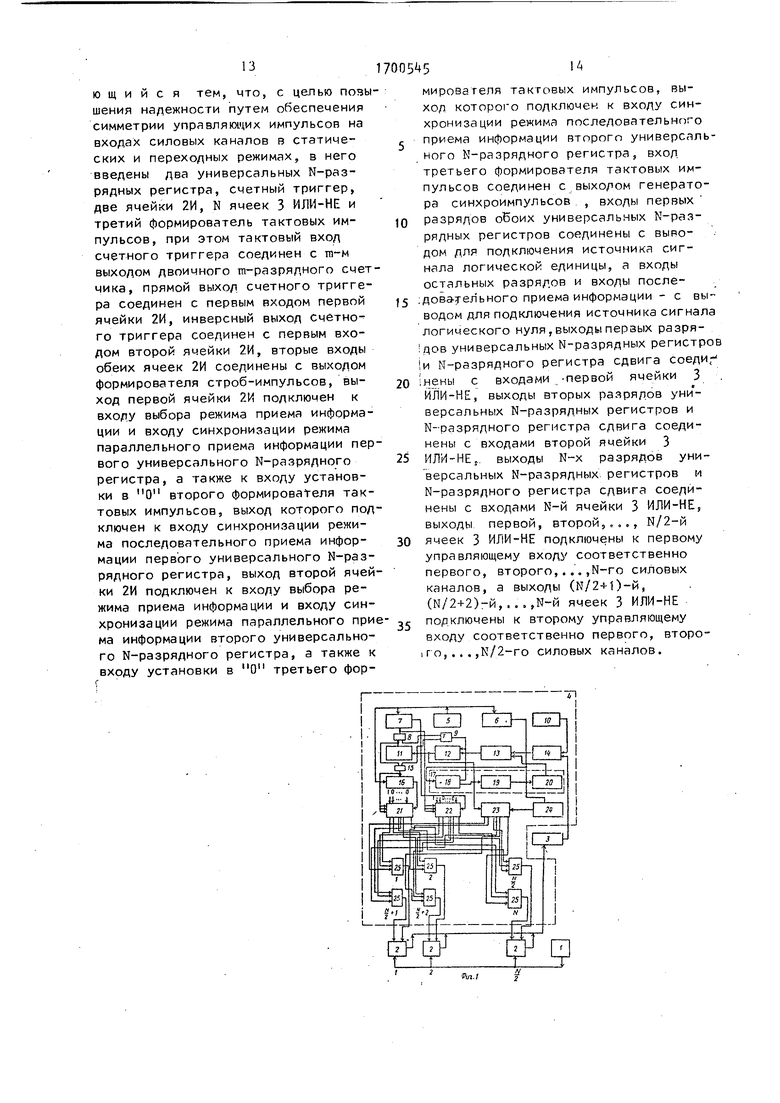

На фиг. 1 приведена блок-схема многофазного импульсного стабилизатора; на фиг.2 - временная диаграмма, поясняющая его работу.

Многофазный импульсный стабилизатор содержит входные выводы, с которыми соединен источник питания, входы силовых каналов 2, выходные выводы, к которым подключена нагрузка 3, блок k управления, состоящий из генератора 5 синхроимпульсов, первого 6 и второго 7 формирователей

ел

4

сл

тактовых импульсов, первой ячейки 2И 8, счетного триггера 9, источника 10 опорного напряжения, формирователя 11 строб-импульсов, селектора 12, широтно-импульсного модуля- тора 13, узла 1 сравнения, второй ячейки 2И 15, третьего формирователя 16 тактовых импульсов, формирователя 17 импульсов синхронизации шротно-импульсного модулятора, содержащего двоичный m-разрядный счетчик 18, формирователь 19 синхронизирующих строб- импульсов, формирователь 20 пилообразного напряжения, первого 21 и второго 22 универсального М-разрядного регистра, N-разрядного регистра 23 сдвига, формирователя 2 длительности паузы, N ячеек 3 ИЛИ-Н 25. При этом входные выводы 1 и силовые каналы 2 имеют две общие шины Узел Ik сравнения.одним входом подключен к источнику 10 опорного напряжения s другим - к входным выводам, соединенным с нагрузкой 3, а выходом к одному из входов широтно- импульсного модулятора 13 другой вход которого подключен к выходу 17 формирователя импульсов синхронизации широтно-импульсного модулятора, Выход генератора 5 синхроимпульсов подключен к входам первого 6, второго 7 и третьего 16 формирователей тактовых импульсов. У двоичного т- разрядного счетчика 18 вход, подключен к выходу первого формирователя б тактовых импульсов, (тп-1)-й выход - к входу формирователя 19 синхронизирующих строб-импульсов, а m-й выход - к первому входу селектора 12, К второму входу селектора 12 подключен выход широтно-импульснго модулятора 13. Выход селектора 12 подключен к входу формирователя 11 строб-импульсов и входу последовательного приема информации N-разрядного регистра 23 сдвига. Формирователь 19 синхронизирующих строб- импульсов выходом подключен к входу формирователя 20 пилообразного напряжения. Вход формирователя 2k длительности паузы подключен к выходу первого формирователя 6 тактовых импульсов, а выход - к входу синхронизации последовательного приема информации N-разрядного регистра 23 сдвига. Тактовый вход счетного триггера 9 соединен с m-м выходом двоичного счетчика 1В. Пря0

5

0

5

0

5

0

мой выход триггера 9 соединен с первым входом первой ячейки 2И 8, инверсный выход триггера 9 соединен с первым входом второй ячейки 2И 15. Вторые входы обеих ячеек 2И соединены с выходом формирователя 11 строб-импульсов. Выход первой ячейки 2И 8 подключен к входу выбора режима приема информации и входу синхронизации режима параллельного приема информации первого универсального N-разрядного регистра 22, а также к входу установки в О второго формирователя тактовых импульсов 7, выход которого подключен к входу синхронизации режима последовательного приема информации первого универсального N-разрядного регистра 22. Выход второй ячейки 2И 15 подключен к входу выбора режима приема информации и входу синхронизации режима параллельного приема информации второго универсального N-разрядного регистра 21, а также к входу установки в 0й третьего формирователя 16 .тактовых импульсов, выход которого подключен к входу синхронизации режима последовательного приема информации второго универсального N-разрядного регистра 21. Выходы первых разрядов регистров 21-23 соединены с входами первой ячейки 3 ИЛИ-НЕ 25, выходы вторых разрядов регистров 21-23 соединены с входами второй ячейки 3 ИЛИ-НЕ 25, выходы N-x разрядов регистров 21-23 соединены с входами N-й ячейки 3 ИЛИ-НЕ 25. Выходы первой , второй,..,

11-й ячейки 3

5

0

5

ИЛИ-НЕ 25 подключены к первому управляющему входу соответственно

N первого, второго,..., -г--го силовых

каналов 2, а выходы (+ 1 )-й,(- +2)-й5

...... N-й ячейки 3 ИЛИ-НЕ 25 - к второму управляющему входу соответстNвенно первого, второго,..., -го

силовых каналов 2. В качестве силовых каналов 2 могут быть использованы двухтактные конверторы (или два однотактных), выполненные по любой известной схеме, формирователи тактовых импульсов 6, 7, 16 и регистры 21-23 могут быть выполнены на базе двоичных счетчиков. Аппаратное задание кодов 00,...,01 на входах

регистров 21 и 22 означает подключение входов первых разрядов к шине +5В через резистор 1 «Ом и замыкание на землю входов остальных раз- рядов и входов последовательного приема. Эпюры напряжений на фиг.2 показаны для случая, когда многофазный импульсный стабилизатор содержит два двухтактных силовых канала, т.е. N 4, для понимания работы схемы этого достаточно. Сигналы показаны на:

а)выходе первого формирователя

6 тактовых импульсов ,

б)выходе формирователя 2k длительности пауяы;

в)выходе m-го разряда счетчика 1Ј

г)прямом выходе триггера 9,

д)выходе формирователя 20, пило- образного напряжения.и вхоле узла 14 сравнения

е)выходе широтно-импульсного модулятора 13J

ж)выходе селектора 12;

з)выходе первой ячейки 211 8, и) выходе второй ячейки 2И 15,

к) выходе первого разряда регистра 23;

д) выходе второго разряда регист- Ра 23;

м) выходе третьего разряда регистра 23;

н) выходе четвертого разряда регистра 23;

о) выходе первого разряда регистра 22;

п) выходе второго разряда регистра 22;

р) выходе третьего разряда регист ра 22;

с) выходе четвертого разряда регистра 22;

т) выходе первого разряда регистра 21;

у) выходе второго разряда регистра 21;

ф) выходе третьего разряда регистра 21;

х) выходе четвертого разряда ре- гистра 21;

ш) выходе первой ячейки 3 ИЛИ- НЕ 25,

щ) выходе второй ячейки 3 ИЛИ- НЕ 25;

ч) выходе третьей ячейки 3 ИЛИ- НЕ 25,

э) выходе четвертой ячейки 3 ИЛИ- НЕ 25.

Многофазный импульсный стабилизатор работает следующим образом.

С выхода генератора 5 синхроимпульсов сигнал с периодом

ги

0,01-Т-К,

5

5

0

0

5

0

5

где Т - период электрических процессов в силовых каналах 2, К - точность ( о) воспроизведения длительности импульса выходного сигнала широтно- импульсного модулятора. 13 на выходе ячеек 3 ИЛИ-НЕ 25, поступает на входы формирователей 6, 7, 16 тактовых импульсов. На выходах формирователей 6 (см.фиг.2а), 7 и 1б формируются напряжения с периодом следования Ти T/N. В общем случае эти напряжения сдвинуты по фазе относительно друг друга, так как формирователи 7 и 16 синхронизируются фронтом 0/1 сигнала с выхода селектора 12. Сигнал с выхода формирователя 16 синхронизирует сдвиг данных в регистре 21, сигнал с выхода формирователя 7 синхронизирует сдвиг данных в регистре 22. Сигнал с выхода формирователя 6 поступает на вход т-разряд- ного счетчика 18. Разрядность го является функцией числа N

m .

Выходной сигнал (т-1)-го разряда счетчика 18 используется для синхронизации широтно-импульсного модулятора 13, на фиг.2д показано напряжение развертки. На фиг.2е показан сигнал на выходе широтно-импульсного модулятора 13, его период составляет Т/2. На один вход селектора 12 подается сигнал с выхода широтно-импульсного модулятора 13 (см.фиг.2е), на другой сигнал с выхода га-го разряда счетчика 18 (см.фиг.2в). Селектор 12 пропускает на выход низкие уровни широтно-модулированного сигнала при наличии низкого уровня сигнала на выходе m-го разряда счетчика 18, в противном случае на выходе селектора наблюдается высокий уровень (см. фиг.2ж) . Таким образом сигнал на выходе селектора 12 имеет период. Т. Этим достигается ограничение максимальной длительности ширины импульса управления на уровне Т/2 при периоде следования т и обеспечивается возможность использования его для ооганизации электрических процессов в силовых каналах на очснове двухтактных преобразователей Постоянного напряжения. На перепад 0/1 выходного сигнала селектора 12 (см,фиг,2ж) формирователь 11 строб-импульсов формирует положительные строб-импулсы. Эти импульсы проходят через ячейку 2И 8 к счетчику 7, регистру 22 или через ячейку 2И 15 к счетчку 16, регистру 21 в зависимости от состояния счетного триггера 9. Стро импульс с выхода формирователя 11 в момент t проходит через ячейку 2И 15, так как в это время триггер 9 находится в состоянии О и ячейка 2И 8-заперта, а 2И 15 открыта (сМофиг,2г,и). Строб-импульс с выхода формирователя 11 в момент tz проходит через ячейку 2И 8, так как триггер Э находится в состоянии 1 (см„фиг.2г,з) и т.д. Фактически счетный триггер Э работает как (т+1)-й разряд счетчика 18. Строб-импульс, пройдя через ячейку 2И к счетчику и универсальному регистру (7-22 и 16-21 на фиг.1), производит следующие действия. Устанавливает в О формирователь тактовых импульсов (например третий 16 в момент t и второй.7 в момент t), Переводит универсальный N-разрядный регистр (21 в момент ц и 22 в момент t, фиг.2з,и) в режим параллельного приема, переписывает аппаратно заданную входную комбинацию в регистр (1 в первый разряд, О в остальные). После окончания строб-импульса Формирователь тактовых импульсов работает синхронно с фронтом 0/1 сигнала на выходе селектора 12, универсальные регистры возвращаются в режим последовательного приема информации,. На входы последовательного приема информации обоих универсальных регистров 21 и 22 аппаратно заведен уровень О. Уровень 1 из первого разряда будет сдвигаться в старшие разряды, регистры после прихода строб-импульса последовательно пребывают в следующих состояниях; 10U,...,0, 010,...,0, 001,....,О,...

оо,...,ю, оо, от,...,00,...,

00 (см.фиг.2 ОХ). За счет работы счетнбго триггера 9 синхронизация второго 7 и третьего 16 формирователей тактовых импульсов и установ

универсальных регистров в состояние 10,...,00 производится поочередно (см.Лиг.2з,и), один раз на периоде Т„ При отработке возмущений (например, интервал времени между моментами t,| и tg меньше Т) ни один из регистров не сбрасывается, не отработав поочередно все комбинации

от 10,...,00, до 00,...,00. Длительность положительного импульса на выходе любого разряда регистров 21, 22 составляет Т,и T/N. Выходной сигнал первого Формирователя 6 тактовых импульсов (см.фиг.2а) используется для синхронизации формирователя 17 и для синхронизации Формирователя 2k длительности паузы. На выходе формирователя 2k формируется

0 импульсный сигнал (фиг.26) длительности t, на период 1/0 выходного сигнала (см.фиг.2а) формирователя 6„ Длительность t,n указанных положительных импульсов выбирается

5 из условия превышения длительности времени рассасывания неосновных носителей в области базы силовых коммутирующих транзисторов силовых каналов 2. Выходной сигнал (см.фиг.26)

0 формирователя 2k используется для синхронизации регистра 23 сдвига. Выходной сигнал (см.фиг.2з) селектора 12 воздействует на информационный вход последовательного ввода

5 информации регистра 23. Запись его в первый разряд и сдвиг в последующие старшие разряды указанного регистра осуществляется фронтом 1/0 выходного сигнала (см.фиг.26) форми0 рователя 2k. В результате на выходах первого, второго,...,(N/2+l)-ro,..., N-ro разрядов регистра 23 появляются сигналы (фиг.2к,л,м,н), равномерно сдвинутые на время Tn T/N,

5 равное периоду следователя выходного сигнала (см.-фиг .26) формирователя 2k. Так как перепад 1/0 выходного синхронизирующего сигнала (см. фиг.26) формирователя 2k смещен отQ носит ельно переднего Фронта выхолно- го сигнала селектора 12 (см.фиг.2ж), то передний фронт выходного сигнала (см.фиг.2к) первого разряда регистра 23 смещен на величину tn, второго разряда - на величину Тп + tn,..., и т.д. Поскольку запись в первый разряд регистра 23 выходного сигнала селектора 12 и его сдви-г в старшие разряды (со второго по N-й) осуществляется дискретно через интервал времени ti( T/N .j то в общем случае на выходах первого, второго,...,(N/2+1)- го,...,М-го разрядов регистра 12 сиг- налы (фиг.2 к,л,м,н) отличаются от поступающего сигнала (см.фиг.2ж) на информационный вход. Максимальная ошибка воспроизведения указанного сигнала достигает величины периода Тп T/N следования синхронизирующих импульсов формирователя 2k. Однако воздействие выходных сигналов регистров 23 и 21, 22 на входы ячеек 3 ИЛИ-НЕ 25 позволяет получить на их выходах идентичные равномерно сдвинутые сигналы, отличающиеся от выходного сигнала (см„фиг.2ж) селектору 12 на величину гарантированной длительности паузы tn. При t01 на входах первой ячейки 3 ИЛИ-НЕ 25 имеются уровни сигналов: 1 с выхода первого разряда регистра 23 (см. фиг.2к), О с выхода первого разряда регистра 22 (см.фиг.2о), О с

выхода первого разряда регистра 21 (см.фиг.2т). В результате на выходе первой ячейки 3 ИЛИ-НЕ 25 наблюдается уровень О (см.фиг.2ш). В интервале 101 : t 14 на выходах пер- вых разрядов всех трех регистров будет уровень О (см.фиг.2к,о,т). В результате на выходе первой ячейки 3 ИЛИ-НЕ 25 будет уровень 1 (фиг.2ш). В момент t на выходе пер- вого разряда регистра 21 появляется положительный импульс (см.фиг.2т) синхронизированный фронтом 0/1 выходного сигнала селектора 12 (см. фиг.2ж)„ После момента t,| выход пер- вой ячейки 3 ИЛИ-НЕ 25 (см.фиг.2ш) имеет уровень О, выходной сигнал на этой ячейке точно повторяет сигнал на выходе селектора 12. Со сдвигом на Т, аналогично будут работать ос- тальные ячейки 3 ИЛИ-НЕ 25. В момент

001

на выходах первых разрядов регистров 21-23 опять уровни О, соответственно на выходе первой ячей- ки 3 ИЛИ-НЕ 25 появляется уровень 1. В момент t2 фронтом 0/1 сигнала на выходе селектора 12 через формирователь 11, ячейки 2И 8 синхронизируется счетчик 7 и появляется уровень 1 на выходе первого разряда регистра 22 (см.фиг.2о). В это время в регистре 21 уровень 1 еще в третьем разряде (см.фиг .2ф) .Теперь сдвиг 1 в регистре 22 производится

5 ю 15 20

25

30 35 0 45

0

5

выходным сигналом второго Формирова- . теля 7 тактовых импульсов, синхронизированного в момент t, в это же время продолжается сдвиг 1 в регистре 21 выходным сигналом третьего формирователя 16 тактовых импульсов, синхронизированного в момент с .Так как моменты t, и t сдвинуты относительно друг друга не менее чем на Т/2, а регистры 21 и 22 после прохода всех комбинаций автоматически устанавливаются в О, никаких сбоев в работе стабилизатора не наступает. В момент t регистр 22 выходным сигналом первого разряда (см.фиг.2о) устанавливает в О выход первой ячейки 3 ИЛИ-НЕ 25 (см.фиг.2ш). В момент to3 регистр 21 выходным сигналом четвертого разряда (см.фиг.2х) устанавливает в О выход четвертой ячейки 3 ИЛИ-НЕ 25 (см.Аиг.2з). Управляющий импульс на выходе четвертой ячейки 3 ИЛИ-НЕ 25 получается по длительности таким же, как и импульсы в остальных ячейках 3 ИЛИ-НЕ (см. фиг.2ш-э). Формирователи 68 7, 16 имзют одинаковую разрядность. Это обеспечивает формирование ими тактовых импульсов с равным периодом Т. но сдвинутых (в общем случае) по фазе, так как начальные состояния формирователей 7 и 16 синхронизируются в моменты времени, совпадающие с фронтом 0/1 широтно-модулиро- ванного сигнала (см.фиг.2ж) селектора 12, длительность которого лежит в интервале 04 ии с Т/2. Поэтому оба фронта широтно-модулированного сигнала (см.) воспроизводятся на выходах ячеек 3 ИЛИ-НЕ 25 точно с равным временным сдвигом Т Т/М„ (Ьронт 0/1 на выходах ячеек 3 ИЛИ-МЕ 25 воспроизводится с помощью выходных сигналов с разрядов регистра 21 (см.фиг.2к-н). фронт 1/10 на выходах ячеек 3 ИЛИ-НЕ 25 воспроизводится с помощью выходных сигналов с разрядоз регистров 21 или 22 (см.фиг.2 о-х) . В результате на выходах ячеек 3 ИЛИ- НЕ 25 получаются широтно-модулиро- ванные импульсы (см„фиг,2 ш-э), равномерно сдоинутые на время Ти и равные по длительности сигналу на выходе селектора 12 (см,фиг.2ж). Сдвиг во времени на величину Ти T/N данных сигналов управления обеспечивает равномерный сдвиг во времени электрических процессов в силовых каналах 2. На первый и второй входы силовых каналов 2 поступают идентичные сигналы управления, сдвинутые относительно друг друга на время Т/2, т. на половину периода следования выход ного сигнала селектора 12 (см.фиг.2ж Это обеспечивается подключением первого и второго входов первого, второго,. „,,N-ro силового канала 2 к выходам соответственно первой и (Ы+1)-й,

второй и (N/2+2)-, . .., | -ой и N-й

ячеек 3 ИЛИ-НЕ 25. Например, на первый вход первого силового канала 2 воздействует широтно-модулированный сигнал (см„фиг.2ш) с выхода первой ячейки 3 ИЛИ-НЕ 25, а на второй - с выхода (N+0-й ячейки 3 ИЛИ-НЕ 25 (третьей в данном случае) (см.фиг,2 и) Между их передними и их задними фронтами обеспечивается равный временной сдвиг на половину периода Т/2 за смет работы формирователей тактовых импульсов 6, 7 16, регистров 21, 22, 23 и т.д. Идентичность равномерно сдвинутых на Т/2 сигналов управления обеспечивает исполнение силовых каналов 2 на основе двухтактных преобразователей постоянного напряжения с нагрузкой в виде трансформатора. При этом обеспечивается симметричное перемаг- ничивание силового трансформатора в статических и переходных режимах работы стабилизатора. Тем самым исключается насыщение трансформатора и повышается надежность преобразователя в целом. Изменение напряжения на выходных выводах, соединенных с нагрузкой 3 при воздействии какого-ли- 1бо возмущающего воздействия, приводит к изменению уровня напряжения на выходе узла 1 сравнения и соответствующему изменению сигнала на выходе широтно-импульсного модулятора 13 и селектора 12. Это приводит к изменению (сдвигу) во времени сигналов на выходах регистров 22, 21 в зависимости от фронта 0/1 широтно- модулированного сигнала, соответствующему изменению длительности сигналов на выходах ячеек 3 ИЛИ-НЕ 25 и изменению энергии, передаваемой каждым силовым каналом 2. Указанные изменения за счет использования отрицательной обратной связи направлены на компенсацию возмущающих воздействий и установлению с заданной точностью выходного напряжения.

5

фоомула изобретение

Многофазный импульсный стабилизатор напряжения, содержащий силовую цепь, выполненную в виде N/2 параллельно или последоаательно включенных относительных входных и выходных выводов силовых каналов, и блок управления, состоящий из генератора синхроимпульсов, формирователя импульсов синхронизации широтно-импульсного модулятора, содержащего входной каскад, выполненный на двоичном

5 tn-разрядном счетчике, формирователь ,синхронизирующих строб-импульсов и выходной каскад формирователя пилообразного напряжения, N-разрядного регистра сдвига, двух формирователей

0 тактовых импульсов, формирователя строб-импульсов, источника опорного напряжения, селектора, широтно-импульсного модулятора, узла сравнения и формирователя длительности паузы, при этом узел сравнения одним из входов подключен к источнику опорного напряжения, другим подсоединен к выходным выводам, а выходом к одному из входов широтио-импульсного мо0 дулятора, другой вход которого подключен к выходу формирователя импульсов синхронизации широтно-импульсного модулятора, выход генератора синхроимпульсов подключен

5 к входам первого и второго Формирователей тактовых импульсов, у двоичного m-разрядного счетчика вход подключен к выходу первого формирователя тактовых импульсов, (т-1)-й

0 выход подсоединен к входу формирователя синхронизирующих строб-импульсов, а та-й выход подключен к первому входу селектора, к второму входу которого подключен выход ши5 ротно-импульсного модулятора, выход селектора подключен к входу Формирователя строб-импульсов и информационному входу последовательного приема информации N-разрядного регистра

0 сдвига формирователь синхронизирующих строб-импульсов выходом подключен к входу формирователя пилообразного Напряжения, вход формирователя длительности паузы подключен

5 к выходу первого формирователя тактовых импульсов, а выход подсоединен к входу синхронизации последовательного приема информации N-разрядного регистра сдвига, о т л и ч а ю щ и и с я тем, что, с целью повышения надежности путем обеспечения симметрии управляющих импульсов на входах силовых каналов в статических и переходных режимах, в него введены два универсальных N-раз- рядных регистра, счетный триггер, две ячейки 2И, N ячеек 3 ИЛИ-НЕ и третий формирователь тактовых импульсов, при этом тактовый вход счетного триггера соединен с та-м выходом двоичного m-разрядного счетчика, прямой выход счетного триггера соединен с первым входом первой ячейки 2И, инверсный выход счетного триггера соединен с первым входом второй ячейки 2И, вторые входы обеих ячеек 2И соединены с выходом формирователя строб-импульсов, выход первой ячейки 2И подключен к входу выбора режима приема информации и входу синхронизации режима параллельного приема информации первого универсального N-разрядного регистра, а также к входу установки в О второго формирователя тактовых импульсов, выход которого подключен к входу синхронизации режима последовательного приема информации первого универсального N-разрядного регистра, выход второй ячейки 2И подключен к входу выбора режима приема информации и входу синхронизации режима параллельного прима информации второго универсального N-разрядного регистра, а также к входу установки в О третьего фор0

5

0

5

0

5

мирователя тактовых импульсов, выход которого подключен к входу синхронизации режима последовательного приема информации второго универсального N-разрядного регистра, вход третьего формирователя тактовых импульсов соединен с выходом генератора синхроимпульсов , входы первых разрядов обоих универсальных N-раз- рядных регистров соединены с выводом для подключения источника сигнала логической единицы, а входы остальных разрядов и входы последовательного приема информации - с выводом для подключения источника сигнала логииеского нуля,выходы первых разря- дов универсальных N-разрядных регистров и N-разрядного регистра сдвига соеди- ,нены с входами -первой ячейки 3 ИЛИ-НЕ, выходы вторых разрядов универсальных N-разрядных регистров и N-разрядного регистра сдвига соединены с входами второй ячейки 3 ИЛИ-НЕ, выходы N-x разрядов универсальных N-разрядных регистров и N-разрядного регистра сдвига соединены с входами N-й ячейки 3 ИЛИ-НЕ, выходы первой, второй,,.., N/2-й ячеек 3 ИЛИ-НЕ подключены к первому управляющему входу соответственно первого, второго,...,N-ro силовых каналов, а выходы (N/2+1)-fi, (М/2+2)-й,...,Н-й ячеек 3 ИЛИ-НЕ подключены к второму управляющему входу соответственно первого, второ- iг о,...,N/2-ro силовых каналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265741A1 |

| Многофазный импульсный стабилизатор напряжения | 1983 |

|

SU1156032A1 |

| Многофазный импульсный стабилизатор напряжения | 1987 |

|

SU1483438A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265743A1 |

| Многозонный стабилизатор постоянного напряжения | 1990 |

|

SU1700544A1 |

| Блок управления многофазным импульсным стабилизатором | 1983 |

|

SU1123085A1 |

| Многофазный импульсный стабилизатор | 1984 |

|

SU1196830A1 |

| Многофазный импульсный стабилизатор | 1982 |

|

SU1070528A1 |

| Многофазный импульсный стабилизатор | 1982 |

|

SU1019413A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1317415A1 |

Изобретение относится к источникам вторичного электропитания электротехнической и радиоэлектронной аппаратуры.Цель изобретения - повышение надежности.Силовые каналы 2,подключенные параллельно к входным выводам, преобразуют входное напряжение заданного уровня. Это напряжение на входе узла 1U сравнения сравнивается с опорным напряжением источника 10. Полученный сигнал ошибки с сигналом формирователя 17 импульсов синхронизации формирует на выходе широтно- импульсного модулятора 13 последовательность управляющих импульсов. Эти импульсы через селектор 12, формирователь 11 строб - импульсов и первую 8 и вторую 15 ячейки 2И управляют работой первого 21 и второго 22 уни- , версальных N-разрядных регистров, а также N-разрядным регистром 23 сдвига. Выходные сигналы N-x разрядов регистров 21-23 селектируется N-й ячейкой 3 ИЛИ-НЕ 25. На входы управления каждого силового канала 2 поступают сигналы соответственно с выходов N-й и (N/2+О-й ячеек 3 ИЛИ-НЕ 25, чем достигается симметрия управляющих импульсов, исключающая возможность одностороннего насыщения трансформаторов силовых каналов 2. 2 ил. (Я

| Вопросы радиоэлектроники | |||

| Серия общетехническая, вып.2, 1981, с.128, рис.7 | |||

| Авторское свидетельство СССР № ,.кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Авторское свидетельство СССР № , кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-12-23—Публикация

1990-01-10—Подача