(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ОБСЛУЖИВАНИЕМ ЗАПРОСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обслуживания запросов | 1980 |

|

SU942023A1 |

| Многоканальное устройство для обслуживания запросов | 1978 |

|

SU769542A1 |

| Устройство для обслуживания запросов | 1985 |

|

SU1347080A1 |

| Многоканальное устройство динамического приоритета | 1981 |

|

SU970371A1 |

| УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА | 1993 |

|

RU2087939C1 |

| Устройство для обслуживания сообщений | 1983 |

|

SU1104517A1 |

| Устройство для обслуживания группы запросов | 1988 |

|

SU1562913A1 |

| Многоканальное устройство приоритета | 1988 |

|

SU1580364A1 |

| Устройство для сопряжения каналов ввода-вывода с устройством управления оперативной памятью | 1984 |

|

SU1265788A1 |

| Устройство переменного приоритета | 1983 |

|

SU1149259A1 |

Изобретение относится к вычислительной технике, в частности к системам селективного пользования.

Известно многоканальное устройство приоритетных прерываний, содержащее каналы, блок управления, шифратор, регистр, элемент ИЛИ tl .

Недостатком данного устройства является большой объем оборудования.

Наиболее близким по технической сущности и достигаемому результату к предлагаемому является устройство для управления запуском программ, содержащее блок управления, распределители импульсов, триггер управления, блок установки исходного состояния, вентили записи, триггера записи, вентили выдачи элементы ИЛИ, шифраторы, регистр, счетчик дешифратора f 2 .

Недостатком данного устройства является также большой объем оборудования.

Цель изобретения - сокращение объема оборудования.

Поставленная цель достигается тем, что в устройство для управления обслуживанием запросов, содержащее триггер управления, элемент И, ре,гистр сдвига, первый, втооой элементц ИЛИ;Счетчик, первый дешифратор, выходной регистр, шифратор, каналы, а в каждом канале первый элемент ИЛИ, первую, вторую группуэлементов И, группу триггеров канала, причем каждый вход первого элемента ИЛИ канала соединен с соответствующим запросным входом группу запросных входов устройства, выход первого элемента ИЛИ

10 устройства соединен со входом счетчика, выход счетчика соединен со входом первого дешифратора, каждый выход первого дешифратора соединен с первым входом соответствукяцего элемента

15 И первой группы каждого канала, выход каждого регистра сдвига соединен с первым входом соответствукицего элемента И второй группы каждого канала, выход последнего разряда

20 регистра сдвига соединен с первым управляющим входом регистра сдвига, выход каждого элемента И первой группы каждого канала соединен с единичным входом соответствующего триггера

25 группы триггеров своего кангша, выход каждого триггера группы каждого канала соединен со вторым входом соответствующего элемента И второй группы своего канала, выход каждого элемента

30 И второй группы каждого канала соединен с нулевЕлм входом соответствующег триггера .группы своего канала и с соответствующим входом первого элемента ИЛИ своего канала, выход первого элемента ИЛИ каждого канала соединен с соответствующим входом второго элемента ИЛИ, выход шифратора соединен с информационным входом выходного регистра, выход выходного регистра соединен с информационным выходом устройства, управляющий вход выходного регистра соединен с первым управляющим входом устройства, выход второго элемента ИЛИ соединен с единичным входом триггера управления нулевой вход триггера управления соединен со вторым управляющим входом устройства, выход триггера управления соединен с первым входомэлемента И, второй вход элемента И соединен с третьим управляющим входом устройства, выход элемента И соединен с информационным входом регистра сдвига, второй управляющий вход регистра сдвига соединен с четвертым управляющим входом устройства, введены второй дешифратор, а в каждом канале второй элемент ИЛИ, причем каждый вход второго элемента ИЛИ каждого канала соединен с соответствующим запросным входом устройства, выход второго элемента ИЛИ каждого канала соединен со вторым входом каждого элемента И первой группы своего канала, каждый вход второго дешифратора соединен с выходом соответствующего первого элемента ИЛИ каждого канала, выходы второго дешифратора соединены с входами шифратора.

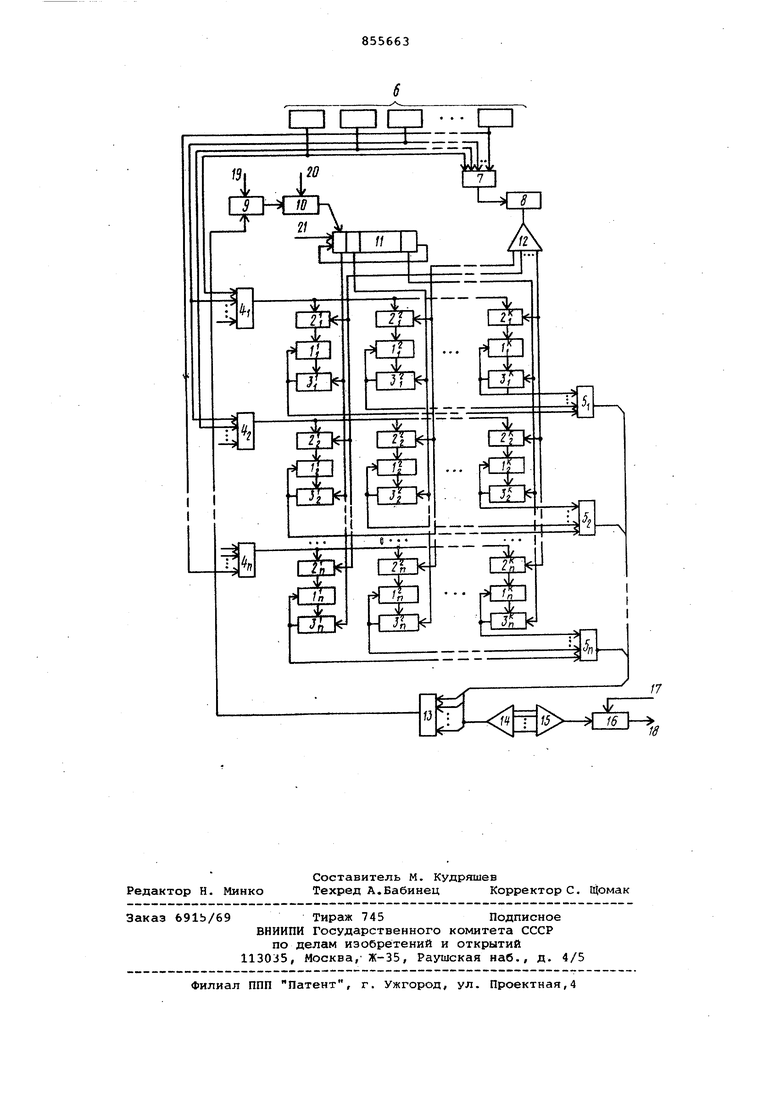

На чертеже приведена структурная схема устройства..

Устройство содержит триггеры групп триггеров каналов, гэрвые группы элементов И каналов, вторые группы элементов И каналов, вторые элементы ИЛИ 4.-4 каналов, первые элементы ИЛИ , каналов, группа запросных входов 6 устройства, первый элемент ИЛИ 7, счетчик 8,-Триггер 9 управления, элемент И 10, регистр ll сдвига, первый дешифратор 12, второй элемент ИЛ 13, второй дешифратор 14, шифратор 15, выходной регистр 16, первый управляющий вход 17 устройства, информационный выход 18 устройства,второй управляющий вход 19 устройства, третий управляющий вход 20 устройства, четвертый управляющий вход 21 устройства.

Устройство работает следующим образом.

В исходном состоянии триггеры , 9, регистры 11 и 16,счетчик 8 обнулены. Устройство готово к приему запросов. Запрос от одного из входов группы входов 6 поступает на входы элементов ИЛИ 4 . . . .4,

выполняющих роль шифратора двоичного кода, а также через элемент ИЛИ 7, счетчик 8 и дешифратор 12 - на первые входы элементов И 2;|2{J,

Элементы ИЛИ , преобразуют

одиночный сигнал запроса в сигналы двоичного кода номера источника запроса . Сигналы двоичного кода с выходов элемента ИЛИ поступают далее на вторые входы элементов И . Первый пришедший запрос пропускается элементами И и фиксируется в триггерах , в виде двоичного кода номера источника запросов. С приходом второго запроса разрешающий потенциал появляется на втором выходе дешифратора 12. Тем самым открываются другие элементы И 2, из групп элементов И 2 и происходит запоминание запроса на триггерах 1J ...... 1,. Одновременно с

запоминанием запроса происходит выборка запросов для обслуживания. Регистр 11 сдвига поочередно опрашивает группы элементов И . Считываемый код запроса через элементы ИЛИ (, поступает через дешифратор 14, шифратор 15 в регистр 16. При этом с выходов элементов И - соответствующей группы снимаются сигналы, которые обнуляют триггеры этой группы. Дешифратор. 14 и шифратор 15 преобразуют код номера источника запрос в адрес начальной команды программы, обслуживающий данный запрос. Одновременно сигналы кода запроса через элемент ИЛИ 13 поступают на единичный вход триггера 9, в результате чего блокируется работа регистра 11 сдвига. По окончании обслуживания запроса из ЭВМ на управляющий вход 20 поступает сигнал готовности к обслуживанию следующего запроса. Происходит запуск регистра 11 сдвига, и выборка запросов для обслуживания продолжается. Адрес начальной команды программы считывается с выхода 18 по управляющему сигналу входа 19.

Уменьшение аппаратурных затрат, а именно количества триггеров, очередности и вентилей записи и выдачи достигается тем, что происходит запоминание двоичного кода номера источника запросов, а не одиночного сигнала при поступлении запроса ма обслуживание.

Формула изобретения

Устройство для управления обслуживанием запросов, содержащее триггер управления, элемент И, регистр сдвига, первый, второй элементы ИЛИ, счетчик, первый дешифратор, выходной регистр, шифратор, каналы, а в каждом канале первый элемент ИЛИ, первую, вторую группу элементов И,

группу триггеров канала, причем каждый вход первого элемента ИЛИ канала соединен с соответствующим запросным входом группы запросных входов устройства, выход первого элемента ИЛИ устройства соединен со входом счетчика, выход счетчика соединен со входом первого дешифратора, каждый выход первого дешифратора соединен с первьь- входом соответствующего элемента И первой Группы каждого канала, выход каждого разряда регистра сдвига соединен с первым входом соответствующего элемента И второй группы каждого канала, выход последнего разряда регистра сдвига соединён с первым управляющим входом регистра сдвига, илхрд каждого элемента И первой группы каладоГо канала соединен с единичным входом соответствующего триггера группы своего канала, выход каждого триггера Группы каждого канала соединен со входом соответствупюег элемента И второй Группы своего канала, вьлход каждого элемента И второй группы каждого канала соединен с нулевым входом соответствукмцеГр триггера группы своего канала и с соответствующим входом первого элемента ИЛИ своего канала, выход первого элемента ИЛИ каждоГо канала соединен с соответствук)Ц|им входом второго элемента ИЛИ, выход шифратора соеди нен с информационным входом выходиоГо регистра, выход выходного регистра соединен с информационным выходом устроЯства, управлякхций вход

выходного регистра соединен с первым управляющим входом устройства, выход второго элемента ИЛИ соединен с единичным входом триггера управления, нулевой вход триггера управления соединен со вторым управляюоим входом устройства, выход триггера управлении соединен с первым входом элемента И, второй вход элемента И соединен с третьим управляющим входом устройства, выход элемента

0 И соединен с информационным входом регистра сдвига, второй управляющий вход регистра сдвига соединен с четвертьм управляющим входом устройства, Охличающеес я тем, что,

5 с целью сокращения оборудования, устройство содержит второй дешифратор, а в каждом канале второй элемент ИЛИ, причем каждый вход второго элемента ИЛИ каждого канала соединен с соот0ветствующим запросным входом группы запроснЕ входов устройства, выход второго элемента ИЛИ каждого канала соединен со вторым входом каждого элемента h первой группы своего канала, каждый вход второго дешифра5тора соединен с выходом соответствующего первого элемента ИЛИ каждого канала, выходы второго дешифратора соединены с входами шифратора. Источники информации,

0 принятые во внимание при экспертизе

5 (прототип).

Авторы

Даты

1981-08-15—Публикация

1979-11-01—Подача