со 00 со 4;

00

со

Изобретение относится к цифровой технике и может использоваться в схемах контроля формирователей опорных частот, а также в устройствах автонодстройки частоты и поэлементной синхронизации систем передачи дискретных сообщений.

Целью изобретения является расширение диапазона временных параметров входных сигналов за счет исключения влияния на работу устройства длительностей импульсов входных последовательностей.

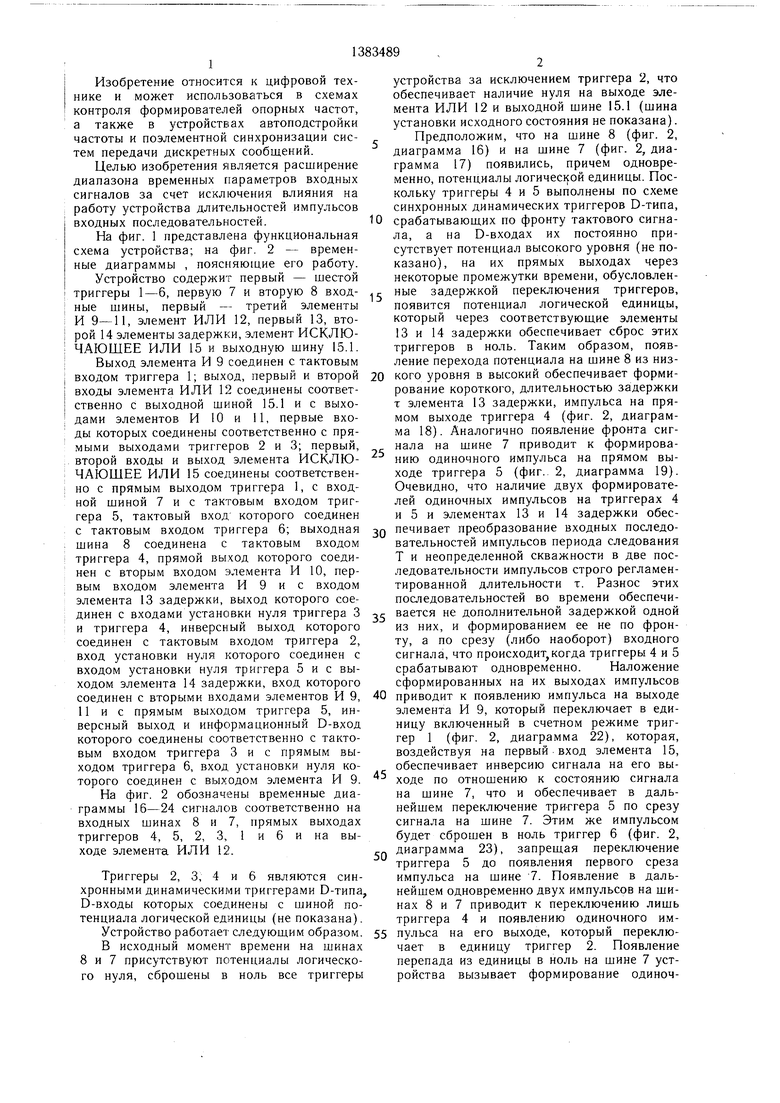

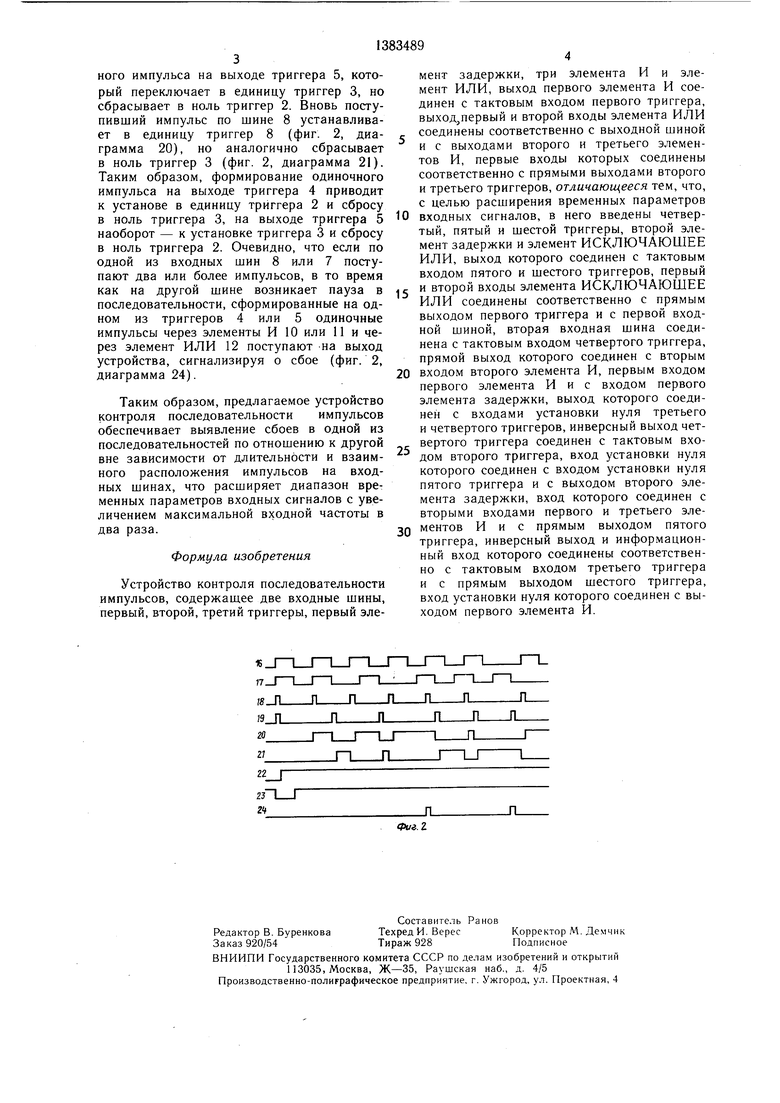

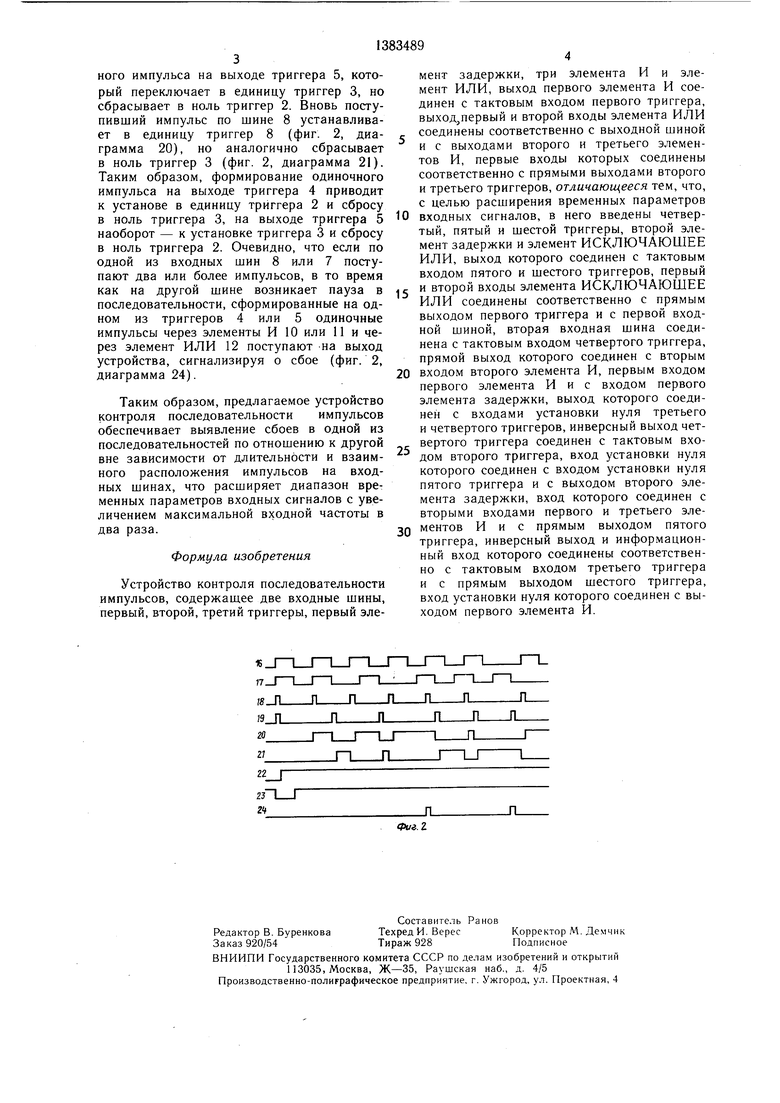

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - временные диаграммы , поясняющие его работу. Устройство содержит первый - щестой I триггеры 1-6, первую 7 и вторую 8 вход- ; ные шины, первый - третий элементы И 9-11, элемент ИЛИ 12, первый 13, вто- i рой 14 элементы задержки, элемент ИСКЛЮ- : ЧАЮШЕЕ ИЛИ 15 и выходную шину 15.1. I Выход элемента И 9 соединен с тактовым

устройства за исключением триггера 2, что обеспечивает наличие нуля на выходе элемента ИЛИ 12 и выходной щине 15.1 (шина установки исходного состояния не показана). Предположим, что на шине 8 (фиг. 2, диаграмма 16) и на шине 7 (фиг. 2, диаграмма 17) появились, причем одновременно, потенциалы логической единицы. Поскольку триггеры 4 и 5 выполнены по схеме синхронных динамических триггеров D-типа, 10 срабатывающих по фронту тактового сигнала, а на D-входах их постоянно присутствует потенциал высокого уровня (не показано), на их прямых выходах через некоторые промежутки времени, обусловленные задержкой переключения триггеров, появится потенциал логической единицы, который через соответствующие элементы 13 и 14 задержки обеспечивает сброс этих триггеров в ноль. Таким образом, появление перехода потенциала на шине 8 из низвходом триггера 1; ВЕ)1ход, первый и второй 20 кого уровня в высокий обеспечивает форми- входы элемента ИЛИ 12 соединены соответ-рование короткого, длительностью задержки

ственно с выходной шиной 15.1 и с выхо-т элемента 13 задержки, импульса на прядами элементов И 10 и 11, первые вхо-мом выходе триггера 4 (фиг. 2, диаграмды которых соединены соответственно с пря-ма 18). Аналогично появление фронта сигмыми выходами триггеров 2 и 3; первый, второй входы и выход элемента ИСКЛЮ- ЧАЮШЕЕ ИЛИ 15 соединены соответственно с прямым выходом триггера 1, с входной шиной 7 и с тактовым входом триггера 5, тактовый вход которого соединен

нала на шине 7 приводит к формированию одиночного импульса на прямом выходе триггера 5 (фиг., 2, диаграмма 19). Очевидно, что наличие двух формирователей одиночных импульсов на триггерах 4 и 5 и элементах 13 и 14 задержки обесс тактовым входом триггера 6; выходная о печивает преобразование входных последовательностей импульсов периода следования Т и неопределенной скважности в две последовательности импульсов строго регламентированной длительности т. Разнос этих последовательностей во времени обеспечи- динен с входами установки нуля триггера 3 ос вается не дополнительной задержкой одной и триггера 4, инверсный выход которогоиз них, и формированием ее не по фронту, а по срезу (либо наоборот) входного сигнала, что происходит,когда триггеры 4 и 5 срабатывают одновременно. Наложение сформированных на их выходах импульсов

соединен с вторыми входами элементов И 9, 40 приводит к появлению импульса на выходе 11 и с прямым выходом триггера 5, ин-элемента И 9, который переключает в едишина о соединена с тактовым входом триггера 4, прямой выход которого соединен с вторым входом элемента И 10, первым входом элемента И 9 и с входом элемента 13 задержки, выход которого соесоединен с тактовым входом триггера 2, вход установки нуля которого соединен с входом установки нуля триггера 5 и с выходом элемента 14 задержки, вход которого

версный выход и информационный D-вход которого соединены соответственно с тактовым входом триггера 3 и с прямым выходом триггера 6, вход установки нуля которого соединен с выходом элемента И 9.

На фиг. 2 обозначены временные диаграммы 16-24 сигналов соответственно на входных шинах 8 и 7, прямых выходах триггеров 4, 5, 2, 3, 1 и 6 и на выходе элемента ИЛИ 12.

ницу включенный в счетном режиме триггер 1 (фиг. 2, диаграмма 22), которая, воздействуя на первый вход элемента 15, обеспечивает инверсию сигнала на его выходе по отношению к состоянию сигнала на шине 7, что и обеспечивает в дальнейшем переключение три-ггера 5 по срезу сигнала на шине 7. Этим же импульсом будет сброшен в ноль триггер 6 (фиг. 2, диаграмма 23), запрещая переключение триггера 5 до появления первого среза импульса на шине 7. Появление в дальнейшем одновременно двух импульсов на щи- нах 8 и 7 приводит к переключению лишь

ницу включенный в счетном режиме триггер 1 (фиг. 2, диаграмма 22), которая, воздействуя на первый вход элемента 15, обеспечивает инверсию сигнала на его выходе по отношению к состоянию сигнала на шине 7, что и обеспечивает в дальнейшем переключение три-ггера 5 по срезу сигнала на шине 7. Этим же импульсом будет сброшен в ноль триггер 6 (фиг. 2, диаграмма 23), запрещая переключение триггера 5 до появления первого среза импульса на шине 7. Появление в дальнейшем одновременно двух импульсов на щи- нах 8 и 7 приводит к переключению лишь

Триггеры 2, 3, 4 и 6 являются синхронными динамическими триггерами D-типа, D-входы которых соединены с шиной потенциала логической единицы (не показана).

Устройство работает следующим образом. 55 пульса на его выходе, который переклю

В исходный момент времени на шинах чает в единицу триггер 2. Появление

8 и 7 присутствуют потенциалы логическо- перепада из единицы в ноль на шине 7 устго нуля, сброшены в ноль все триггеры ройства вызывает формирование одиночтриггера 4 и появлению одиночного имг

устройства за исключением триггера 2, что обеспечивает наличие нуля на выходе элемента ИЛИ 12 и выходной щине 15.1 (шина установки исходного состояния не показана). Предположим, что на шине 8 (фиг. 2, диаграмма 16) и на шине 7 (фиг. 2, диаграмма 17) появились, причем одновременно, потенциалы логической единицы. Поскольку триггеры 4 и 5 выполнены по схеме синхронных динамических триггеров D-типа, 0 срабатывающих по фронту тактового сигнала, а на D-входах их постоянно присутствует потенциал высокого уровня (не показано), на их прямых выходах через некоторые промежутки времени, обусловленные задержкой переключения триггеров, появится потенциал логической единицы, который через соответствующие элементы 13 и 14 задержки обеспечивает сброс этих триггеров в ноль. Таким образом, появление перехода потенциала на шине 8 из низ0 кого уровня в высокий обеспечивает форми- рование короткого, длительностью задержки

нала на шине 7 приводит к формированию одиночного импульса на прямом выходе триггера 5 (фиг., 2, диаграмма 19). Очевидно, что наличие двух формирователей одиночных импульсов на триггерах 4 и 5 и элементах 13 и 14 задержки обесницу включенный в счетном режиме триггер 1 (фиг. 2, диаграмма 22), которая, воздействуя на первый вход элемента 15, обеспечивает инверсию сигнала на его выходе по отношению к состоянию сигнала на шине 7, что и обеспечивает в дальнейшем переключение три-ггера 5 по срезу сигнала на шине 7. Этим же импульсом будет сброшен в ноль триггер 6 (фиг. 2, диаграмма 23), запрещая переключение триггера 5 до появления первого среза импульса на шине 7. Появление в дальнейшем одновременно двух импульсов на щи- нах 8 и 7 приводит к переключению лишь

пульса на его выходе, который переклю

триггера 4 и появлению одиночного имного импульса на выходе триггера 5, который переключает в единицу триггер 3, но сбрасывает в ноль триггер 2. Вновь поступивший импульс по шине 8 устанавливает в единицу триггер 8 (фиг. 2, диаграмма 20), но аналогично сбрасывает в ноль триггер 3 (фиг. 2, диаграмма 21). Таким образом, формирование одиночного импульса на выходе триггера 4 приводит к установе в единицу триггера 2 и сбросу

мент задержки, три элемента И и элемент ИЛИ, выход первого элемента И соединен с тактовым входом первого триггера, выход первый и второй входы элемента ИЛИ соединены соответственно с выходной шиной и с выходами второго и третьего элементов И, первые входы которых соединены соответственно с прямыми выходами второго и третьего триггеров, отличающееся тем, что, с целью расширения временных параметров

в ноль триггера 3, на выходе триггера 5 входных сигналов, в него введены четвер- наоборот - к установке триггера 3 и сбросутый, пятый и шестой триггеры, второй эле мент задержки и элемент ИСКЛЮЧАЮЩЕЕ

ИЛИ, выход которого соединен с тактовым входом пятого и шестого триггеров, первый .с и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с прямым выходом первого триггера и с первой входной шиной, вторая входная шина соединена с тактовым входом четвертого триггера, прямой выход которого соединен с вторым 20 входом второго элемента И, первым входом первого элемента И и с входом первого элемента задержки, выход которого соединен с входами установки нуля третьего и четвертого триггеров, инверсный выход четвертого триггера соединен с тактовым входом второго триггера, вход установки нуля которого соединен с входом установки нуля пятого триггера и с выходом второго элемента задержки, вход которого соединен с вторыми входами первого и третьего эле- 3Q ментов И и с прямым выходом пятого триггера, инверсный выход и информационный вход которого соединены соответственно с тактовым входом третьего триггера и с прямым выходом шестого триггера, вход установки нуля которого соединен с выходом первого элемента И.

в ноль триггера 2. Очевидно, что если по одной из входных шин 8 или 7 поступают два или более импульсов, в то время как на другой шине возникает пауза в последовательности, сформированные на одном из триггеров 4 или 5 одиночные импульсы через элементы И 10 или 11 и через элемент ИЛИ 12 поступают на выход устройства, сигнализируя о сбое (фиг. 2, диаграмма 24).

Таким образом, предлагаемое устройство контроля последовательности импульсов обеспечивает выявление сбоев в одной из последовательностей по отношению к другой вне зависимости от длительности и взаимного расположения импульсов на входных шинах, что расширяет диапазон временных параметров входных сигналов с увеличением максимальной входной частоты в два раза.

Формула изобретения

Устройство контроля последовательности импульсов, содержащее две входные шины, первый, второй, третий триггеры, первый эле25

мент задержки, три элемента И и элемент ИЛИ, выход первого элемента И соединен с тактовым входом первого триггера, выход первый и второй входы элемента ИЛИ соединены соответственно с выходной шиной и с выходами второго и третьего элементов И, первые входы которых соединены соответственно с прямыми выходами второго и третьего триггеров, отличающееся тем, что, с целью расширения временных параметров

входных сигналов, в него введены четвер- тый, пятый и шестой триггеры, второй эле.с 20 3Q

25

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ ПО ФРОНТУ И СРЕЗУ СИГНАЛОВ | 1987 |

|

SU1537106A1 |

| Формирователь импульсов | 1986 |

|

SU1455385A1 |

| Цифровой измеритель длительности одиночных импульсов | 1984 |

|

SU1257600A1 |

| Устройство для расширения временных интервалов | 1986 |

|

SU1406561A1 |

| Формирователь синхронизированных импульсов | 1989 |

|

SU1651360A1 |

| Устройство фазовой синхронизации | 1985 |

|

SU1332553A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Десятичный счетчик | 1980 |

|

SU921094A1 |

| Устройство для формирования пачки импульсов | 1983 |

|

SU1193784A1 |

| Формирователь одиночного импульса | 1989 |

|

SU1626352A1 |

Изобретение относится к цифровой технике и может быть использовано в схемах контроля формирователей опорных частот, а также устройствах автоподстройки частоты и поэлементной синхронизации систем передачи дискретных сообщений. Изобретение расширяет диапазон временных параметров входных сигналов, что достигается за счет исключения влияния на работу устройства длительностей импульсов входных последовательностей. Устройство содержит триггеры 1-6, входные шины 7 и 8, элементы И 9-11, элемент ИЛИ 12, элементы 13 и 14 задержки, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 15 и входную шину 15.1. Устройство обеспечивает выявление сбоев в одной из последовательностей по отношению к другой вне зависимости от длительности и взаимного расположения импульсов на входных шинах, что расширяет диапазон временных параметров входных сигналов с увеличением максимальной входной частоты в два раза. 2 ил. сл

| Устройство для контроля последовательности импульсов | 1980 |

|

SU869052A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| , Авторское свидетельство СССР № 1175029, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-03-23—Публикация

1986-07-09—Подача