1

Изобретение относится к вычислительной технике и, в частности, к средствам автоматического контроля цифровых объектов, и может быть использовано для высокочастотной функциональной проверки узлов ЭВМ, построенных с использованием микросхем большой степени интеграции.

Цель изобретения - повьвпение быстродействия устройства и увеличение глубины контроля за счет изменения в широких пределах вероятностных и временных параметров генерируемых им последовательностей.

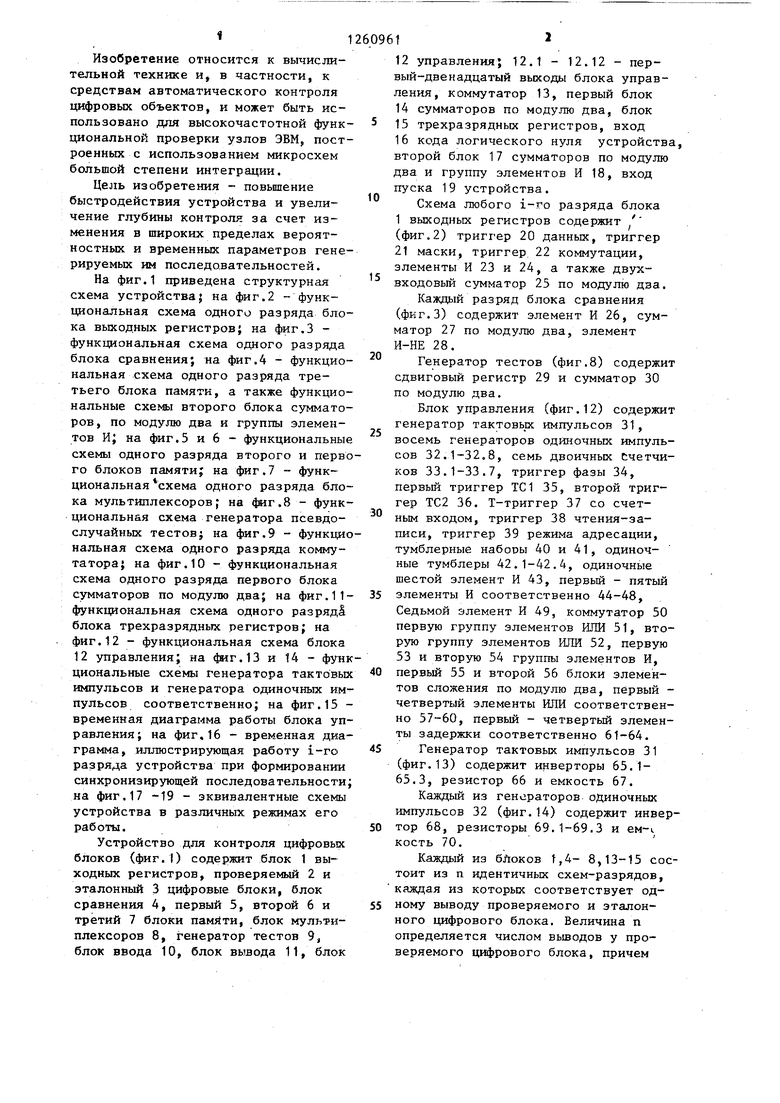

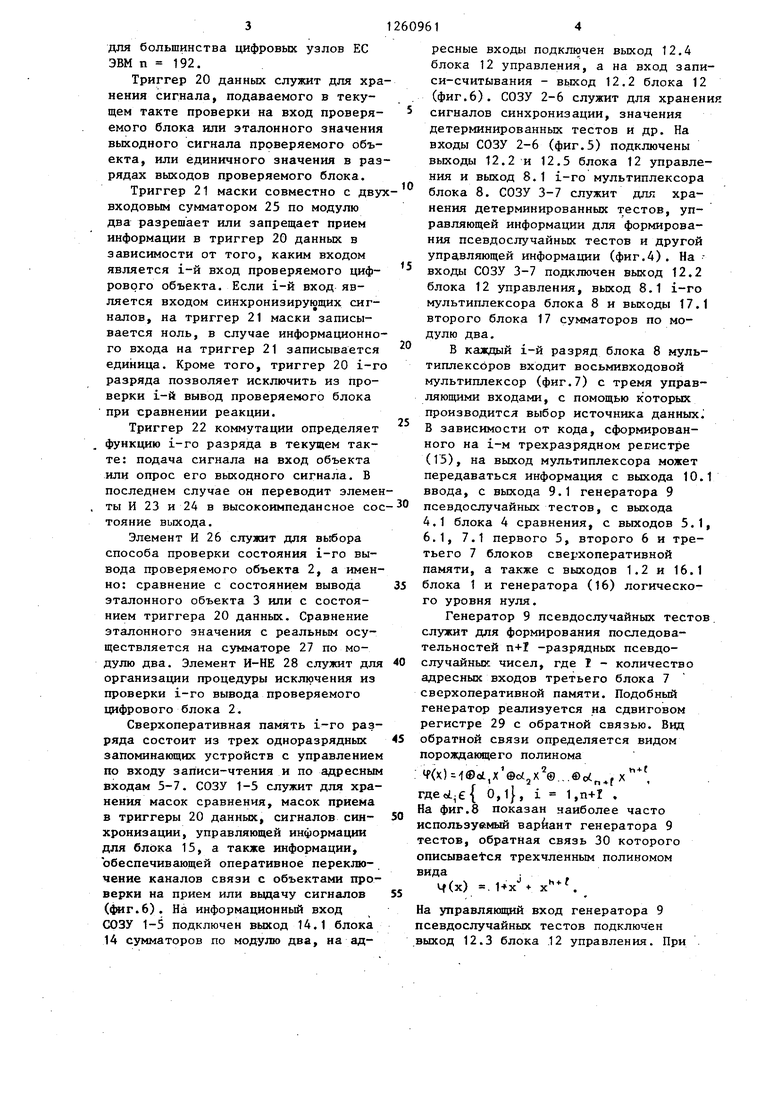

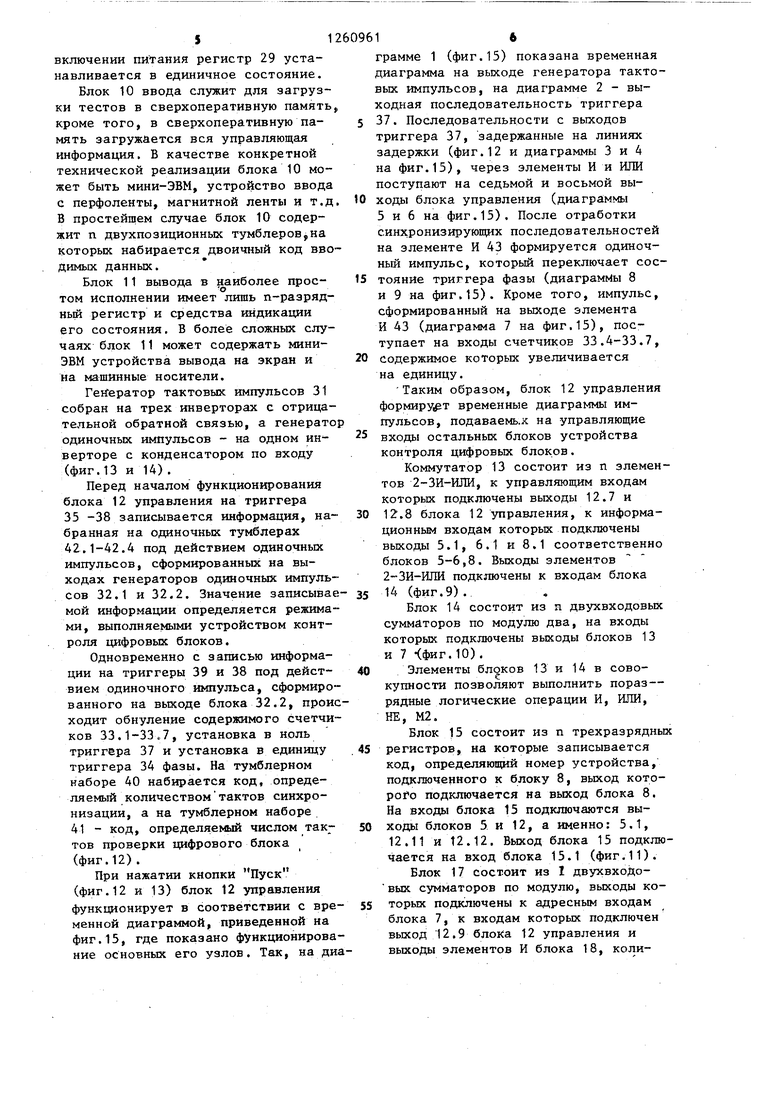

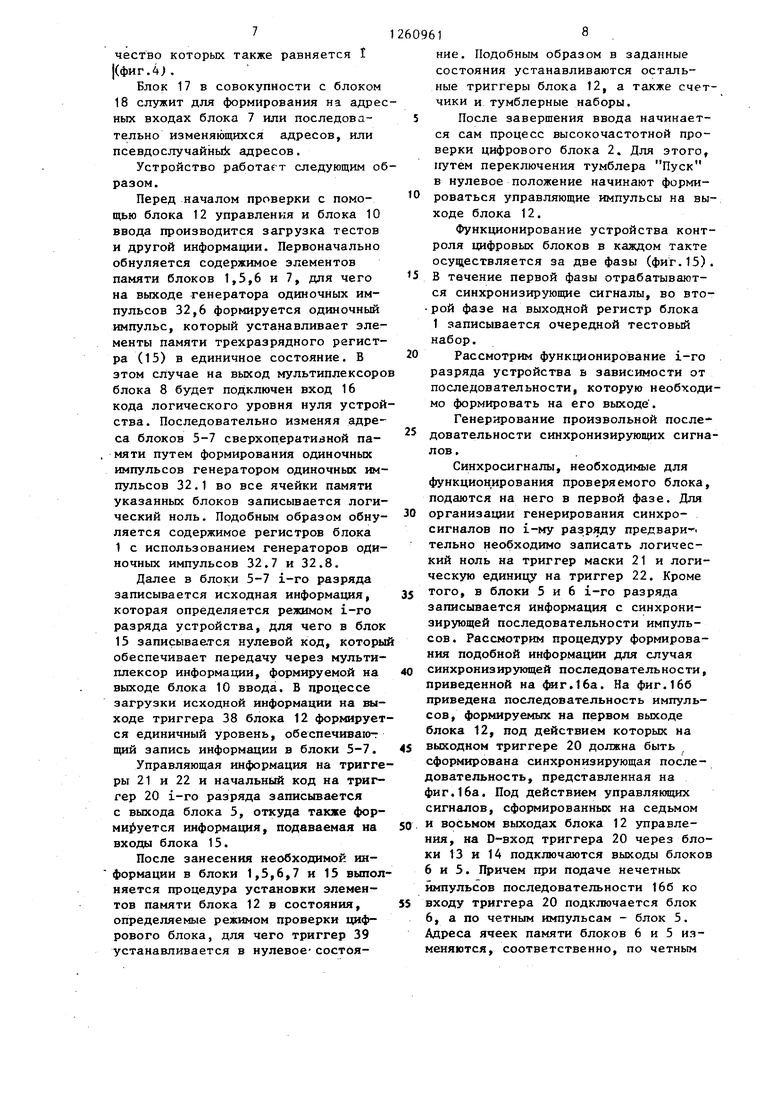

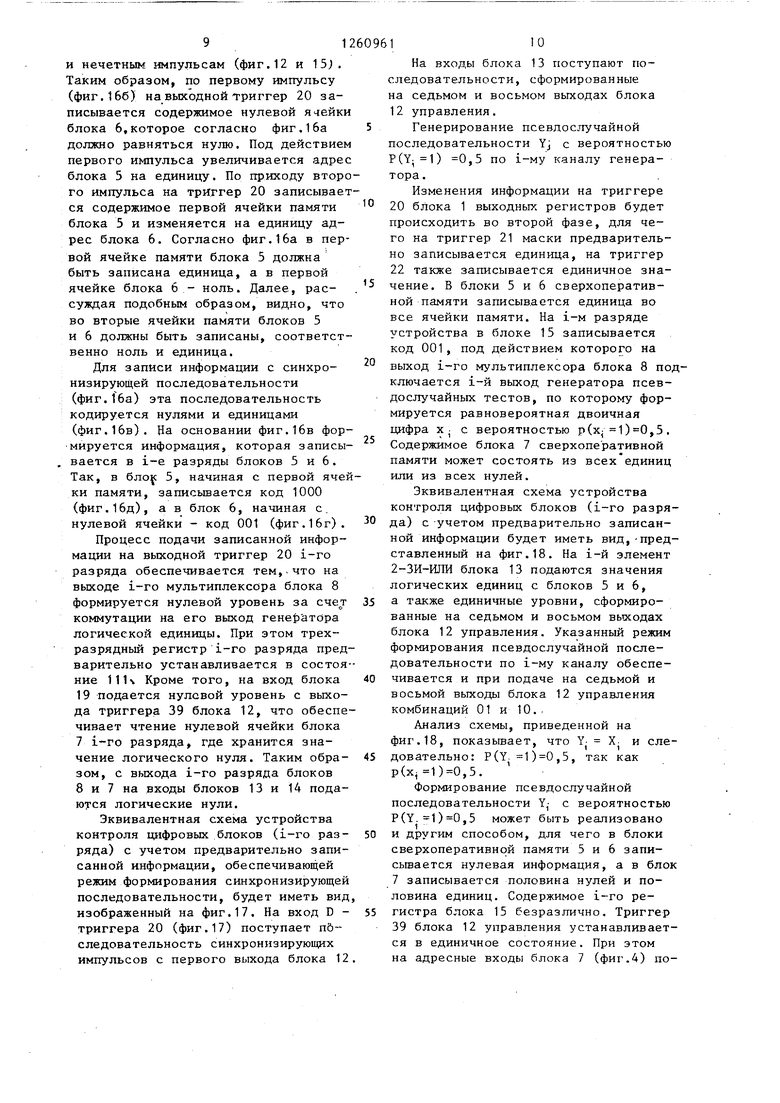

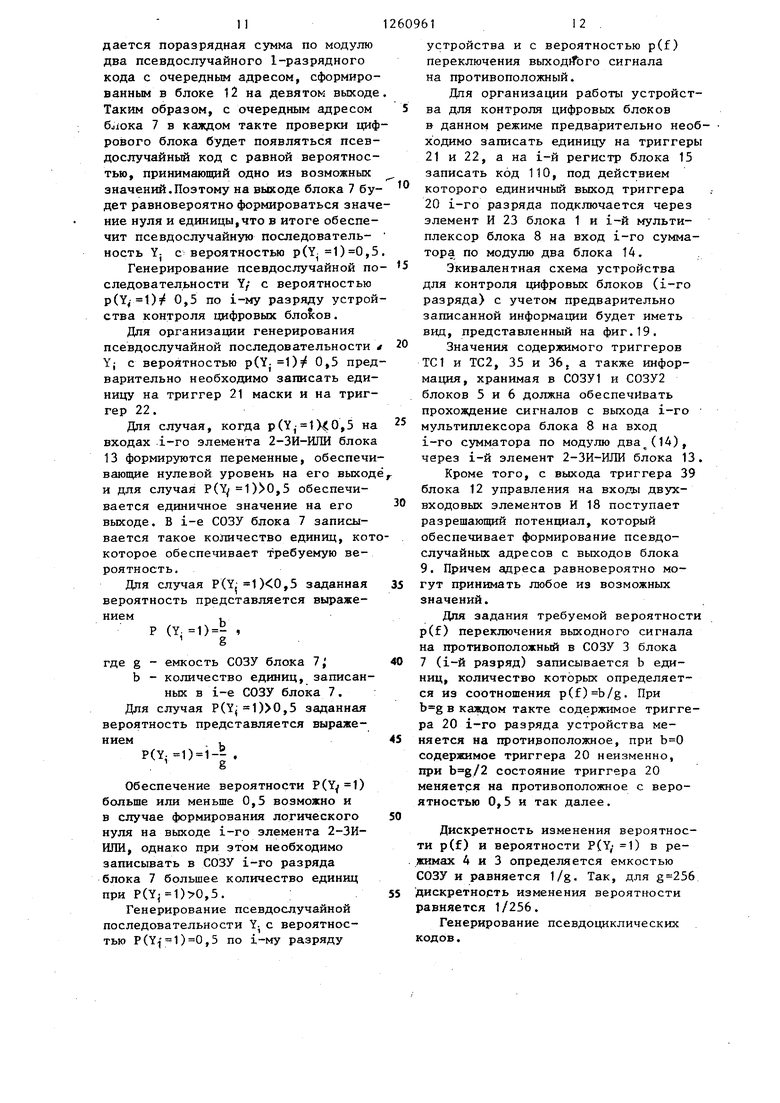

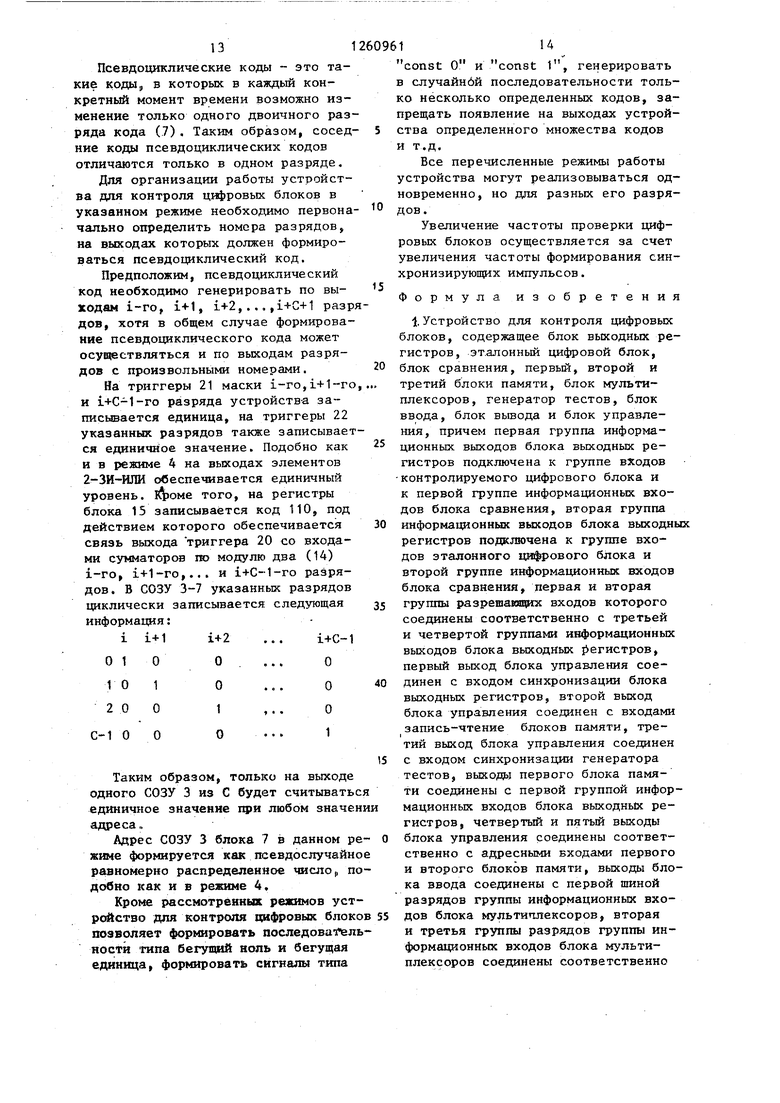

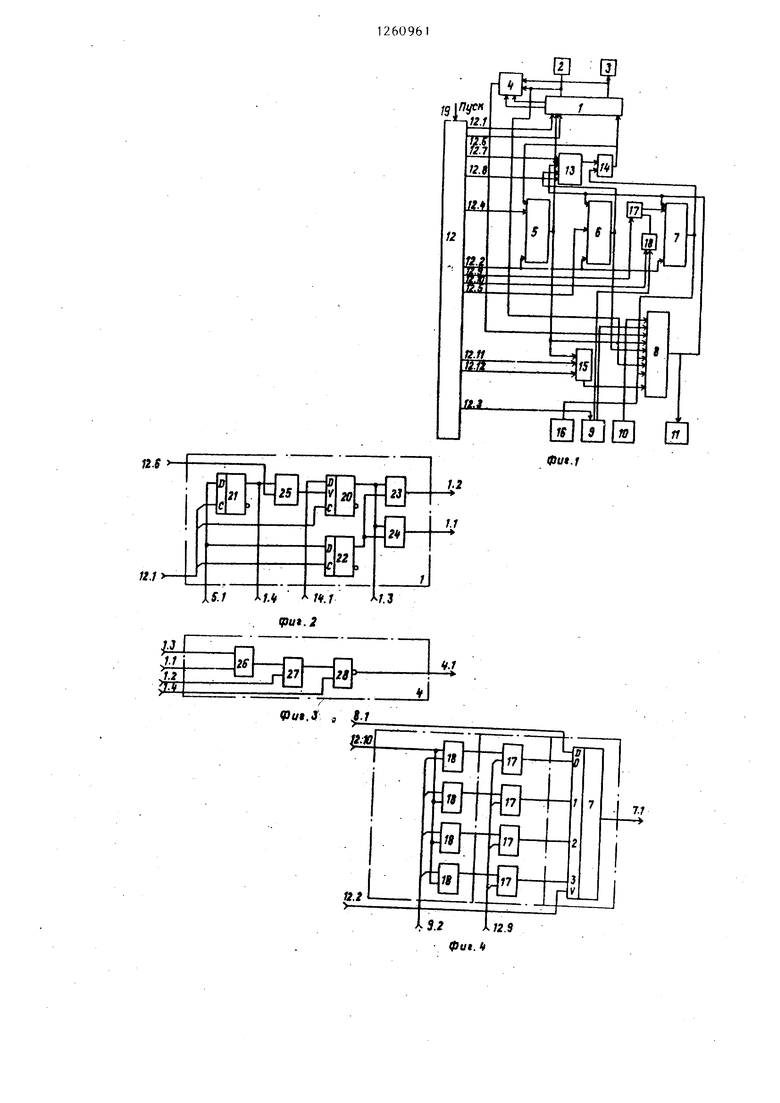

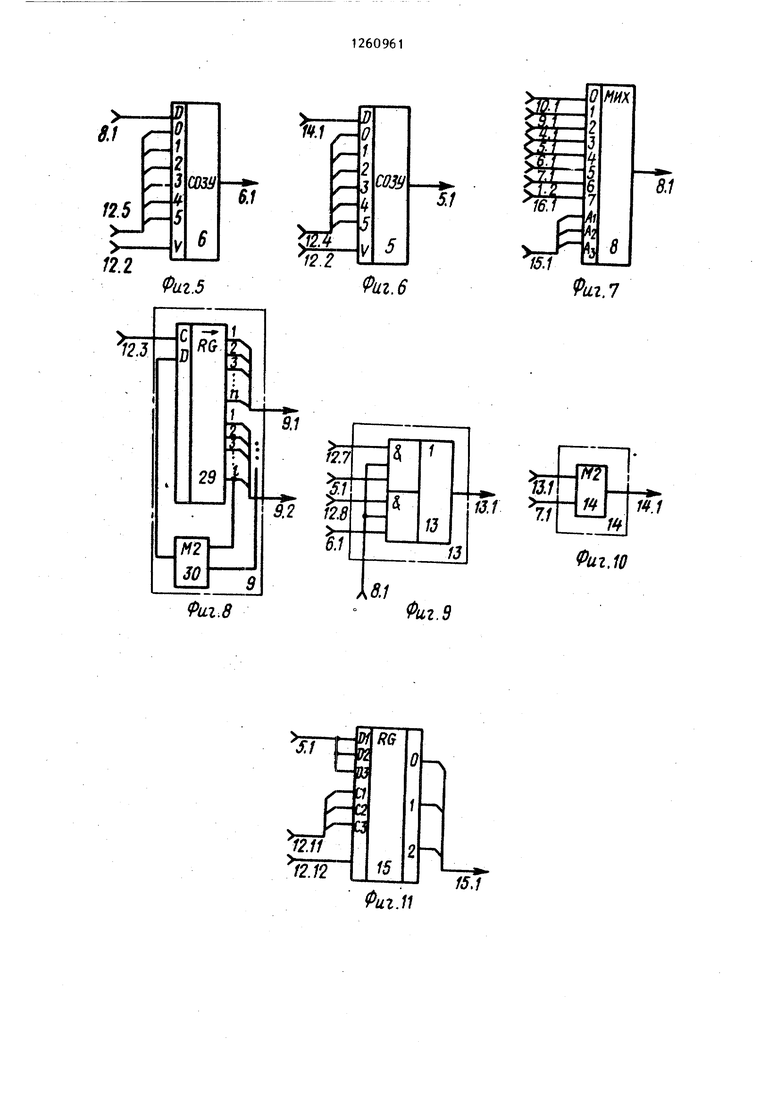

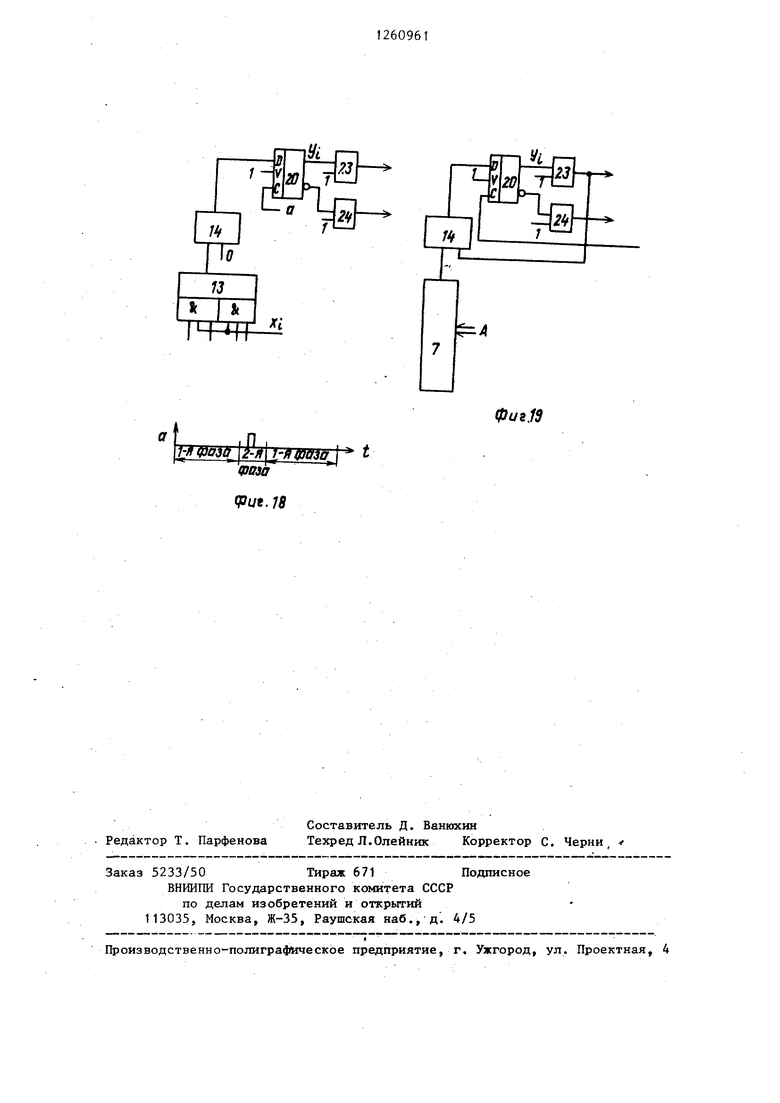

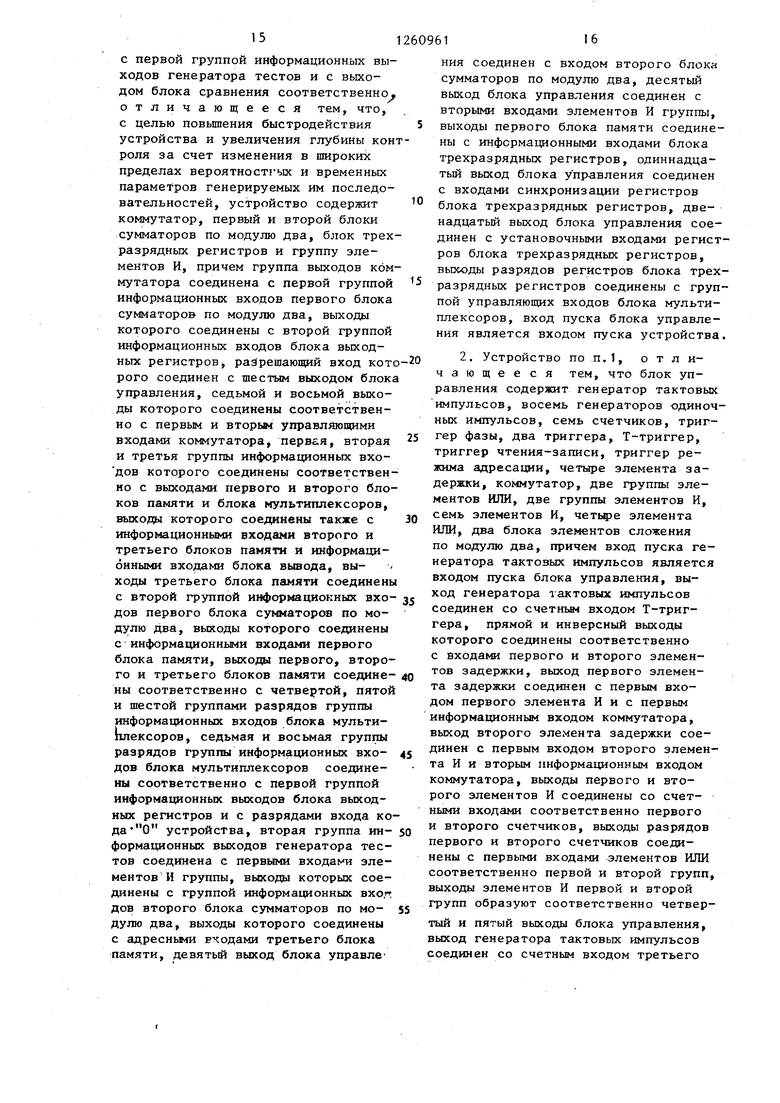

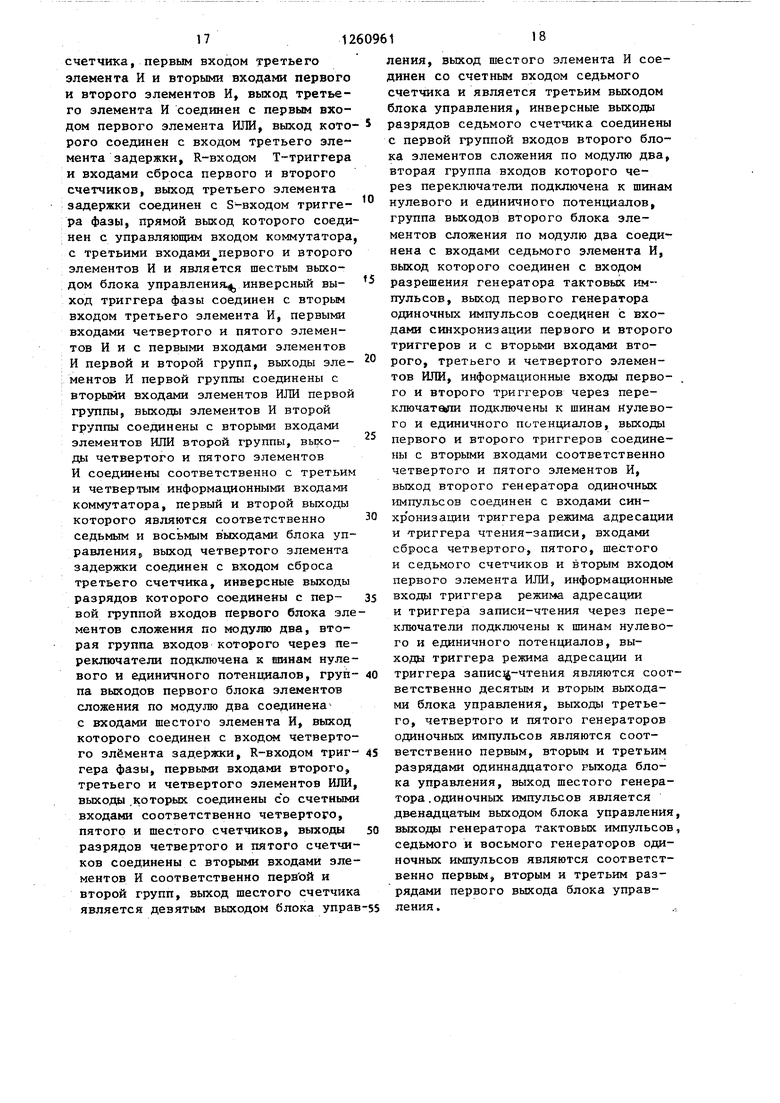

На фиг.1 приведена структурная схема устройства; на фиг.2 - функциональная схема одного разряда блока выходных регистров; на фиг.З - функциональная схема одного разряда блока сравнения; на фиг.4 - функциональная схема одного разряда третьего блока памяти, а также функциональные схемы второго блока сумматоров, по модулю два и группы элементов И; на фиг.З и 6 - функциональные схемы одного разряда второго и первого блоков памятиJ на фиг.7 функциональная схема одного разряда блока мультиплексоров; на фиг.8 - функциональная схема генератора псевдослучайных тестов; на фиг.9 - функциональная схема одного разряда коммутатора} на фиг.10 - функциональная схема одного разряда первого блока сумматоров по модулю два; на фиг.11- функциональная схема одного разряд блока трехразрядных регистров; на фиг.12 - функциональная схема блока 12 управления; на фиг.13 и 14 - функциональные схемы генератора тактовых импульсов и генератора одиночных импульсов соответственно; на фиг.15 - временная диаграмма работы блока управления; на фиг,16 - временная диаграмма, иллюстрирующая работу i-ro разряда устройства при формировании синхронизирующей последовательности на фиг.17 -19 - эквивалентные схемы устройства в различных режимах его работы.

Устройство для контроля цифровых блоков (фиг.1) содержит блок 1 выходных регистров, проверяемый 2 и эталонный 3 цифровые блоки, блок сравнения 4, первый 5, второй 6 и третий 7 блоки памйти, блок мультиплексоров 8, генератор тестов 9, блок ввода 10, блок вывода 11, блок

;

10

15

20

25

260961

12 управления; 12.1 - 12.12 - пер- вый-двенадцатый выходы блока управления, коммутатор 13, первый блок

14сумматоров по модулю два, блок

15трехразрядньк регистров, вход

16кода логического нуля устройства, второй блок 17 сумматоров по модулю два и группу элементов И 18, вход пуска 19 устройства.

Схема любого i-ro разряда блока 1 выходных регистров содержит (фиг.2) триггер 20 данных, триггер 21 маски, триггер 22 коммутации, элементы И 23 и 24, а также двух- входовый сз мматор 25 по модулю два.

Каждый разряд блока сравнения (фкг.З) содержит элемент И 26, сумматор 27 по модулю два, элемент И-НЕ 28.

Генератор тестов (фиг.8) содержит сдвиговый регистр 29 и сумматор 30 по модулю два.

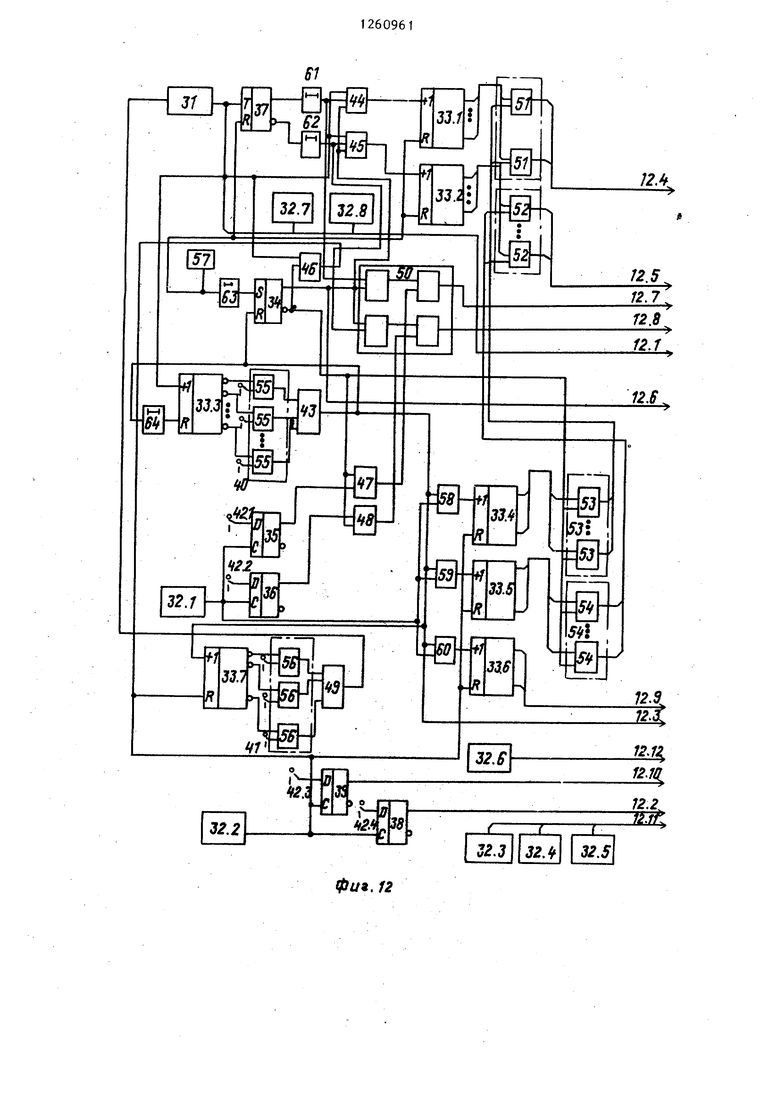

Блок управления (фиг.12) содержит генератор тактовьк импульсов 31, восемь генераторов одиночных импульсов 32.1-32.8, семь двоичных Счетчиков 33.1-33.7, триггер фазы 34, первый триггер ТС1 35, второй триггер ТС2 36. Т-триггер 37 со счетным входом, триггер 38 чтения-записи, триггер 39 режима адресации, тумблерные наборы 40 и 41, одиночные тумблеры 42.1-42.4, одиночные шестой элемент И 43, первый - пятый элементы И соответственно 44-48, Седьмой элемент И 49, коммутатор 50 первую группу элементов ИЛИ 51, вторую группу элементов ИЛИ 52, первую 53 и вторую 54 группы элементов И, первый 55 и второй 56 блоки элементов сложения по модулю два, первый - четвертый элементы ИЛИ соответственно 57-60, первый - четвертый элементы задержки соответственно 61-64.

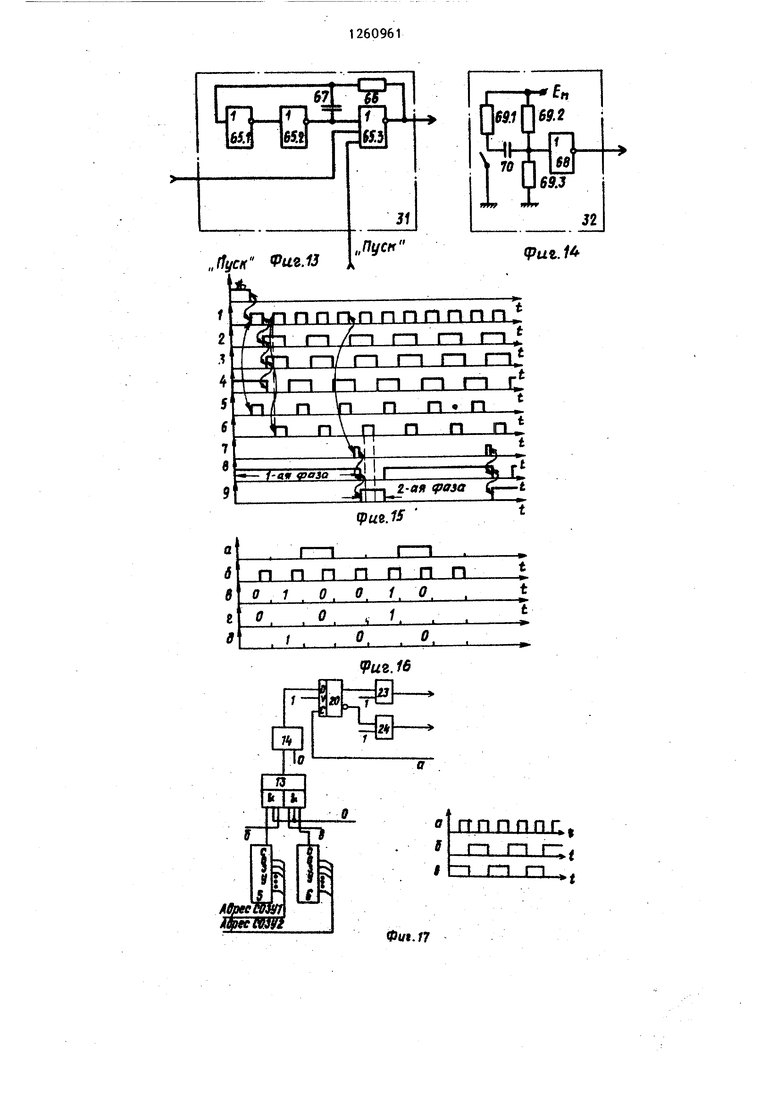

Генератор тактовых импульсов 31 (фиг.13) содержит инверторы 65.1- 65.3, резистор 66 и емкость 67.

Каждый из генераторов одиночных импульсов 32 (фиг.14) содержит инвертор 68, резисторы 69.1-69.3 и ем-i. кость 70.

Каждый из блоков t,4- 8,13-15 состоит из п идентичных схем-разрядов, каждая из которых соответствует одному выводу проверяемого и эталонного цифрового блока. Величина п определяется числом вьшодов у проверяемого цифрового блока, причем

30

35

40

45

50

55

для большинства цифровых узлов ЕС ЭВМ п 192.

Триггер 20 данных служит для хранения сигнала, подаваемого в текущем такте проверки на вход проверяемого блока или эталонного значения выходного сигнала проверяемого объекта, или единичного значения в разрядах выходов проверяемого блока.

Триггер 21 маски совместно с двух входовым сумматором 25 по модулю два разрешает или запрещает прием информации в триггер 20 данных в зависимости от того, каким входом является i-й вход проверяемого цифрового объекта. Если i-й вход является входом синхронизирующих сигналов, на триггер 21 маски записывается ноль, в случае информационного входа на триггер 21 записывается единица. Кроме того, триггер 20 i-ro разряда позволяет исключить из проверки i-й вывод проверяемого блока при сравнении реакции.

Триггер 22 коммутации определяет функцию i-ro разряда в текущем такте: подача сигнала на вход объекта или опрос его выходного сигнала. В последнем случае он переводит элементы И 23 и 24 в высокоимпедансное состояние выхода.

Элемент И 26 служит для выбора способа проверки состояния i-ro вывода проверяемого объекта 2, а именно: сравнение с состоянием вывода эталонного объекта 3 или с состоянием триггера 20 данных. Сравнение эталонного значения с реальным осуществляется на сумматоре 27 по модулю два. Элемент И-НЕ 28 служит для организации процедуры исключения из проверки i-ro вывода проверяемого цифрового блока 2.

Сверхоперативная память i-ro разряда состоит из трех одноразрядных запоминающих устройств с управлением по входу записи-чтения и по адресным входам 5-7. СОЗУ 1-5 служит для хранения масок сравнения, масок приема в триггеры 20 данных, сигналов синхронизации, управляющей информации для блока 15, а также информации, обеспечивающей оперативное переключение каналов связи с объектами проверки на прием или выдачу сигналов (4мг.6). На информационный вход СОЗУ 1-5 подключен выход 14.1 блока 14 сумматоров по модулю два, на ад10

ресные входы подключен выход 12.4 блока 12 управления, а на вход записи-считывания - выход 12.2 блока 12 . (фиг.6). СОЗУ 2-6 служит для хранения 5 сигналов синхронизации, значения детерминированных тестов и др. На входы СОЗУ 2-6 (фиг.5) подключены выходы 12.2 и 12.5 блока 12 управления и выход 8.1 i-ro мультиплексора блока 8. СОЗУ 3-7 служит для хранения детерминированных тестов, управляющей информации для формирования псевдослучайных тестов и другой управляющей информации (фиг.4). На входы СОЗУ 3-7 подключен выход 12.2 блока 12 управления, выход 8.1 i-ro мультиплексора блока 8 и выходы 17.1 второго блока 17 сумматоров по модулю два.

В каждый i-й разряд блока 8 мультиплексоров входит восьмивходовой мультиплексор (фиг.7) с тремя управляющими входами, с помощью которых производится выбор источника данных В зависимости от кода, сформированного на i-M трехразрядном ресистре (15), на выход мультиплексора может передаваться информация с выхода 10.1 ввода, с выхода 9.1 генератора 9

0 псевдослучайных тестов, с выхода

4.1 блока 4 сравнения, с выходов 5.1, 6.1, 7.1 первого 5, второго 6 и третьего 7 блоков сверхоперативной памяти, а также с выходов 1.2 и 16.1

5 блока 1 и генератора (16) логического уровня нуля.

Генератор 9 псевдослучайных тестов служит для формирования последовательностей п+1 -разрядных псевдо0 случайных чисел, где I - количество адресных входов третьего блока 7 сверхоперативной памяти. Подобный генератор реализуется на сдвиговом регистре 29 с обратной связью. Вид

5 обратной связи определяется видом порождающего полинома

4(x)-1®ot,x ®ot,jX €).,.€)o(f , гдео(..е{ 0,1}, i 1,п+1 . На фиг.8 показан наиболее часто используб;ьалй вариант генератора 9 тестов, обратная связь 30 которого описываешься трехчленньш полиномом

0

вида

Ч(х) . l+x .

На управляющий вход генератора 9 псевдослучайных тестов подключён выход 12.3 блока .12 управления. При

включении питания регистр 29 устанавливается в единичное состояние.

Блок 10 ввода служит для загрузки тестов в сверхоперативную память кроме того, в сверхоперативную па- мять загружается вся управляющая информация, В качестве конкретной технической реализации блока 10 может быть мини-ЭВМ, устройство ввода с перфоленты, магнитной ленты и т.д В простейшем случае блок 10 содержит п двухпозиционных тумблеров,на которых набирается двоичный код вводимых данных.

Блок 11 вывода в наиболее прос- том исполнении имеет лишь п-разряд- ньм регистр и средства индикации его состояния. В более сложных случаях блок 11 может содержать мини- ЭВМ устройства вывода на экран и на машинные носители.

Гейератор тактовых импульсов 31 собран на трех инверторах с отрицательной обратной связью, а генерато одиночных импульсов - на одном ин - верторе с конденсатором по входу (фиг.13 и 14).

Перед началом функционирования блока 12 управления на триггера 35 -38 записывается информация, на- бранная на одиночньк тумблерах 42.1-42.4 под действием одиночных импульсов, сформированных на выходах генераторов одиночных импульсов 32.1 и 32,2. Значение записывав мой информации определяется режимами, выпoлняe lыми устройством контроля цифровых блоков.

Одновременно с записью информации на триггеры 39 и 38 под деист- вием одиночного импульса, сформированного на выходе блока 32.2, происходит обнуление содержимого счетчиков 33.1-33.7, установка в ноль триггера 37 и установка в единицу триггера 34 фазы. На тумблерном наборе 40 набирается код, определяемый количеством тактов синхронизации, а на тумблерном наборе 41 код, определяемый числом тов проверки цифрового блока (фиг.12).

При нажатии кнопки Пуск (фиг.12 и 13) блок 12 упрЕШления функционирует в соответствии с вре- менной диаграммой, приведенной на фиг.15, где показано функционирование основных его узлов. Так, на ди5

О

5 0

0

0 5 0

5

грамме 1 (фиг.15) показана временная диаграмма на выходе генератора тактовых импульсов, на диаграмме 2 - выходная последовательность триггера 37. Последовательности с выходов триггера 37, задержанные на линиях задержки (фиг.12 и диаграммы 3 и 4 на фиг.15), через элементы И и ИЛИ поступают на седьмой и восьмой выходы блока управления (диаграммы 5 и 6 на фиг.15), После отработки синхронизирующих последовательностей на элементе И 43 формируется одиночный импульс, который переключает состояние триггера фазы (диаграммы 8 и 9 на фиг.15). Кроме того, импульс, сформированный на выходе элемента И 43 (диаграмма 7 на фиг.15), поступает на входы счетчиков 33.4-33.7, содержимое которых увеличивается на единицу.

Таким образом, блок 12 управления формирует временные диаграммы импульсов, подаваемь.х на управляющие входы остальных блоков устройства контроля цифровых блоков.

Коммутатор 13 состоит из п элементов 2-ЗИ-ИЛИ, к управляющим входам которых подключены выходы 12.7 и 12.8 блока 12 управления, к информационным входам которых подключены выходы 5.1, 6.1 и 8.1 соответственно блоков 5-6,8. Выходы элементов 2-ЗИ-Ш1И подключены к входам блока 14 (фиг.9).

Блок 14 состоит из п двухвходовых сумматоров по модулю два, на входы которых подключены выходы блоков 13 и 7 фиг.10).

Элементы блоков 13 и 14 в совокупности позволяют выполнить пораз- рядные логические операции И, ИЛИ, НЕ, М2.

Блок 15 состоит из п трехразрядных регистров, на которые записывается код, определяющий номер устройства, подключенного к блоку 8, выход КОТОРОГО подключается на выход блока 8. На входы блока 15 подключаются выходы блоков 5 и 12, а именно: 5.1, 12.11 и t2.12. Выход блока 15 подключается на вход блока 15.1 (фиг.11). Блок 17 состоит из I двухвхоДо- вых сумматоров по модулю, выходы которых подключены к адресным входам блока 7, к входам которых подключен выход 12.9 блока 12 управления и выходы элементов И блока 18, коли7

чество которых также равняется I |(фиг.4ь

Блок 17 в совокупности с блоком 18 служит для формирования на адресных входах блока 7 или последовательно изменяющихся адресов, или псевдослучайный адресов.

Устройство работагт следующим образом.

Перед началом проверки с помощью блока 12 управления и блока 10 ввода производится загрузка тестов и другой информации. Первоначально обнуляется содержимое элементов памяти блоков 1,5,6 и 7, для чего на выходе генератора одиночных импульсов 32,6 формируется одиночный импульс, который устанавливает элементы памяти трехразрядного регистра (15) в единичное состояние. В этом случае на выход мультиплексоро блока 8 будет подключен вход 16 кода логического уровня нуля устройства. Последовательно изменяя адреса блоков 5-7 сверхоперативной памяти путем формирования одиночных импульсов генератором одиночных импульсов 32.1 во все ячейки памяти указанных блоков записывается логический ноль. Подобным образом обнуляется содержимое регистров блока 1 с использованием генераторов одиночных импульсов 32.7 и 32.8.

Далее в блоки 5-7 i-ro разряда записывается исходная информация, которая определяется режимом i-ro разряда устройства, для чего в блок 15 записывается нулевой код, которы обеспечивает передачу через мультиплексор информации, формируемой на выходе блока 10 ввода. В процессе загрузки исходной информации на выходе триггера 38 блока 12 формируется единичный уровень, обеспечивают щий запись информации в блоки 5-7.

Управляющая информация на триггеры 21 я 22 и начальный код на триггер 20 i-ro разряда записывается с выхода блока 5, откуда также фор- мил уется информация, подаваемая на входы блока 15.

После занесения необходимой информации в блоки 1,5,6,7 и 15 выполняется процедура установки элементов памяти блока 12 в состояния, определяемые режимом проверки цифрового блока, для чего триггер 39 устанавливается в нулевое- состоя609618

ние. Подобным образом в заданные состояния устанавливаются остальные триггеры блока 12, а также счетчики и тумблерные наборы. 5 После завершения ввода начинается сам процесс высокочастотной проверки цифрового блока 2. Для этого, 1гутем переключения тумблера Пуск в нулевое положение начинают форми- 10 роваться управляющие импульсы на выходе блока 12.

Функционирование устройства контроля цифровых блоков в каждом такте осуществляется за две фазы (фиг.15). 13 в течение первой фазы отрабатываются синхронизирующие сигналы, во вто- рой фазе на выходной регистр блока 1 записывается очередной тестовый набор.

20 Рассмотрим функционирование i-ro разряда устройства в зависимости от последовательности, которую необходимо формировать на его выходе .

Генерирование произвольной после- 25 довательности синхронизирую1цих сигналов.

Синхросигналы, необходимые для функционирования проверяемого блока, подаются на него в первой фазе. Для 30 организации генерирования синхросигналов по i-му разряду предвари- тельно необходимо записать логический ноль на триггер маски 21 и логическую единицу на триггер 22. Кроме 5 того, в блоки 5 и 6 i-ro разряда записывается информация с синхронизирующей последовательности импульсов. Рассмотрим процедуру формирования подобной информации для случая 0 синхронизирующей последовательности, приведенной на ф«г.16а. На фиг.166 приведена последовательность импульсов, формируемых на первом выходе блока 12, под действием которых на 5 выходном триггере 20 должна быть

сформирована синхронизирующая последовательность, представленная на фиг.16а. Под действием управляющих сигналов, сформированных на седьмом 0. и восьмом выходах блока 12 управления, на D-вход триггера 20 через блоки 13 и 14 подключаются выходы блоков 6 и 5. Причем при подаче нечетных импульсов последовательности 1бб ко 5 входу триггера 20 подключается блок 6, а по четным импульсам - блок 5. Адреса ячеек памяти блоков 6 и 5 изменяются, соответственно, по четным

912

и нечетным импульсам (фиг. 12 к 15). Таким образом, по первому импульсу (фиг. 166) на выходной триггер 20 записывается содержимое нулевой ячейки блока 6,которое согласно фиг.16а должно равняться нулю. Под действием первого импульса увеличивается адрес блока 5 на единицу. По приходу второго импульса на триггер 20 записывается содержимое первой ячейки памяти блока 5 и изменяется на единицу адрес блока 6. Согласно фиг.16а в первой ячейке памяти блока 5 должна быть записана единица, а в первой ячейке блока 6 - ноль. Далее, рассуждая подобным образом, видно, что во вторые ячейки памяти блоков 5 и 6 должны быть записаны, соответственно ноль и единица.

Для записи информации с синхронизирующей последовательности (фиг.16а) эта последовательность кодируется нулями и единицами (фиг.16в). На основании фиг.1бв формируется информация, которая записывается в i-e разряды блоков 5 и 6. Так, в бло|: 5, начиная с первой ячейки памяти, записьшается код 1000 (фиг.16д), а в блок 6, начиная с, нулевой ячейки - код 001 (фиг.16г). Процесс подачи записанной информации на выходной триггер 20 i-ro разряда обеспечивается тем,.что на выходе i-ro мультиплексора блока 8 формируется нулевой уровень за счет коммутации на его выход генер атора логической единицы. При этом трехразрядный регистр i-ro разряда предварительно устанавливается в состояние 11К Кроме того, на вход блока 19 подается нулевой уровень с выхода триггера 39 блока 12, что обеспечивает чтение нулевой ячейки блока

7i-ro разряда, где хранится значение логического нуля. Таким образом, с выхода i-ro разряда блоков

8и 7 на входы блоков 13 и 14 подаются логические нули.

Эквивалентная схема устройства контроля Ц11фровых блоков (i-ro разряда) с учетом предварительно записанной информации, обеспечивающей режим формирования синхронизирующей последовательности, будет иметь вид изображенный на фиг.17. На вход D - триггера 20 (фиг.17) поступает пб- следовательность синхронизирующих импульсов с первого выхода блока 12

6

10

На входы блока 13 поступают последовательности, сформированные на седьмом и восьмом выходах блока 12 управления.

Генерирование псевдослучайной последовательности Yj с вероятностью P(Y.I) 0,5 по i-му каналу генератора.

Изменения информации на триггере 20 блока 1 выходных регистров будет происходить во второй фазе, для чего на триггер 21 маски предварительно записывается единица, на триггер 22 также записывается единичное значение. В блоки 5 и 6 сверхоперативной памяти записывается единица во все ячейки памяти. На i-м разряде устройства в блоке 15 записывается код 001, под действием которого на выход i-ro мультиплексора блока 8 подключается i-й выход генератора псевдослучайных тестов, по которому формируется равновероятная двоичная цифра X. с вероятностью р()0,5. Содержимое блока 7 сверхоперативной памяти может состоять из всех единиц или из всех нулей.

Эквивалентная схема устройства контроля цифровых блоков (i-ro разряда) с учетом предварительно записанной информации будет иметь вид,-представленный на фиг.18. На i-й элемент 2-ЗИ-Ш1И блока 13 подаются значения логических единиц с блоков 5 и 6, а также единичные уровни, сформированные на седьмом и восьмом выходах блока 12 управления. Указанный режим формирования псевдослучайной последовательности по i-му каналу обеспечивается и при подаче на седьмой и восьмой выходы блока 12 управления комбинаций 01 и 10.Анализ схемы, приведенной на фиг. 18, показывает, что У- X и следовательно: Р(У. 1)0,5, так как р()0,5.

Формирование псевдослучайной последовательности Y,- с вероятностью P(Y.1)0,5 может быть реализовано и другим способом, для чего в блоки сверхоперативной памяти 5 и 6 записьшается нулевая информация, а в блок 7 записывается половина нулей и половина единиц. Содержимое i-ro регистра блока 15 безразлично. Триггер 39 блока 12 управления устанавливается в единичное состояние. При этом на адресные входы блока 7 (фиг.4) подается поразрядная сумма по модулю два псевдослучайного 1-разрядного кода с очередным адресом, сформированным в блоке 12 на девятом выходе. Таким образом, с очередным адресом блока 7 в каждом такте проверки цифрового блока будет появляться псевдослучайный код с равной вероятностью, принимающий одно из возможных

значений.Поэтому на выходе блока 7 будет равновероятно формироваться значение нуля и единицы,что в итоге обеспечит псевдослучайную последователь- ность YJ с вероятностью p(Y. 1)0,5

Генерирование псевдослучайной по следовательности Y/ с вероятностью p() 0,5 по i-му разряду устройства контроля цифровых бло1:ов.

Для организации генерирования псевдослучайной последовательности Yj с вероятностью p(Yj 1) 0,5 предварительно необходимо записать единицу на триггер 21 маски и на триггер 22.

Для случая, когда p()0,5 на входах .i-ro элемента 2-ЗИ-Ш1И блока 13 формируются переменные, обеспечивающие нулевой уровень на его выход и для случая P(Yy 1)0,5 обеспечивается единичное значение на его выходе. В i-e СОЗУ блока 7 записывается такое количество единиц, кото которое обеспечивает требуемую вероятность.

Для случая P()0,5 заданная вероятность представляется выражением ,

P(Y,,b-,

где g - емкость СОЗУ блока 7; b - количество единиц, записанных в i-e СОЗУ блока 7. Для случая P()0,5 заданная вероятность представляется выражением , P(Y.1)1-|.

Обеспечение вероятности P(Yy 1) больше или меньше 0,5 возможно и в случае формирования логического нуля на выходе i-ro элемента 2-ЗИ- ИЛИ, однако при этом необходимо записывать в СОЗУ i-ro разряда блока 7 большее количество единиц при P()0,5.

Генерирование псевдослучайной последовательности Y. с вероятностью P()0,5 по i-му разряду

20

5

26096112 .

устройства и с вероятностью p(f) переключения выходного сигнала на противоположный.

Для организации работы устройст- 5 ва для контроля цифровых блоков

в данном режиме предварительно необходимо записать единицу на триггеры 21 и 22, а на i-й регистр блока 15 записать код 110, под действием которого единичный выход триггера 20 i-ro разряда подключается через элемент И 23 блока 1 и i-й мультиплексор блока 8 на вход i-ro сумматора по модулю два блока 14.

Экивалентная схема устройства для контроля цифровых блоков (i-ro разряда) с учетом предварительно записанной информации будет иметь вид, представленный на фиг.19.

Значения содержимого триггеров

10

ТС1 и ТС2, 35 и 36, а также информация, хранимая в СОЗУ1 и СОЗУ2 блоков 5 и 6 должна обеспечивать прохождение сигналов с выхода i-ro мультиплексора блока 8 на вход i-ro сумматора по модулю два(14), через i-й элемент 2-ЗИ-ИЛИ блока 13.

Кроме того, с выхода триггера 39 блока 12 управления на входы двух- входовых элементов И 18 поступает разрешающий потенциал, который обеспечивает формирование псевдослучайных адресов с выходов блока 9. Причем адреса равновероятно могут принимать любое из возможных значений.

Для задания требуемой вероятности p(f) переключения выходного сигнала на противоположный в СОЗУ 3 блока 7 (i-й разряд) записывается b единиц, количество которых определяется из соотношения p(f)b/g. При в каждом такте содержимое триггера 20 i-ro разряда устройства меняется на противоположное, при содержимое триггера 20 неизменно, при состояние триггера 20 меняется на противоположное с вероятностью О,5 и так далее.

Дискретность изменения вероятности p(f) и вероятности P(Y,- 1) в режимах 4 и 3 определяется емкостью СОЗУ и равняется 1/g. Так, для дискретность изменения вероятности равняется 1/256.

Генерирование псевдоциклических кодов.

Псевдоциклические коды это такие коды, в которых в каждый конкретный момент времени возможно изменение только одного двоичного разряда кода (7). Таким образом, сосед- ние коды псевдоциклических кодов отличаются только в одном разряде,

Для организации работы устройства для контроля цифровых блоков в указанном режиме необходимо первона- чально определить номера разрядов, на выходах которых должен формироваться псевдоциклический код.

Предположим, псевдоциклический код необходимо генерировать по вы- ходам i-ro, i+l, i+2,... , разрядов, хотя в общем случае формирование псевдоциклического кода может осуществляться и по выходам разрядов с произвольными номерами.

На триггеры 21 маски i-ro,i+1-ro и L+C-1-го разряда устройства записывается единица, на триггеры 22 указанных разрядов также записывается единичное значение. Подобно как и в режиме 4 на выходах элементов 2-ЗИ-ЙЛИ обеспечивается единичный уровень. того, на регистры блока 15 записывается код 110, под действием которого обеспечивается связь выхода триггера 20 со входами сумматоров по модулю два (14) i-ro, i-i-1-го,... и i+C-1-го разрядов. В СОЗУ 3-7 указанных разрядов циклически записывается следующая информация:

i i+l i+2 ... i+C-1

О

1 О

О

о о о

с-1 о о

Таким образом, только на выходе одного СОЗУ 3 из С будет считываться единичное значение при любом значени адреса„

Адрес СОЗУ 3 блока 7 в данном ре- жиме формируется как псевдослучайное равномерно распределенное число,, подобно как и в режиме 4.

Кроме рассмотренных режимов устройство для контроля цифровых блоков позволяет формировать последовательности гипа бегущий ноль и бегущая единица, формировать сигналы типа

5

5 20

. 5 0 5

0

15

О

SS

const О и const 1, генерировать в случайнбй последовательности только несколько определенных кодов, запрещать появление на выходах устройства определенного множества кодов и т.д.

Все перечисленные режимы работы устройства могут реализовываться одновременно, но для разных его разрядов.

Увеличение частоты проверки цифровых блоков осуществляется за счет увеличения частоты формирования синхронизирующих импульсов.

Формула изобретения

1 Устройство для контроля цифровых блоков, содержащее блок выходных регистров, эталонный цифровой блок, блок сравнения, первый, второй и третий блоки памяти, блок мультиплексоров, генератор тестов, блок ввода, блок вьшода и блок управления, причем первая группа информационных выходов блока выходных регистров подключена к группе входов контролируемого цифрового блока и к первой группе информационных входов блока сравнения, вторая группа информационных выходов блока выходных регистров подключена к группе входов эталонного цифрового блока и второй группе информащюнных входов блока сравнения, первая и вторая грушш разрешагачих входов которого соединены соответственно с третьей и четвертой группами информационных выходов блока выходных 1 егистров, первый выход блока управления соединен с входом синхронизации блока выходных регистров, второй выход блока управления соединен с входами запись-чтение блоков памяти, третий выход блока управления соединен с входом синхронизации генератора тестов, выходы первого блока памяти соединены с первой группой информационных входов блока выходных регистров, четвертый и пятый выходы блока управления соединены соответственно с адресными входами первого и второго блоков памяти, выходы блока ввода соединены с первой щиной разрядов группы информационных входов блока мультиплексоров, вторая и третья группы разрядов группы информационных входов блока мультиплексоров соединены соответственно

с первой группой информационных выходов генератора тестов и с выходом блока сравнения соответственно, отличающееся тем, что, с целью повышения быстродействия устройства и увеличения глубины конроля за счет изменения в широких пределах вероятност1 ых и временных параметров генерируемых им последовательностей, устройство содержит ко1Ф1утатор, первый и второй блоки сумматоров по модулю два, блок трехразрядных регистров и группу элементов И, причем группа выходов коммутатора соединена с первой группой информационных входов первого блока сумматоров по модулю два, выходы которого соединены с второй группой информационных входов блока выходных регистров, разрешающий вход кото рого соединен с шестым выходом блока управления, седьмой и восьмой выходы которого соединены соответственно с первым и вторьм управляющими входами коммутатора, , вторая и третья группы информационных вхо- дов которого соединены соответственно с выходами первого и второго блоков памяти и блока мультиплексоров, выходы которого соединены также с информационными входами второго и третьего блоков памяти и информационными входами блока вывода, выходы третьего блока памяти соединены с второй группой информационных вхо- дов первого блока сумматоров по модулю два, выходы которого соединены с информационными входами первого блока памяти, выходы первого, второго и третьего блоков памяти соедине- ны соответственно с четвертой, пятой и шестой группами разрядов группы информационных входов блока мультиплексоров, седьмая и восьмая группы разрядов группы информационных вхо- дов блока мультиплексоров соединены соответственно с первой группой информационных выходов блока выходных регистров и с разрядами входа кода устройства, вторая группа ин- формационных выходов генератора тестов соединена с первыми входами элементов И группы, выходы которых соединены с группой информационных Bxo.t дов второго блока сумматоров по мо- дулю два, выходы которого соединены с адресньми входами третьего блока памяти, девятый выход блока управле

кия соединен с входом второго блокд сумматоров по модулю два, десятый выход блока управления соединен с вторыми входами элементов И группы, выходы первого блока памяти соединены с информационными входами блока трехразрядных регистров, одиннадца- тьй выход блока управления соединен с входами синхронизации регистров блока трехразрядных регистров, двенадцатый выход блока управления соединен с установочными входами регистров блока трехразрядных регистров, выходы разрядов регистров блока трехразрядных регистров соединены с группой управляющих входов блока мультиплексоров, вход пуска блока управления является входом пуска устройства.

2. Устройство по П.1, отличающееся тем, что блок управления содержит генератор тактовых импульсов, восемь генераторов одиночных импульсов, семь счетчиков, триггер фазы, два триггера, Т-триггер, триггер чтения-записи, триггер режима адресации, четыре элемента задержки, коммутатор, две группы элементов ИЛИ, две группы элементов И, семь элементов И, четьфе элемента ИЛИ, два блока элементов сложения по модулю два, причем вход пуска генератора тактовых импульсов является входом пуска блока управления, выход генератора тактовых импульсов соединен со счетньм входом Т-триг- гера, прямой и инверсный выходы которого соединены соответственно с входами первого и второго элементов задержки, выход первого элемента задержки соединен с первым входом первого элемента И и с первым информационньм входом коммутатора, выход второго элемента задержки соединен с первым входом второго элемента И и вторым информационным входом коммутатора, выходы первого и второго элементов И соединены со счетными входами соответственно первого и второго счетчиков, выходы разрядов первого и второго счетчиков соединены с первыми входами элементов ИЛИ соответственно первой и второй групп, выходы элементов И первой и второй групп образуют соответственно четвертый и пятый выходы блока управления, выход генератора тактовых импульсов соединен со счетным входом третьего

элемента И и вторыми входами первого и второго элементов И, выход третьего элемента И соединен с первым входом первого элемента ИЛИ, выход кото- рого соединен с входом третьего элемента задержки, R-входом Т триггера и входами сброса первого и второго счетчиков, выход третьего элемента задержки соединен с S-входом триггера фаэы, прямой выход которого соединен с управляющим входом коммутатора с третьими входами первого и второго элементов И и является шестым выходом блока управления, инверсный выход триггера фазы соединен с вторым входом третьего элемента И, первыми входами четвертого и пятого элементов И и с первыми входами элементов И первой и второй групп, выходы элементов И первой группы соединены с вторь ми входами элементов ИЛИ первой группы, выходы элементов И второй группы соединены с вторыми входами элементов ИЛИ второй группы, выходы четвертого и пятого элементов И соединены соответственно с третьим и четвертым информационными входами коммутатора, первый и второй выходы которого являются соответственно седьмым и восьмым в ыходами блока управления, выход четвертого элемента задержки соединен с входом сброса третьего счетчика, инверсные выходы разрядов которого соединены с первой группой входов первого блока элементов сложения по модулю два, вторая группа входов которого через переключатели подключена к шинам нулевого и единичного потенвдалов, груп- па выходов первого блока элементов сложения по модулю два соединена с входами шестого элемента И, выход которого соединен с входе четвертого элемента задержки, R-входом триг- гера фазы, первыми входами второго, третьего и четвертого элементов ИЛИ, выходы .которых соединены сЪ счетными входами соответственно четвертого, пятого и шестого счетчиков, выходы разрядов четвертого и пятого счетчиков соединены с вторыми входами элементов И соответственно перв ой и второй групп, выход шестого счетчика является девятым выходом блока управ

5

0

5

5 0 5 0 55

0

5

ления, выход шестого элемента И соединен со счетным входом седьмого счетчика и является третьим выходом блока управления, инверсные выходы разрядов седьмого счетчика соединены с первой группой входов второго блока элементов сложения по модулю два, вторая группа входов которого через переключатели подключена к шинам нулевого и единичного потенциалов, группа выходов второго блока элементов сложения по модулю два соединена с входами седьмого элемента И, выход которого соединен с входом разрешения генератора тактовых импульсов, выход первого генератора одиночных импульсов соединен с входами синхронизации первого и второго триггеров и с вторыми входами второго, третьего и четвертого элементов ИЛИ, информационные входы первого и второго триггеров через переключатели подключены к шинам Нулевого и единичного потенциалов, выхода первого и второго триггеров соединены с вторыми входами соответственно четвертого и пятого элементов И, выход второго генератора одиночных импульсов соединен с входами син- хр онизации триггера режима адресации и триггера чтения-записи, входами сброса четвертого, пятого, шестого и седьмого счетчиков и вторым входом первого элемента ИЛИ, информационные входы триггера режима адресации и триггера записи-чтения через переключатели подключены к шинам нулевого и единичного потенциалов, выходы триггера режима адресации и триггера записи-чтения являются соответственно десятым и вторым выходами блока управления, выходы третьего, четвертого и пятого генераторов одиночных импульсов являются соответственно первым, вторым и третьим разрядами одиннадцатого рыхода блока управления, выход шестого генератора . одиночных импульсов является двенадцатым выходом блока управления, выходы генератора тактовых импульсов, седьмого и восьмого генераторов одиночных импульсов являются соответственно первым, вторым и третьим разрядами первого выхода блока управления .

6.1

5,1

Фиг.5

1 9.2

JO

Pai.ff

иг.6

Йгг.7

W

М2 Щ

ЛW./

1±

иг.Ю

Фиг.9

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| Генератор псевдослучайных чисел | 1989 |

|

SU1691839A2 |

| Генератор псевдослучайных чисел | 1990 |

|

SU1805465A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для формирования тестовых воздействий | 1984 |

|

SU1168953A1 |

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1990 |

|

SU1725222A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Устройство для контроля многовыходных цифровых узлов | 1988 |

|

SU1566353A1 |

Изобретение относится к вычислительной технике, в частности к устройствам автоматического контроля Ц1 ровьк объектов, и может быть использовано для высокочастотной функциональной проверки узлов ЭВМ, построенных с использованием микросхем большой степени интеграции. Цель изобретения - повышение быстродействия устройства и увеличение глубины контроля за счет изменения в широких пределах вероятностных и временных параметров генерируемых им последовательностей. Устройство содержит блок выходных регистров, проверяемый и эталонный цифровые блоки, блок сравнения, три блока памяти блок мультиплексоров, генераторов тестов, блок ввода, блок вывода, блок управления, коммутатор, два блока сумматоров по модулю два, блок трехразрядных регистров, группу элементов И. 1 з.п. ф-лы, 19 ил. сл го Од о со О)

Фиг.П

Фи9. 12

JycK «Pue.fJ

«Pue. /

M.1S

ГТП n П n r

ri m r

1 r r-i

. /7

W

«J

г-JoTl-iLr 20

г-ЦГ

.11

W r|fejsi :

ФОЗО

«Pue. IB

t

Редактор Т. Парфенова

Составитель Д. Ванюхин

Техред Л.Олейник Корректор С. Черни, у

Заказ 5233/50Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д . 4/5

f

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

фиг.13

| Яковлев В.В.,Федоров Р.Ф | |||

| Стохастические вычислительнью машины | |||

| Л.: Машиностроение, 1974 | |||

| Устройство контроля микропроцессорных блоков | 1982 |

|

SU1042023A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-30—Публикация

1985-04-12—Подача