JггlJlш JlJ JгпJ JlШlJl

Jl rTTTiriJnrT TlJirbJlITl

5

к

00 оо

ел

оо ;о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тактовой синхронизации канала цифровой магнитной записи-воспроизведения | 1987 |

|

SU1432598A2 |

| Устройство для воспроизведения цифровых сигналов с магнитного носителя | 1990 |

|

SU1737508A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Способ магнитной записи цифровой информации | 1981 |

|

SU974406A1 |

| Устройство для тактовой синхронизации канала цифровой магнитной записи-воспроизведения | 1985 |

|

SU1278943A1 |

| Устройство для записи цифровой информации | 1989 |

|

SU1607008A1 |

| Устройство записи-воспроизведения цифровой информации на магнитном носителе | 1981 |

|

SU980138A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1988 |

|

SU1606996A1 |

| Способ магнитной записи сигналов цифровой информации | 1984 |

|

SU1206835A1 |

| Устройство для записи-воспроизведения цифровой информации на магнитном носителе | 1984 |

|

SU1191936A1 |

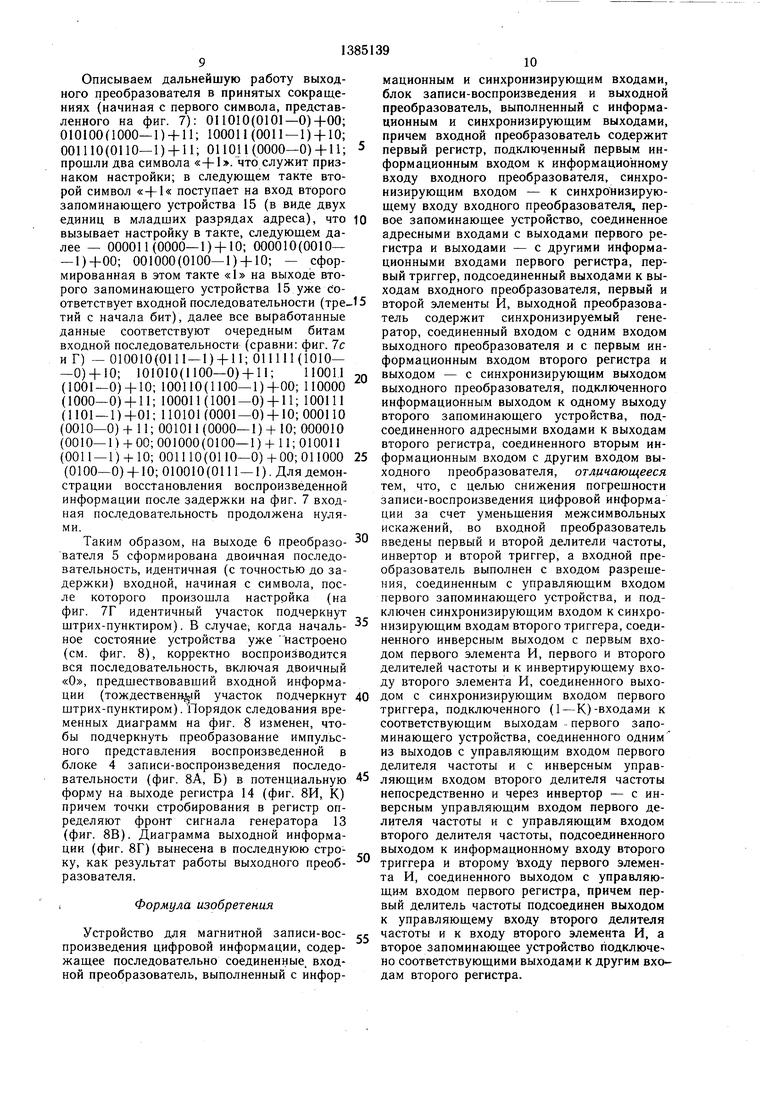

Изобретение относится к накоплению информации. Цель изобретения - снижение погрешности записи-воспроизведения цифровой информации за счет уменьшения межсимвольных искажений. На выходе преобразователя сформирована двоичная последовательность, идентичная входной, начиная с символа, после которого произошла настройка. В случае, когда начальное состояние устройства уже настроено, корректно воспроизводится вся последовательность, включая двоичный нуль, предшествовавший входной информации (тождественный участок подчеркнут штрих-пунктиром. Порядок следования временных диаграмм изменен, чтобы подчеркнуть преобразование импульсного представления воспроизведенной в блоке записи-воспроизведения последовательности (А и Б) в потенциальную форму на выходе регистра (И, К). Точки строби- рования в регистр определяют фронт сигнала генератора. Диаграмма Г - результат работы выходного преобразователя. 8 ил., 1 табл. § (Л

.

Изобретение относится к накоплению информации, а именно к устройствам для магнитной записи-воспроизведения цифровой информации.

Целью изобретения является снижение погрешности записи-воспроизведения цифровой информации за счет уменьшения меж- символьНых искажений.

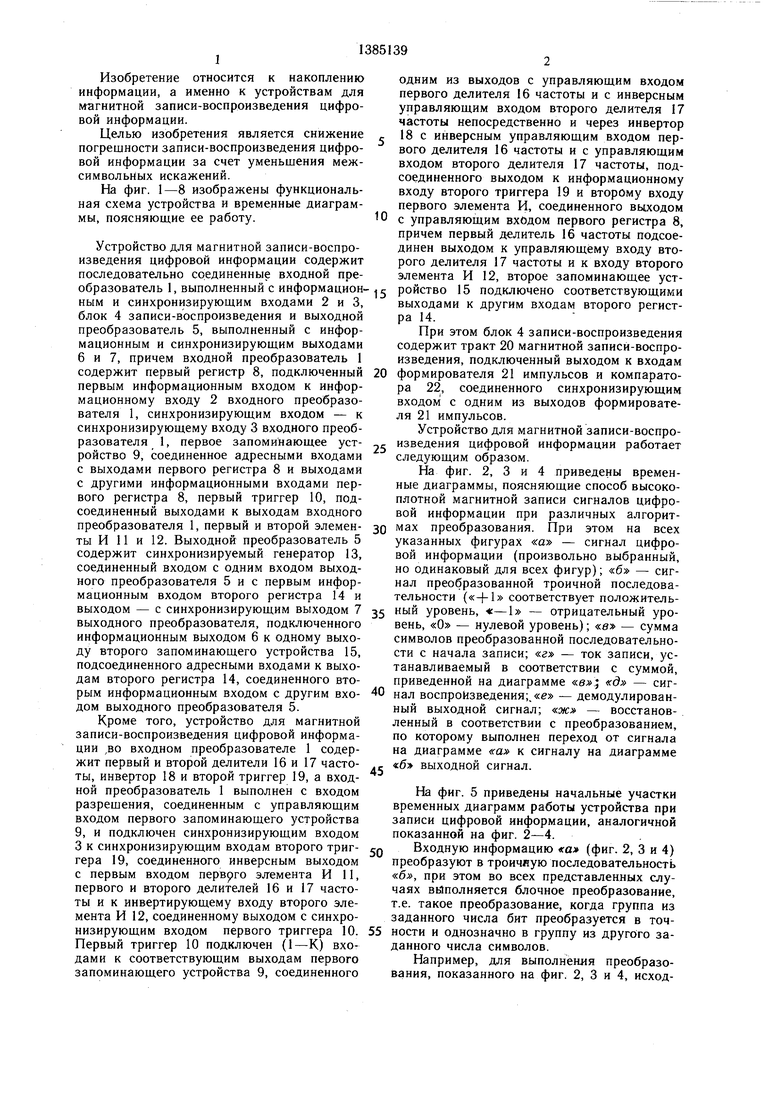

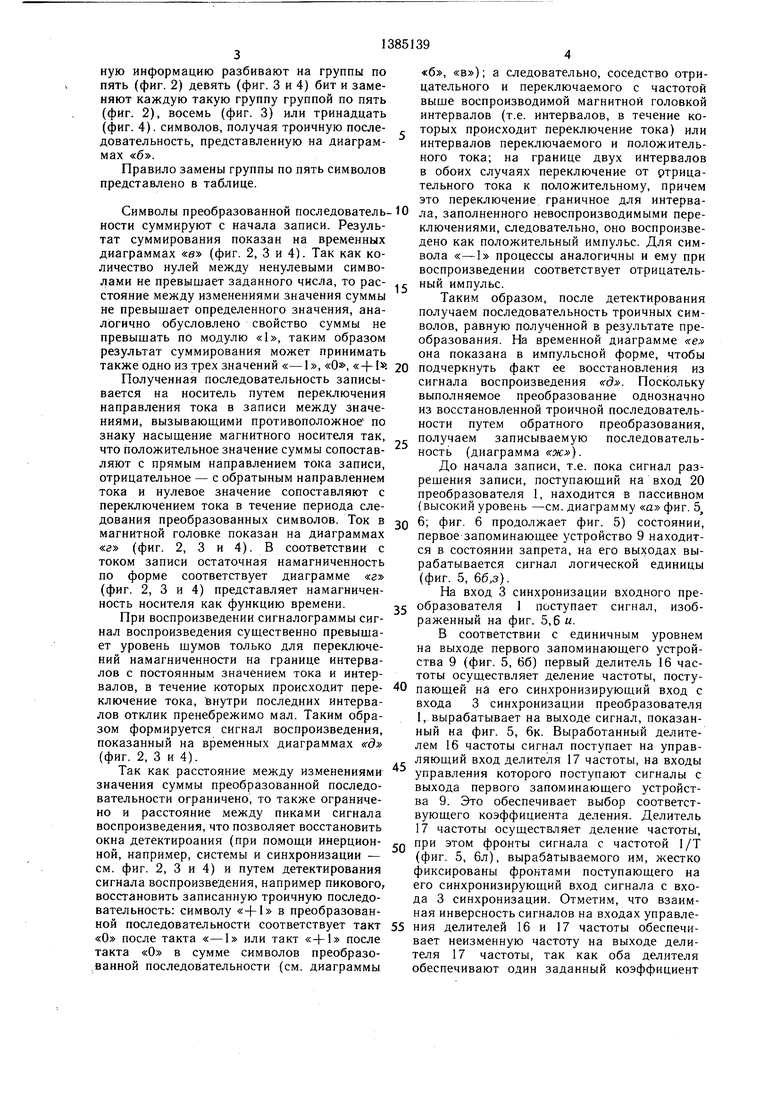

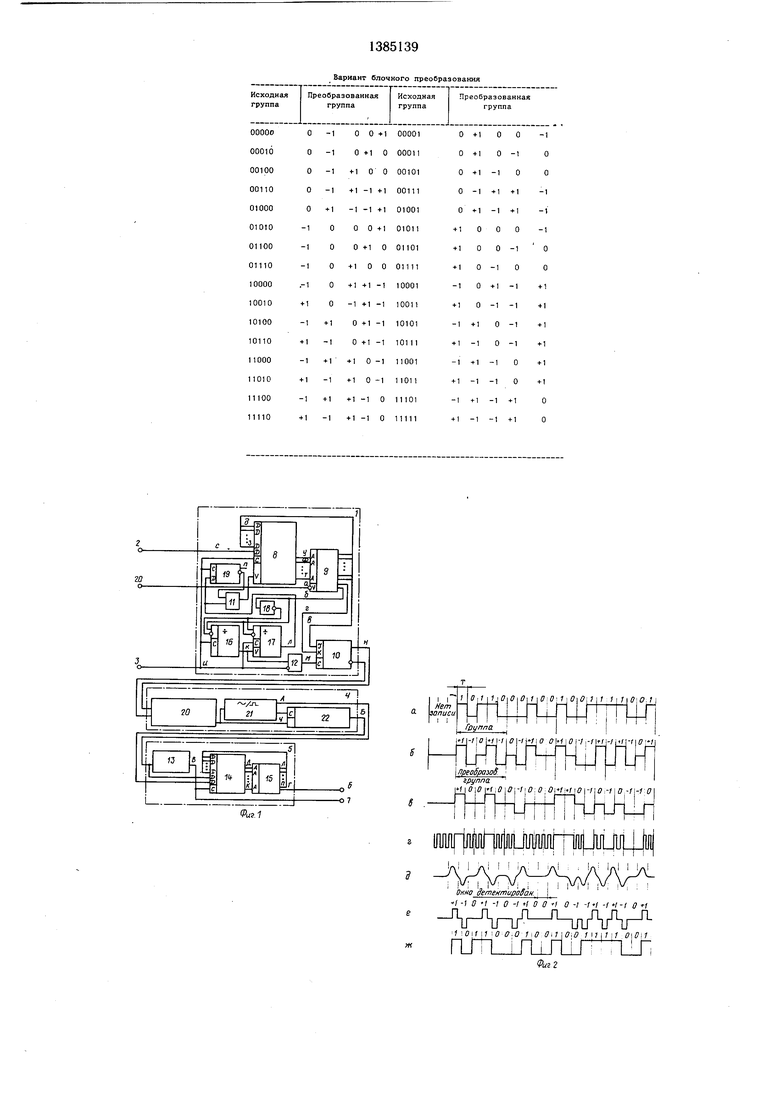

На фиг. 1-8 изображены функциональная схема устройства и временные диаграммы, поясняющие ее работу.

Устройство для магнитной записи-воспроизведения цифровой информации содержит последовательно соединенные входной преобразователь 1, выполненный с информационным и синхронизирующим входами 2 и 3, блок 4 записи-воспроизведения и выходной преобразователь 5, выполненный с информационным и синхронизирующим выходами 6 и 7, причем входной преобразователь 1 содержит первый регистр 8, подключенный первым информационным входом к информационному входу 2 входного преобразователя 1, синхронизирующим входом - к синхронизирующему входу 3 входного преобразователя 1, первое запоминающее устройство 9, соединенное адресными входами с выходами первого регистра 8 и выходами с другими информационными входами первого регистра 8, первый триггер 10, подсоединенный выходами к выходам входного преобразователя 1, первый и второй элементы И 11 и 12. Выходной преобразователь 5 содержит синхронизируемый генератор 13, соединенный входом с одним входом выходного преобразователя бис первым информационным входом второго регистра 14 и выходом - с синхронизирующим выходом 7 выходного преобразователя, подключенного информационным выходом 6 к одному выходу второго запоминающего устройства 15, подсоединенного адресными входами к выходам второго регистра 14, соединенного вторым информационным входом с другим входом выходного преобразователя 5.

Кроме того, устройство для магнитной записи-воспроизведения цифровой информации ,во входном преобразователе 1 содержит первый и второй делители 16 и 17 частоты, инвертор 18 и второй триггер 19, а входной преобразователь 1 выполнен с входом разрешения, соединенным с управляющим входом первого запоминающего устройства 9, и подключен синхронизирующим входом 3 к синхронизирующим входам второго триггера 19, соединенного инверсным выходом с первым входом первсрго элемента И 11, первого и второго делителей 16 и 17 частоты и к инвертирующему входу второго элемента И 12, соединенному выходом с синхронизирующим входом первого триггера 10. Первый триггер 10 подключен (1-К) входами к соответствующим выходам первого запоминающего устройства 9, соединенного

одним из выходов с управляющим входом первого делителя 16 частоты и с инверсным управляющим входом второго делителя 17 частоты непосредственно и через инвертор

с 18 с инверсным управляющим входом первого делителя 16 частоты и с управляющим входом второго делителя 17 частоты, подсоединенного выходом к информационному входу второго триггера 19 и второму входу первого элемента И, соединенного выходом

0 с управляющим входом первого регистра 8, причем первый делитель 16 частоты подсоединен выходом к управляющему входу второго делителя 17 частоты и к входу второго элемента И 12, второе запоминающее уст5 ройство 15 подключено соответствующими выходами к другим входам второго регистра 14.

При этом блок 4 записи-воспроизведения содержит тракт 20 магнитной записи-воспроизведения, подключенный выходом к входам

0 формирователя 21 импульсов и компаратора 22, соединенного синхронизирующим входом с одним из выходов формирователя 21 импульсов.

Устройство для магнитной записи-воспро5 изведения цифровой информации работает следующим образом.

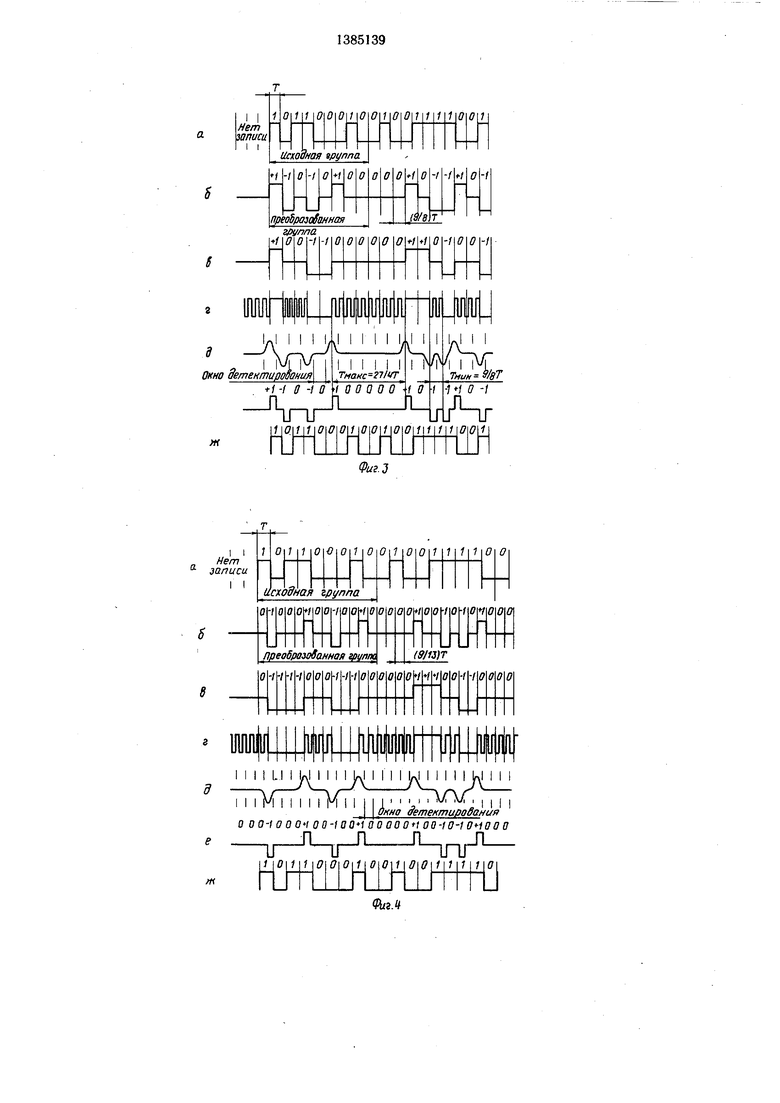

На фиг. 2, 3 и 4 приведены временные диаграммы, поясняющие способ высокоплотной магнитной записи сигналов цифровой информации при различных алгорит0 мах преобразования. При этом на всех указанных фигурах «а - сигнал цифровой информации (произвольно выбранный, но одинаковый для всех фигур); «б - сигнал преобразованной троичной последовательности («+1 соответствует положитель5 ный уровень, -1 - отрицательный уровень, «О - нулевой уровень); «0 - сумма символов преобразованной последовательности с начала записи; «г - ток записи, устанавливаемый в соответствии с суммой, приведенной на диаграмме «д - сиг0 нал воспроизведения;, «е - демодулирован- ный выходной сигнал; «ж - восстановленный в соответствии с преобразованием, по которому выполнен переход от сигнала на диаграмме «а к сигналу на диаграмме

Е «б выходной сигнал.

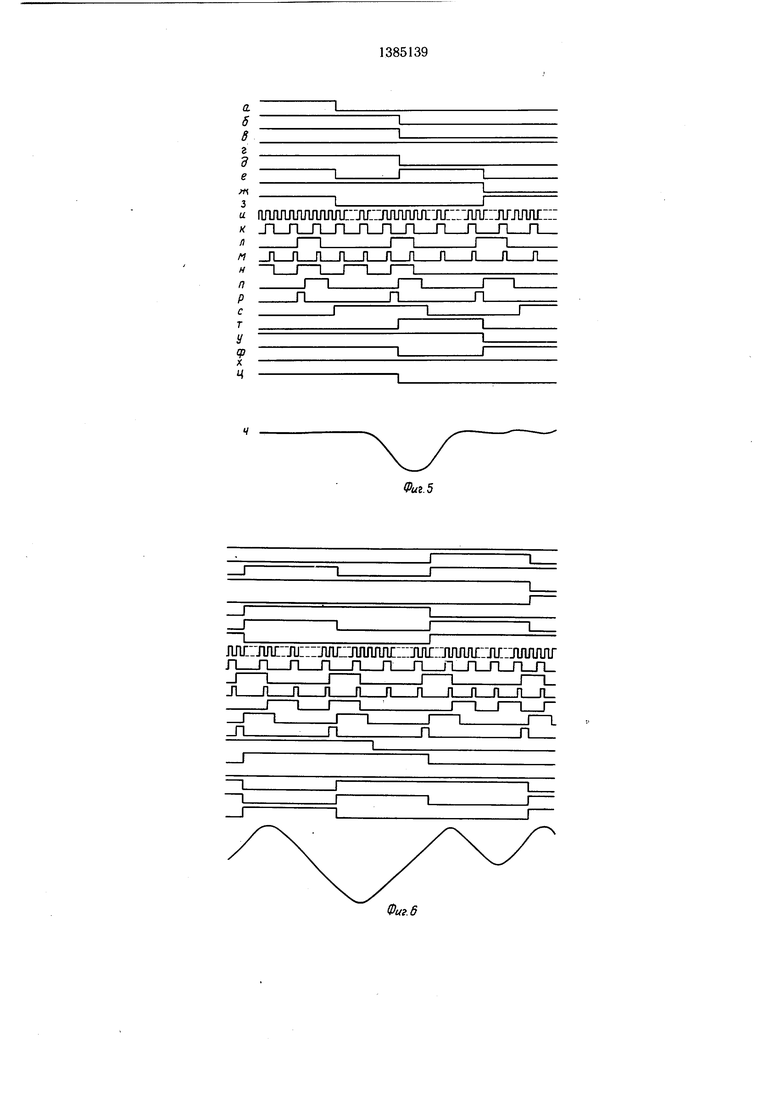

На фиг. 5 приведены начальные участки временных диаграмм работы устройства при записи цифровой информации, аналогичной показанной на фиг. .

0 Входную информацию «га (фиг. 2, 3 и 4) преобразуют в троичяую последовательность «б, при этом во всех представленных случаях выполняется блочное преобразование, т.е. такое преобразование, когда группа из заданного числа бит преобразуется в точ5 ности и однозначно в группу из другого заданного числа символов.

Например, для выполнения преобразования, показанного на фиг. 2, 3 и 4, исходную информацию разбивают на группы по пять (фиг. 2) девять (фиг. 3 и 4) бит и заменяют каждую такую группу группой по пять (фиг. 2), восемь (фиг. 3) или тринадцать (фиг. 4). символов, получая троичную последовательность, представленную на диаграммах «б.

Правило замены группы по пять символов представлено в таблице.

ключениями, следовательно, оно воспроизведено как положительный импульс. Для символа «-1 процессы аналогичны и ему при воспроизведении соответствует отрицательвается на носитель путем переключения направления тока в записи между значениями, вызывающими противоположное по знаку насыщение магнитного носителя так, что положительное значение суммы сопоставляют с прямым направлением тока записи, отрицательное - с обратыным направлением тока и нулевое значение сопоставляют с переключением тока в течение периода сле25

«б, «в); а следовательно, соседство отрицательного и переключаемого с частотой выше воспроизводимой магнитной головкой интервалов (т.е. интервалов, в течение которых происходит переключение тока) или интервалов переключаемого и положительного тока; на границе двух интервалов в обоих случаях переключение от ртрица- тельного тока к положительному, причем это переключение граничное для интерваСимволы преобразованной последователь-10 ла, заполненного невоспроизводимыми пере- ности суммируют с начала записи. Результат суммирования показан на временных диаграммах «в (фиг. 2, 3 и 4). Так как количество нулей между ненулевыми символами не превышает заданного числа, то рас- . ный импульс. стояние между изменениями значения суммыТаким образом, после детектирования

не превышает определенного значения, ана- получаем последовательность троичных сим- логично обусловлено свойство суммы не волов, равную полученной в результате пре- превышать по модулю «1, таким образом образования. На временной диаграмме «е результат суммирования может принимать она показана в импульсной форме, чтобы такжеодноизтрехзначений«-1, «О, «+1 20 подчеркнуть факт ее восстановления из Полученная последовательность записы- сигнала воспроизведения «д. Поскольку

выполняемое преобразование однозначно из восстановленной троичной последовательности путем обратного преобразования, получаем записываемую последовательность (диаграмма «ж.

До начала записи, т.е. пока сигнал разрешения записи, поступающий на вход 20 преобразователя 1, находится в пассивном (высокий уровень -см. диаграмму «а фиг. 5,

дования преобразованных символов. Ток в о 6; фиг. 6 продолжает фиг. 5) состоянии магнитной головке показан на диаграммах первое запоминающее устройство 9 находит- «г (фиг. 2, 3 и 4). В соответствии с ся в состоянии запрета, на его выходах вы- током записи остаточная намагниченность рабатывается сигнал логической единицы по форме соответствует диаграмме «г (фиг. 5, 6б,з).

(фиг. 2, 3 и 4) представляет намагничен-На вход 3 синхронизации входного пре35 образователя 1 поступает сигнал, изображенный на фиг. 5,6 ч.

В соответствии с единичным уровнем на выходе первого запоминающего устройства 9 (фиг. 5, 66) первый делитель 16 частоты осуществляет деление частоты, постувалов, в течение которых происходит пере- 40 пающей на его синхронизирующий вход с ключение тока, внутри последних интерва- входа 3 синхронизации преобразователя лов отклик пренебрежимо мал. Таким образом формируется сигнал воспроизведения, показанный на временных диаграммах «д

ОИТ у.А С ,Ei ri ил. Vi/1 ri i in /i i/ -lUVJi l IJi, II Cl D.

Так как расстояние между изменениями управления которого поступают сигналы с

значения суммы преобразованной последо-выхода первого запоминающего устройствательности ограничено, то также ограниче-ва 9. Это обеспечивает выбор соответстно и расстояние между пиками сигналавующего коэффициента деления. Делитель

воспроизведения, что позволяет восстановить17 частоты осуществляет деление частоты,

окна детектироания (при помощи инерцион- - при этом фронты сигнала с частотой 1/ Г

ной, например, системы и синхронизации -(фиг. 5, 6л), вырабатываемого им, жестко

см. фиг. 2, 3 и 4) и путем детектированияфиксированы фронтами поступающего на

сигнала воспроизведения, например пикового,его синхронизирующий вход сигнала с вховосстановить записанную троичную последо-да 3 синхронизации. Отметим, что взаимвательность: символу «-f 1 в преобразован-ная инверсность сигналов на входах управленой последовательности соответствует такт55 ния делителей 16 и 17 частоты обеспечи«0 после такта «-1 или такт «+1 послевает неизменную частоту на выходе делитакта «0 в сумме символов преобразо-теля 17 частоты, так как оба делителя

.ванной последов;ательности (см. диаграммыобеспечивают один заданный коэффициент

ность носителя как функцию времени.

При воспроизведении сигналограммы сигнал воспроизведения существенно превышает уровень щумов только для переключений намагниченности на границе интервалов с постоянным значением тока и интер1, вырабатывает на выходе сигнал, показанный на фиг. 5, 6к. Выработанный делителем 16 частоты сигнал поступает на управляющий вход делителя 17 частоты, на входы

ключениями, следовательно, оно воспроизведено как положительный импульс. Для символа «-1 процессы аналогичны и ему при воспроизведении соответствует отрицатель ла, заполненного невоспроизводимыми пере- ный импульс. Таким образом, после детектирования

25

В соответствии с единичным уровнем на выходе первого запоминающего устройства 9 (фиг. 5, 66) первый делитель 16 частоты осуществляет деление частоты, поступающей на его синхронизирующий вход с входа 3 синхронизации преобразователя

,Ei ri ил. Vi/1 ri i in /i i/ -lUVJi l IJi, II Cl D.

управления которого поступают сигналы с

1, вырабатывает на выходе сигнал, показанный на фиг. 5, 6к. Выработанный делителем 16 частоты сигнал поступает на управляющий вход делителя 17 частоты, на входы

деления при единичном потенциале на прямом входе управления и другой заданный коэффициент деления при нулевом потенциале. Таким образом, от сигнала управления на выходе постоянного запоминающепоследовательности. В исходное состояние схема приводится благодаря выработке на выходах первого запоминающего устройства 9 логических единиц в отсутствие разрешающего потенциала на входе разрешения

го устройства 9 (фиг. 5,6,6) зависит тольно 5 первого запоминающего устройства 9 (т.е.

частота сигнала на выходе делителя 16 частоты.

Выработанный делителем 16 частоты сигнал поступает также на вход второго элена входе разрешения входного преобразователя 1).

До начала записи логические единицы с выходов первого запоминающего устроймента И 12 и в активном состоянии разре- ю ства 9 и информацию с входа 2 запоми- шает селекцию (выборку) импульса син- нает регистр 8. При поступлении на вход

20 разрешения активного уровня сигнала первое запоминающее устройство 9 начинает преобразование: первый адрес, по которому происходит выбор информации, сос- 15 тавляют заполненные в регистре 8 логические единицы, вырабатывавшиеся ранее на информационных выходах первого запоминающего устройства, и нуль, присутствовавший на информационном входе 2 до на- (фиг. 5, бв,г). До начала записи (сигнал .,д чала записи.

разрешения записи - в пассивном состоя-При завершении очередного периода дении; фиг. 5, 6а) на входах 1К-триггера 10 уровень логической единицы, следовательно, по каждому сигналу на входе его синхронизации триггер 10 переключается в противоположное состояние.25 Сигнал с выхода делителя 17 частоты

хронизации, поступающего с входа 3 синхронизации, при этом выработанный на выходе элемента И 12 сигнал инверсен относительно синхронизирующего сигнала (фиг. 5, 6м).

Этот сигнал (фиг. 5, 6м) поступает на вход синхронизации 1К-триггера 10, на I- и К-входы которого поступают сигналы с выходов первого запоминающего устройства 9

ления частоты делитель 17 частоты формирует сигнал согласно фиг. 5, 6л, чем разрешает выработку сигнала на выходе элемента И 11 (фиг. 5, 6р), который в свою очередь разрешает загрузку регистра 8. Регистр -8 загружает значение, выработанное на выходе первого запоминающего устройства 9 (фиг. 5, 6д-з) и первый бит информации, подлежащий записи, с входа 2. В результате (фиг. 5, 6т-д) на вход первого

ления частоты делитель 17 частоты формирует сигнал согласно фиг. 5, 6л, чем разрешает выработку сигнала на выходе элемента И 11 (фиг. 5, 6р), который в свою очередь разрешает загрузку регистра 8. Регистр -8 загружает значение, выработанное на выходе первого запоминающего устройства 9 (фиг. 5, 6д-з) и первый бит информации, подлежащий записи, с входа 2. В результате (фиг. 5, 6т-д) на вход первого

поступает на информационный вход второго триггера 19, который вырабатывает сигнал той же частоты (фиг. 5, 6п). На вход его синхронизации поступает сигнал с входа 3,. .

т.е. сигнал, используемый делителем 17 30 запоминающего устройства 9 поступает но- частоты для фиксации фронтов вырабаты-вый адрес. На входах регистра 8 возникает

ваемого им сигнала. Благодаря фиксации фронта сигнала, вырабатываемого делителем 17 частоты, расстояние между передним фронтом сигнала на входе и выходе триггера 19 син.хронизировано.

Элемент И 11 обеспечивает выделение

новая информация (фиг. 5, 6д-э), на входы триггера 10 поступают сигналы: «О (фиг. 5, 6в) на вход I и «1 (фиг. 5, 6г) - на вход К, поэтому очередной импульс на входе его син35 хронизации (фиг. 5, 6м) сбрасывает триггер 10 (фиг. 5, 6н). Сохранение информации на входах триггера 10 обеспечивает неизменность его состояния при появлении очередных импульсов на входе его синхрониназванного такта частоты синхронизации (фиг. 4, 6р), формирует сигнал, возникающий после появления сигнала на выходе делителя 17 частоты.

40 зации. Сигнал управления делителями частоты, равный «О (фиг. 5, 66) изменяет коэффициенты деления делителей 16 и 17 частоты, что однако не изменяет частоты загрузки регистра 8.

Представленные на фиг. 5 и 6 диаграмВыработанный элементом И 11 сигнал поступает на вход разрешения регистра 8, в результате чего происходит занесение в регистр 8 информации по фронту сигнала

синхронизации с входа 3, поступающего 45 мь1 позволяют увидеть результат управления на соответствующий вход регистра 8. Таким коэффициентом деления делителей частоты образом, период обновления информации в 7 и 8: на фиг. 6 показаны оба возмож- регистре 8, поступающей с информацион- ных вариата сопряжения такта, в течение ного входа 2, составляет период частоты которого происходит переключение тока за- (фиг. 5, 6с - на входе регистра, т - на писи (от триггера 10) с частотой выще выходе), что обеспечивает преобразование 50 воспроизводимой магнитной головкой трак- каждого бита входной информации, по- та 20 записи-воспроизведения. Таким образом, в среднем из названных тактов имеет место переключение триггера 10 с частотой, выше воспроизводимой, а в тактах до и после названного - одинаковый постоянный уровень. Для возвращения по окончании такта с переключениями в исходное положение триггер 10 внутри такого такта переклюступающеи с тем же периодом, и происходит запоминание сигналов, вырабатываемых первым запоминающим устройством 9 (фиг. 5 6у-ц на выходе регистра 8).

Таким образом происходит как преобразование входной последовательности в троичную, так и суммирование полученной

последовательности. В исходное состояние схема приводится благодаря выработке на выходах первого запоминающего устройства 9 логических единиц в отсутствие разрешающего потенциала на входе разрешения

первого запоминающего устройства 9 (т.е.

на входе разрешения входного преобразователя 1).

До начала записи логические единицы с выходов первого запоминающего устрой ства 9 и информацию с входа 2 запоми- нает регистр 8. При поступлении на вход

При завершении очередного периода деления частоты делитель 17 частоты формирует сигнал согласно фиг. 5, 6л, чем разрешает выработку сигнала на выходе элемента И 11 (фиг. 5, 6р), который в свою очередь разрешает загрузку регистра 8. Регистр -8 загружает значение, выработанное на выходе первого запоминающего устройства 9 (фиг. 5, 6д-з) и первый бит информации, подлежащий записи, с входа 2. В результате (фиг. 5, 6т-д) на вход первого

. .

запоминающего устройства 9 поступает но- вый адрес. На входах регистра 8 возникает

0 запоминающего устройства 9 поступает но- вый адрес. На входах регистра 8 возникает

новая информация (фиг. 5, 6д-э), на входы триггера 10 поступают сигналы: «О (фиг. 5, 6в) на вход I и «1 (фиг. 5, 6г) - на вход К, поэтому очередной импульс на входе его син5 хронизации (фиг. 5, 6м) сбрасывает триггер 10 (фиг. 5, 6н). Сохранение информации на входах триггера 10 обеспечивает неизменность его состояния при появлении очередных импульсов на входе его синхрони0 зации. Сигнал управления делителями частоты, равный «О (фиг. 5, 66) изменяет коэффициенты деления делителей 16 и 17 частоты, что однако не изменяет частоты загрузки регистра 8.

Представленные на фиг. 5 и 6 диаграм5 мь1 позволяют увидеть результат управления коэффициентом деления делителей частоты 7 и 8: на фиг. 6 показаны оба возмож- ных вариата сопряжения такта, в течение которого происходит переключение тока за- писи (от триггера 10) с частотой выще 0 воспроизводимой магнитной головкой трак- та 20 записи-воспроизведения. Таким образом, в среднем из названных тактов имеет место переключение триггера 10 с частотой, выше воспроизводимой, а в тактах до и после названного - одинаковый постоянный уровень. Для возвращения по окончании такта с переключениями в исходное положение триггер 10 внутри такого такта переключают нечетное число раз, а затем в начале следующего такта возвращают в исходное состояние. Требуемую частоту переключений достигают путем выбора коэффициента деления первого делителя 16 (фиг. 6к).

В случае, когда такты, окружающие такт с переключениями, имеют противоположные значения тока записи, т.е. различные состояния триггера 10 (пример такого случая также приведен на фиг. 6), в такте с переключениями производят четное число переключений, для чего устанавливают другой коэффициент деления первого делителя 16 частоты, чему соответствует единичный сигнал на выходе первого запоминающего устройства 9 (фиг. 66).

В результате управления коэффициентом деления достигается синхронизация переключений триггера 10 на границе различающихся тактов, благодаря этому после прохождения через тракт 20 записи-воспроизведения сигнал (фиг. 5, 6ч) имеет расстояние между -пиками (экстремумами, существенно превышающими уровень шумов), кратное Т (с точностью до межсимвольной интерференции).

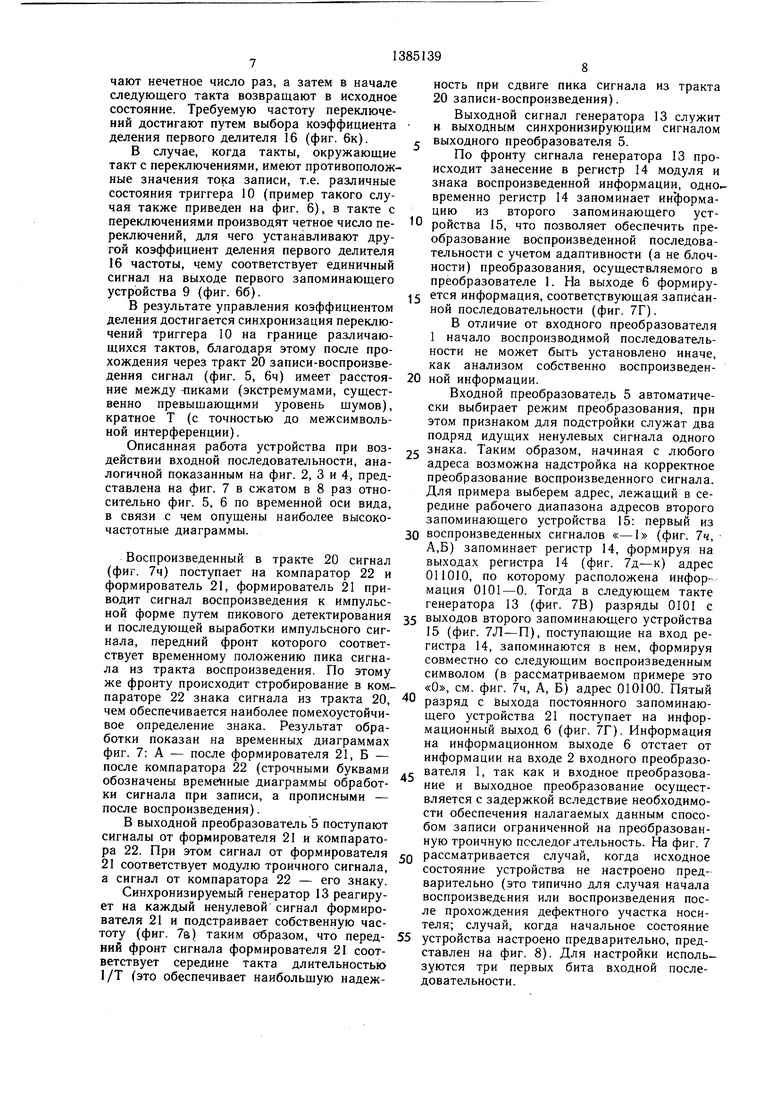

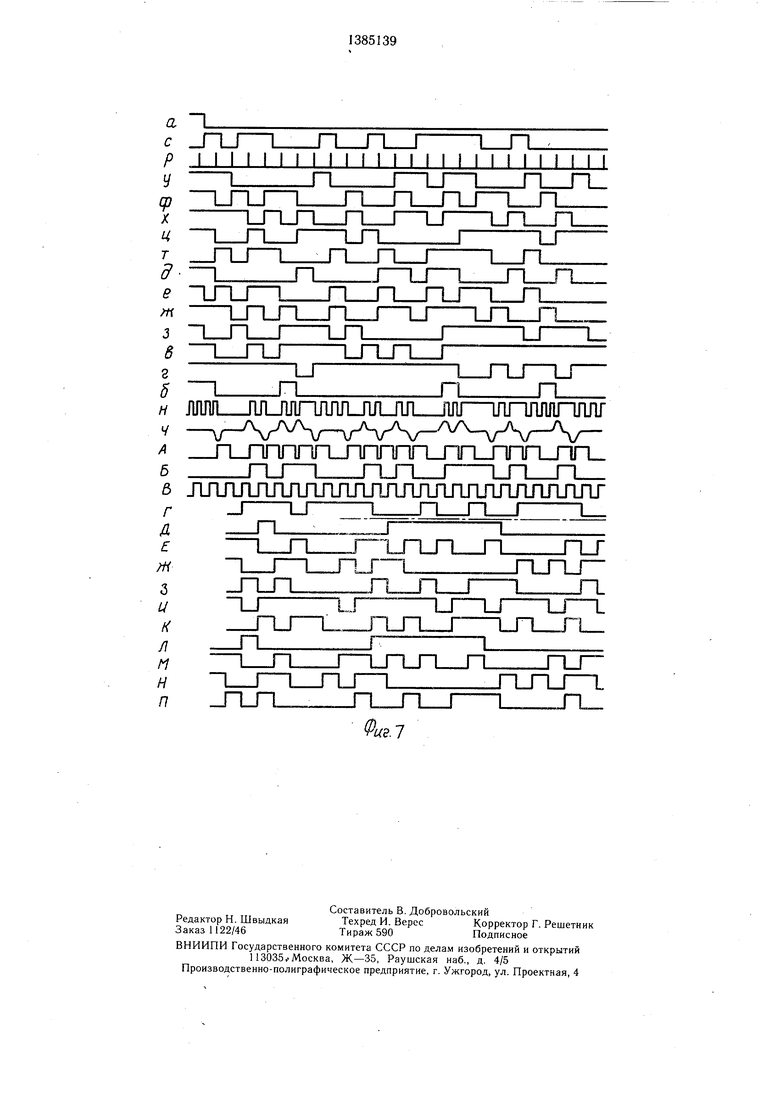

Описанная работа устройства при воздействии входной последовательности, аналогичной показанным на фиг. 2, 3 и 4, представлена на фиг. 7 в сжатом в 8 раз относительно фиг. 5, 6 по временной оси вида, в связи чем опущены наиболее высокочастотные диаграммы.

Воспроизведенный в тракте 20 сигнал (фиг. 7ч) поступает на компаратор 22 и формирователь 21, формирователь 21 приводит сигнал воспроизведения к импульсной форме путем пикового детектирования и последующей выработки импульсного сигнала, передний фронт которого соответствует временному положению пика сигнала из тракта воспроизведения. По этому же фронту происходит стробирование в компараторе 22 знака сигнала из тракта 20, чем обеспечивается наиболее помехоустойчивое определение знака. Результат обработки показан на временных диаграммах фиг. 7: А - после формирователя 21, Б - после компаратора 22 (строчными буквами обозначены временные диаграммы обработки сигнала при записи, а прописными - после воспроизведения).

В выходной преобразователь 5 поступают сигналы от формирователя 21 и компаратора 22. При этом сигнал от формирователя 21 соответствует модулю троичного сигнала, а сигнал от компаратора 22 - его знаку.

Синхронизируемый генератор 13 реагирует на каждый ненулевой сигнал формирователя 21 и подстраивает собственную частоту (фиг. 7в) таким образом, что передний фронт сигнала формирователя 21 соответствует середине такта длительностью 1/Т (это обеспечивает наибольшую надежность при сдвиге пика сигнала из тракта 20 записи-воспроизведения).

Выходной сигнал генератора 13 служит и выходным синхронизирующим сигналом 2 выходного преобразователя 5.

По фронту сигнала генератора 13 происходит занесение в регистр 14 модуля и знака воспроизведенной информации, одновременно регистр 14 запоминает информацию из второго запоминающего уст 0 ройства 15, что позволяет обеспечить преобразование воспроизведенной последовательности с учетом адаптивности (а не блоч- ности) преобразования, осуществляемого в преобразователе 1. На выходе 6 формиру 5 ется информация, соответствующая записанной последовательности (фиг. 7Г).

В отличие от входного преобразователя 1 начало воспроизводимой последовательности не может быть установлено иначе, как анализом собственно воспронзведен0 ной информации.

Входной преобразователь 5 автоматически выбирает режим преобразования, при этом признаком для подстройки служат два подряд идущих ненулевых сигнала одного

5 знака. Таким образом, начиная с любого адреса возможна надстройка на корректное преобразование воспроизведенного сигнала. Для примера выберем адрес, лежащий в середине рабочего диапазона адресов второго запоминающего устройства 15: первый из

0 воспроизведенных сигналов «-1 (фиг. 7ч, А,Б) запоминает регистр 14, формируя на выходах регистра 14 (фиг. 7д-к) адрес 011010, по которому расположена инфор- мация 0101-0. Тогда в следующем такте генератора 13 (фиг. 7В) разряды 0101 с

5 выходов второго запоминающего устройства 15 (фиг. 7Л-П), поступающие на вход регистра 14, запоминаются в нем, формируя совместно со следующим воспроизведенным символом (в рассматриваемом примере это «О, см. фиг. 7ч, А, Б) адрес 010100. Пятый

0 разряд с выхода постоянного запоминающего устройства 21 поступает на информационный выход 6 (фиг. 7Г). Информация на информационном выходе 6 отстает от информации на входе 2 входного преобразос вателя 1, так как и входное преобразование и выходное преобразование осуществляется с задержкой вследствие необходимости обеспечения налагаемых данным способом записи ограниченной на преобразованную троичную псследогательность. На фиг. 7

0 рассматривается случай, когда исходное состояние устройства не настроено предварительно (это типично для случая начала воспроизведения или воспроизведения после прохождения дефектного участка носителя; случай, когда начальное состояние 5 устройства настроено предварительно, представлен на фиг. 8). Для настройки используются три первых бита входной последовательности.

Описываем дальнейшую работу выходного преобразователя в прннятых сокращениях (начиная с первого символа, представленного на фиг. 7): 011010(0101-0)+00; 010100(1000-D-f 11; 100011(0011 -1) +10; 001110(0110-1) + 11; 011011(0000-0) + П; прошли два символа что служит признаком настройки; в следующем такте второй символ «-|-1« поступает на вход второго запоминающего устройства 15 (в виде двух единиц в младших разрядах адреса), что вызывает настройку в такте, следующем далее - 000011(0000-1) +10; 000010(0010- -1)+00; 001000(0100-1) + 10; - сформированная в этом такте «1 на выходе второго запоминающего устройства 15 уже Соответствует входной последовательности (третий с начала бит), далее все выработанные данные соответствуют очередным битам входной последовательности (сравни: фиг. 7с и Г) - 010010(0111 -1) + 11; 011111(1010-

-0) + 10; 101010(1100-0) + 11; 110011 (1001-0)4-10; 100110(1100-1)+00; 110000 (1000-0) + 11; 100011(1001-0) + 11; 100111 (1101 -1)+01; 110101(0001-0) +10; 000110 (0010-0) + 11; 001011 (0000-1) + 10; 000010 (0010-П+ 00; 001000(0100-1) + 11; 010011 (ООП -1) + 10; 001110(0110-0)+00;011000 (0100-0) + 10; 010010(0111 -1). Для демонстрации восстановления воспроизведенной информации после задержки на фиг. 7 входная последовательность продолжена нулями.

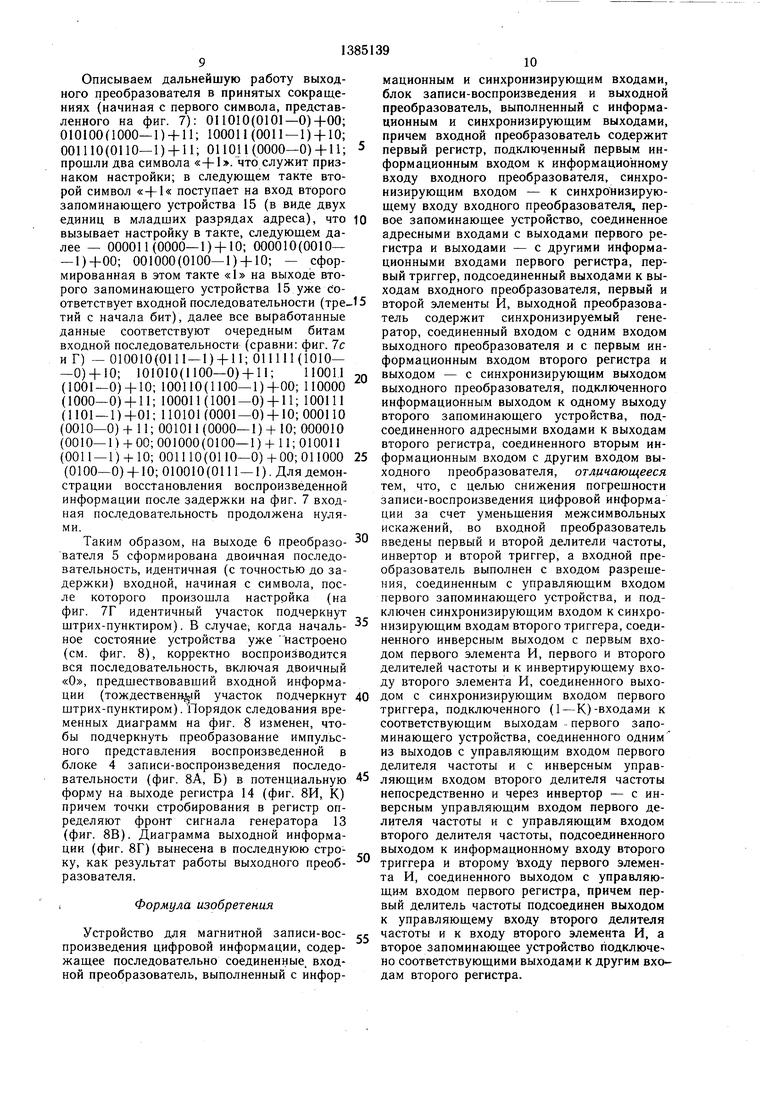

Таким образом, на выходе 6 преобразо- вателя 5 сформирована двоичная последовательность, идентичная (с точностью до задержки) входной, начиная с символа, после которого произошла настррйка (на фиг. 7Г идентичный участок подчеркнут штрих-пунктиром). В случае, когда началь- ное состояние устройства уже настроено (см. фиг. 8), корректно воспроизводится вся последовательность, включая двоичный «О, предшествовавший входной информации (тождественн ш участок подчеркнут штрих-пунктиром). Порядок следования временных диаграмм на фиг. 8 изменен, чтобы подчеркнуть преобразование импульсного представления воспроизведенной в блоке 4 записи-воспроизведения последовательности (фиг. 8А, Б) в потенциальную форму на выходе регистра 14 (фиг. 8И, К) причем точки стробирования в регистр определяют фронт сигнала генератора 13 (фиг. 8В). Диаграмма выходной информации (фиг. 8Г) вынесена в последнуюю строку, как результат работы выходного преоб- разователя.

1Формула изобретения

Устройство для магнитной записи-вое- произведения цифровой информации, содержащее последовательно соединенные, входной преобразователь, выполненный с инфор5

0

5

0 5

мационным и синхронизирующим входами, блок записи-воспроизведения и выходной преобразователь, выполненный с информационным и синхронизирующим выходами, причем входной преобразователь содержит первый регистр, подключенный первым информационным входом к информационному входу входного преобразователя, синхронизирующим входом - к синхронизирующему входу входного преобразователя, первое запоминающее устройство, соединенное адресными входами с выходами первого регистра и выходами - с другими информационными входами первого регистра, первый триггер, подсоединенный выходами к выходам входного преобразователя, первый и второй элементы И, выходной преобразователь содержит синхронизируемый генератор, соединенный входом с одним входом выходного преобразователя и с первым информационным входом второго регистра и выходом - с синхронизирующим выходом выходного преобразователя, подключенного информационным выходом к одному выходу второго запоминающего устройства, подсоединенного адресными входами к выходам второго регистра, соединенного вторым информационным входом с другим входом выходного преобразователя, отличающееся тем, что, с целью снижения погрещности записи-воспроизведения цифровой информации за счет уменьшения межсимвольных искажений, во входной преобразователь введены первый и второй делители частоты, инвертор и второй триггер, а входной преобразователь выполнен с входом разрешения, соединенным с управляющим входом первого запоминающего устройства, и подключен синхронизирующим входом к синхронизирующим входам второго триггера, соединенного инверсным выходо.м с первым входом первого элемента И, первого и второго делителей частоты и к инвертирующему входу второго элемента И, соединенного выходом с синхронизирующим входом первого триггера, подключенного (1-К)-входа.ми к соответствующим выходам - первого запоминающего устройства, соединенного одним из выходов с управляющим входом первого делителя частоты и с инверсным управляющим входом второго делителя частоты непосредственно и через инвертор - с инверсным управляющим входом первого делителя частоты и с управляющим входом второго делителя частоты, подсоединенного выходом к информационному входу второго триггера и второму входу первого элемента И, соединенного выходом с управляющим входом первого регистра, причем первый делитель частоты подсоединен выходом к управляющему входу второго делителя частоты и к входу второго элемента И, а второе запоминающее устройство подключено соответствующими выходами к другим входам второго регистра.

Вариант блочного преобразования

Фиу.1

Окно детенглирдёан. / -J О i -1 О -I / О О -f / -/ / -/ О 1

Wi/ - 4n/VV

1 0 1 .о 0.0 1 0 Oil gig 1 1

П

Фиг 2

011000J00100J111001

исиоаная группа

i -I 1 00

преодрозоУанная

zflynna 1 0 0 -1 -t 0 0 0

Окно

ж

011000100100111ТОО

аскодная группа 01-/ о о owioо -то а

о о о

Преобразованнай группа

О-1 -1 -1-10 О а -1-I-10

UI I I I 1 iVl iVl I I wg детектирования

О 00-t о О 0 100-tao i aooooft oo-to-1 аноо О

лп П1

га

1

0 0 0 -I -ft-l 0-1

jB/aW

00 о -1 1 о -1 о о -i

Ш|1

а

1 о

1 / О -/

{/Чг

т

о о о

(91П}Т

оаооо

О

1шлшшлшиж//ж7лшшпл:ж:: жг.:и1гллш :::

лпг/глл :ж::жг1жллл :::жг::лпш11:ж:жллпг

пппппппппппп

Фиг. б

-

лпллгиишпллл яг1ллши-шплмпллг

JTJnnrTTlJirTTTL nn

JШЛJlJ JUuшлJlЛJгплJlЛJlл

rL

rL

fe

| Способ магнитной записи сигналов цифровой информации | 1984 |

|

SU1177848A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для записи-воспроизведения цифровой информации на магнитном носителе | 1984 |

|

SU1191936A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-03-30—Публикация

1986-10-21—Подача