со оо

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для управления вентильным преобразователем | 1990 |

|

SU1777216A1 |

| Устройство для синхронизации цифровой магнитной записи | 1989 |

|

SU1691888A1 |

| Одноканальное устройство для управления -фазным преобразователем | 1978 |

|

SU775855A1 |

| Устройство для воспроизведения цифровых сигналов с магнитного носителя | 1990 |

|

SU1737508A1 |

| УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ГЕНЕРАТОРА ИМПУЛЬСОВ | 2004 |

|

RU2259630C1 |

| Фазометр | 1987 |

|

SU1479890A1 |

| Способ формирования периодических двуполярных колебаний с заданным фазовым сдвигом и устройство для его реализации | 2016 |

|

RU2625047C1 |

| Устройство поэлементной синхронизации | 1987 |

|

SU1517142A1 |

| Цифровой квазикогерентный фазовый демодулятор | 1980 |

|

SU902301A1 |

| Устройство компенсации сдвига частот | 1985 |

|

SU1316097A2 |

Изобретение относится к электротехнике и может быть использовано для синхронизации систем управления многофазными преобразователями. Целью изобретения является упрощение. Поставленная цель достигается тем, что формируют синхроимпульсы при каждом переходе напряжения сети через нуль, производят деление периода синхронизации на три с помощью генератора с фазовой автоподстройкой частоты, затем деление на три частоты этого генератора, сравнение фазы синхроимпульсов с фазой импульсов, полученных в результате деления частоты, после чего поддерживают процесс деления периода синхроимпульсов на равные промежутки независимым от изменения частоты сети с помощью генератора, выходные импульсы которого распределяют по трем каналам с частотой синхроимпульсов. 1 з.п. ф-лы, 2 ил. 1 сл

оо

00

Изобретение относится к электротехнике и может быть использовано для синхронизации систем управления многофазными преобразователями.

Целью изобретения является упрощение.

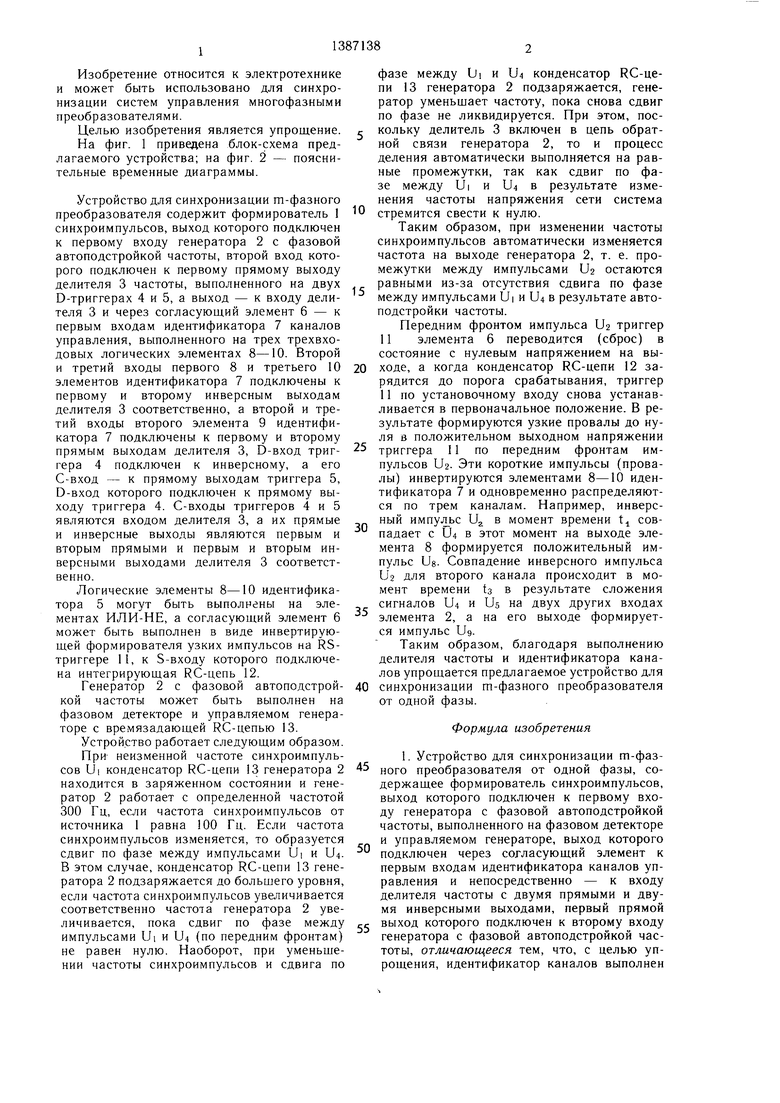

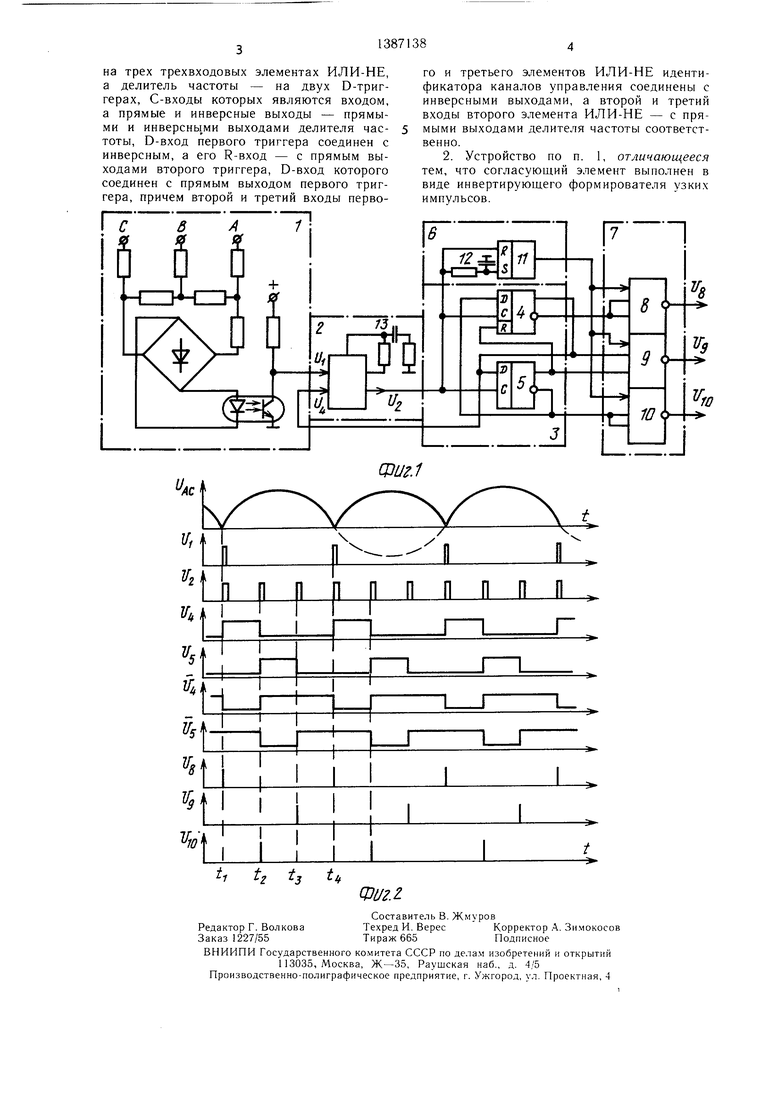

На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг. 2 - пояснительные временные диаграммы.

Устройство для синхронизации ш-фазного преобразователя содержит формирователь 1 синхроимпульсов, выход которого подключен к первому входу генератора 2 с фазовой автоподстройкой частоты, второй вход которого подключен к первому прямому выходу делителя 3 частоты, выполненного на двух D-триггерах 4 и 5, а выход - к входу делителя 3 и через согласующий элемент 6 - к первым входам идентификатора 7 каналов управления, выполненного на трех трехвхо- довых логических элементах 8-10. Второй и третий входы первого 8 и третьего 10 элементов идентификатора 7 подключены к первому и второму инверсным выходам делителя 3 соответственно, а второй и третий входы второго элемента 9 идентификатора 7 подключены к первому и второму прямым выходам делителя 3, D-вход триггера 4 подключен к инверсному, а его С-вход - к прямому выходам триггера 5, D-вход которого подключен к прямому выходу триггера 4. С-входы триггеров 4 и 5 являются входом делителя 3, а их прямые и инверсные выходы являются первым и вторым прямыми и первым и вторым инверсными выходами делителя 3 соответственно.

Логические элементы 8-10 идентификатора 5 могут быть выполнены на элементах ИЛИ-НЕ, а согласующий элемент 6 может быть выполнен в виде инвертирующей формирователя узких импульсов на RS- триггере 11, к S-входу которого подключена интегрирующая RC-цепь 12.

Генератор 2 с фазовой автоподстройкой частоты может быть выполнен на фазовом детекторе и управляемом генераторе с времязадающей RC-цепью 13.

Устройство работает следующим образом. При неизменной частоте синхроимпульсов Ui конденсатор RC-цепи 3 генератора 2 находится в заряженном состоянии и генератор 2 работает с определенной частотой 300 Гц, если частота синхроимпульсов от источника 1 равна 100 Гц. Если частота синхроимпульсов изменяется, то образуется сдвиг по фазе между импульсами Ui и U4. В этом случае, конденсатор RC-цепи 13 генератора 2 подзаряжается до большего уровня, если частота синхроимпульсов увеличивается соответственно частота генератора 2 увеличивается, пока сдвиг по фазе между импульсами Ui и U4 (по передним фронтам) не равен нулю. Наоборот, при уменьще- нии частоты синхроимпульсов и сдвига по

0

5

0

5

0

5

0

5

фазе между Ui и U4 конденсатор RC-цепи 13 генератора 2 подзаряжается, генератор уменьщает частоту, пока снова сдвиг по фазе не ликвидируется. При этом, поскольку делитель 3 включен в цепь обратной связи генератора 2, то и процесс деления автоматически выполняется на равные промежутки, так как сдвиг по фазе между Ui и и в результате изменения частоты напряжения сети система стремится свести к нулю.

Таким образом, при изменении частоты синхроимпульсов автоматически изменяется частота на выходе генератора 2, т. е. промежутки между импульсами Uz остаются равными из-за отсутствия сдвига по фазе между импульсами Ui и U4 в результате автоподстройки частоты.

Передним фронтом импульса U2 триггер 11 элемента 6 переводится (сброс) в состояние с нулевым напряжением на выходе, а когда конденсатор RC-цепи 12 зарядится до порога срабатывания, триггер 11 по установочному входу снова устанавливается в первоначальное положение. В результате формируются узкие провалы до нуля в положительном выходном напряжении триггера 11 по передним фронтам импульсов U2. Эти короткие импульсы (провалы) инвертируются элементами 8-10 идентификатора 7 и одновременно распределяются по трем каналам. Например, инверсный импульс Ug в момент времени t совпадает с LJ4 в этот момент на выходе элемента 8 формируется положительный импульс Us. Совпадение инверсного импульса U2 для второго канала происходит в момент времени ts в результате сложения сигналов U4 и Us на двух других входах элемента 2, а на его выходе формируется импульс Ug.

Таким образом, благодаря выполнению делителя частоты и идентификатора каналов упрощается предлагаемое устройство для синхронизации ш-фазного преобразователя от одной фазы.

Формула изобретения

на трех трехвходовых элементах ИЛИ-НЕ, а делитель частоты - на двух D-триг- герах, С-входы которых являются входом, а прямые и инверсные выходы - прямыми и инверсны ми выходами делителя частоты, D-вход первого триггера соединен с инверсным, а его R-вход - с прямым выходами второго триггера, D-вход которого соединен с прямым выходом первого триггера, причем второй и третий входы первои.

АС

го и третьего элементов ИЛИ-НЕ идентификатора каналов управления соединены с инверсными выходами, а второй и третий входы второго элемента ИЛИ-НЕ - с прямыми выходами делителя частоты соответственно.

F-I

.

Фиг.1

| УСТРОЙСТВО СИНХРОНИЗАЦИИ СИСТЕМЫ УПРАВЛЕНИЯ ВЕНТИЛЯМИ га-ФАЗНОГО ПРЕОБРАЗОВАТЕЛЯ | 1969 |

|

SU425296A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Одноканальное устройство для управления -фазным преобразователем | 1978 |

|

SU775855A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1988-04-07—Публикация

1986-06-09—Подача