Изобретение относится к радиотехнике, может найти применение в высокоточных синхронизирующих устройствах систем связи, передачи дискретной информации и т.п., и является усовер- шенствованием устройства по авт. св. № 843270.

Цель изобретения - повьшение точности компенсации сдвига частот.

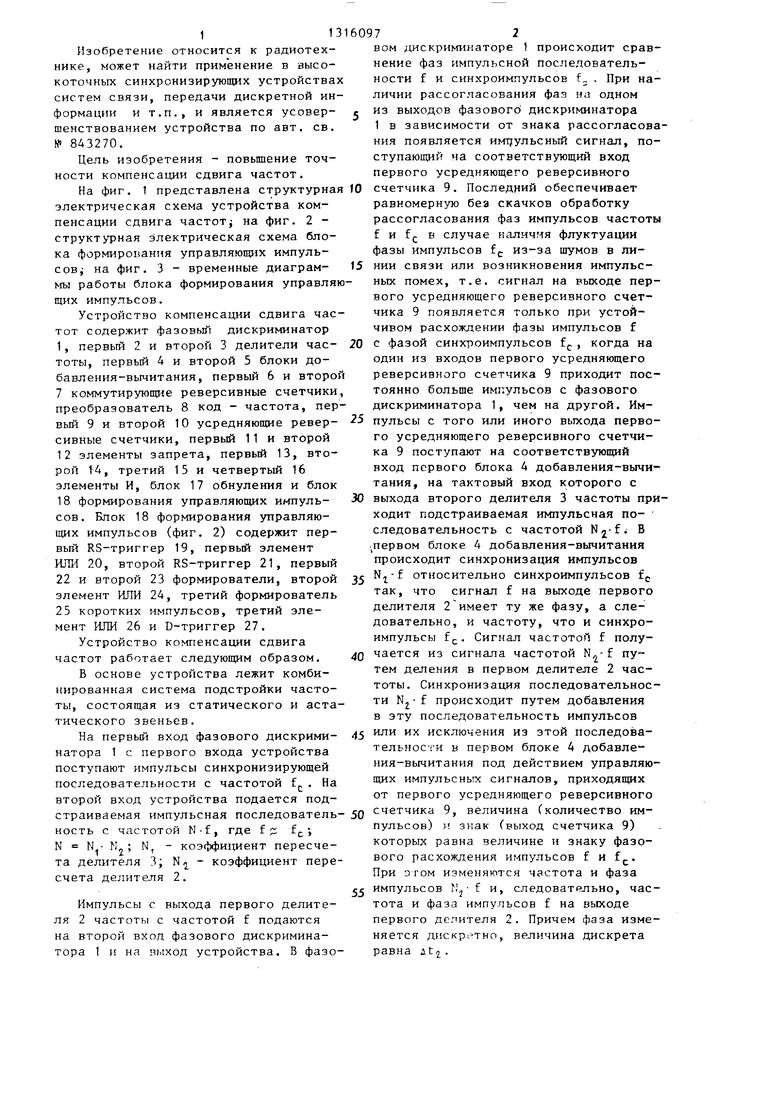

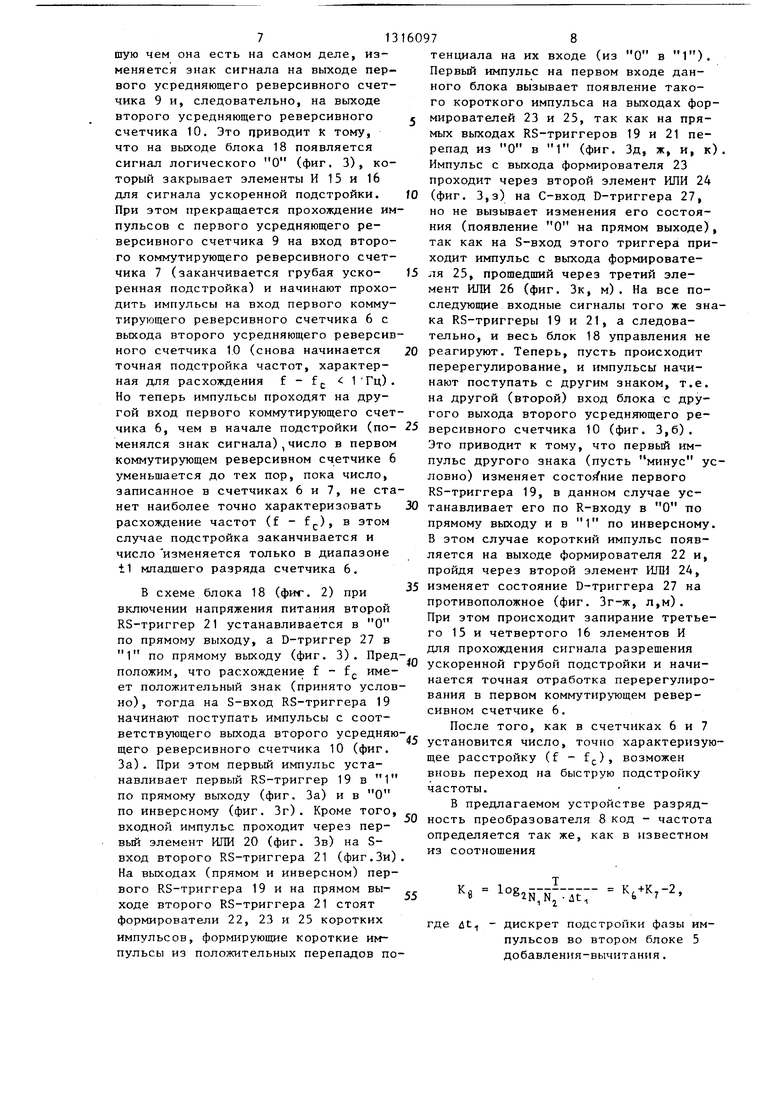

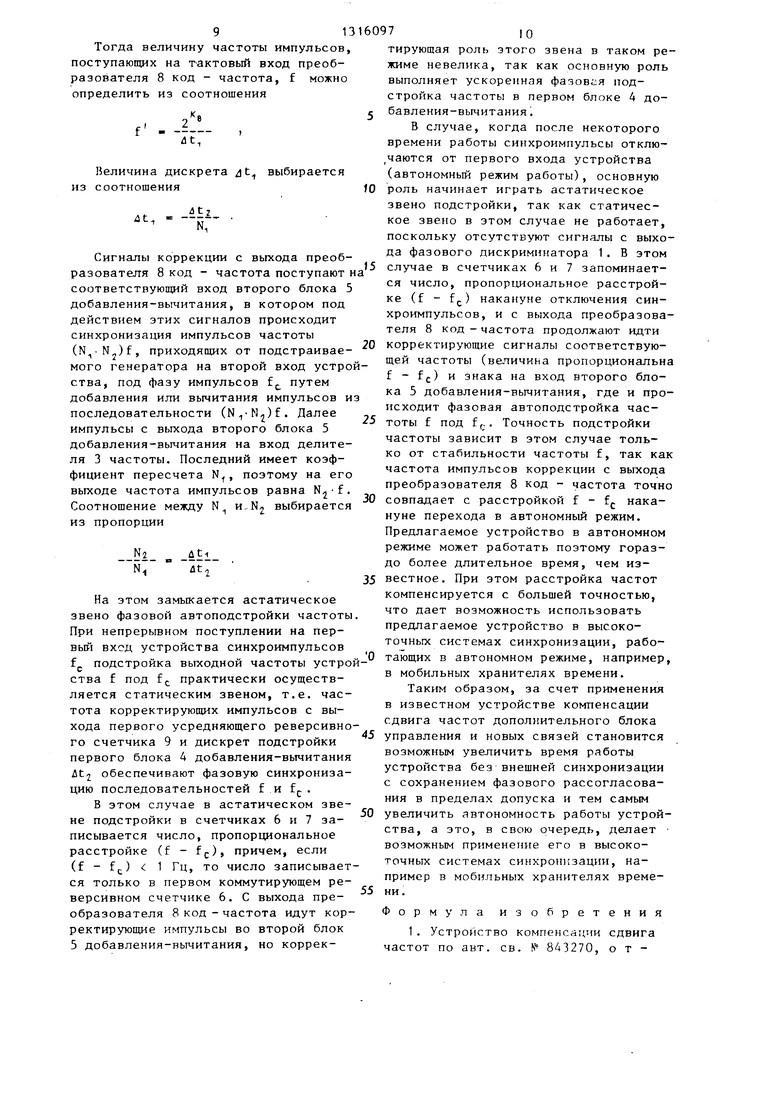

На фиг. 1 представлена структурная электрическая схема устройства компенсации сдвига частот на фиг. 2 - структурная электрическая схема блока формиропания управляющих импульсов j на фиг. 3 - временные диаграм- мы работы блока формирования управляющих импульсов.

Устройство компенсации сдвига частот содержит фазовый дискриминатор 1, первый 2 и второй 3 делители час- тоты, первый 4 и второй 5 блоки добавления-вычитания, первый 6 и второй 7 коммутирующие реверсивные счетчики преобразователь 8 код - частота, первый 9 и второй 10 усредняющие ревер- сивные счетчики, первый 11 и второй 12 элементы запрета, первый 13, второй 14, третий 15 и четвертый 16 элементы И, блок 17 обнуления и блок 18 формирования управляющих импуль- сов. Блок 18 формирования управляющих импульсов (фиг. 2) содержит первый RS-триггер 19, первый элемент ИЛИ 20, второй RS-триггер 21, первый 22 и второй 23 формирователи, второй элемент ИЛИ 24, третий формирователь 25 коротких импульсов, третий элемент ИЛИ 26 и D-триггер 27.

Устройство компенсации сдвига частот работает следующим образом.

В основе устройства лежит комбинированная система подстройки частоты, состоящая из статического и астатического звеньев.

На первый вход фазового дискрими- натора 1 с первого входа устройства поступают импульсы синхронизирующей последовательности с частотой f, . На второй вход устройства подается подстраиваемая импульсная последователь- ность с частотой M-f, где f ;: , N N N ; N, - коэффициент пересчета делителя 3; N - коэффициент пересчета делителя 2.

Импульсы с выхода первого делителя 2 частоты с частотой f подаются на второй вход фазового дискриминатора 1 и на выход устройства. В фазовом ; 1скриминаторе 1 происходит сравнение фаз импульсной последовательности f и синхроимпульсов f„ , При наличии рассогласования фаз на одном из выходов фазового дискриминатора 1 в зависимости от знака рассогласования появляется имт ульсный сигнал, поступающий на соответствующий вход первого усредняющего реверсивного счетчика 9. Последний обеспечивает равномерную без скачков обработку рассогласования фаз импульсов частоты f и f(. в случае наличия флуктуации фазы импульсов f. из-за шумов в линии связи или возникновения импульсных помех, т.е. сигнал на выходе первого усредняющего реверсивного счетчика 9 появляется только при устойчивом расхождении фазы импульсов f с фазой синхроимпульсов f, когда на один из входов первого усредняющего реверсивного счетчика 9 приходит постоянно больще импульсов с фазового дискриминатора 1, чем на другой. Импульсы с того или иного выхода первого усредняющего реверсивного счетчика 9 поступают на соответствующий вход первого блока 4 добавления-вычитания, на тактовый вход которого с выхода второго делителя 3 частоты приходит подстраиваемая импульсная последовательность с частотой Nj-fi В первом блоке 4 добавления-вычитания происходит синхронизация импульсов Nj-f относительно синхроимпульсов f так, что сигнал f на выходе первого делителя 2 имеет ту же фазу, а следовательно, и частоту, что и синхроимпульсы (-. Сигнал частотой f получается из сигнала частотой N« f путем деления в первом делителе 2 частоты. Синхронизация последовательности происходит путем добавления в эту последовательность импульсов или их исключения из этой последовательности в первом блоке 4 добавления-вычитания под действием управляющих импульсных сигналов, приходящих от первого усредняющего реверсивного счетчика 9, величина (количество импульсов) и знак (выход счетчика 9) которых равна величине и знаку фазового расхождения импульсов f и f.. При эгом изменяются частота и фаза импульсов fJj f и, следовательно, частота и фаза импульсов f на выходе первого делителя 2. Причем фаза изменяется дискретно, величина дискрета равна д1J.

Таким образом, фазовый дискриминатор 1, первьв усредняющий реверсивный счетчик 9, первый блок 4 добавления-вычитания и первый делитель 2 частоты составляют первое статичес- кое звено подстройки частоты, которо обеспечивает фазирование импульсов f относительно импульсов f, с точностью до дискрета подстройки, равного N ut.. Данное звено работает только при наличии эталонных синхроимпульсов fg на первом входе устройства.

Астатическое звено подстройки частоты работает следующим образом.

Управляющие импульсные сигналы с выхода первого усредняющего реверсивного счетчика 9 поступают на второй усредняющий реверсивный счетчик 10, где происходит дополнительное усреднение этих сигналов во времени. При этом, если величина и знак сигнала на входе второго усредняющего реверсивного счетчика 10 пропорциональны величине и знаку фазового расхождения импульсов f и f J-, то величина и знак сигнала на выходе счетчика 10 пропорциональны первой производной |По времени величины и знака фазового рассогласования импульсов f и f,T.e скорости расхождения фаз или разнос- ти этих частот. Таким образом, астатическое звено подстройки должно скорре ктировать фазовое расхождение импульсов f и f, вызванное неравенством этих частот (их действительных значений).

Сигналы с выходов счетчика второго усредняющего раверсивного счетчик 10 поступают через первый 11 и второ 12 элементы запрета, в качестве которых могут быть использованы элементы ИЛИ, на соответствующие входы первого коммутир тощего реверсивного счетчика 6. Выходные сигналы первого усредняющего реверсивного счетчика 9 поступают через первый 13 и второй 14 элементы И на соответствующие входы второго коммутирующего ре

версивного счетчика 7. Выходы перво50

го 6 и второго 7 коммутирующих реверсивных счетчиков подключены к соответствующим информационным входам преобразователя 8 код - частота. Последний, в зависимости Ьт кода, запи- ., Да счетчика 9 начинают поступать санного в первый 6 и второй 7 ком- импульсные сигналы. Разрядность счет- мутирующие реверсивные счетчики, вырабатывает импульсные сигналы, поступающие на соответствующие входы

После включения питан1;я в случае присутствия на первом входе устройства синхроимпульсов f начинается фазовая подстройка импульсов с выхода второго делителя 2 частоты (выход устройства) под синхроимпульсы f в статическом звене автоподстройки частоты. При этом с того или иного выхо- 9

чика 9 выбирается из соотноьчения

Т

log,

-- ilt,-N.3

второго блока 5 добавления-вычитания. В нем частота выходных импульсов оп- pJEдeляeтcя из соотношения

-пр

f . Е М

г

5 0 5 0 5

,,

5

где t

ПР

0

, Да счетчика 9 начинают поступать импульсные сигналы. Разрядность счет-

частота сигналов на выходе преобразователя 8 код-частота ;

- частота импульсов на тактовом входе преобразователя 8 код-частота, являющемся третьим входом устройства;

m - значение числа, код которого присутствует на информационных входах преобразователя 8 код-частота; М - максимально возможное из

этих чисел при данной разрядности преобразователя В код - частота.

Знак выходного сигнала преобразователя, т.е. с какого выхода преобразователя 8 код - частота идет сигнал на второй блок 5 добавления-вычитания, определяется состоянием старшего разряда первого 6 и второго 7 коммутирующего реверсивных счетчиков.

При включении питающих напряжений блок 17 обнуления вырабатывает единичный импульсньш сигнал небольшой длительности, которьп производит начальную установку разрядов первого 6 и второго 7 коммутирующих реверсивных счетчиков, при которой с выхода преобразователя 8 код, - частота поступают импульсы с частотой следования, близкой к нулю. При этом на выходах третьего 15 и четвертого 16 элементов И присутствует сигнал уровня логического О, который открывает для прохождения сигналов первого 11 л второго 12 элементов запрета и закрывает первый 13 и второй 14 элементы И.

После включения питан1;я в случае присутствия на первом входе устройства синхроимпульсов f начинается фазовая подстройка импульсов с выхода второго делителя 2 частоты (выход устройства) под синхроимпульсы f в статическом звене автоподстройки частоты. При этом с того или иного выхо- 9

Да счетчика 9 начинают поступать импульсные сигналы. Разрядность с

чика 9 выбирается из соотноьчения

Т

log,

-- ilt,-N.3

ч N, новилась при включении питающего напряжения .

Разрядность первого коммутирующего реверсивного счетчика 6 выбираетгде Т - период следования импульсов на выходе первого делителя 2 частоты;

дискрет подстройки фазы импульсов в первом блоке 4 до- с ся из условия бавления-вычитания; коэффициент пересчета первого делителя 2 частоты. Импульсы поступают с выходов третьего 15 и четвертого 16 элементов И 10 где if „ - минимал но возможное рас- сигналы коррекции проходят на соответствующие входы первого коммутирующего реверсивного счетчика 6 через

Кь - log,

1

Tf

мин

1,

второй усредняющий реверсивный счетхоященйё частот f и f. Логическая 1 с выходов третьего 15 и четвертого 16 элементов И за- крьшает первый 11 и второй 12 эле- чик 10 и открытые первый 11 и второй 15 менты запрета и открывает первый 13 12 элементы запрета. Во втором усред- и второй 14 элементы И для прохожде- няющем реверсивном счетчике 10 частота импульсов с выхода первого усредняющего реверсивного счетчика 9

ния импульсов. При этом сигнал с соответствующего выхода первого усредняющего реверсивного счетчика 9, ми- усредняется во времени с целью добить-20 нуя второй усредняющий реверсивный ся ее пропорциональности разности счетчик 10 и первый коммутирующий ре- частот (f - fj), в то время как частота импульсов на выходе первого усредняющего реверсивного счетчика 9

версивный счетчик 6, следует на соответствующий вход второго коммутирующего реверсивного счетчика 7, т.е.

кию фаз импульсов с выхода первого делителя 2 частоты и синхроимпульсов f . Разрядность второго усредняющего реверсивного счетчика 10 определяется из соотношения

пропорциональна начальному расхожде- 25 сигнал с выхода первого усредняющего

реверсивного счетчика 9 без дополнительного усреднения поступает на вход второго коммутирующего счетчика 7, управляющего старшими разрядами пре- 30 образователя 8 код-частота. Таким образом происходит ускоренная запись в первый 6 и второй 7 коммутирующие реверсивные счетчики числа, пропорционального расстройке (f - f j.) . Раз- где At2 - дискрет подстройки фазы им- 35 рядность счетчика второго коммутирующего реверсивного выбирается из условия

К.

°Si 4t;Tr- f;).N;

пульсов в первом блоке 4 добавления-вычитания; f - частота импульсов на выходе первого делителя 2 частоты j40 fj. - частота синхроимпульсов

на первом входе устройстваj Nj, - коэффициент пересчета первого делителя 2 частоты. Величина й. дискрета подстройки 45 счетчиках, определяет частоту кор- выбирается из учета требуемой точное- ректирующих сигналов с того или ино- ти подстройки и чувствительности ап- го выхода преобразователя 8код-час- паратуры,стоящей на выходе устройства.

К, logjluf el 1,

где - максимально возможное

расхождение частот f и f. Число, записанное в первом 6 и втором 7 коммутирующих реверсивных

тота, а выход преобразователя 8 код- частота, с которого идет сигнал

При установке всех разрядов первого коммутирующего реверсивного счетчика 6 в 1 или О, что соответствует сдвигу частот (f - f), превы50 (знак коррекции), определяется старшим разрядом числа, записанного в первом 6 и втором 7 коммутирующих реверсивных счетчиках.

В случае, когда происходит перешающему 1 Гц, на выходах третьего 15 регулирование, т.е. число, записан- и четвертого 16 элементов И появля- нов в первом 6 и втором 7 коммути- ется сигнал логической 1, так как рующих реверсивных счетчиках, после i эти элементы открыты логической 1 ускоренной подстройки такое, что ха- с выхода блока 18, которая там уста- рактеризует расстройку (f - f), боль

новилась при включении питающего напряжения .

Разрядность первого коммутирующего реверсивного счетчика 6 выбирается из условия где if „ - минимал но возможное рас-

условия f „ - минимал но возможн

Кь - log,

1

Tf

мин

1,

ния импульсов. При этом сигнал с соответствующего выхода первого усредняющего реверсивного счетчика 9, ми- нуя второй усредняющий реверсивный счетчик 10 и первый коммутирующий ре-

версивный счетчик 6, следует на соответствующий вход второго коммутирующего реверсивного счетчика 7, т.е.

счетчиках, определяет частоту кор- ректирующих сигналов с того или ино- го выхода преобразователя 8код-час-

К, logjluf el 1,

где - максимально возможное

расхождение частот f и f. Число, записанное в первом 6 и втором 7 коммутирующих реверсивных

счетчиках, определяет частоту кор- ректирующих сигналов с того или ино- го выхода преобразователя 8код-час-

тота, а выход преобразователя 8 код- частота, с которого идет сигнал

(знак коррекции), определяется старшим разрядом числа, записанного в первом 6 и втором 7 коммутирующих реверсивных счетчиках.

В случае, когда происходит перерегулирование, т.е. число, записан- нов в первом 6 и втором 7 коммути- рующих реверсивных счетчиках, после i ускоренной подстройки такое, что ха- рактеризует расстройку (f - f), боль

713

шую чем она есть на самом деле, изменяется знак сигнала на выходе первого усредняющего реверсивного счетчика 9 и, следовательно, на выходе второго усредняющего реверсивного счетчика 10. Это приводит k тому, что на выходе блока 18 появляется сигнал логического О (фиг. 3), который закрывает элементы И 15 и 16 для сигнала ускоренной подстройки. При этом прекращается прохождение импульсов с первого усредняющего реверсивного счетчика 9 на вход второго коммутирующего реверсивного счетчика 7 (заканчивается грубая ускоренная подстройка) и начинают проходить импульсы на вход первого коммутирующего реверсивного счетчика 6 с выхода второго усредняющего реверсивного счетчика 10 (снова начинается точная подстройка частот, характерная для расхождения f - f 1 Тц) . Но теперь импульсы проходят на другой вход первого коммутирующего счетчика 6, чем в начале подстройки (поменялся знак сигнала),число в первом коммутирующем реверсивном счетчике 6 уменьшается до тех пор, пока число, записанное в счетчиках 6 и 7, не станет наиболее точно характеризовать расхождение частот (f - f.), в этом случае подстройка заканчивается и число изменяется только в диапазоне 11 младшего разряда счетчика 6.

В схеме блока 18 (фиг. 2) при включении напряжения питания второй RS-триггер 21 устанавливается в О по прямому выходу, а D-триггер 27 в 1 по прямому выходу (фиг. 3). Пред положим, что расхождение f - f, имеет положительный знак (принято услов но), тогда на S-вход RS-триггера 19 начинают поступать импульсы с соответствующего выхода второго усредняю щего реверсивного счетчика 10 (фиг. За). При этом первый импульс устанавливает первый RS-триггер 19 в 1 по прямому выходу (фиг. За) и в О по инверсному (фиг. Зг). Кроме того, входной импульс проходит через первый элемент ИЛИ 20 (фиг. Зв) на S- вход второго RS-триггера 21 (фиг.Зи) На выходах (прямом и инверсном) первого RS-триггера 19 и на прямом выходе второго RS-триггера 21 стоят формирователи 22, 23 и 25 коротких импульсов, формирующие короткие импульсы из положительных перепадов по60978

тенциала на их входе (из О в 1). Первый импульс на первом входе данного блока вызывает появление такого короткого импульса на выходах фор мирователей 23 и 25, так как на прямых выходах RS-триггеров 19 и 21 перепад из О в 1 (фиг. Зд, ж, и, к). Импульс с выхода формирователя 23 проходит через второй элемент ИЛИ 24

W (фиг. 3,з) на С-вход D-триггера 27, но не вызывает изменения его состояния (появление О на прямом выходе), так как на 8-вход этого триггера приходит импульс с выхода формировате15 ля 25, прошедший через третий элемент ИЛИ 26 (фиг. Зк, м). На все последующие входные сигналы того же знака RS-триггеры 19 и 21, а следовательно, и весь блок 18 управления не

20 реагируют. Теперь, пусть происходит перерегулирование, и импульсы начинают поступать с другим знаком, т.е. на другой (второй) вход блока с другого выхода второго усредняющего ре25 версивного счетчика 10 (фиг. 3,6). Это приводит к тому, что первый импульс другого знака (пусть минус условно) изменяет состояние первого RS-триггера 19, в данном случае ус30 танавливает его по R-входу в О TIC прямому выходу и в Г по инверсному. В этом случае короткий импульс появляется на выходе формирователя 22 и, пройдя через второй элемент ИЛИ 24,

35 изменяет состояние D-триггера 27 на противоположное (фиг. Зг-ж, л,м). При этом происходит запирание третьего 15 и четвертого 16 элементов И для прохождения сигнала разрешения

0 ускоренной грубой подстройки и начи- нается точная отработка перерегулирования в первом коммутирующем реверсивном счетчике 6.

После того, как в счетчиках 6 и 7

45 установится число, точно характеризующее расстройку (f - , возможен вновь переход на быструю подстройку частоты.

В предлагаемом устройстве разряд50 кость преобразователя 8 код - частота определяется так же, как в известном из соотношения

55 8 l°8iN:N-T4tr .

где ut - дискрет подстройки фазы импульсов во втором блоке 5 добавления-вычитания.

Тогда величину частоты импульсов, поступающих на т-актовый вход преобразователя 8 код - частота, f можно определить из соотношения

f ut.

Величина дискрета t выбирается из соотношенияfO

t.

t2

N,

Сигналы коррекции с выхода преоб15

20

разователя в код - частота поступают на соответствуюш 1й вход второго блока 5 добавления-вычитания, в котором под действием этих сигналов происходит синхронизация импульсов частоты ()f, приходящих от подстраиваемого генератора на второй вход устройства, под фазу импульсов путем добавления или вычитания импульсов из последовательности (Ni-M2)f. Далее - импульсы с выхода второго блока 5 добавления-вычитания на вход делителя 3 частоты. Последний имеет коэффициент пересчета N, поэтому на его выходе частота импульсов равна . Соотношение между N и,N выбирается из пропорции

N uti

N.

at.

.На этом замыкается астатическое звено фазовой автоподстройки частоты При непрерывном поступлении на пер- вьй вход устройства синхроимпульсов f подстройка выходной частоты устройства f под f. практически осуществляется статическим звеном, т.е. частота корректирующих импульсов с выхода первого усредняющего реверсивного счетчика 9 и дискрет подстройки первого блока 4 добавления-вычитания ЛС обеспечивают фазовую синхронизацию последовательностей f и fj. .

В этом случае в астатическом звене подстройки в счетчиках 6 и 7 записывается число, пропорциональное расстройке (f - f), причем, если (f - f) 1 Гц, то число записывается только в первом коммутирующем реверсивном счетчике 6. С выхода преобразователя 8 код - частота идут кор- ректируюш {е импульсы во второй блок 5 добавления-вычитания, но коррекfO

15

20

-

35

О

45

50

55

тирующая роль этого звена в таком режиме невелика, так как основную роль выполняет ускоренная фазовая подстройка частоты в первом блоке 4 добавления-вычитания .

В случае, когда после некоторого времени работы синхроимпульсы отклю- чаются от первого входа устройства (автономный режим работы), основную роль начинает играть астатическое звено подстройки, так как статическое звено в этом случае не работает, поскольку отсутствуют сигналы с выхода фазового дискриминатора 1. В этом случае в счетчиках 6 и 7 запоминается число, пропорциональное расстройке (f - fj.) накануне отключения синхроимпульсов, и с выхода преобразователя 8 код - частота продолжают идти корректирующие сигналы соответствующей частоты (величина пропорциональна f - fc) и знака на вход второго блока 5 добавления-вычитания, где и происходит фазовая автоподстройка частоты f под ff.. Точность подстройки частоты зависит в этом случае только от стабильности частоты f, так как частота импульсов коррекции с выхода преобразователя 8 код - частота точно совпадает с расстройкой f - f накануне перехода в автономный режим. Предлагаемое устройство в автономном режиме может работать поэтому гораздо более длительное время, чем известное. При этом расстройка частот компенсируется с большей точностью, что дает возможность использовать предлагаемое устройство в высокоточных системах синхронизации, работающих в автономном режиме, например, в мобильных хранителях времени.

Тактл образом, за счет применения в известном устройстве компенсации сдвига частот дополнительного блока управления и новых связей становится возможным увеличить время работы устройства без внешней синхронизации с сохранением фазового рассогласования в пределах допуска и тем самым увеличить автономность работы устройства, а это, в свою очередь, делает возможным применение его в высокоточных системах синхронизации, например в мобильных хранителях времени.

Формула изобретения

1. Устройство компенсации сдвига частот по авт. св. V 843270, о т П131609712

личающ ееся тем, что, с це-го элемента ИЛИ, а выходы через перлью повьшения точности компенсациивый и второй формирователи коротких

сдвига частот, в него введен блокимпульсов подключены к входам второформирования управляющих импульсов,го элемента ИЛИ, выход которого подпервый и второй входы которого соеди- ключей к С-входу D-триггера, D-вход

немы с соответствующими выходами вто-которого подключен к инверсному выхорого усредняющего реверсивного счет-ду D-триггера, прямой выход которого

чика, третий выход - с вьПсодом бло-является выходом блока формирования

ка обнуления, а выход - с дополнитель-управляющих импульсов, а к S-входу

ным входом третьего и четвертого эле-JOD-триггера подключен выход третьего

ментов И.

элемента ИЛИ, первый и второй входы которого подключены соответственно к R-входу второго RS-триггера, являю щемуся третьим входом блока формиро2. Устройство по п. 1, отличающееся тем, что блок формирования управляющих импульсов содер- 5 вания управляющих импульсов, и через жит первый RS-триггер, входы которого третий формирователь коротких импуль являются первым и вторым входами блока формирования управляющих импульсов и соединены с входами первосов к выходу второго RS-триггера, S-вход которого соединен с выходом первого элемента ИЛИ,

элемента ИЛИ, первый и второй входы которого подключены соответственно к R-входу второго RS-триггера, являющемуся третьим входом блока формирования управляющих импульсов, и через третий формирователь коротких импуль

вания управляющих импульсов, и чере третий формирователь коротких импул

сов к выходу второго RS-триггера, S-вход которого соединен с выходом первого элемента ИЛИ,

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации | 1984 |

|

SU1223390A1 |

| Устройство цифровой фазовой автоподстройки частоты | 1982 |

|

SU1125748A1 |

| Устройство фазовой автоподстройки частоты | 1987 |

|

SU1469553A1 |

| Устройство компенсации сдвигачАСТОТ | 1979 |

|

SU843270A1 |

| Устройство автоматической подстройки частоты | 1989 |

|

SU1698987A1 |

| Резервированный генератор импульсов | 1989 |

|

SU1619440A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1332552A1 |

| Устройство восстановления несущей фазоманипулированного сигнала | 1990 |

|

SU1786659A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

Изобретение относится к радиотехнике и является дополнительным к авт. св. № 843270. Цель изобретения - -повьппение точности коьшенсации сдвига частот. Устр-во содержит фазовый дискриминатор 1, делители 2 и 3 частоты, блоки добавления-вычитания 4 и 5, коммутирующие реверсивные счетчики 6 и 7, преобразователь 8 .код - частота,усредняющие реверсивные счетчики 9 и 10, эл-ты запрета 11 и 12, эл-ты И 13-16, блок 17 обнуления и блок формирования управляющих импульсов (БФУИ) 18. Цель достигается путем увеличения времени работы устр- ва без внешней синхронизации с сохранением фазового рассогласования в пределах допуска с помощью введенного БФУИ 18. Устр-во по п. 2 ф-лы отличается выполнением БФУИ 18, дана его ил. 1 з-п. ф-лы, 3 ил. сл 00 О5 о со vl N)

| Устройство компенсации сдвигачАСТОТ | 1979 |

|

SU843270A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-06-07—Публикация

1985-08-13—Подача