со: 00 00 00

со

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах и устройствах обработки данных для выполнения над матрицами операции С + АВ.

Цель изобретения - расширение функциональных возмолшостей устройства за счет выполнения Дополнительных операций и повышение его быстродействия.

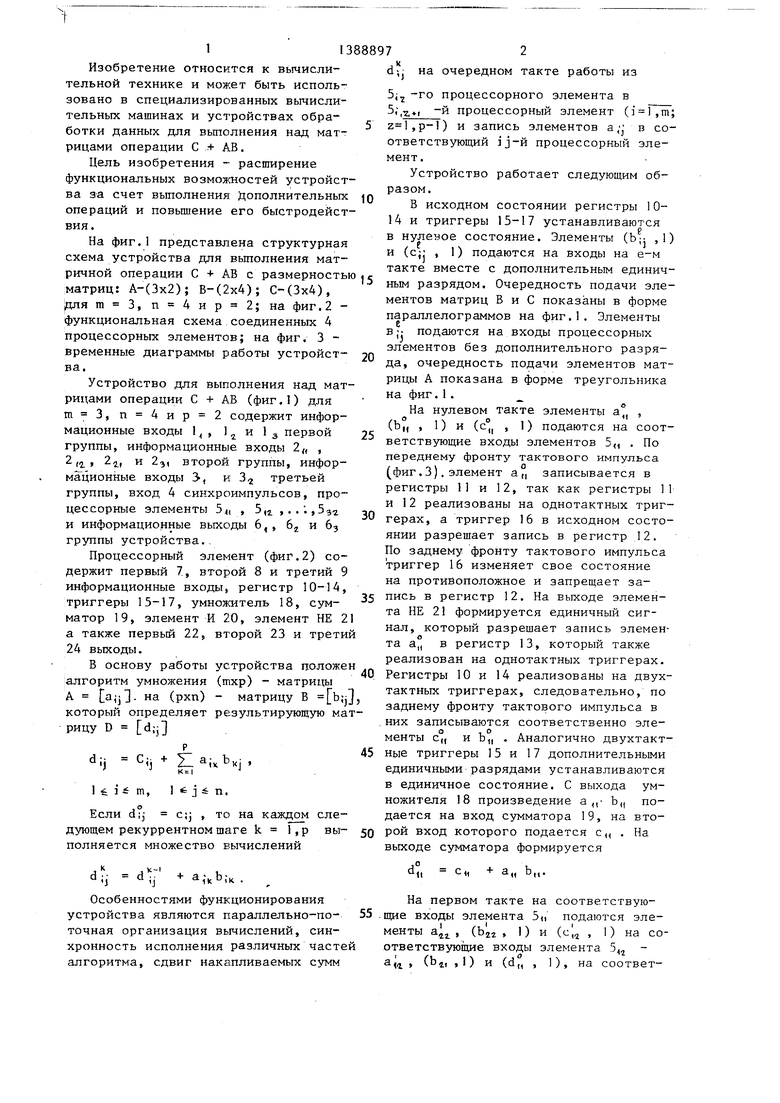

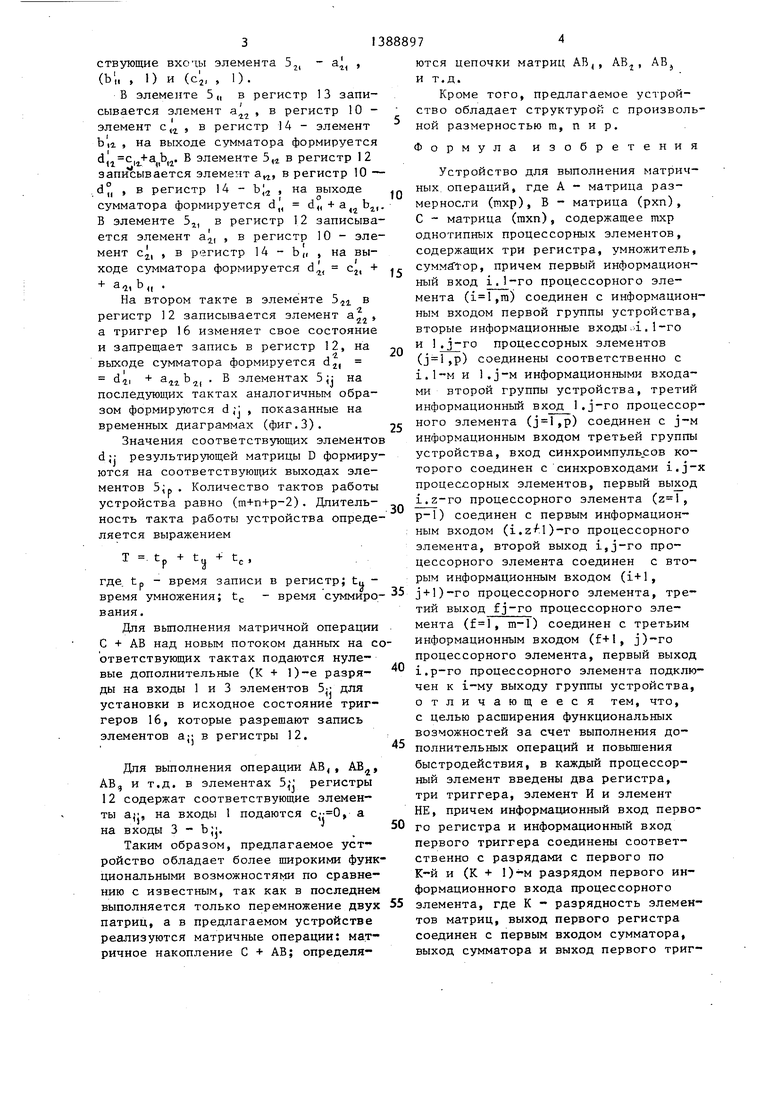

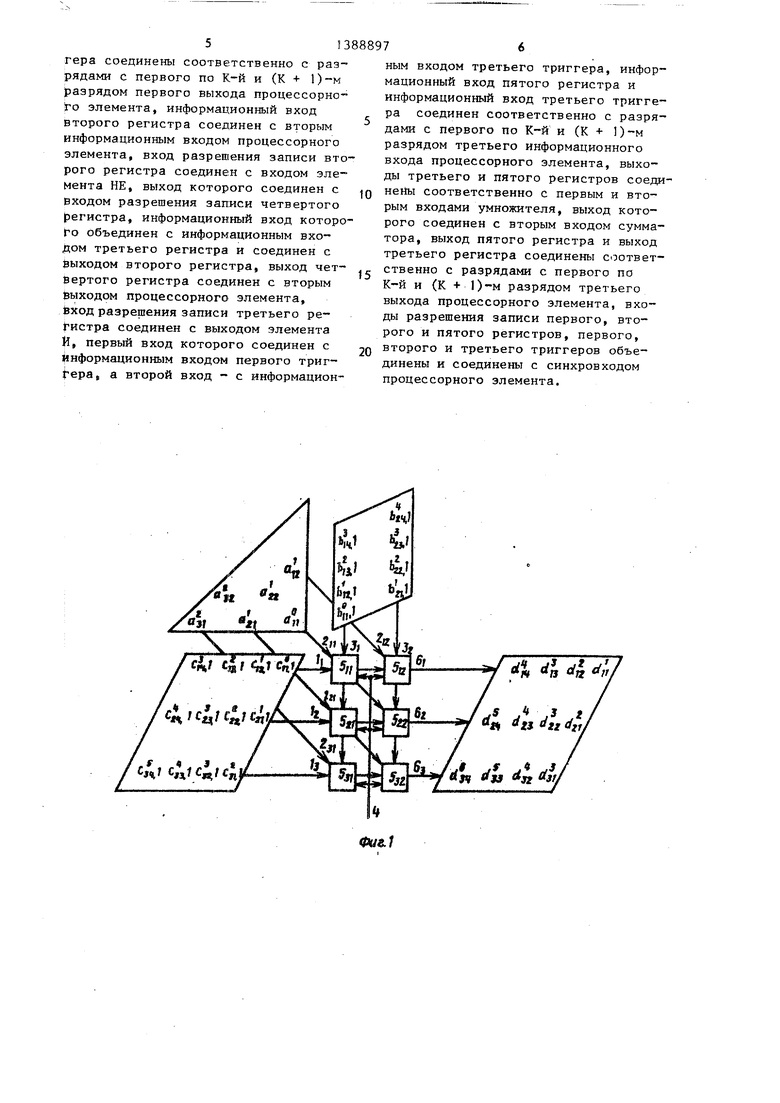

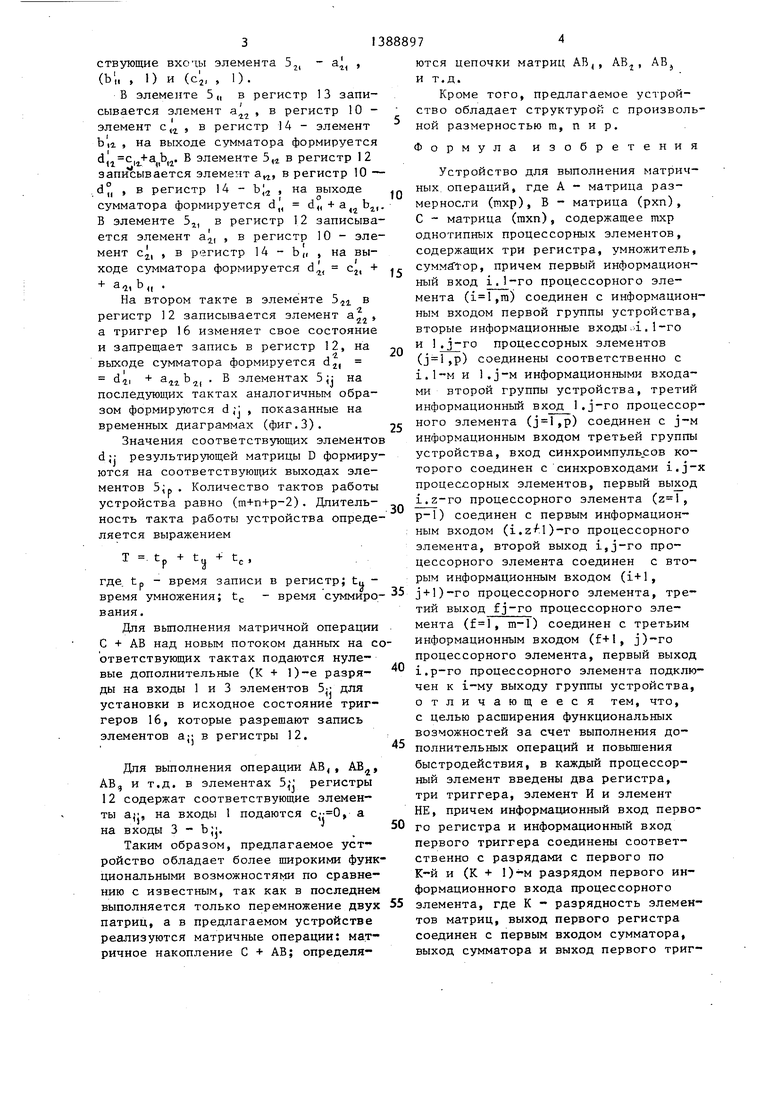

На фиг.1 представлена структурная схема устройства для вьтолнения матричной операции С + АВ с размерностью матриц: А-(Зх2); В-(2x4); С-(3x4), :для т 3, п 4ир 2;на фиг. 2 - функциональная схема соединенных 4 процессорных элементов; на фиг. 3 - временные диаграммы работы устройст- ва.

Устройство для выполнения над матрицами операции С + АВ (фиг.1) для , содержит информационные входы 1 , 1,., и 1 3 первой группы, информационные входы 2„ , 2,, 2, и 2э1 второй группы, инфор- ма ционные входы 3, и 3 третьей группы, вход 4 синхроимпульсов, процессорные элементы 5щ , 5,i ,, и информационные выходы 6, , 6j, и 63 группы устройства..

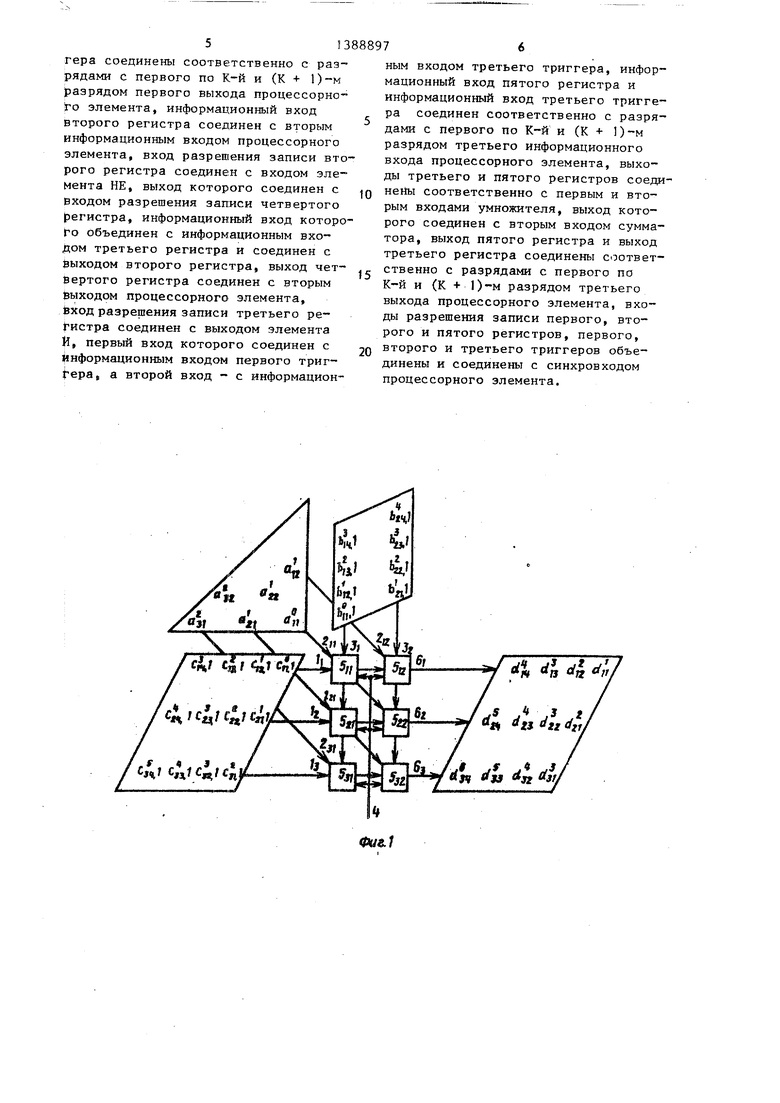

Процессорный элемент (фиг.2) содержит первый 7, второй 8 и третий 9 информационные входы, регистр 10-14, триггеры 15-17, умножитель 18, сум- матор 19, элемент И 20, элемент НЕ 21 а также первый 22, второй 23 и третий 24 выходы.

В основу работы устройства положен алгоритм умножения (тхр) - матрицы А ajj. на (рхп) - матрицу В b;j который определяет результирующую матрицу D djj

dii Cj. а;,Ъ

ж - Kj I

1 i i m, 1 t j i n,

Если d°j C)j , TO на каждом следующем рекуррентном шаге k 1, р вы- зо полняется множество вычислений

V

а;.,Ь;к .

.J ч - .к

Особенностями функционирования устройства являются параллепьно-по- 55 точная организация вычислений, синхронность исполнения различных частей алгоритма, сдвиг накапливаемых сумм:

с 0

5 о

..

5

о

5

d-- на очередном такте работы из

5; -го процессорного элемента в 5,-2,4.| -и процессорный элемент (i l,m; ,p-l) и запись элементов а; в соответствующий ij-й процессорный элемент.

Устройство работает следующим образом.

В исходном состоянии регистры 10- 14 и триггеры 15-17 устанавливаются в нулевое состояние. Элементы (Ь- ,1) и (cjj , 1) подаются на входы на е-м такте вместе с дополнительным единичным разрядом. Очередность подачи элементов матриц В и С показаны в форме параллелограммов на фиг.1. Элементы в ; подаются на входы процессорных элементов без дополнительного разряда, очередность подачи элементов матрицы А показана в форме треугольника на фиг.1.

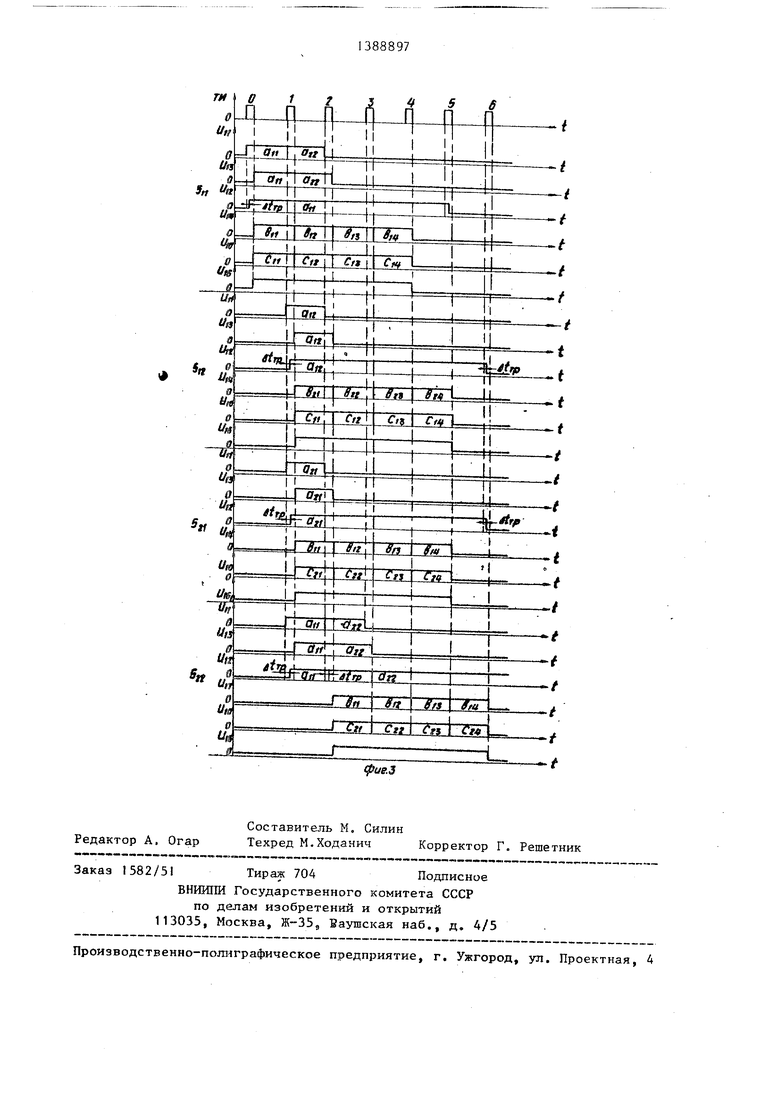

На нулевом такте элементы а, , (Ь„ , 1) и (с°, , 1) подаются на соответствующие входы элементов 5, . По переднему фронту тактового импульса (фиг.3). элемент а,, записывается в регистры 11 и 12, так как регистры 11 и 12 реализованы на однотактных триггерах, а триггер 16 в исходном состоянии разрешает запись в регистр 12, По заднему фронту тактового импульса триггер 16 изменяет свое состояние на противоположное и запрещает запись в регистр 12. На выходе элемента НЕ 2 формируется единичный сигнал, который разрешает запись элемента а° в регистр 13, который также реализован на однотактных триггерах. Регистры 10 и 14 реализованы на двухтактных триггерах, следовательно, по заднему фронту тактового импульса в них записываются соответственно элементы с„ и Ь„ . Аналогично двухтактные триггеры 15 и 17 дополнительными единичными разрядами устанавливаются в единичное состояние. С выхода умножителя 18 произведение а,, Ъ,, подается на вход сумматора 19, на второй вход которого подается c , На выходе сумматора формируется

d,, с„ + а„ Ь,,.

На первом такте на соответствую- .щие входы элемента 5ц подаются элементы а,

, (bji , ) и (с , I)

на соответствующие входы элемента 5, - (bj, ,1) и (d,, , 1), на соответствующие вхо ш элемента 5, - а , (Ь ,. , I) и (с, ,1).

В элементе 5„ в регистр 13 записывается элемент а., , в регистр 10 I, ,

элемент с, , в регистр 14 - элемент

b11 , на выходе сумматора формируется d,,,j. В элементе 5,,i в регистр 12 записывается элемент а, в регистр 10 - d,, , в регистр 14 - b|,j на выходе сумматора формируется d,, d,, а b,, В элементе 5, в регистр 12 записывается элемент а, , в регистр 10 - элемент Cj, , в регистр 14 - b,, , на выходе сумматора формируется d, с, + + а, Ь„ .

На втором такте в элементе 5 в регистр 12 записывается элемент а триггер 16 изменяет свое состояние

и запрещает запись в регистр 12, на

,-i выходе сумматора формируется d,

dii + 1. В элементах 5;; на последующих тактах аналогичным образом формируются d,-; , показанные на временных диаграммах (фиг.З).

Значения соответствующих элементов d;: результирующей матрицы D формируются на соответствующих выходах элементов . Количество тактов работы

устройства равно (m+n+p-2). Длительность такта работы устройства определяется выражением

,

Т tp t t,.

где. tp - время записи в регистр} tn время умножения; tf. - время суммирования.

Для выполнения матричной операции С + АВ над новым потоком данных на соответствующих тактах подаются нулевые дополнительные (К + 1)-е разря- ды на входы 1 и 3 элементов 5- для установки в исходное состояние триггеров 16, которые разрешают запись

элементов a;j в регистры 12.

Для выполнения операции АВ, АВ, АВ, и т.д. в элементах 5,. регистры 12 содержат соответствующие элементы а

jj, на входы 1 подаются , а

,T ч - Ъ

на входы 3 - Ь;.

Таким образом, предлагаемое устройство обладает более широкими функциональными возможностями по сравнению с известным, так как в последнем выполняется только перемножение двух патриц, а в предлагаемом устройстве реализуются матричные операции: матричное накопление С + АВ; определя5

д,. . «г

-,«

и

25

30

35

45

50

55

ются цепочки матриц АВ,, АВ, , АВ и т.д.

Кроме того, предлагаемое устройство обладает структурой с произвольной размерностью га, п и р.

Формула изобретения

Устройство для выполнения матричных, операций, где А - матрица раз- мернос.ти (тхр), В - матрица (рхп) , С - матрица (гахп), содержащее тхр однотипных процессорных элементов, содержащих три регистра, умножитель, cyMMrftop, причем первый информационный вход i.1-го процессорного элемента (,m) соединен с информационным входом первой группы устройства, вторые информационные входы;d.1-го и l.j-ro процессорных элементов () соединены соответственно с i.l-M и 1.J-M информационными входами второй группы устройства, третий информационный вход l.j-ro процессорного элемента (,p) соединен с j-M информационным входом третьей группы устройства, вход синхроимпуль сов которого соединен с синхровходами i.j-x процессорных элементов, первый выход i.z-ro процессорного элемента (, р-1) соединен с первым информационным входом (i.zfl)-ro процессорного элемента, второй выход i,j-ro процессорного элемента соединен с вторым информационным входом (, j+l)-ro процессорного элемента, третий выход fj-ro процессорного элемента (, m-1) соединен с третьим информационным входом (f+1, j)-ro процессорного элемента, первый выход i.p-ro процессорного элемента подключен к i-му выходу группы устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет выполнения дополнительных операций и повьшения быстродействия, в каждый процессорный элемент введены два регистра, три триггера, элемент И и элемент НЕ, причем информационный вход первого регистра и информационный вход первого триггера соединены соответственно с разрядами с первого по К-й и (К + 1)-м разрядом первого информационного входа процессорного элемента, где К - разрядность элементов матриц, выход первого регистра соединен с первым входом сумматора, выход сумматора и выход первого триггера соединены соответственно с разрядами с первого по К-й и (К + 1)-м разрядом первого выхода процессорно- го элемента, информационный вход второго регистра соединен с вторым информационным входом процессорного элемента, вход разрешения записи второго регистра соединен с входом элемента НЕ, выход которого соединен с входом разрешения записи четвертого регистра, информационный вход которо f o объединен с информационным входом третьего регистра и соединен с выходом второго регистра, выход четвертого регистра соединен с вторым Выходом процессорного элемента, йход разрешения записи третьего ре- t HCTpa соединен с выходом элемента И, первый вход которого соединен с Информационным входом первого триг- fepa, а второй вход - с информацион

ным входом третьего триггера, информационный вход пятого регистра и информационный вход третьего триггера соединен соответственно с разрядами с первого по К-й и (К + 1)-м разрядом третьего информационного входа процессорного элемента, выходы третьего и пятого регистров соединены соответственно с первым и вторым входами умножителя, выход которого соединен с вторым входом сумматора, выход пятого регистра и выход третьего регистра соединены соответственно с разрядами с первого по К-й и (К + 1)-м разрядом третьего выхода процессорного элемента, входы разрешения записи первого, второго и пятого регистров, первого, второго и третьего триггеров объединены и соединены с синхровходом процессорного элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для перемножения матриц | 1988 |

|

SU1552200A1 |

| Устройство для вычисления двухмерного преобразования фурье | 1989 |

|

SU1661790A1 |

| Устройство для обращения плотных ( @ х @ ) матриц | 1986 |

|

SU1387013A1 |

| Устройство для вычисления двумерного дискретного преобразования Фурье | 1988 |

|

SU1589289A1 |

| Устройство для умножения матриц | 1990 |

|

SU1793446A1 |

| Устройство для обращения матриц | 1987 |

|

SU1527643A1 |

| Устройство для выполнения операций над матрицами | 1990 |

|

SU1741153A1 |

| Устройство для решения систем алгебраических уравнений | 1983 |

|

SU1226427A1 |

| Устройство для вычисления свертки | 1989 |

|

SU1679502A1 |

| Устройство для матричных операций | 1987 |

|

SU1429127A1 |

Изобретение относится к области вычисТгительной техники и может быть использовано в специализированных вычислительных машинах и устройствах обработки данных. Цель изобретения - расширение функциональных возможностей устройства за счет вьтолнения дополнительных операций и повьш1ение быстродействия. Цель достигается тем, что в устройстве, содержащем тр однотипных процессорных элементов, где m и р - размерность матриц А и В соответственно, имеющих три perHctpa, умножитель и сумматор, в каждый процессорный элемент введены два регистра, ;три триггера, элемент И и элемент . И-НЕ. Особенностью функционирования устройства являются параллельно-поточная организация вычислений, синхронность исполнения различных частей алгоритма. 3 ил. с ю (Л

у Л 4 TJ|

j-ra L--у rf

iL, 4JL, в/в it

g gi2-у 4 «

/

rSb «

фие.2

| Однородная параллельная вычислительная структура для вычисления произведения матрицы на вектор | 1984 |

|

SU1236500A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ХИМИЧЕСКИЙ ИСТОЧНИК ТОКА | 1998 |

|

RU2144245C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1988-04-15—Публикация

1986-10-15—Подача