ка-д лителя соединены соответственно с выходом первого элемента И и входом дешифратора нуля, выход переноса- счетчика-делителя подключен к тактирующим входам блока вычитания, регистра инкрементных приращений и накапливающего сумматора и входу одновибратора, выход которого сое.динен с вторым входом элемента И-НЕ первым входом третьего элемента И, устанрвочным входом второго триггера, входом сброса первого триггера и установочным входом счетчика коррекции, выход элемента И-НЕ подключен к второму входу третьего элемента И, тактирующему входу второго триггера и счетному входу счетчика коррекции, информационный вход и выход второго триггера соединены соответственно с шиной нулевого потенциала и управляющими входами третьего и четвертого регистров, третий вход и выхо третьего элемента И подключены соответственно к инверсному выходу первого триггера и управляющим входам первого и второго регистров, выходы которых соединены соответственно с информационными входами третьего и четвертого регистров и первым и вторым выходами кода координат устройства, вход . шифратора подключен к выходу регистра инкрементных приращений, выход шифратора-соединен с адресHI IM входом блока памяти и управляющими входами первого и второго сдвигателей, второй информационный выход блока памяти подключен к информационному входу накапливающего сумматора, а знаковый выход блока вычитания соединен с управляющими входами первого и второго сумматоров.

2.-Устройство по П.1, о т л ичающееся тем, что блок вычитания содержит два сумматора, .нуль-орган, триггер, масштабный резистор и ключ, .причем первый и второй первого сумматора подключены соответственно к суммирующему и вычитающему входам блока, выход первого сумматора соединен с первым входом второго сумматора, входом нуль-органа и через масштабный резистор с входом ключа, выход которого подключен к второму входу второго сумматора, выход второго сумматора соединен с информационным выходом блока, выход нуль-органа подключен к управляющему входу ключа и информационному входу триггера, синхровход и выход которого соединены соответственно с тактирующим входом и знаковым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Устройство для вычисления квадратного корня | 1984 |

|

SU1264167A1 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1290352A1 |

| Инкрементный умножитель аналоговых сигналов | 1983 |

|

SU1113820A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Аналого-цифровой инкрементный умножитель | 1982 |

|

SU1057971A1 |

| Устройство интерполяции для отображения графической информации | 1984 |

|

SU1164732A1 |

| Функциональный генератор напряжения | 1976 |

|

SU734746A2 |

1. УСТРОЙСТВО ДЛЯ ПОВОРОТА ВЕКТОРА, содержащее четыре регистра, два сдвигателя, два сумматора, блок памяти, блок управления, счетчик коррекции, шифратор, блок вычитания, группу пороговых элементов г приоритетную схему, регистр инкрементных приращений, накапливающий сумматор и цифроаналоговый преобразователь, вход и выход которого соединены соответственно с выходом накапливающего.сумматора и вычитающим входом блока вычитания, суммирующий вход, знаковый выход и информационный выход блока вычитания подключены соответственно к аналоговому входу устройства,входу приращения накапливающего сумматора и входам пороговых элементов группы, выходы которых соединены с входами приоритетной схемы, выход которой подключен к информационному входу регистра инкрементных приращений, выход накапливающего сумматора соединен с информационным выходом устройства, первый информационный выход блока памяти подключен к информационному входу счетчика коррек ции, информационный и установочный входы устройства .соединены соответственно с первыми информационными входами и установочными входами первого и второго регистров, вторые информационные входы которых подключены к выходам соответственно первого и второго сумматоров, первый и второй информационные входы первого сумматора соединены с выходами соответственно третьего регистра и второго сдвигателя, первый и второй информационные входы второго сумматора подключены к выходам соответственно четвертого регистра и первого сдвигателя, информационные входы первого и второго сдвигателей соединены с выходами соответственно перво го и второго регистров, о т л ичающееся тем, что, с целью повышения быстродействия, оно содержит шифратор, а блок управления включает мультивибратор, два триггера, счетчик-делитель, дешифратор нуля, одновибратор, три элемента И, элемент И-НЕ, элемент задержки и элемент ИЛИ, первый и второй входы и выход которого подключены соответ ственно к прямому выходу первого триггера , выходу дешифратора нуля и первому входу первого элемента И, запускающий вход устройства соединен с входом установки О накапливающеО го сумматора, входом сброса счетчика-делителя, входом мультивибратора j и первым входом второго элемента И, горой вход и выход которого подключены соответственно к выходу счетчика коррекции и установочному вхо,ЕСу первого триггера, выход мультивибратора соединен с вторым входом первого элемента И и входом элемента задержки j,. выход которого подключен к первому входу элемента И-НЁ, счетный вход и информационный выход счетчи

Изобретение относится к вычисли тельной технике и может быть использовано в управляющих и моделирующих устройствах как общего, так и специального назначения. . Поворот векторов и координат используется во многих задачах управления и моделирования с примене ем реальной аппаратуры. При этом угол поворота часто снимается с датчиков в аналоговой форме, в то время как координаты объекта представлены в ЦВМ в цифровой форме. Известно аналого-цифровое устройство для поворота вектора, содержащее два сумматора, элементы ИЛИ, четыре группы элементов И реверсивный счетчик, два регистра схему сравнения и другие вспомогательные элементы, причем аргумент представленный в аналоговой.форме посредством схемы сравнения и реверсивного счетчика отслеживается с формированием элементарных прира щений, используемых для поворота вектора по методу решения на цифровых дифференциальных анализатоpax (ГИД) определяющих систем дифференциальных уравнений iT . Недостатками данного устройства являются низкие точность и быстродействие, присущие методам вычисления посредством ЦДА. Известно цифровое устройство для поворота вектора, содержащее три регистра, два блока сдвига, семь сумматоров, блок памяти и блок управления, причем соединения между блоками выполнены по схеме, реализующей алгоритм Волдера с коррекцией результата. Если аргумент представлен в аналоговой форме, то последовательно с входом третьего регистра необходимо подключить аналого-цифровой преобразователь 2, Недостатками указанного устройства являются сложность оборудования и малое быстродействие, обусловленное необходимостью выполнения большого количества итераций для каждого изменяющегося значения аргумента. Наиболее близким к предлагаемому является устройство, содержащее последовательно включенные аналогоцифровой преобразователь следящего типа и цифровое устройство для поворота вектора з ,

Известное устройство характеризуется тем, что содержит пять регистров, пять cyivjMaTopOB, два блока сдвига, блок памяти, счетчик кор-., рекций, блок-управления, блок анализа состояния, генератор импульсов, блок вычитания, набор пороговых элементов, приоритетную схему, регистр инкрементных приращений, накапливающий сумматор и цифроаналоговый преобразователь, причем аналого-цифровой преобразователь преобразовывает аналоговый аргумент в цифровой код, после чего осуществляется поворот каждый раз из начального состояния на заданную величину аргумента.

Недостатком известного устройства является низкое быстродействие, обусловленное наличием длительного итерационного процесса при повороте вектора из начального состояния в заданное.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство, содержащее четыре регистра, два сдвигателя, два сумматора, блок памяти, блок управления, счетчик коррекции, шифратор, блок вычитания, группу пороговых элементов, приоритетную схему, регистр инкрементных приращений, накапливающий сумматор и цифроаналоговый преобразователь, входи выход которого соединены соответственно с выходом накапливающего сумматора и вычитающим входом блока вычитания, суммирующий вход, знаковый выход и информационный выход блока вычитания подключены соответственно к аналоговому входу устройства, входу приращения накапливающего сумматора и входам пороговых элементов группы, выходы которых соединены с входами приоритетной схемы, выход которой подключен к информационному входу регистра инкрементных приращений, выход накапливающего сумматора соединен с информационным выходом устройства, первый информационный выход блока памяти подключен к информационному входу счетчика коррекции, информационный и установочный |входы устройства соединены соответственно с первыми информационным входами и установочными входами первого и второго регистров, вторые информационные входы которых подключены к выходам соответственно первого и второго сумматоров,первый и второй информационные входы первого сумматора соединены с выходами соответственно третьего регистра и

второго сдвигателя, первый и второй информационные входы второго сумматора подключены к выходам соответственно четвертого регистра и первого сдвигателя, информационные входы первого и второго сдвигателей соединены с выходами соответственно первого и второго регистров, введен шифратор, а блок управления влючает мультивибратор, два триггера,счетчик-делитель, дешифратор нуля, одновибратор, три элемента И, элемент И-НЕ, элемент задержки и элемент ИЛИ, первый и второй входы и выход которого подключены соответственно к прямому выходу первого триггера, выходу дешифратора нуля и первому входу первого элемента И, запускающий вход устройства соединен с входом установки О накапливающего сумматора, входом сброса счетчика-делителя, входом мультивибратора и первым входом второго элемента И, второй вход и выход которого подключены соответственно к выходу счетчика коррекции и установочному входу первого триггера, выход мультивибратора соединен с вторым входом первого элемента И и входом элемента задержки , выход которого подключен кпервому входу элемента И-НЕ, счетный вход и информационный выход счетчика-делителя соединены соответственно с выходом первого элемента И и входом дешифратора нуля, выход переноса счетчика-делителя подключен к тактирующим входам блока вычитания, регистра инкрементных приращений и накапливающего сумматора и входу одновибратора, выход которого соединен с вторым входом элемента И-НЕ, первым входом третьего элемента И,установочным входом второго триггера, входом сброса первого триггера и . установочным входом счетчика коррекции, выход элемента И-НЕ подключен к второму входу третьего элемента И, тактирующему входу второго триггера и счетному входу счетчика коррекции, информационный вход и выход второго триггера соединены соответственно с шиной нулевого потенциала и управляющими входами третьего и четвертого регистров третий вход и выход третьего элемента И подклю ены соответственно к инверсному выходу первого триггера и управляющим входам первого и второго регистров, выходы которых соединены соответственно с информационными входами третьего и четвертого регистров и nepBtJM и вторьпи выходами кода координат устройства вход шифратора подключен к выходу регистра инкрементных приращений, выход шифратора соединен с адресным

входом блока памяти и управляющими входами первого и второго сдвигателей, второй информационный выход блок-а памяти подключен к информационному входу накапливающего сумматора, а знаковый выход блока вычитания соединен с управляющими входами первого и второго сумматоров.

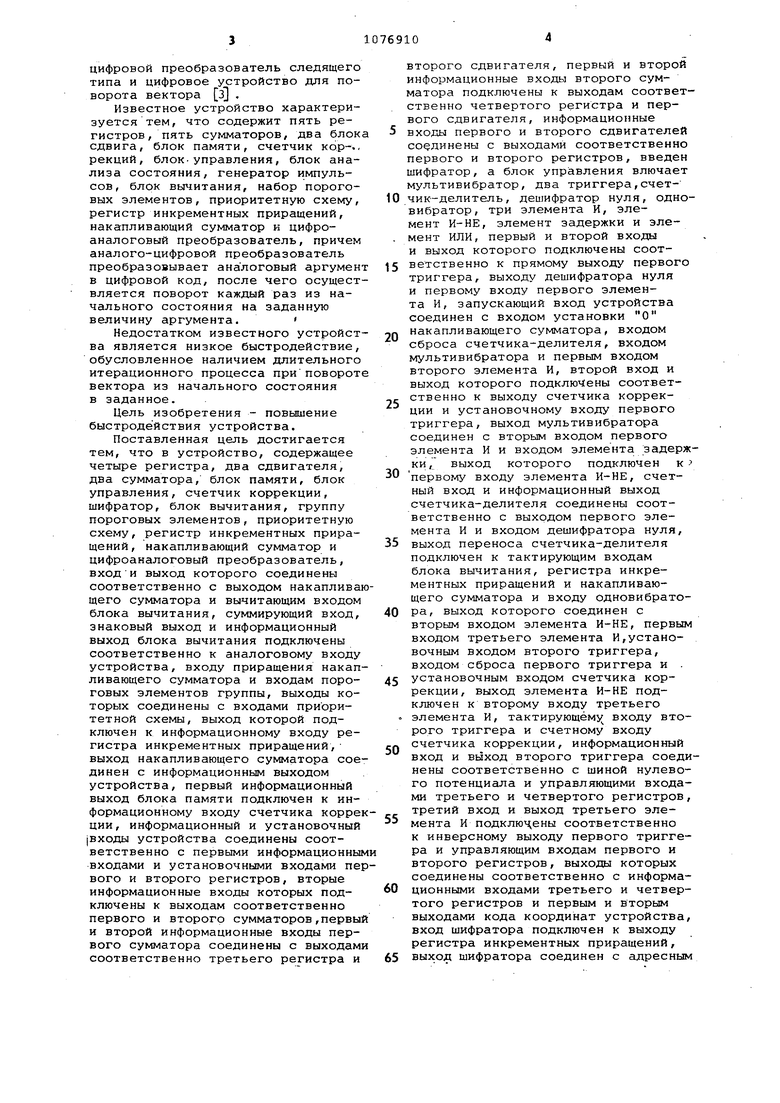

Блок вычитания содержит два , нуль-орган, триггер, Масштабный резистор и ключ, причем первый и второй входы первого сумматора подключены соответственно к суммирующему и вычитающему входам блока, выход первого сумматора соединен с первым входом второго сумматора, входом нуль-органа и через масштабный резистор с входом ключа выход которого подключен к второму входу второго cyKiwaTOpa, выход второго сумматора соединен с информационным входом ©пока, выход нульоргана подключен к управляющему входу ключа и информационному входу триггера, синхровход и выход которого соединены соответственно с тактирующим входом и знаковым выходом бл ок а.

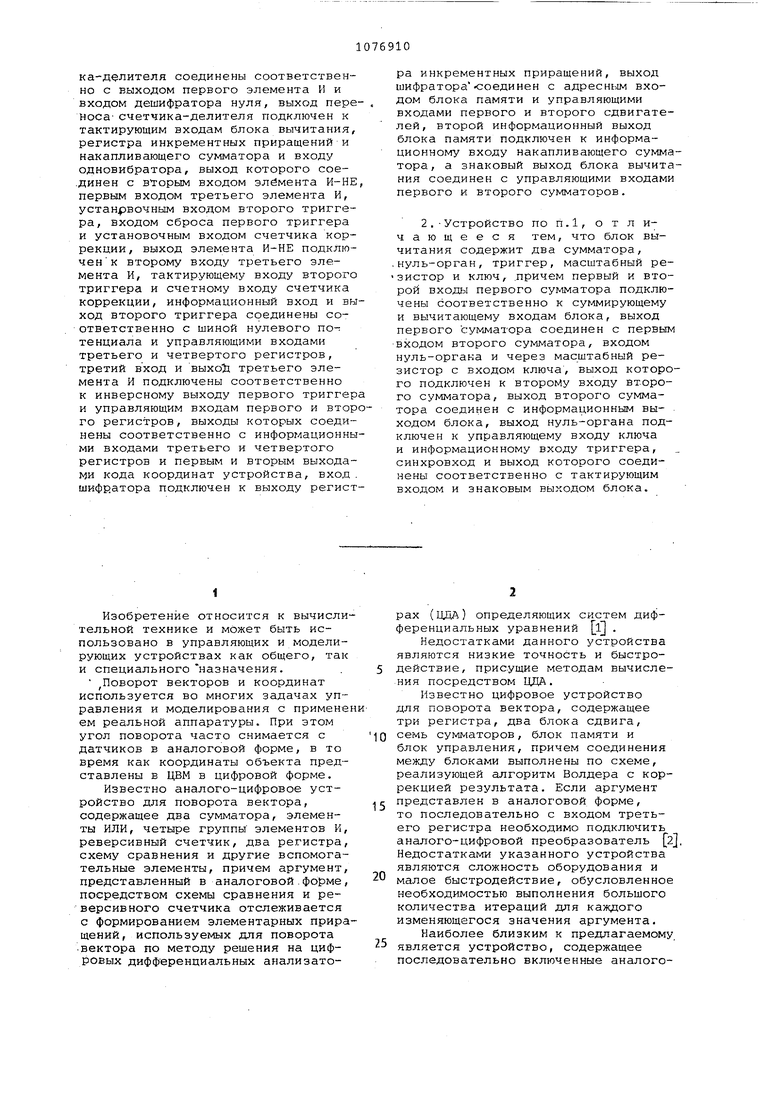

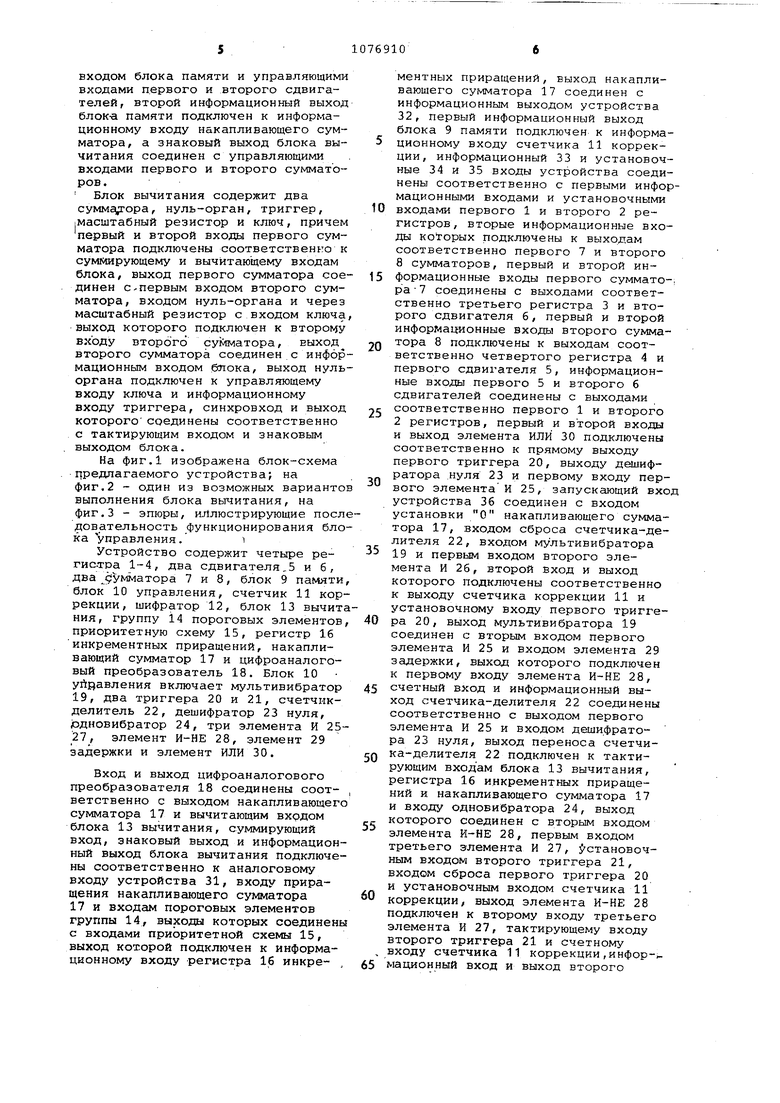

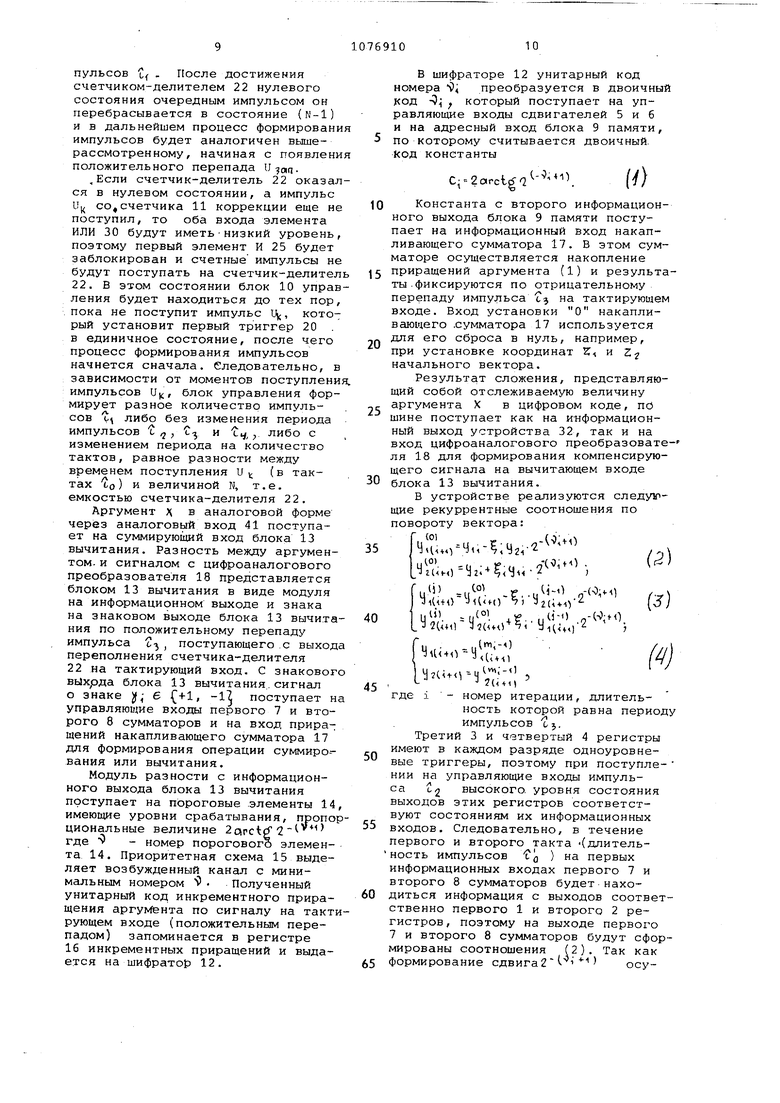

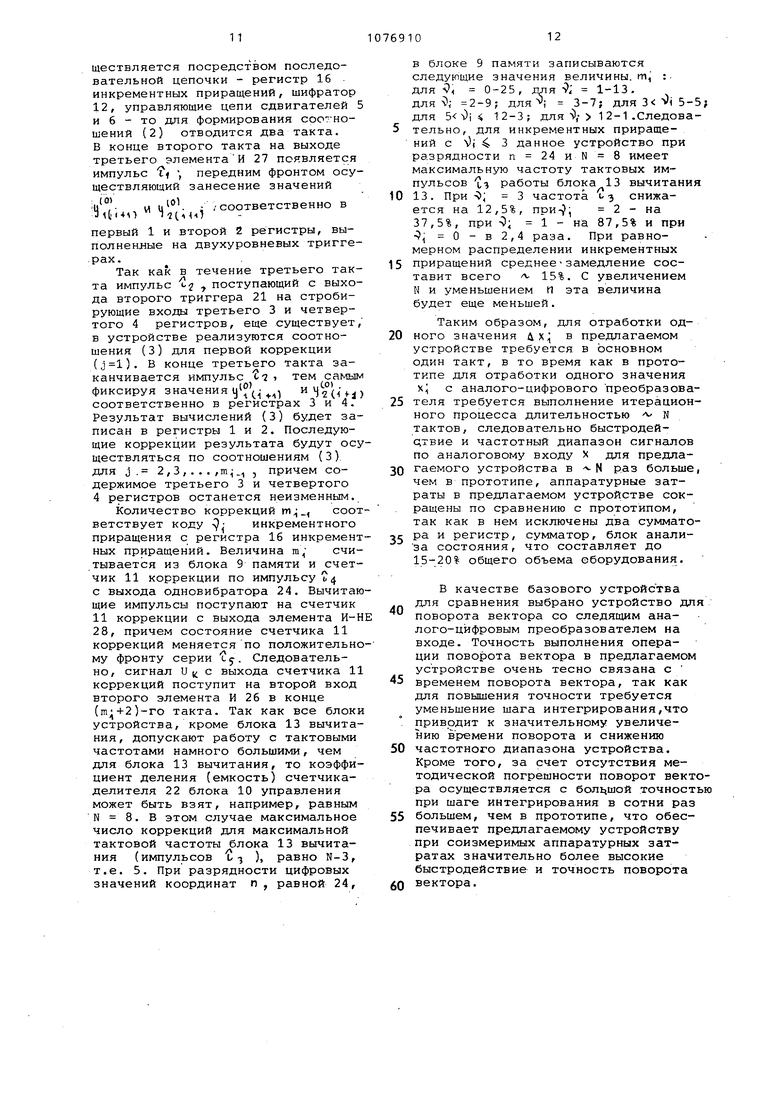

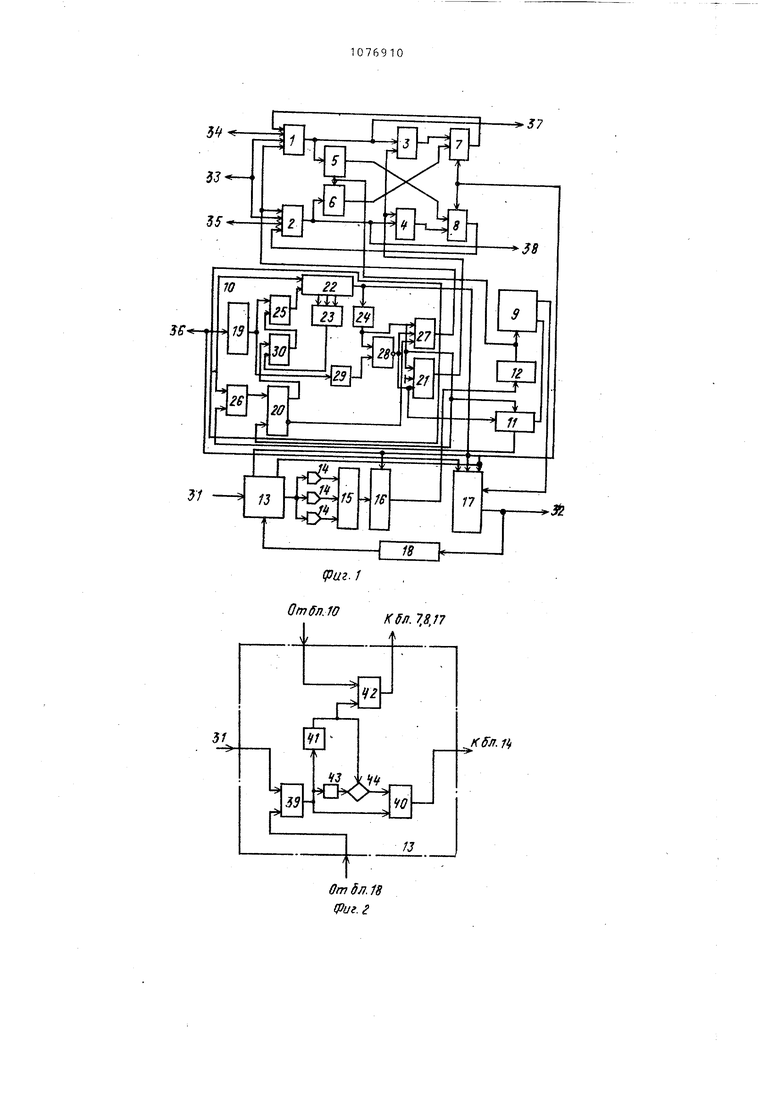

На фигЛ изображена блок-схема предлагаемого устройства; на фиг.2 - один из возможных варианто выполнения блока вьтчитания, на фиг.З - эпюры, иллюстрирующие послдовательность функционирования блока управления. 1

Устройство содержит четыре регистра 1-4, два сдвигателя,5 и 6, два 5 умматора 7 и 8, блок 9 памяти блок 10 управления, счетчик 11 коррекции, шифратор 12, блок 13 вычитния, группу 14 пороговых элементов приоритетную схему 15, регистр 16 инкрементных приращений, накапливающий сумматор 17 и цифроаналоговый преобразователь 18. Блок 10 уйдавления включает мультивибратор 19, два триггера 20 и 21, счетчикделитель 22, дешифратор 23 нуля, рдновибратор 24, три элемента И 2527, элемент И-НЕ 28, элемент 29 задержки и элемент ИЛИ 30.

Вход и выход цифроаналогового преобразователя 18 соединены соответственно с выходом накапливающего сумматора 17 и вычитающим вхрдом блока 13 вычитания, суммирующий вход, знаковый выход и информационный выход блока вычитания подключены соответственно к аналоговому входу устройства 31, входу прирашения накапливающего сумматора 17 и входам пороговых элементов группы 14, выходы которых соединены с входами приоритетной схемы 15, выход которой подключен к информационному входу регистра 16 инкрементных приращений, выход накапливающего сумматора 17 соединен с информационным выходом устройства 32, первый информационный выход блока 9 памяти подключен к информа5 ционному входу счетчика 11 коррекции, информационный 33 и установочные 34 и 35 входы устройства соединены соответственно с первыми информационными входами и установочными

0 входами первого 1 и второго 2 регистров, вторые информационные входы когорых подключены к выходам соответственно первого 7 и второго 8 сумматоров, первый и второй ин5 формационные входы первого суммато-: ра 7 соединены с выходами соответственно третьего регистра 3 и второго сдвигателя б, первый и второй информационные входы второго суммаQ тора 8 подключены к выходам соответственно четвертого регистра 4 и первого сдвигателя 5, информационные входы первого 5 и второго 6 сдвигателей соединены с выходами

5 соответственно первого 1 и второго 2 регистров, первый и второй входы и выход элемента ИЛИ 30 подключены соответственно к прямому выходу первого триггера 20, выходу дешифратора нуля 23 и первому входу первого элемента И 25, запускающий вход устройства 36 соединен с входом установки О накапливающего сумматора 17, входом сброса счетчика-делителя 22, входом мультивибратора

5 19 и первым входом второго элемента И 26, второй вход и выход которого подключены соответственно к выходу счетчика коррекции 11 и установочному входу первого тригге0 ра 20, выход мультивибратора 19 соединен с вторым входом первого элемента И 25 и входом элемента 29 задержки, выход которого подключен к первому входу элемента И-НЕ 28,

5 счетный вход и информационный выход счетчика-делителя 22 соединены соответственно с выходом первого элемента И 25 и входом дешифратора 23 нуля, выход переноса счетчиQ ка-делителя 22 подключен к тактирующим входам блока 13 вычитания, регистра 16 инкрементных приращений и накапливающего сумматора 17 и входу одновибратора 24, выход которого соединен с вторым входом элемента Й-НЕ 28, первым входом третьего элемента И 27, становочным входом второго триггера 21, входом сброса первого триггера 20 и установочным входом счетчика 11

коррекции, выход элемента И-НЕ 28 подключен к второму входу третьего элемента И 27, тактирующему входу второго триггера 21 и счетному , входу счетчика 11 коррекции , инфор-н.

5 мационный вход и выход второго

триггера 21 соединены соответственно с шиной нулевого потенциала и управляющими входами третьего 3 и четвертого 4 регистров, третий вход и выход третьего элемента И 27 подключены соответственно к инверсному выходу первого триггера 20 и управляющим входам первого 1 и второго 2 регистров, выходы которых соединены соответственно с информационными входами третьего 3 и четвертого 4 регистров и первым 37 и вторым 38 выходами кода координат устройства, вход шифратора 12 подключен к выходу регистра 16 инкре.ментных пр иращений, выход шифратора 12 соединен с адресным входом блока 9 памяти и управляющими входами- первого 5 и второго 6 сдвигателей, второй информационный выход блока 9 памяти подключен к информационному входу накапливающего сумматора 17, а знаковый выход блока 13 вычитания соединен с управляющими входами первого 7 и второго 8 сумматоров.

Блок 13 вычитания содержит два сумматора 39 и 40, нуль-орган 41, триггер 42, масштабный резистор 43/ и ключ 44, причем первый и второй входы первого сумматора 39 подключены соответственно к суммирующему и вычитающему входам блока, выход первого сумматора 39 соединен с первым входом второго сумматора 40, входом нуль-органа 41 и через масштабный регистр 43 с входом ключа 44, выход которого подключен к второму входу второго сумматора 40, выход второго сумматора 40 соединен с информационным выходом блока, выход нуль-органа 41 подключен к управляющему вход ключа 44 и информационному входу триггера 42, синхровход и выход которого соединены соответственно с тактирующим входом и знаковым выходом блока.

Последовательность работы устройства состоит в занесении через информационный вход устройства 33 цифровых значений координат Z и Z2 исходного вектора, задании аналогового аргумента X на аналоговом входе 31, выдаче запускающего сигнала зап ° запускающему входу 36 и снятии в процессе отслеживания результатов вычислений на выходах кода координат устройства 37 и 38.

Последовательность вычислений в устройстве -определяется сигналами блока 10 управления. Запускающий сигнал 1Ц(з,;, низкого уровня, поступая через запускающий вход устройства 36 на вход мультивибратора 19 и вход сброса счетчика-делителя 22, сбрасывает их в нулевое состояние. Одновременно изап через вто

рой элемент И 26 устанавливает первый триггер 20 в единичное состояние. Когда запускающий сигнал Uзцр принимает высокий уровень, мультивибратор 19 начинает фор иировать серию импульсов ьд, которая при высоком уровне на выходе элемента ИЛИ 30 через первый элемент И 25 поступает на счетный вход счетчика-делителя 22. Счетчик-делитель.

0 22 работает на вычитание, причем изменение его состояния осуществляется по положительному фронту им,пульса с выхода первого элемента И 25.Так как первый триггер 20 установлен в единичное состоя5ние, то высоким уровнем с прямого выхода этого триггера (сигнал Т) обеспечивает поступление на счетчик-делитель 22 первого счетного импульса. Если емкость счетчика0делителя 22 равна N, то первым импульсом он устанавливается в состояние N-1. Следовательно, на последовательном выходе счетчика-делителя 22, соответствующем выходу триггера

5 старшего разряда, сформируется сигнал 3 высокого уровня, который запускает одновибратор 24, на вцхо- де которого формируется сигнал С. низкого уровня, который, поступая

0 на установочный вход второго триггера 21, устанавливает его в единичное состояние, обеспечивая формирование высокого уровня сигнала t. Кроме того, сигнал L с выхода

5 одновибратора 24, поступая на обнуляющий вход первого триггера 20, сбрасывает последний в нулевое состояние, обеспечивая формирование низкого уровня сигнала Т на прямом выходе первого триггера 20.Но пока

0 счетчик-делитель 22 не окажется в нулевом состоянии, на выходе дешифратора нуля 23 будет сигнал высокого уровня, который через элемент ИЛИ 30 будет разрешать прохождение счёт5ных импульсов, длительность импульсов С с выхода одновибратора 24 несколько меньше величины двух периодов серии CQ , поэтому на выходе третьего элемента И 27 нач0нут формироваться импульсы i с задержкой на два такта, в то время как на выходе элемента И-НЕ 28 положительные импульсы t через три такта, причем передний фронт

5 их соответствует заднему фронту задержанных на элементе 29 задержки импульсов серии приходом с счетчика 11 коррекции отрицательного импульса первый триггер 20 устанавливается в единичное состояние. Если U | поступит до достижения счетчикомделителем 22 нулевого состояния, то первый триггер 20 по инверсномувыходу блокирует формирование им5

пульсов LI , После достижения счетчиком-делителем 22 нулевого состояния очередным импульсом он перебрасывается в состояние (N-1) и в дальнейшем процесс формирования импульсов будет аналогичен вышерассмотренному, начиная с появления положительного перепада U-JQKJ.

.Если счетчик-делитель 22 оказался в нулевом состоянии, а импульс и со,счетчика 11 коррекции еще не поступил, то оба входа элемента ИЛИ 30 будут иметь-низкий уровень, поэтому первый элемент И 25 будет заблокирован и счетные импульсы не будут поступать на счетчик-делитель 22. В этом состоянии блок 10 управления будет находиться до тех пор, пока не поступит импульс , который установит первый триггер 20 . в единичное состояние, после чего процесс формирования импульсов начнется сначала. Следовательно, в зависимости от моментов поступления импульсов U|, блок управления формирует разное количество импульсов tt либо без изменения периода

А

Су,, либо с

импульсов с ,, L-j

и

изменением периода на количество тактов, равное разности между временем поступления U I- (в тактах to) и величиной N, т.е. емкостью счетчика-делителя 22.

Аргумент Л в аналоговой форме через аналоговый вход 41 поступает на суммирующий вход блока 13 вычитания. Разность между аргументом- и сигналом с цифроаналогового преобразователя 18 представляется блоком 13 вычитания в виде модуля на информационном выходе и знака на знаковом выходе блока 13 вычитания по положительному перепаду импульса бз, поступающего с выход переполнения счетчика-делителя 22 на тактирующий вход. С знаковог выхрда блока 13 вычитания.сигнал о знаке ,- 6 (+1, -1 поступает н управляющие входы первого 7 и второго 8 сумматоров и на вход приращений накапливающего сумматора 17 для формирования операции суммирования или вычитания.

Модуль разности с информационного выхода блока 13 вычитания поступает на пороговые элементы 14 имеющие уровни срабатывания, пропоциональные величине где - номер порогового элемента 14. Приоритетная схема 15 выделяет возбужденный канал с минимальным номером J Полученный унитарный код инкрементного приращения apryivffeHTa по сигналу на тактрующем входе (положительным перепадом) запоминается в регистре 16 инкрементных приращений и выдается на шифратор 12.

В шифраторе 12 унитарный код номера )4 преобразуется в двоичный код -Q f который поступает на управляющие входы сдвигателей 5 и 6 и на адресный вход блока 9 памяти, по которому считывается двоичный. код константы

Ю

..

o Константа с второго информационного выхода блока 9 памяти поступает на информационный вход накапливающего сумматора 17. В этом сумматоре осуществляется накопление

5 приращений аргумента (1) и результаты .фиксируются по отрицательному перепаду импульса Сз на тактирующем входе. Вход установки О накапливающего .сумматора 17 используется для его сброса в нуль, например, при установке координат К, и 2 начального вектора.

Результат сложения, представляющий собой отслеживаемую величину аргумента X в цифровом коде, пО шине поступает как на информационный выход устройства 32, так и на вход цифроаналогового преобразователя 18 для формирования компенсирующего сигнала на вычитающем входе

0 блока 13 вычитания.

В устройстве реализуются следующие рекуррентные соотношения по повороту вектора:

-ц - ЧН1+О V 42i

(5)

п(° -U -xif-ti - TZ(«K) -У2.+ Чм )

hi. 1,°. -g.. л)

4i(uO ) ) y2(UiV (j 1

и° 4g-. .9-.

У2(и) УэОмГ У-1(м1 - J

4 - yiuv:;

() .- v:;;:;

где i - номер итерации, длительность которой равна периоду импульсов G}.

Третий 3 и четвертый 4 регистры имеют в каждом разряде одноуровневые триггеры, поэтому при поступле- НИИ на управляющие входы импульса С2 высокого, уровня состояния выходов этих регистров соответствуют состояниям их информационных входов. Следовательно, в течение первого и второго такта -{длительность импульсов t о ) на первых информационных входах первого 7 и второго 8 сумматоров будет находиться информация с выходов соответственно первого 1 и второго 2 регистров, поэтому на выходе первого 7 и второго 8 сумматоров будут сформированы соотношения (2). Так как 5 формирование сдвига2( осуществляется посредством последовательной цепочки - регистр 16 инкрементных приращений, шифратор 12, управляющие цепи сдвигателей 5

и 6 - то для формирования СОО7НОшений (2) отводится два такта. В конце второго такта на выходе третьего элементаИ 27 появляется импульс , передним фронтом осуществляющий занесение значений

ц°,- и ; /соответственно в it(+o )

первый 1 и второй 2 регистры, выполненлые на двухуровневых триггерах.

Так как в течение третьего такта импульс , поступающий с выхода второго триггера 21 на стробирующие входы третьего 3 и четвертого 4 регистров, еще существует/ в устройстве реализуются соотношения (3) для первой коррекции (). В конце третьего такта заканчивается импульс 07 тем самым фиксируя значения ij°( и .соответственно в регистрах 3 и 4. Результат вычислений (3) будет записан в регистры 1 и 2. Последующие коррекции результата будут осуществляться по соотношениям (3) для j. 2,3,...,m , причем содержимое третьего 3 и четвертого 4 регистров останется неизменным.

Количество коррекций т, соответствует коду 9 инкрементного приращения с регистра 16 инкрементных приращений. Величина m, считывается из блока 9 памяти и счетчик 11 коррекции по импульсу 4 с выхода одновибратора 24. Вычитающие импульсы поступают на счетчик 11 коррекции с выхода элемента И-Н 28, причем состояние счетчика 11 коррекций меняется по положительному фронту серии су. Следовательно, сигнал и J/ с выхода счетчика 11 коррекций поступит на второй вход второго элемента И 26 в конце ()-го такта. Так как все блоки устройства, кроме блока 13 вычитания, допускают работу с тактовыми частотами намного большими, чем для блока 13 вычитания, то коэффициент деления (емкость) счетчикаделителя 22 блока 10 управления может быть взят, например, равным N 8. В этом случае максимальное число коррекций для максимальной тактовой частоты блока 13 вычитания (импульсов ii-} ), равно N-3, т.е. 5. При разрядности цифровых значений координат п , равной 24,

в блоке 9 памяти записываются следующие значения величины, т, : для -Р 0-25, для 1-13. для J; 2-9; для ; 3-7; дляЗ 15-5; для 5 ч)| 4 12-3; для , 1 2-1 .Следовательно, для инкрементных приращений с ч); 4 3 данное устройство при разрядности п 24 и N 8 имеет максимальную частоту тактовых импульсов J-) работы блока 13 вычитания

приращений среднее замедление составит всего 15%. С увеличением N и уменьшением И эта величина будет еще меньшей.

Таким образом, для отработки одного значения дх в предлагаемом устройстве требуется в основном один такт, в то время как в прототипе для отработки одного значения х с аналого-цифрового преобразователя требуется выполнение итерационного процесса длительностью N тактов, следовательно быстродейатвие и частотный диапазон сигналов по аналоговому входу X для предлагаемого устройства в N раз больше, чем в прототипе, аппаратурные затраты в предлагаемом устройстве сокращены по сравнению с прототипом, так как в нем исключены два сумматора и регистр, сумматор, блок анализа состояния, что составляет до 15-20% общего объема оборудования.

В качестве базового устройства для сравнения выбрано устройство для поворота вектора со следящим аналого-цифровым преобразователем на входе. Точность выполнения операции поворота вектора в предлагаемом устройстве очень тесно связана с

временем поворота вектора, так как для повышения точности требуется уменьшение шага интегрирования,что приводит к значительному увеличению времени поворота и снижению

частотного диапазона устройства. Кроме того, за счет отсутствия методической погрешности поворот вектора осуществляется с бол11шой точностью при шаге интегрирования в сотни раз

большем, чем в прототипе, что обеспечивает предлагаемому устройству при соизмеримых аппаратурных затратах значительно более высокие быстродействие и точность поворота

вектора.

Ь

1Я

(риг. 1 Отfл.

.r

51

г

J7

Kffl. 1if

40

0m 6л. IB Фиг. г

и

зоп О

0

О

П о

VK

т

J

о

о

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Малиновский Б.Н | |||

| и др | |||

| Введение в кибернетическую технику | |||

| Наукова думка, 1979, с | |||

| Приспособление для воспроизведения изображения на светочувствительной фильме при посредстве промежуточного клише в способе фотоэлектрической передачи изображений на расстояние | 1920 |

|

SU172A1 |

| Деревянный торцевой шкив | 1922 |

|

SU70A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР по заявке № 2977720/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-02-28—Публикация

1982-04-19—Подача