со

00 СХ)

со

СП

СО

Изобретение относится к автоматике и измерительной технике и может быть использовано для хранения мгновенного значения быстроизменяющейся величины на время измерительного процесса.

Целью изобретения является повышение точности устройства.

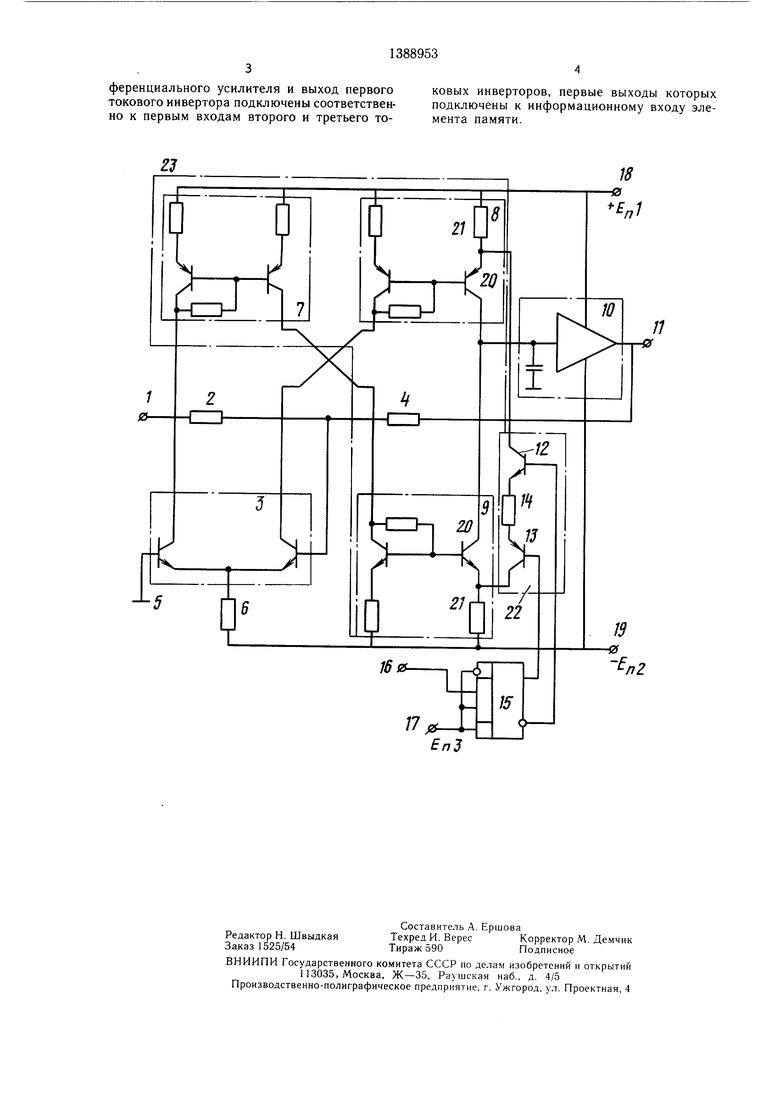

На чертеже приведена принципиальная схема предлагаемого устройства.

Устройство содержит входную клемму 1, первый токозадающий элемент 2 на резисторе, дифференциальный усилитель 3, элемент 4 обратной связи на резисторе, шину 5 нулевого потенциала, второй токозадающий элемент 6 на резисторе, первый, второй и третий токовые инверторы 7, 8, 9, накопительный элемент 10 памяти, выходную клемму 11, первый, второй ключевые элементы 12, 13 на транзисторах, третий токозадающий элемент 14 на резисторе, D-триг- гер 15, управляющий вход 16, третью, первую и вторую шины 17, 18, 19 питания устройства. Усилительные элементы 20 на транзисторах и нагрузочные элементы 21 на резисторах входят в состав токового инвертора.

Коммутирующая цепь 22 состоит из ключевых элементов 12, 13 на транзисторах и третьего токозадающего элемента 14 на резисторе.

Предварительный усилитель 23 включает токовые инверторы 7, 8, 9.

Устройство выборки-хранения работает следующим образом.

В режиме выборки аналоговый сигнал поступает на входную клемму 1 и через резистор 2 - на вход усилителя 3. На этот же вход подается сигнал через элемент 4.

Предварительный усилитель 23 имеет больщой коэффициент усиления из-за динамического характера нагрузки всех каскадов. Динамический диапазон предварительного усилителя симметричен относительно шины 5 и определяется размахом питающих напряжений. Далее сигнал через элемент 10 памяти поступает на клемму 11 и в цепь обратной связи. Ток через элементы 12, 13 и элемент 14 в режиме выборки не протекает, так как триггер 15 под воздействием сигнала на входе 16 установлен в единичное состояние. В таком состоянии схема повторяет входной сигнал на выходной клемме 11 и на входе накопительного элемента с точностью, определяемой глубиной обратной связи и коэффициентом усиления предварительного усилителя.

С изменением управляющего сигнала на входе 16 на низкий уровень триггер 15 приходит в нулевое состояние и разность потенциалов между базами транзисторов 12, 13 становится отпирающей, транзисторы выходят из режима отсечки и переходят в активный режим. При этом ток через них постепенно увеличивается, уменьшая ток в выходном каскаде предварительного усилителя из-за увеличения падения напряжения на элементах 21 выходного каскада, действующего на транзисторы 20 в запирающем

направлении. Ток в цепи коммутации задается при помощи элемента 14 таким, чтобы обеспечить запирание транзисторов 20. При этом режимы усилителя 3, инвертора 7 и входных цепей инверторов 8 и 9 остаются неизменными. Переключение только части питающих токов предварительного усилителя при уменьшении количества коммутируемых элементов и выравнивания времен их коммутации за счет симметрирования цепей коммутации приводит к снижению коммутационной ошибки и повышению точности работы предлагаемого устройства при одновременном увеличении динамического диапазона выходного сигнала.

0

5

0

5

0

5

0

5

Формула изобретения

Устройство выборки-хранения, содержащее первый и второй токозадающие элементы на резисторах, элемент обратной связи на резисторе, токовый инвертор, дифференциальный усилитель, элемент памяти, вход выборки которого является информационным выходом устройства, а информационный вход элемента памяти соединен с первым выводом резистора элемента обратной связи, второй вывод которого подключен к второму входу дифференциального усилителя и второму выводу резистора первого токозадающего элемента, второй вывод которого является информационным входом устройства, первый информационный вход и вход компенсации дифференциального усилителя подключены соответственно к шине нулевого потенциала устройства и первому выводу резистора второго токозадающего элемента, второй вывод которого подключен к второй шине питания устройства, второй и первый входы токового инвертора подключены соответственно к первой шине питания устройства и первому входу дифференциального усилителя, отличающееся тем, что, с целью повышения точности устройства, в него введены второй и третий токовые инверторы, первый и второй ключевые элементы на транзисторах, третий токозадающий элемент на резисторе, первый и второй выводы которого подключены соответственно к эмиттерам транзисторов первого и второго ключевых элементов, а базы являются соответственно первым и вторым управляющими входами устройства, а коллекторы подключены соответственно к третьим входам второго и третьего инверторов, вторые входы которых подключены соответственно к первой и второй шинам питания устройства, к которым подключены соответственно первый и второй входы стабилизации элемента памяти, второй выход дифференциального усилителя и выход первого токового инвертора подключены соответственно к первым входам второго и третьего токовых инверторов, первые выходы которых подключены к информационному входу элемента памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство выборки-хранения | 1990 |

|

SU1716571A1 |

| Устройство выборки-хранения | 1989 |

|

SU1686481A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU881866A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Устройство для решения дифференциальных уравнений | 1980 |

|

SU1339594A1 |

| Устройство для пожарной сигнализации | 1990 |

|

SU1836706A3 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОМАГНИТОМ | 2007 |

|

RU2349978C2 |

| Устройство для определения моментов времени квантования сигналов | 1984 |

|

SU1167731A1 |

| Устройство для выборки и хранения информации | 1986 |

|

SU1388955A1 |

| Электронный коммутатор | 1984 |

|

SU1188874A2 |

Изобретение относится к автоматике и измерительной технике и может быть использовано для хранения мгновенного значения быстроизменяющейся величины. Цель изобретения - повышение точности устройства. Поставленная цель осуществляется за счет переключения только части питающих токов предварительного усилителя при уменьшении количества коммутирующих элементов и выравнивании времен их коммутации за счет симметрирования цепей коммутации, что приводит к снижению коммутационной ошибки и повышению точности работы устройства при одновременном увеличении динамического диапазона выходного сигнала. 1 ил. (Л

Ю

0

ЕпЗ

| Алексеенко А | |||

| Г | |||

| и др | |||

| Применение прецизионных аналоговых микросхем | |||

| М.: Радио и связь, 1985, с | |||

| Универсальный двойной гаечный ключ | 1920 |

|

SU169A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU881866A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-04-15—Публикация

1986-10-17—Подача