Изобретение относится к вычислительной технике, в частности к полупроводниковым постоянным запоминающим устройствам (ПЗУ).

Цель изобретения - повышение быстродействия устройства.

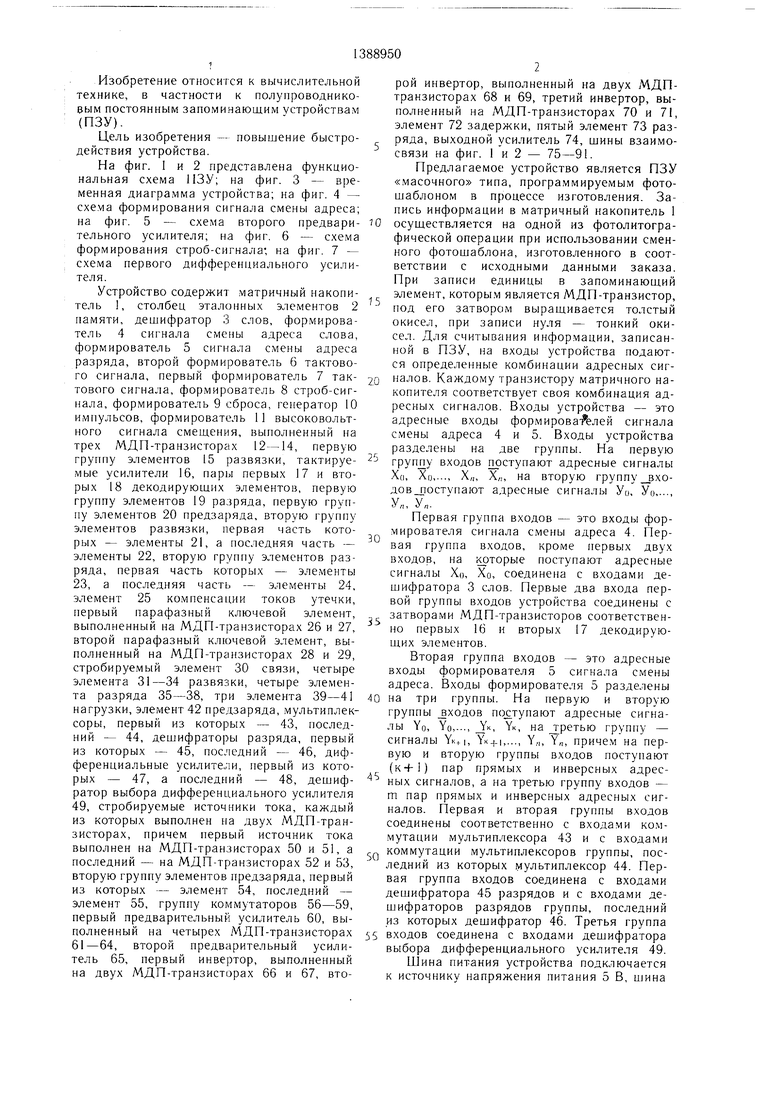

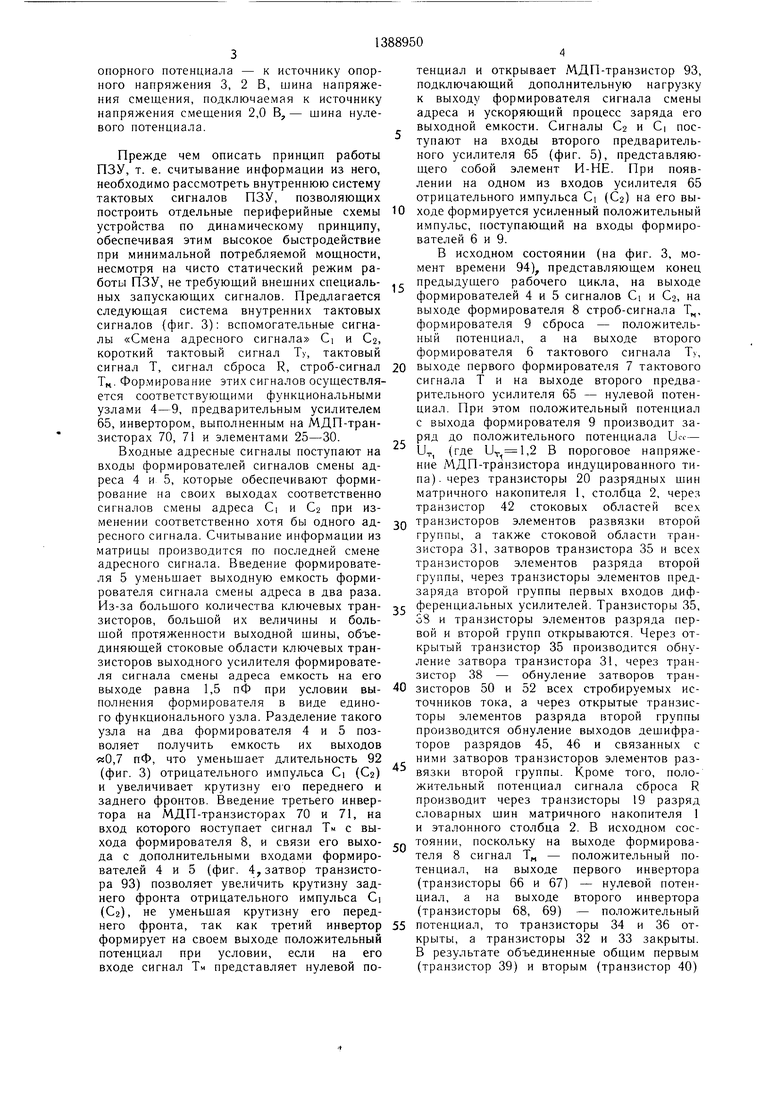

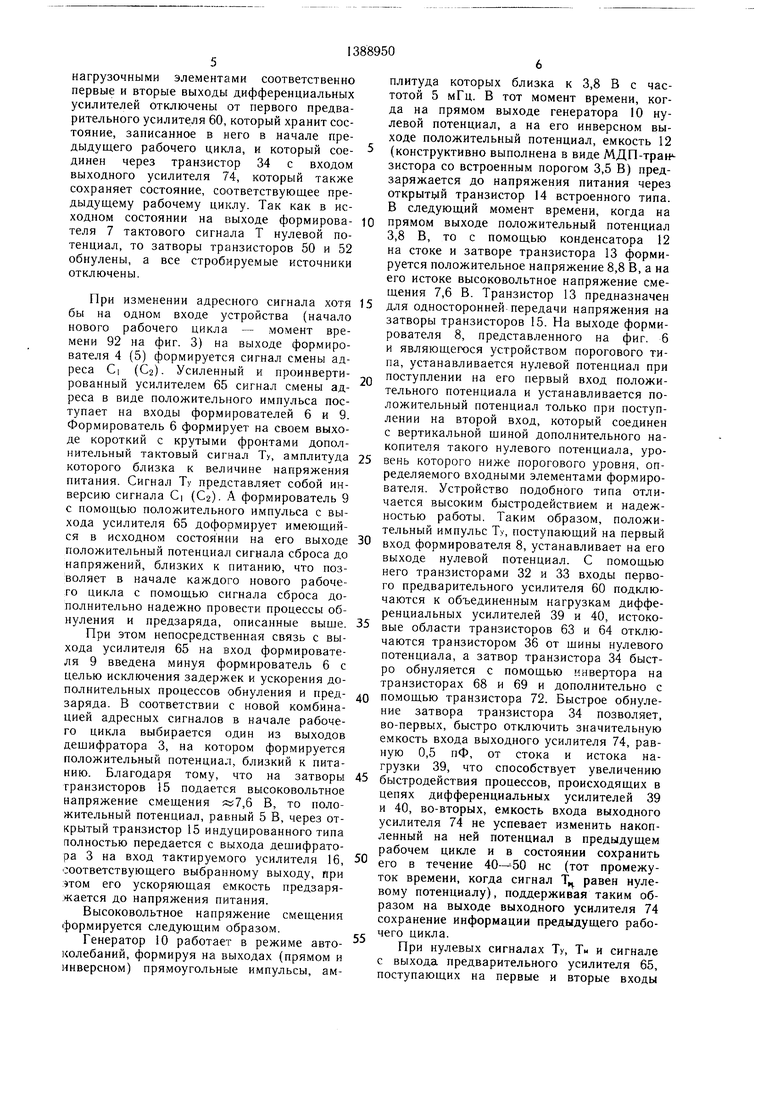

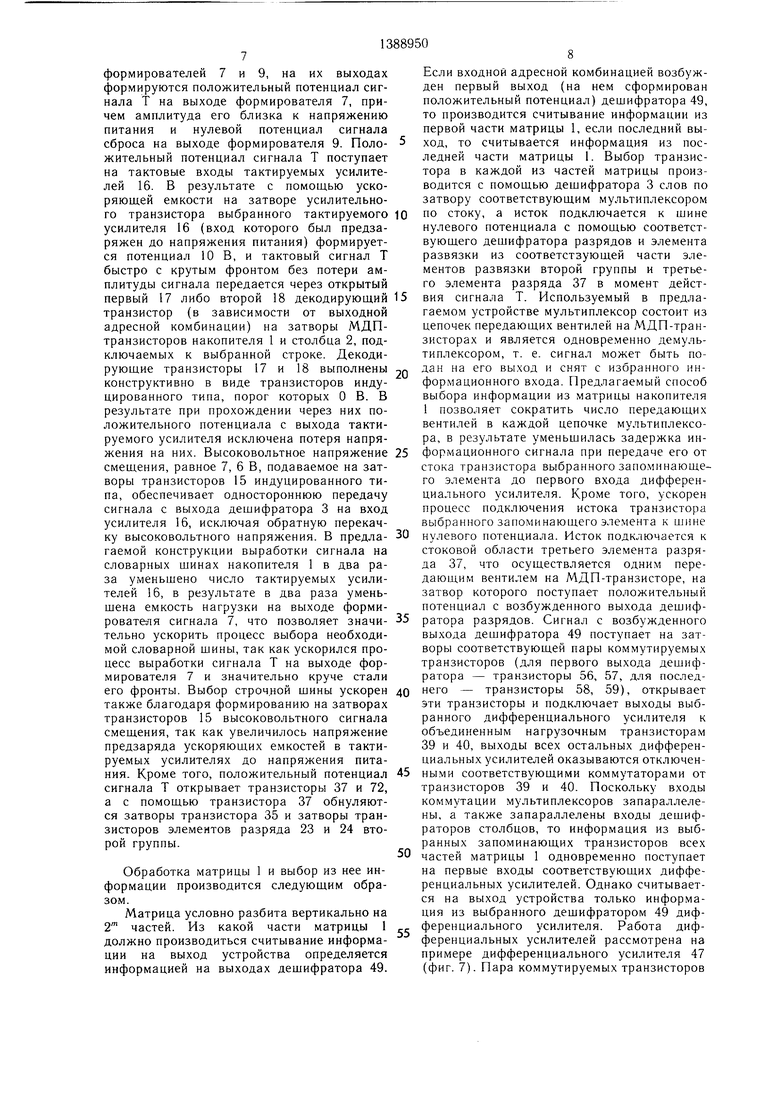

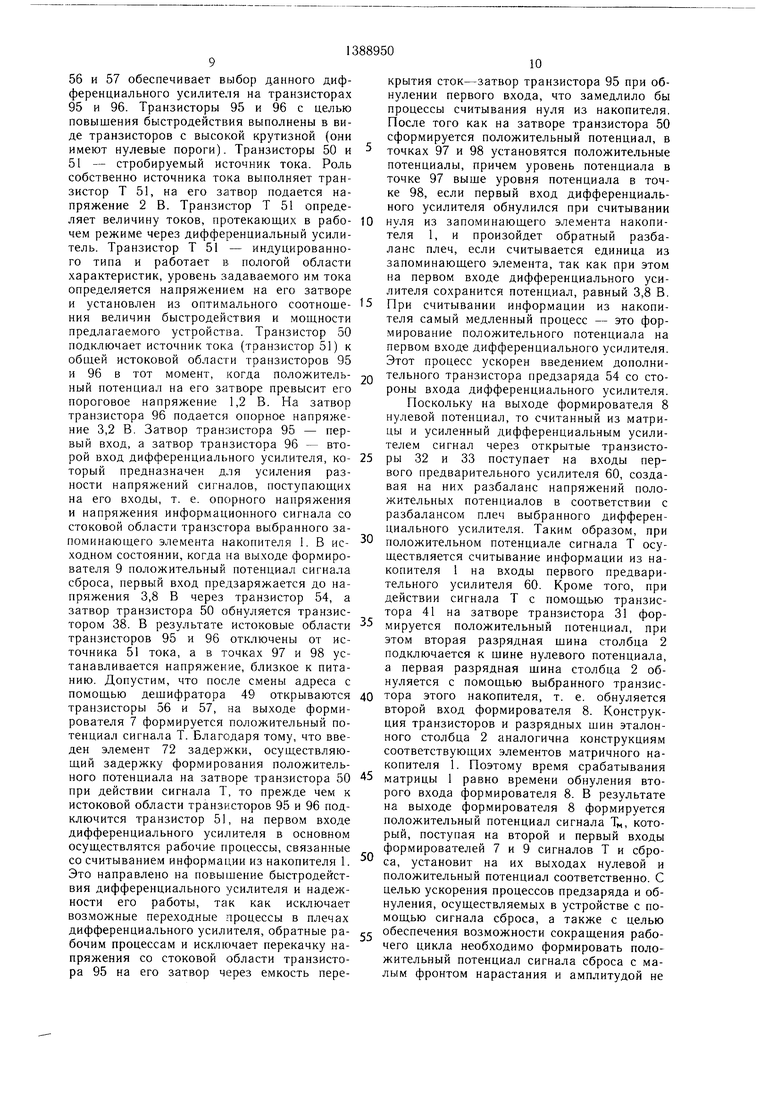

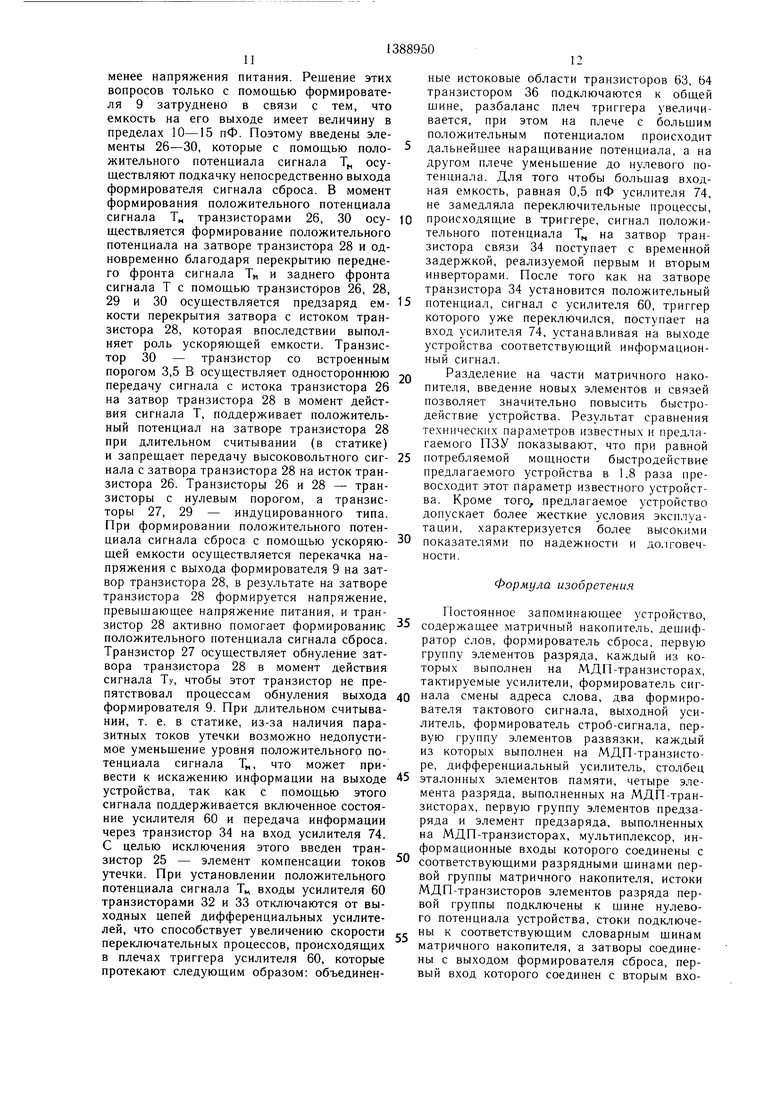

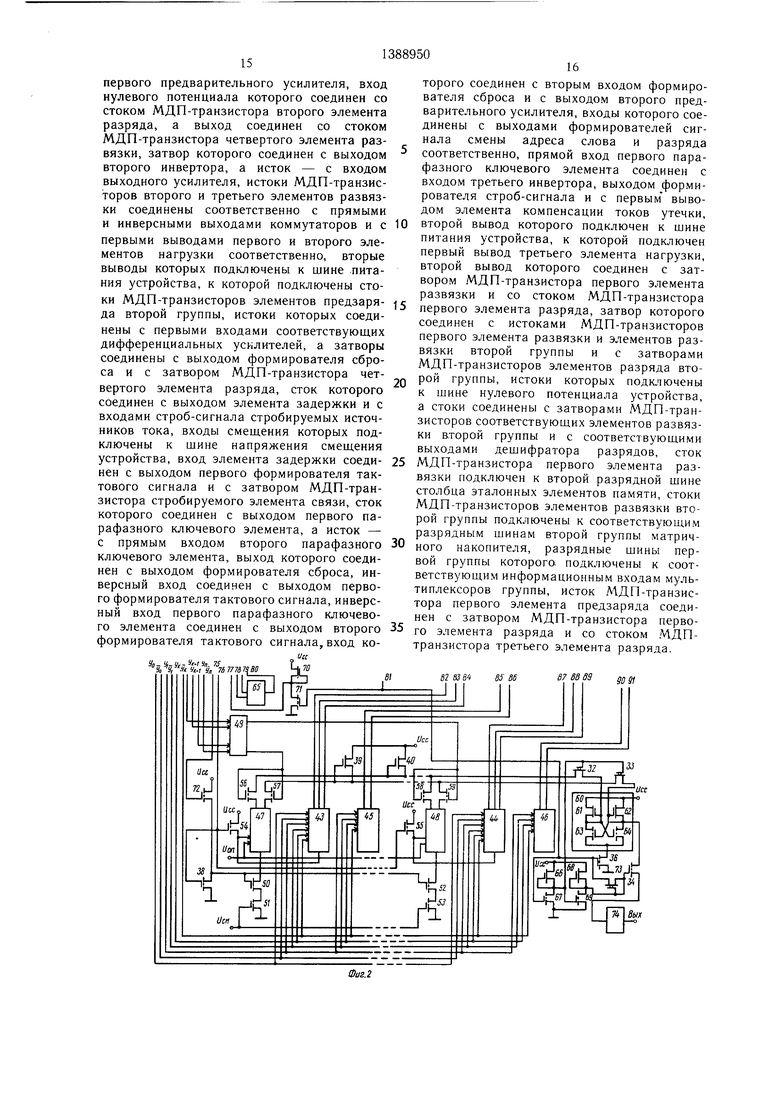

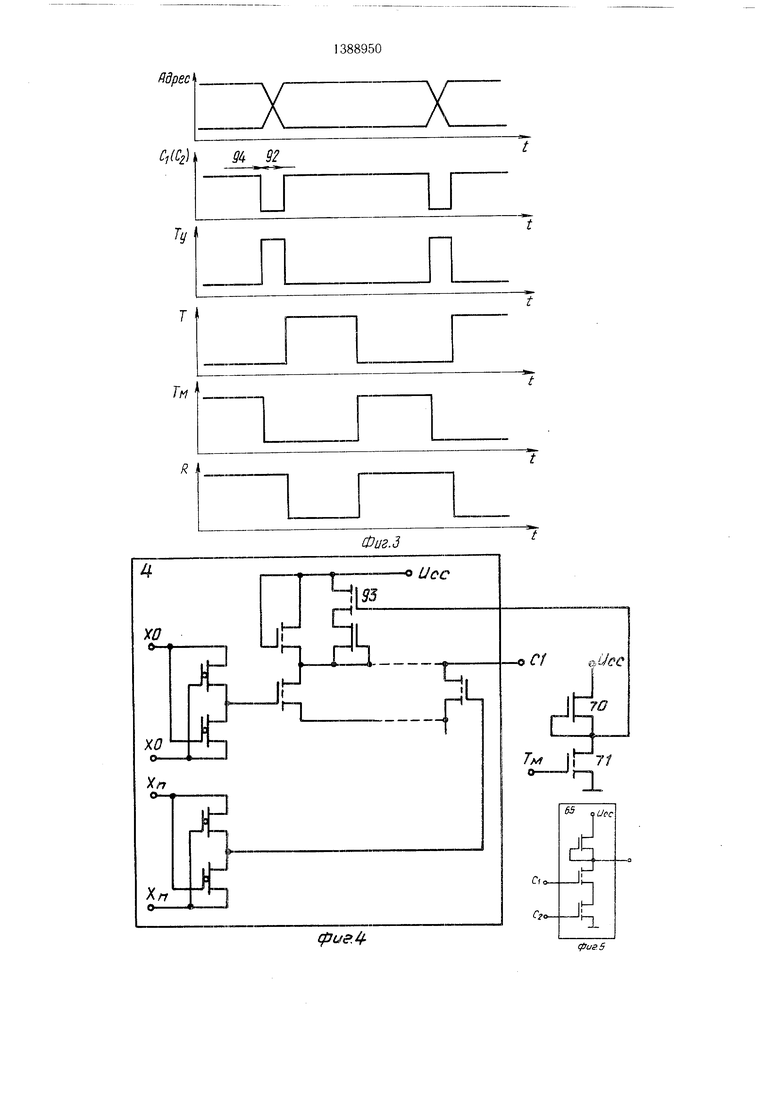

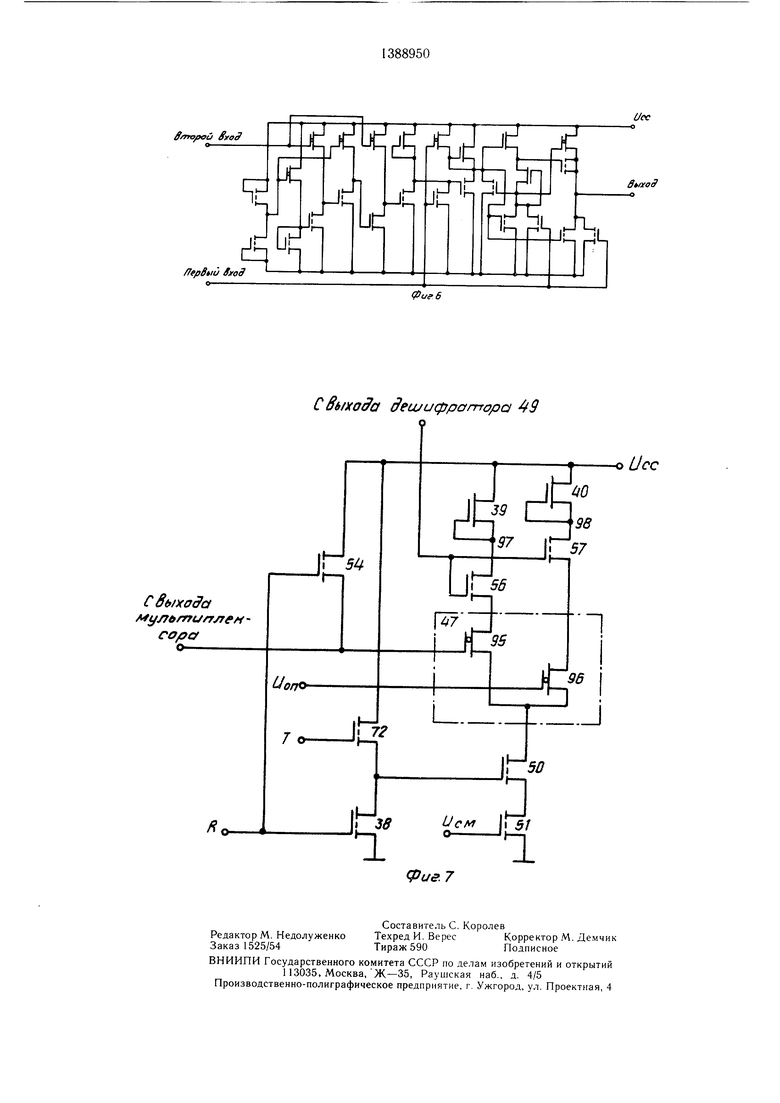

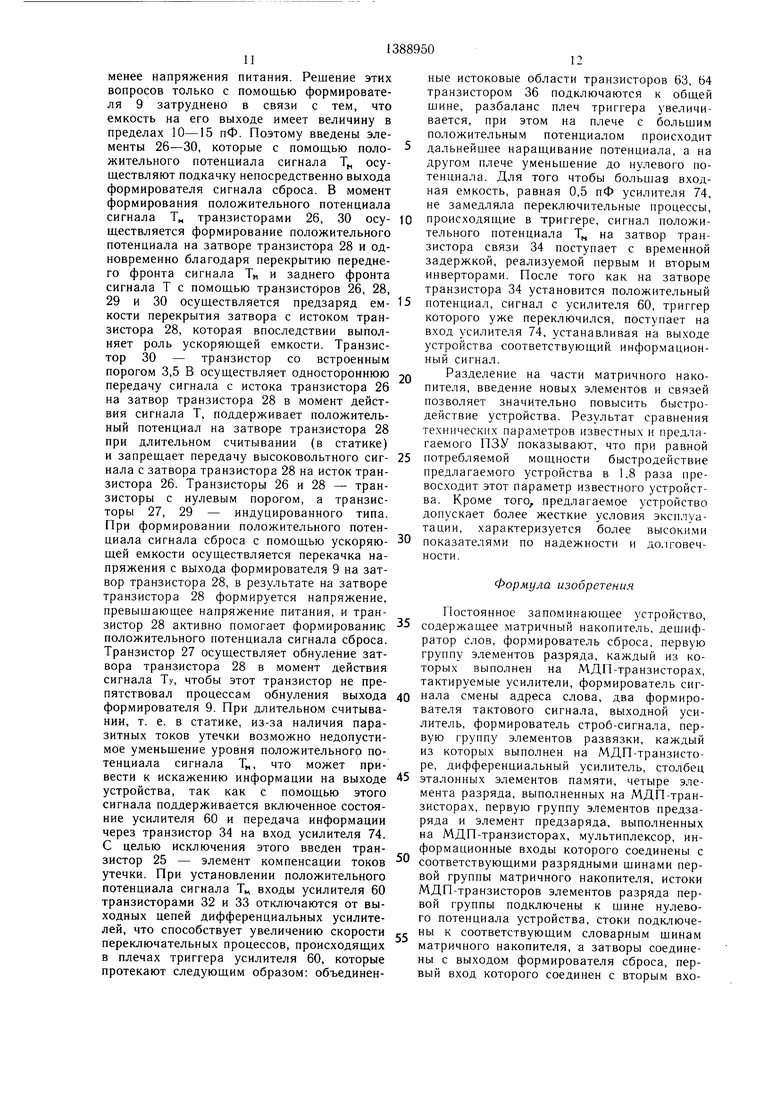

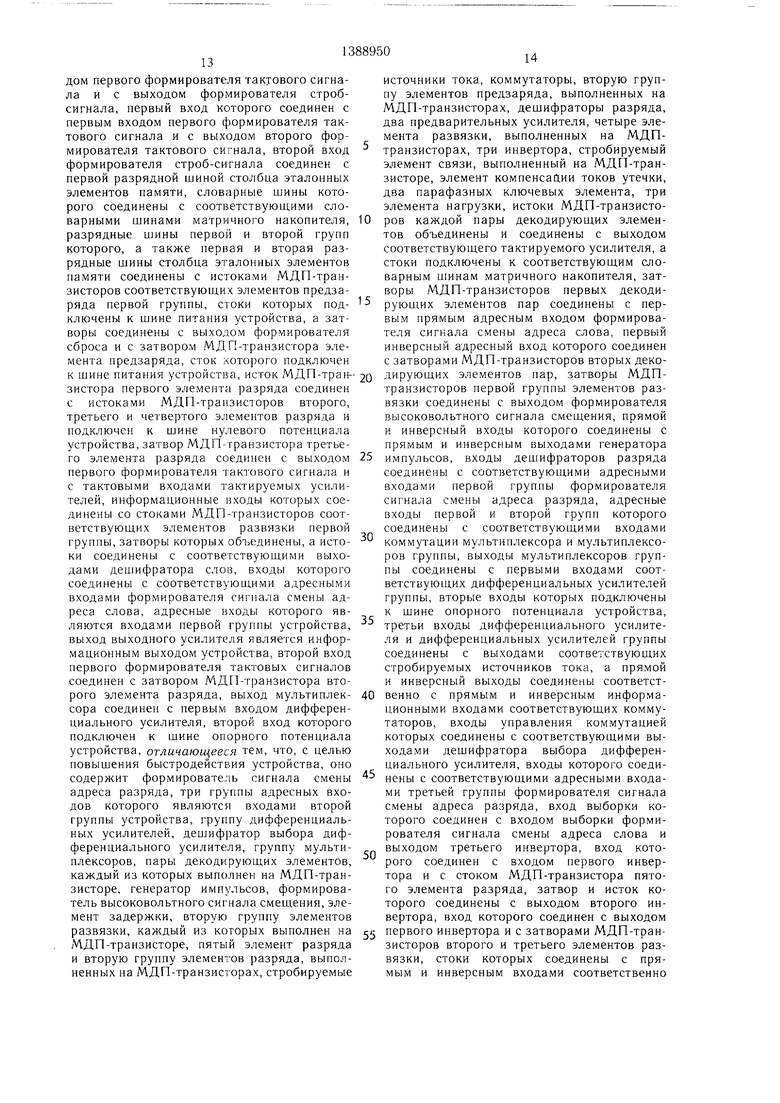

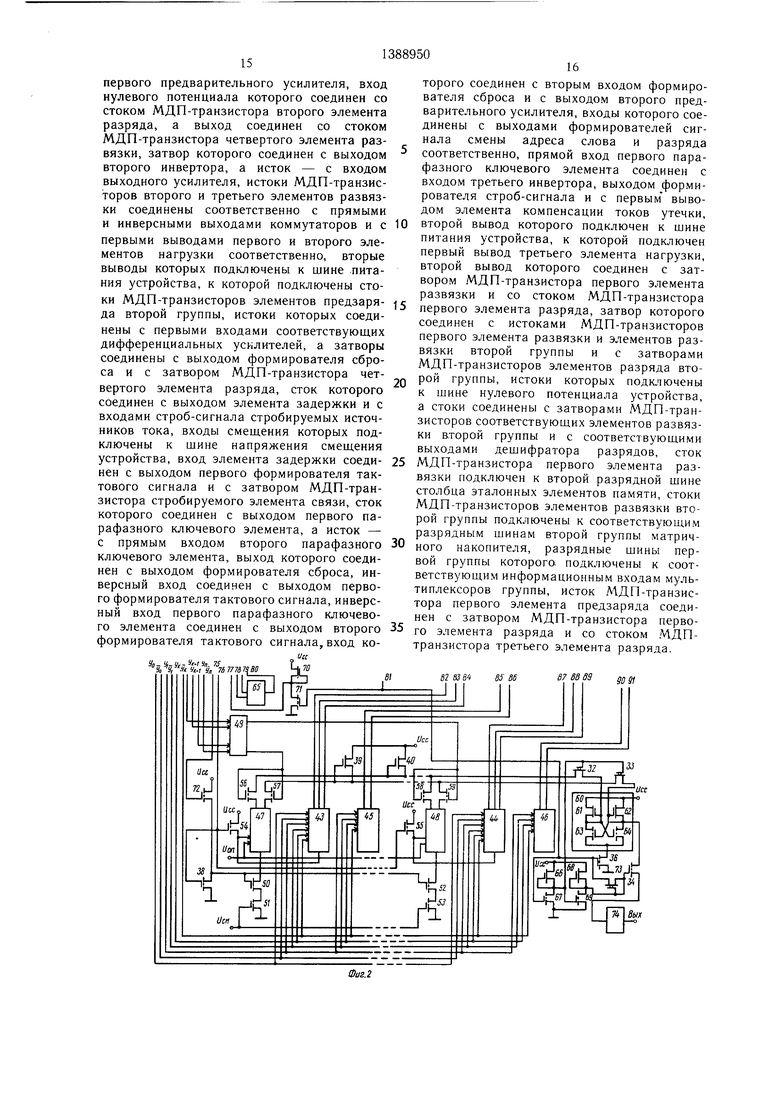

На фиг. 1 и 2 представлена функциональная схема ПЗУ; на фиг. 3 - временная диаграмма устройства; на фиг. 4 - схема формирования сигнала смены адреса; на фиг. 5 - схема второго предвари- тельного усилителя; на фиг. 6 - схема формирования строб-сигнала; на фиг. 7 - схема первого дифференциального усилителя.

Устройство содержит матричный накопитель 1, столбец эталонных элементов 2 памяти, дешифратор 3 слов, формирователь 4 сигнала смены адреса слова, формирователь 5 сигнала смены адреса разряда, второй формирователь 6 тактового сигнала, первый формирователь 7 тактового сигнала, формирователь 8 строб-сигнала, формирователь 9 сброса, генератор 10 импульсов, формирователь 11 высоковольтного сигнала смещения, выполненный на трех МДП-транзисторах 12-14, первую группу элементов 15 развязки, тактируемые усилители 16, пары первых 17 и вторых 18 декодирующих элементов, первую группу элементов 19 разряда, первую группу элементов 20 предзаряда, вторую группу элементов развязки, первая часть которых - элементы 21, а последняя часть - элементы 22, вторую группу элементов разряда, первая часть которых - эле.менты 23, а последняя часть - элементы 24, элемент 25 компенсации токов утечки, первый парафазный ключевой элемент, выполненный на МДП-т)анзисторах 26 и 27, второй парафазный ключевой элемент, выполненный на МДП-транзисторах 28 и 29, стробируемый элемент 30 связи, четыре элемента 31-34 развязки, четыре элемента разряда 35-38, три элемента 39-41 нагрузки, элемент 42 предзаряда, мультиплексоры, первый из которых - 43, последний - 44, дешифраторы разряда, первый из которых - 45, последний - 46, дифференциальные усилители, первый из которых - 47, а последний - 48, дешифратор выбора дифференциального усилителя 49, стробируемые источники тока, каждый из которых выполнен на двух МДП-транзисторах, причем первый источник тока выполнен на МДП-транзисторах 50 и 51, а последний - на МДП-транзисторах 52 и 53, вторую группу элементов предзаряда, первый из которых - элемент 54, последний - элемент 55, группу коммутаторов 56-59, первый предварительный усилитель 60, выполненный на четырех МДП-транзисторах 61-64, второй предварительный усилитель 65, первый инвертор, выполненный на двух МДП-транзисторах 66 и 67, вто

5

0 5

0

5

5

0

рой инвертор, вЕ)1полненный на двух МДП- транзисторах 68 и 69, третий инвертор, выполненный на МДП-транзисторах 70 и 71, элемент 72 задержки, пятый элемент 73 разряда, выходной усилитель 74, шины взаимосвязи на фиг. 1 и 2 - 75-91.

Предлагаемое устройство является ПЗУ «масочного типа, программируемым фотошаблоном в процессе изготовления. Запись информации в матричный накопитель 1 осуществляется на одной из фотолитографической операции при использовании сменного фотощаблона, изготовленного в соответствии с исходными данными заказа. При записи единицы в запоминающий элемент, которы.м является МДП-транзистор, под его затвором выращивается толстый окисел, при записи нуля - тонкий окисел. Для считывания информации, записанной в ПЗУ, на входы устройства подаются определенные комбинации адресных сигналов. Каждому транзистору матричного накопителя соответствует своя комбинация адресных сигналов. Входы устройства - это адресные входы формирователей сигнала смены адреса 4 и 5. Входы устройства разделены на две группы. На первую групду входов гтоступают адресные сигналы .X(j, Хо,..., Х„, Х„, на вторую группу вхо- дов поступают адресные сигналы Уо, Уо,..., V V

/I , Cf ППервая группа входов - это входы формирователя сигнала смены адреса 4. Первая группа входов, кроме первых двух входов, на которые поступают адресные сигналы Хо, Хо, соединена с входами дешифратора 3 слов. Первые два входа первой группы входов устройства соединены с затворами МДП-транзисторов соответственно первых 16 и вторых 17 декодирующих элементов.

Вторая группа входов - это адресные входы формирователя 5 сигнала смены адреса. Входы формирователя 5 разделены на три группы. На первую и вторую группы входов поступают адресные сигналы YO, YO,..., к, YK, на третью группу - сигналы YKI-I, YK + I,..., Y,,, Y, причем на первую и вторую группы входов поступают (к+1) пар прямых и инверсных адресных сигналов, а на третью группу входов - m пар прямых и инверсных адресных сигналов. Первая и вторая группы входов соединены соответственно с входами коммутации мультиплексора 43 и с входами коммутации мультиплексоров группы, последний из которых мультиплексор 44. Первая группа входов соединена с входами дешифратора 45 разрядов и с входами дешифраторов разрядов группы, последний из которых дешифратор 46. Третья группа входов соединена с входами дешифратора выбора дифференциального усилителя 49.

Шина питания устройства подключается к источнику напряжения питания 5 В, шина

опорного потенциала - к источнику опорного напряжения 3, 2 В, шина напряжения смещения, подключаемая к источнику напряжения смещения 2,0 В., - щина нулевого потенциала.

Прежде чем описать принцип работы ПЗУ, т. е. считывание информации из него, необходимо рассмотреть внутреннюю систему тактовых сигналов ПЗУ, позволяющих построить отдельные периферийные схемы Ю ходе формируется усиленный положительный устройства по динамическому принципу,импульс, (оступающий на входы формирообеспечивая этим высокое быстродействие при минимальной потребляемой мощности.

тенциал и открывает МДП-транзистор 93, подключающий дополнительную нагрузку к выходу формирователя сигнала смены адреса и ускоряющий процесс заряда его выходной емкости. Сигналы С2 и C| поступают на входы второго предварительного усилителя 65 (фиг. 5), представляющего собой элемент И-НЕ. При появлении на одном из входов усилителя 65 отрицательного импульса Ci (С2) на его вынесмотря на чисто статический режим раследующая система внутренних тактовых сигналов (фиг. 3): вспомогательные сигналы «Смена адресного сигнала Ci и С-2, короткий тактовый сигнал Ту, тактовый

25

вателей 6 и 9.

В исходном состоянии (на фиг. 3, момент времени 94), представляющем конец боты ПЗУ, не требующий внешних специаль- «с предыдущего рабочего цикла, на выходе ных запускающих сигналов. Предлагаетсяформирователей 4 и 5 сигналов Ci и Со, на

выходе формирователя 8 строб-сигнала Т„, формирователя 9 сброса - положительный потенциал, а на выходе второго формирователя 6 тактового сигнала Ту,

сигнал Т, сигнал сброса R, строб-сигнал 20 выходе первого формирователя 7 тактового Тц. Фор.мирование этих сигналов осуществля- сигнала Т и на выходе второго предва- ется соответствующи.ми функциональными узлами 4-9, предварительным усилителем 65, инвертором, выполненным на МДП-тран- зисторах 70, 71 и элементами 25-30.

Входные адресные сигналы поступают на входы формирователей сигналов смены адреса 4 и 5, которые обеспечивают формирование на своих выходах соответственно сигналов смены адреса d и Са при изменении соответственно хотя бы одного ад- зо транзисторов элементов развязки второй ресного сигнала. Считывание информации изгруппы, а также стоковой области транзистора 31, затворов транзистора 35 и всех транзисторов элементов разряда второй группы, через транзисторы элементов пред- заряда второй группы первых входов дифИз-за больщого количества ключевых тран- s ференциальных усилителей. Транзисторы 35, зисторов, большой их величины и боль-38 и транзисторы элементов разряда первой и второй групп открываются. Через открытый транзистор 35 производится обнуление затвора транзистора 31, через транзистор 38 - обнуление затворов транвыходе равна 1,5 пФ при условии вы- 40 зисторов 50 и 52 всех стробируемых исполнения формирователя в виде едино-точников тока, а через открытые транзисторы элементов разряда второй группы производится обнуление выходов дещифра- торОЕ разрядов 45, 46 и связанных с

рительного усилителя 65 - нулевой потенциал. При этом положительный потенциал с выхода формирователя 9 производит заряд до положительного потенциала Ucc- UT, (где ит, 1,2 В пороговое напряжение МДП-транзистора индуцированного типа), через транзисторы 20 разрядных тин матричного накопителя 1, столбца 2, через транзистор 42 стоковых областей всех

матрицы производится по последней смене адресного сигнала. Введение формирователя 5 уменьшает выходную емкость формирователя сигнала смены адреса в два раза.

шой протяженности выходной шины, объединяющей стоковые области ключевых транзисторов выходного усилителя формирователя сигнала смены адреса емкость на его

го функционального узла. Разделение такого узла на два формирователя 4 и 5 позволяет получить емкость их выходов

«0,7 пФ, что уменьшает длительность 92 ними затворов транзисторов элементов раз/ /4ч II .Г ГЛ 11И11ПЛ7ТТ1 1- 0 . IС DOOI. TJП ГГ Г Г ГгГТЧЛ/ПГТ ЛТ-Гм тл е- п Г

(фиг. 3) отрицательного импульса Ci (Сз) и увеличивает крутизну его переднего и заднего фронтов. Введение третьего инвертора на МДП-транзисторах 70 и 71, на вход которого ноступает сигнал Тм с вывязки второй группы. Кроме того, положительный потенциал сигнала сброса R производит через транзисторы 19 разряд словарных щин матричного накопителя 1 и эталонного столбца 2. В исходном сосхода формирователя 8, и связи его выхо-гг. тоянии, поскольку на выходе формировада с дополнительными входами формиро-теля 8 сигнал Т„ - положительный пователей 4 и 5 (фиг. 4,затвор транзисто-тенциал, на выходе первого инвертора

ра 93) позволяет увеличить крутизну зад-(транзисторы 66 и 67) - нулевой потеннего фронта отрицательного импульса Ciциал, а на выходе второго инвертора

(С2), не уменьшая крутизну его перед-(транзисторы 68, 69) - положительный

него фронта, так как третий инвертор55 потенциал, то транзисторы 34 и 36 отформирует на своем выходе положительныйкрыты, а транзисторы 32 и 33 закрыты,

потенциал при условии, если на егоВ результате объединенные общим первым

входе сигнал Тм представляет нулевой по-(транзистор 39) и вторым (транзистор 40)

ходе формируется усиленный положительный импульс, (оступающий на входы формиротенциал и открывает МДП-транзистор 93, подключающий дополнительную нагрузку к выходу формирователя сигнала смены адреса и ускоряющий процесс заряда его выходной емкости. Сигналы С2 и C| поступают на входы второго предварительного усилителя 65 (фиг. 5), представляющего собой элемент И-НЕ. При появлении на одном из входов усилителя 65 отрицательного импульса Ci (С2) на его вы

выходе первого формирователя 7 тактового сигнала Т и на выходе второго предва-

транзисторов элементов развязки второй группы, а также стоковой области транрительного усилителя 65 - нулевой потенциал. При этом положительный потенциал с выхода формирователя 9 производит заряд до положительного потенциала Ucc- UT, (где ит, 1,2 В пороговое напряжение МДП-транзистора индуцированного типа), через транзисторы 20 разрядных тин матричного накопителя 1, столбца 2, через транзистор 42 стоковых областей всех

ними затворов транзисторов элементов раз DOOI. TJП ГГ Г Г ГгГТЧЛ/ПГТ ЛТ-Гм тл е- п Г

вязки второй группы. Кроме того, положительный потенциал сигнала сброса R производит через транзисторы 19 разряд словарных щин матричного накопителя 1 и эталонного столбца 2. В исходном соснагрузочными элементами соответственно первые и вторые выходы дифференциальных усилителей отключены от первого предварительного усилителя 60, который хранит состояние, записанное в него в начале предыдущего рабочего цик,па, и который соединен через транзистор 34 с входом выходного усилителя 74, который также сохраняет состояние, соответствующее предыдущему рабочему циклу. Так как в исплитуда которых близка к 3,8 В с частотой 5 мГц. В тот момент времени, когда на прямом выходе генератора 10 нулевой потенциал, а на его инверсном выходе положительный потенциал, емкость 12 (конструктивно выполнена в виде МДП-тра№ зистора со встроенным порогом 3,5 В) пред- заряжается до напряжения питания через открыт1 1Й транзистор 14 встроенного типа. В следующий момент времени, когда на

ходном состоянии на выходе формирова- Ю прямом выходе положительный потенциал теля 7 тактового сигнала Т нулевой по- 3,8 В, то с помощью конденсатора 12 тенциал, то затворы транзисторов 50 и 52на стоке и затворе транзистора 13 формиобнулены, а все стробируемые источникируется положительное напряжение 8,8 В, а на

отключены.его истоке высоковольтное напряжение смещения 7,6 В. Транзистор 13 предназначен

При изменении адресного сигнала хотя 15 для односторонней передачи напряжения на бы на одном входе устройства (начало нового рабочего цикла - момент времени 92 на фиг. 3) на выходе формирователя 4 (5) формируется сигнал смены адреса С| (С2). Усиленный и проинверти- рованный усилителем 65 сигнал смены адреса в виде положительного импульса поступает на входы формирователей 6 и 9. Формирователь 6 формирует на своем выходе короткий с крутыми фронтами доползатворы транзисторов 15. На выходе формирователя 8, представленного на фиг. 6 и являющегося устройством порогового типа, устанавливается нулевой потенциал при поступлении на его первый вход положительного потенциала и устанавливается положительный потенциал только при поступлении на второй вход, который соединен с вертикальной щиной дополнительного накопителя такого нулевого потенциала, уронительный тактовый сигнал Ту, амплитуда 25 вень которого ниже порогового уровня, опкоторого близка к величине напряжения питания. Сигнал Ту представляет собой инверсию сигнала С: (€2). А формирователь 9 с помощью положительного импульса с выхода усилителя 65 доформирует имеющийределяемого входными элементами формирователя. Устройство подобного типа отличается высоким быстродействием и надежностью работы. Таким образом, положительный импульс Ту, поступающий на первый

ся в исходном состоянии на его выходе 30 вход формирователя 8, устанавливает на его

положительный потенциал сигнала сброса до напряжений, близких к питанию, что позволяет в начале каждого нового рабочего цикла с помощью сигнала сброса дополнительно надежно провести процессы обвыходе нулевой потенциал. С помощью него транзисторами 32 и 33 входы первого предварительного усилителя 60 подключаются к объединенным нагрузкам дифференциальных усилителей 39 и 40, истоко40

нуления и предзаряда, описанные выще. 35 вые области транзисторов 63 и 64 отклю- При этом непосредственная связь с вы-чаются транзистором 36 от шины нулевого

хода усилителя 65 на вход формирователя 9 введена минуя формирователь 6 с целью исключения задерж;ек и ускорения дополнительных процессов обнуления и пред- заряда. В соответствии с новой комбинацией адресных сигналов в начале рабочего цикла выбирается один из выходов дещифратора 3, на котором формируется положительный потенциал, близкий к питанию. Благодаря тому, что на затворы 45 быстродействия процессов, происходящих в транзисторов 15 подается высоковольтное цепях дифференциальных усилителей 39 напряжение смещения «7,6 В, то положительный потенциал, равный 5 В, через открытый транзистор 15 индуцированного типа полностью передается с выхода дещифратора 3 на вход тактируемого усилителя 16, соответствующего выбранному выходу, при этом его ускоряющая емкость предзаряпотенциала, а затвор транзистора 34 быстро обнуляется с помощью инвертора на транзисторах 68 и 69 и дополнительно с помощью транзистора 72. Быстрое обнуление затвора транзистора 34 позволяет, во-первых, быстро отключить значительную емкость входа выходного усилителя 74, равную 0,5 пФ, от стока и истока нагрузки 39, что способствует увеличению

50

и 40, во-вторых, емкость входа выходного усилителя 74 не успевает изменить накопленный на ней потенциал в предыдущем рабочем цикле и в состоянии сохранить его в течение 40--50 не (тот промежуток времени, когда сигнал Т равен нулевому потенциалу), поддерживая таким образом на выходе выходного усилителя 74 сохранение информации предыдущего рабочего цикла.

жается до напряжения питания.

Высоковольтное напряжение смещения формируется следующим образом.

Генератор 10 работает в режиме авто- колебаний, формируя на выходах (прямом и инверсном) прямоугольные импульсы, амплитуда которых близка к 3,8 В с частотой 5 мГц. В тот момент времени, когда на прямом выходе генератора 10 нулевой потенциал, а на его инверсном выходе положительный потенциал, емкость 12 (конструктивно выполнена в виде МДП-тра№- зистора со встроенным порогом 3,5 В) пред- заряжается до напряжения питания через открыт1 1Й транзистор 14 встроенного типа. В следующий момент времени, когда на

для односторонней передачи напряжения на

затворы транзисторов 15. На выходе формирователя 8, представленного на фиг. 6 и являющегося устройством порогового типа, устанавливается нулевой потенциал при поступлении на его первый вход положительного потенциала и устанавливается положительный потенциал только при поступлении на второй вход, который соединен с вертикальной щиной дополнительного накопителя такого нулевого потенциала, уровень которого ниже порогового уровня, опвень которого ниже порогового уровня, определяемого входными элементами формирователя. Устройство подобного типа отличается высоким быстродействием и надежностью работы. Таким образом, положительный импульс Ту, поступающий на первый

вход формирователя 8, устанавливает на его

вход формирователя 8, устанавливает на его

выходе нулевой потенциал. С помощью него транзисторами 32 и 33 входы первого предварительного усилителя 60 подключаются к объединенным нагрузкам дифференциальных усилителей 39 и 40, истоковые области транзисторов 63 и 64 отклю- чаются транзистором 36 от шины нулевого

вые области транзисторов 63 и 64 отклю- чаются транзистором 36 от шины нулевого

быстродействия процессов, происходящих в цепях дифференциальных усилителей 39

потенциала, а затвор транзистора 34 быстро обнуляется с помощью инвертора на транзисторах 68 и 69 и дополнительно с помощью транзистора 72. Быстрое обнуление затвора транзистора 34 позволяет, во-первых, быстро отключить значительную емкость входа выходного усилителя 74, равную 0,5 пФ, от стока и истока нагрузки 39, что способствует увеличению

быстродействия процессов, происходящих в цепях дифференциальных усилителей 39

и 40, во-вторых, емкость входа выходного усилителя 74 не успевает изменить накопленный на ней потенциал в предыдущем рабочем цикле и в состоянии сохранить его в течение 40--50 не (тот промежуток времени, когда сигнал Т равен нулевому потенциалу), поддерживая таким образом на выходе выходного усилителя 74 сохранение информации предыдущего рабочего цикла.

При нулевых сигналах Ту, Тм и сигнале с выхода предварительного усилителя 65, поступающих на первые и вторые входы

формирователей 7 и 9, на их выходах формируются положительный потенциал сигнала Т на выходе формирователя 7, причем амплитуда его близка к напряжению питания и нулевой потенциал сигнала сброса на выходе формирователя 9. Поло- жительный потенциал сигнала Т поступает на тактовые входы тактируемых усилителей 16. В результате с помощью ускоряющей емкости на затворе усилительного транзистора выбранного тактируемого усилителя 16 (вход которого был предза- ряжен до напряжения питания) формируется потенциал 10 В, и тактовый сигнал Т быстро с крутым фронтом без потери амплитуды сигнала передается через открытый первый 17 либо второй 18 декодирующий транзистор (в зависимости от выходной адресной комбинации) на затворы МДП- транзисторов накопителя 1 и столбца 2, подключаемых к выбранной строке. Декодирующие транзисторы 17 и 18 выполнены конструктивно в виде транзисторов индуцированного типа, порог которых О В. В результате при прохождении через них положительного потенциала с выхода тактируемого усилителя исключена потеря напряжения на них. Высоковольтное напряжение смещения, равное 7, 6 В, подаваемое на затворы транзисторов 15 индуцированного типа, обеспечивает одностороннюю передачу сигнала с выхода дешифратора 3 на вход усилителя 16, исключая обратную перекачку высоковольтного напряжения. В предла- гаемой конструкции выработки сигнала на словарных щинах накопителя 1 в два раза уменьшено число тактируемых усилителей 16, в результате в два раза уменьшена емкость нагрузки на выходе формирователя сигнала 7, что позволяет значи- тельно ускорить процесс выбора необходимой словарной шины, так как ускорился процесс выработки сигнала Т на выходе формирователя 7 и значительно круче стали его фронты. Выбор строчной шины ускорен также благодаря формированию на затворах транзисторов 15 высоковольтного сигнала смещения, так как увеличилось напряжение предзаряда ускоряющих емкостей в тактируемых усилителях до напряжения питания. Кроме того, положительный потенциал сигнала Т открывает транзисторы 37 и 72, а с помощью транзистора 37 обнуляются затворы транзистора 35 и затворы транзисторов элементов разряда 23 и 24 второй группы.

Обработка матрицы 1 и выбор из нее информации производится следующим образом.

Матрица условно разбита вертикально на 2™ частей. Из какой части матрицы 1 должно производиться считывание информации на выход устройства определяется информацией на выходах дешифратора 49.

Если входной адресной комбинацией возбужден первый выход (на нем сформирован положительный потенциал) дешифратора 49, то производится считывание информации из первой части матрицы 1, если последний выход, то считывается информация из последней части матрицы 1. Выбор транзистора в каждой из частей матрицы производится с помощью дещифратора 3 слов по затвору соответствующим мультиплексором по стоку, а исток подключается к шине нулевого потенциала с помощью соответствующего дещифратора разрядов и элемента развязки из соответствующей части элементов развязки второй группы и третьего элемента разряда 37 в момент действия сигнала Т. Используемый в предлагаемом устройстве мультиплексор состоит из цепочек передающих вентилей на МДП-тран- зисторах и является одновременно демуль- типлексором, т. е. сигнал может быть подан на его выход и снят с избранного информационного входа. Предлагаемый способ выбора информации из матрицы накопителя 1 позволяет сократить число передающих вентилей в каждой цепочке мультиплексора, в результате уменьшилась задержка информационного сигнала при передаче его от стока транзистора выбранного запоминающего элемента до первого входа дифференциального усилителя. Кроме того, ускорен процесс подключения истока транзистора выбранного запоминающего элемента к шине нулевого потенциала. Исток подключается к стоковой области третьего элемента разряда 37, что осуществляется одним передающим вентилем на МДП-транзисторе, на затвор которого поступает положительный потенциал с возбужденного выхода дешифратора разрядов. Сигнал с возбужденного выхода дещифратора 49 поступает на затворы соответствующей пары коммутируемых транзисторов (для первого выхода дешифратора - транзисторы 56, 57, для последнего - транзисторы 58, 59), открывает эти транзисторы и подключает выходы выбранного дифференциального усилителя к объединенным нагрузочным транзисторам 39 и 40, выходы всех остальных дифференциальных усилителей оказываются отключенными соответствующими коммутаторами от транзисторов 39 и 40. Поскольку входы коммутации мультиплексоров запараллеле- ны, а также запараллелены входы дешифраторов столбцов, то информация из выбранных запоминающих транзисторов всех частей матрицы 1 одновременно поступает на первые входы соответствующих дифференциальных усилителей. Однако считывается на выход устройства только информация из выбранного дешифратором 49 дифференциального усилителя. Работа дифференциальных усилителей рассмотрена на примере дифференциального усилителя 47 (фиг. 7). Пара коммутируемых транзисторов

56 и 57 обеспечивает выбор данного дифференциального усилителя на транзисторах 95 и 96. Транзисторы 95 и 96 с целью повышения быстродействия выполнены в виде транзисторов с высокой крутизной (они имеют нулевые пороги). Транзисторы 50 и 51 - стробируемый источник тока. Роль собственно источника тока выполняет транзистор Т 51, на его затвор подается напряжение 2 В. Транзистор Т 51 опредекрытия сток-затвор транзистора 95 при обнулении первого входа, что замедлило бы процессы считывания нуля из накопителя. После того как на затворе транзистора 50 сформируется положительный потенциал, в точках 97 и 98 установятся положительные потенциалы, причем уровень потенциала в точке 97 выше уровня потенциала в точке 98, если первый вход дифференциального усилителя обнулился при считывании

ляет величину токов, протекаюших в рабо- 10 нуля из запоминающего элемента накопичем режиме через дифференциальный усилитель. Транзистор Т 51 - индуцированного типа и работает в пологой области характеристик, уровень задаваемого им тока определяется напряжением на его затворе

теля 1, и произойдет обратный разбаланс плеч, если считывается единица из запоминающего элемента, так как при этом на первом входе дифференциального усилителя сохранится потенциал, равный 3,8 В.

установлен из оптимального соотноше- 15 При считывании информации из накопиния величин быстродействия и мощности предлагаемого устройства. Транзистор 50 подключает источник тока (транзистор 51) к общей истоковой области транзисторов 95 и 96 в тот момент, когда положительный потенциал на его затворе превысит его пороговое напряжение 1,2 В. На затвор транзистора 96 подается опорное напряжение 3,2 В. Затвор транзистора 95 - первый вход, а затвор транзистора 96 - втотеля самый медленный процесс - это формирование положительного потенциала на первом входе дифференциального усилителя. Этот процесс ускорен введением дополни- 2Q тельного транзистора предзаряда 54 со стороны входа дифференциального усилителя. Поскольку на выходе формирователя 8 нулевой потенциал, то считанный из матрицы и усиленный дифференциальным усилителем сигнал через открытые транзисторой вход дифференциального усилителя, ко- 25 ры 32 и 33 поступает на входы первого предварительного усилителя 60, создавая на них разбаланс напряжений положительных потенциалов в соответствии с разбалансом плеч выбранного дифференциального усилителя. Таким образом, при

торыи предназначен д.ля усиления разности напряжений сигналов, поступающих на его входы, т. е. опорного напряжения и напряжения информационного сигнала со стоковой области транзстора выбранного запоминающего элемента накопителя 1. В исходном состоянии, когда на выходе формирователя 9 положительный потенциал сигнала сброса, первый вход предзаряжается до напряжения 3,8 В через транзистор 54, а затвор транзистора 50 обнуляется транзистором 38. В результате истоковые области транзисторов 95 и 96 отключены от источника 51 тока, а в точках 97 и 98 устанавливается напряжение, близкое к питанию. Допустим, что после смены адреса с

вого предварительного усилителя 60, создавая на них разбаланс напряжений положительных потенциалов в соответствии с разбалансом плеч выбранного дифференциального усилителя. Таким образом, при

30 положительном потенциале сигнала Т осуществляется считывание информации из накопителя 1 на входы первого предварительного усилителя 60. Кроме того, при действии сигнала Т с помощью транзистора 41 на затворе транзистора 31 фор мируется положительный потенциал, при этом вторая разрядная щина столбца 2 подключается к шине нулевого потенциала, а первая разрядная шина столбца 2 обнуляется с помощью выбранного транзиспомощью дещифратора 49 открываются дО тора этого накопителя, т. е. обнуляется транзисторы 56 и 57, на выходе форми-второй вход формирователя 8. Конструкрователя 7 формируется положительный по-ция транзисторов и разрядных шин эталонтенциал сигнала Т. Благодаря тому, что вве- ного столбца 2 аналогична конструкциям ден элемент 72 задержки, осуществляю- соответствующих элементов матричного на- щий задержку формирования положитель- копителя 1. Поэтому время срабатывания ного потенциала на затворе транзистора 50 45 матрицы 1 равно времени обнуления вто- при действии сигнала Т, то прежде чем к истоковой области транзисторов 95 и 96 подключится транзистор 51, на первом входе дифференциального усилителя в основном осуществлятся рабочие процессы, связанные со считыванием информации из накопителя 1. Это направлено на повышение быстродействия дифференциального усилителя и надежности его работы, так как исключает возможные переходные процессы в плечах дифференциального усилителя, обратные ра- с обеспечения возможности сокращения рабо- бочим процессам и исключает перекачку на- чего цикла необходимо формировать поло- пряжения со стоковой области транзисто- жительный потенциал сигнала сброса с ма- ра 95 на его затвор через емкость пере- лым фронтом нарастания и амплитудой не

50

рого входа формирователя 8. В результате на выходе формирователя 8 формируется положительный потенциал сигнала Т„, который, поступая на второй и первый входы формирователей 7 и 9 сигналов Т и сброса, установит на их выходах нулевой и положительный потенциал соответственно. С целью ускорения процессов предзаряда и обнуления, осуществляемых в устройстве с помощью сигнала сброса, а также с целью

крытия сток-затвор транзистора 95 при обнулении первого входа, что замедлило бы процессы считывания нуля из накопителя. После того как на затворе транзистора 50 сформируется положительный потенциал, в точках 97 и 98 установятся положительные потенциалы, причем уровень потенциала в точке 97 выше уровня потенциала в точке 98, если первый вход дифференциального усилителя обнулился при считывании

нуля из запоминающего элемента накопителя 1, и произойдет обратный разбаланс плеч, если считывается единица из запоминающего элемента, так как при этом на первом входе дифференциального усилителя сохранится потенциал, равный 3,8 В.

При считывании информации из накопителя самый медленный процесс - это формирование положительного потенциала на первом входе дифференциального усилителя. Этот процесс ускорен введением дополни- тельного транзистора предзаряда 54 со стороны входа дифференциального усилителя. Поскольку на выходе формирователя 8 нулевой потенциал, то считанный из матрицы и усиленный дифференциальным усилителем сигнал через открытые транзисторы 32 и 33 поступает на входы перры 32 и 33 поступает на входы первого предварительного усилителя 60, создавая на них разбаланс напряжений положительных потенциалов в соответствии с разбалансом плеч выбранного дифференциального усилителя. Таким образом, при

положительном потенциале сигнала Т осуществляется считывание информации из накопителя 1 на входы первого предварительного усилителя 60. Кроме того, при действии сигнала Т с помощью транзистора 41 на затворе транзистора 31 формируется положительный потенциал, при этом вторая разрядная щина столбца 2 подключается к шине нулевого потенциала, а первая разрядная шина столбца 2 обнуляется с помощью выбранного транзисного столбца 2 аналогична конструкциям соответствующих элементов матричного на- копителя 1. Поэтому время срабатывания матрицы 1 равно времени обнуления вто- обеспечения возможности сокращения рабо- чего цикла необходимо формировать поло- жительный потенциал сигнала сброса с ма- лым фронтом нарастания и амплитудой не

рого входа формирователя 8. В результате на выходе формирователя 8 формируется положительный потенциал сигнала Т„, который, поступая на второй и первый входы формирователей 7 и 9 сигналов Т и сброса, установит на их выходах нулевой и положительный потенциал соответственно. С целью ускорения процессов предзаряда и обнуления, осуществляемых в устройстве с помощью сигнала сброса, а также с целью

менее напряжения питания. Решение этих вопросов только с помощью формирователя 9 затруднено в связи с тем, что емкость на его выходе имеет величину в пределах 10-15 пФ. Поэтому введены элементы 26-30, которые с помощью поло- жительного потенциала сигнала Т„ осуществляют подкачку непосредственно выхода формирователя сигнала сброса. В момент формирования положительного потенциала

ные истоковые области транзисторов 63, 64 транзистором 36 подключаются к общей шине, разбаланс плеч триггера увеличивается, при этом на плече с большим положительным потенциалом происходит дальнейшее наращивание потенциала, а на другом плече уменьшение до нулевого потенциала. Для того чтобы больщаа входная емкость, равная 0,5 пФ усилителя 74, не замедляла переключительные процессы,

сигнала Т„ транзисторами 26, 30 осу- Ю происходящие в триггере, сигнал положи- ществляется формирование положительноготельного потенциала Т„ на затвор транпотенциала на затворе транзистора 28 и од-зистора связи 34 поступает с временной

новременно благодаря перекрытию передне-задержкой, реализуемой первым и вторым

го фронта сигнала Т„ и заднего фронтаинверторами. После того как на затворе

сигнала Т с помощью транзисторов 26, 28,транзистора 34 установится положительный

29 и 30 осуществляется предзаряд ем- 15 потенциал, сигнал с усилителя 60, триггер кости перекрытия затвора с истоком транзистора 28, которая впоследствии выполняет роль ускоряющей емкости. Транзистор 30 - транзистор со встроенным порогом 3,5 В осуществляет одностороннюю 2о передачу сигнала с истока транзистора 26 на затвор транзистора 28 в момент действия сигнала Т, поддерживает положительный потенциал на затворе транзистора 28 при длительном считывании (в статике)

и запрещает передачу высоковольтного сиг- 25 потребляемой мощности быстродействие нала с затвора транзистора 28 на исток тран-предлагаемого устройства в 1,8 раза презистора 26. Транзисторы 26 и 28 - транзисторы с нулевым порогом, а транзисторы 27, 29 - индуцированного типа. При формировании положительного потенциала сигнала сброса с помощью ускоряю- 30 показателями по надежности и долговеч- щей емкости осуществляется перекачка на-ности.

пряжения с выхода формирователя 9 на затвор транзистора 28, в результате на затворе транзистора 28 формируется напряжение, превышающее напряжение питания, и транзистор 28 активно помогает формированию положительного потенциала сигнала сброса. Транзистор 27 осуществляет обнуление затвора транзистора 28 в момент действия сигнала Ту, чтобы этот транзистор не препятствовал процессам обнуления выхода 40 нала смены адреса слова, два формиро- формирователя 9. При длительном считыва- вателя тактового сигнала, выходной уси- нии, т. е. в статике, из-за наличия пара- литель, формирователь строб-сигнала, пер- зитных токов утечки возможно недопусти-вую группу элементов развязки, каждый

мое уменьщение уровня положительного по- из которых выполнен на МДП-транзисто- тенциала сигнала Т„, что может при- ре, дифференциальный усилитель, столбец вести к искажению информации на выходе 45 эталонных элементов памяти, четыре эле- устройства, так как с помощью этого мента разряда, выполненных на МДП-тран- сигнала поддерживается включенное состоя- зисторах, первую группу э,яементов предза- ние усилителя 60 и передача информации ряда и элемент предзаряда, выполненных через транзистор 34 на вход усилителя 74. на МДП-транзисторах, мультиплексор, ин- С целью исключения этого введен тран- формационные входы которого соединены с зистор 25 - элемент компенсации токов соответствующими разрядными щинами пер- утечки. При установлении положительного вой группы матричного накопителя, истоки потенциала сигнала Тм входы усилителя 60 МДП-транзисторов элементов разряда пер- транзисторами 32 и 33 отключаются от вы- вой группы подключены к шине нулево- ходных цепей дифференциальных усилите- го потенциала устройства, стоки подключе- лей, что способствует увеличению скорости гс i к соответствующим словарным шинам переключательных процессов, происходящих матричного накопителя, а затворы соедине- в плечах триггера усилителя 60, которые ны с выходом формирователя сброса, пер- протекают следующим образом: объединен- вый вход которого соединен с вторым вхо35

которого уже переключился, поступает на вход усилителя 74, устанавливая на выходе устройства соответствующий информационный сигнал.

Разделение на части матричного накопителя, введение новых элементов и связей позволяет значительно повысить быстродействие устройства. Результат сравнения технических параметров известных и предлагаемого ПЗУ показывают, что при равной

восходит этот параметр известного устройства. Кроме того, предлагаемое устройство допускает более жесткие условия эксплуатации, характеризуется более высокими

Формула изобретения

Постоянное запоминающее устройство, содержащее матричный накопитель, дешифратор слов, формирователь сброса, первую группу элементов разряда, каждый из которых выполнен на МДП-транзисторах, тактируемые усилители, формирователь сигпотенциал, сигнал с усилителя 60, триггер

потребляемой мощности быстродействие предлагаемого устройства в 1,8 раза прекоторого уже переключился, поступает на вход усилителя 74, устанавливая на выходе устройства соответствующий информационный сигнал.

Разделение на части матричного накопителя, введение новых элементов и связей позволяет значительно повысить быстродействие устройства. Результат сравнения технических параметров известных и предлагаемого ПЗУ показывают, что при равной

показателями по надежности и долговеч- ности.

восходит этот параметр известного устройства. Кроме того, предлагаемое устройство допускает более жесткие условия эксплуатации, характеризуется более высокими

нала смены адреса слова, два формиро- вателя тактового сигнала, выходной уси- литель, формирователь строб-сигнала, пер- вую группу элементов развязки, каждый

Формула изобретения

Постоянное запоминающее устройство, содержащее матричный накопитель, дешифратор слов, формирователь сброса, первую группу элементов разряда, каждый из которых выполнен на МДП-транзисторах, тактируемые усилители, формирователь сигдом первого формирователя тактового сигнала и с выходом формирователя строб- сигнала, первый вход которого соединен с первым входом первого формирователя тактового сигнала и с выходом второго формирователя тактового сигнала, второй вход формирователя строб-сигнала соединен с первой разрядной шиной столбца эталонных элементов памяти, словарные шины которого соединены с соответствуюп;ими слоисточники тока, коммутаторы, вторую группу элементов предзаряда, выполненных на МДП-транзисторах, дешифраторы разряда, два предварительных усилителя, четыре элемента развязки, выполненных на МДП- транзисторах, три инвертора, стробируемый элемент связи, выполненный на МДП-тран- зисторе, элемент компенсации токов утечки, два парафазных ключевых элемента, три элемента нагрузки, истоки МДП-транзистоварными шинами матричного накопителя, 10 ров каждой пары декодирующих элеменразрядные шины первой и второй групп которого, а также первая и вторая разрядные шины столбца эталонных элементов памяти соединены с истоками МДП-тран- зисторов соответствующих элементов предзаряда первой группы, стоки которых подключены к шине питания устройства, а затворы соединены с выходом формирователя сброса и с затвором МДП-транзистора элемента предзаряда, сток которого подключен

15

тов объединены и соединены с выходом соответствующего тактируемого усилителя, а стоки подключены к соответствующим словарным тинам матричного накопителя, затворы МДП-транзисторов первых декодирующих элементов пар соединены с первым прямым адресным входом формирователя сигнала смены адреса слова, первый инверсный а-дресный вход которого соединен с затворами МДП-транзисторов вторых декок шине питания устройства, исток МДП-тран-- 2Q дирующих элементов пар, затворы МДПисточники тока, коммутаторы, вторую группу элементов предзаряда, выполненных на МДП-транзисторах, дешифраторы разряда, два предварительных усилителя, четыре элемента развязки, выполненных на МДП- транзисторах, три инвертора, стробируемый элемент связи, выполненный на МДП-тран- зисторе, элемент компенсации токов утечки, два парафазных ключевых элемента, три элемента нагрузки, истоки МДП-транзисто5

тов объединены и соединены с выходом соответствующего тактируемого усилителя, а стоки подключены к соответствующим словарным тинам матричного накопителя, затворы МДП-транзисторов первых декодирующих элементов пар соединены с первым прямым адресным входом формирователя сигнала смены адреса слова, первый инверсный а-дресный вход которого соединен с затворами МДП-транзисторов вторых деко

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1985 |

|

SU1300565A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1531169A1 |

| Адресный формирователь | 1981 |

|

SU1014027A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Запоминающее устройство | 1985 |

|

SU1269209A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1096693A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Запоминающее устройство | 1985 |

|

SU1317481A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU746718A1 |

Изобретение относится к вычислительной технике и может быть использовано в постоянных запоминающих устройствах. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается введением в устройство мирователя 5 сигнала смены адреса разряда, пар декодирующих элементов 17, 18, двух парафазных ключевых элементов на МДП-транзисторах 26-29, стробируемого элемента связи 30, элемента 25 компенсации токов утечки, первого элемента развязки 31 и второй группы элементов развязки 21, 22, второй группы элементов развязки 23, 24, третьего элемента нагрузки 41, генератора импульсов 10, формирователя 1 1 высоковольтного сигнала смещения с соответствующими связя- .ми. Введение в устройство перечисленных элементов позволяет разбигь накопитель 1 на несколько частей и проводить считывание информации отдельно из каждой части. В результате паразитная емкость щин может быть уменьп ена, а быстродействие увеличено. 7 ил. ffi (Л t/cc« 00 00 00 ;о СП 878869 SO 91 Фиг. f

зистора первого элемента разряда соединен с истоками МДП-транзисторов второго, третьего и четвертого элементов разряда и подключен к шине нулевого потенциала устройства, затвор МДП-транзистора третьетранзисторов первой группы элементов развязки соединены с выходом формирователя высоковольтного сигнала смещения, прямой и инверсный входы которого соединены с прямым и инверсным выходами генератора

го элемента разряда соединен с выходом 25 импульсов, входы дешифраторов разряда первого формирователя тактового сигнала и с тактовыми входами тактируемых усилителей, информационные входы которых соединены со стоками МДП-транзисторов соответствующих элементов развязки первой группы, затворы которых объединены, а исто- ки соединены с соответствующими выходами дешифратора слов, входы которого соединены с соответствующими адресными входами формирователя сигнала смены адреса слова, адресные входы которого яв-., г------ .

ляются входами первой группы устройства, третьи входы дифференциального усилите- выход выходного усилителя является инфор-ля и дифференциальных усилителей группы

мационным выходом устройства, второй вход первого формирователя тактовых сигналов

соединены с соответствующими адресными входами первой группы формирователя сигнала смены адреса разряда, адресные входы первой и второй групп которого соединены с соответствующими входами коммутации мультиплексора и мультиплексоров группы, выходы мультиплексоров группы соединены с первыми входами соответствующих дифференциальных усилителей группы, вторые входы которых подключены к щине опорного потенциала устройства.

соединен с затвором МДП-транзистора втосоединены с выходами соответствующих стробируемых источников тока, а прямой и инверсный выходы соединены соответственно с прямым и инверсным информационными входами соответствующих коммутаторов, входы управления коммутацией которых соединены с соответствующими выходами дешифратора выбора дифференциального усилителя, входы которого соединены с соответствующими адресными входами третьей группы формирователя сигнала смены адреса разряда, вход выборки которого соединен с входом выборки формирователя сигнала смены адреса слова и

40

рого элемента разряда, выход мультиплексора соединен с первым входом дифференциального усилителя, второй вход которого подключен к шине опорного потенциала устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит формирователь сигнала смены адреса разряда, три группы адресных входов которого являются входами второй группы устройства, группу дифференциальных усилителей, дешифратор выбора дифсоединены с выходами соответствующих стробируемых источников тока, а прямой и инверсный выходы соединены соответственно с прямым и инверсным информационными входами соответствующих коммутаторов, входы управления коммутацией которых соединены с соответствующими выходами дешифратора выбора дифференциального усилителя, входы которого соединены с соответствующими адресными входами третьей группы формирователя сигнала смены адреса разряда, вход выборки которого соединен с входом выборки формирователя сигнала смены адреса слова и

ференциального усилителя, группу мульти- выходом третьего инвертора, вход котоплексоров, пары декодирующих элементов, каждый из которых выполнен на МДП-тран- зисторе, генератор импульсов, формирователь высоковольтного сигнала смещения, элемент задержки, вторую группу элементов

рого соединен с входом первого инвертора и с стоком МДП-транзистора пятого элемента разряда, затвор и исток которого соединены с выходом второго инвертора, вход которого соединен с выходом

развязки, каждый из которых выполнен на55 первого инвертора и с затворами МДП-транМДП-транзисторе, пятый элемент разрядазисторов второго и третьего элементов рази вторую группу элементов разряда, выпол-вязки, стоки которых соединены с пряненных на МДП-транзисторах, стробируемыемым и инверсным входами соответственно

транзисторов первой группы элементов развязки соединены с выходом формирователя высоковольтного сигнала смещения, прямой и инверсный входы которого соединены с прямым и инверсным выходами генератора

импульсов, входы дешифраторов разряда ., г------ .

импульсов, входы дешифраторов разряда ., г------ .

третьи входы дифференциального усилите- ля и дифференциальных усилителей группы

соединены с соответствующими адресными входами первой группы формирователя сигнала смены адреса разряда, адресные входы первой и второй групп которого соединены с соответствующими входами коммутации мультиплексора и мультиплексоров группы, выходы мультиплексоров группы соединены с первыми входами соответствующих дифференциальных усилителей группы, вторые входы которых подключены к щине опорного потенциала устройства.

0

соединены с выходами соответствующих стробируемых источников тока, а прямой и инверсный выходы соединены соответственно с прямым и инверсным информационными входами соответствующих коммутаторов, входы управления коммутацией которых соединены с соответствующими выходами дешифратора выбора дифференциального усилителя, входы которого соединены с соответствующими адресными входами третьей группы формирователя сигнала смены адреса разряда, вход выборки которого соединен с входом выборки формирователя сигнала смены адреса слова и

рого соединен с входом первого инвертора и с стоком МДП-транзистора пятого элемента разряда, затвор и исток которого соединены с выходом второго инвертора, вход которого соединен с выходом

первого инвертора и с затворами МДП-транпервого предварительного усилителя, вход нулевого потенциала которого соединен со стоком МДП-транзистора второго элемента разряда, а выход соединен со стоком МДП-транзистора четвертого элемента развязки, затвор которого соединен с выходом второго инвертора, а исток - с входом выходного усилителя, истоки МДП-транзис- торов второго и третьего элементов развязки соединены соответственно с прямыми

торого соединен с вторым входом формирователя сброса и с выходом второго предварительного усилителя, входы которого соединены с выходами формирователей сигнала смены адреса слова и разряда соответственно, прямой вход первого пара- фазного ключевого элемента соединен с входом третьего инвертора, выходом формирователя строб-сигнала и с первым выводом элемента компенсации токов утечки.

и инверсными выходами коммутаторов и с 10 второй вывод которого подключен к шине первыми выводами первого и второго эле-питания устройства, к которой подключен

ментов нагрузки соответственно, вторыепервый вывод третьего элемента нагрузки,

выводы которых подключены к шине пита-второй вывод которого соединен с затния устройства, к которой подключены сто-вором МДП-транзистора первого элемента

ки МДП-транзисторов элементов предзаря- с ° ™ ° МДП-транзистора да второй группы, истоки которых соеди- элемента пазпяпя .ятяпп .птпппт нены с первыми входами соответствующих дифференциальных усилителей, а затворы соединены с выходом формирователя сброса и с затвором МДП-транзистора четвертого элемента разряда, сток которого

соединен с выходом элемента задержки и с входами строб-сигнала стробируемых источников тока, входы смещения которых подключены к шине напряжения смещения

первого элемента разряда, затвор которого соединен с истоками МДП-транзисторов первого элемента развязки и элементов развязки второй группы и с затворами МДП-транзисторов элементов разряда вто- 20 Р° группы, истоки которых подключены к шине нулевого потенциала устройства, а стоки соединены с затворами МДП-транзисторов соответствующих элементов развязки второй группы и с соответствующими выходами дешифратора разрядов сток устройства, вход элемента задержки соеди- 25 МДП-транзистора первого элемента раз- нен с выходом первого формирователя так- вязки подключен к второй разрядной шине тового сигнала и с затвором МДП-тран- столбца эталонных элементов памяти стоки зистора стробируемого элемента связи, сток МДП-транзисторов элементов развязки вто- которого соединен с выходом первого па- рой группы подключены к соответствующим рафазного ключевого элемента, а исток - разрядным шинам второй группы матрич- с прямым входом второго парафазного 30 „ого накопителя, разрядные шины пер- ключевого элемента, выход которого соединен с выходом формирователя сброса, инверсный вход соединен с выходом первого формирователя тактового сигнала, инверсный вход первого парафазного ключево - - J-- .... /-S , D

ГО элемента соединен с выходом второго 35 го элемента разряда и со стоком ЧДП- формирователя тактового сигнала,вход ко- транзистора третьего элемента разряда.

i/

, 7.;/7.7.

разрядные шины первой группы которого подключены к соответствующим информационным входам мультиплексоров группы, исток МДП-транзистора первого элемента предзаряда соединен с затвором МДП-транзистора первоторого соединен с вторым входом формирователя сброса и с выходом второго предварительного усилителя, входы которого соединены с выходами формирователей сигнала смены адреса слова и разряда соответственно, прямой вход первого пара- фазного ключевого элемента соединен с входом третьего инвертора, выходом формирователя строб-сигнала и с первым выводом элемента компенсации токов утечки.

второй вывод которого подключен к шине питания устройства, к которой подключен

первого элемента разряда, затвор которого соединен с истоками МДП-транзисторов первого элемента развязки и элементов развязки второй группы и с затворами МДП-транзисторов элементов разряда вто- Р° группы, истоки которых подключены к шине нулевого потенциала устройства, а стоки соединены с затворами МДП-транзисторов соответствующих элементов развязки второй группы и с соответствующими выходами дешифратора разрядов сток МДП-транзистора первого элемента раз- вязки подключен к второй разрядной шине столбца эталонных элементов памяти стоки МДП-транзисторов элементов развязки вто- рой группы подключены к соответствующим разрядным шинам второй группы матрич- „ого накопителя, разрядные шины пер-

J-- .... /-S , D

го элемента разряда и со стоком ЧДП- транзистора третьего элемента разряда.

разрядные шины первой группы которого подключены к соответствующим информационным входам мультиплексоров группы, исток МДП-транзистора первого элемента предзаряда соединен с затвором МДП-транзистора первоДдрес

Ci(C2 9 S2

фиеЛ

фиг. 5

ff/rrof ou бхоЗ

С Выхода дешифратора 9

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| Авторское свидетельство СССР № 1156139, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-04-15—Публикация

1986-04-24—Подача