СО СО i42

сл

О5

Изобретение относится к радиотехнике и может быть использовано в од- ноканальных и многоканальных приемниках сигналов с амплитудно-фазовой модуляцией для определения порога демодуляции сигнала по амплитуде, а также в устройствах определения оценки среднего значения при выборке сигналов фиксированной длины.

Цель изобретения - повьпаение точности определения порога демодуляции

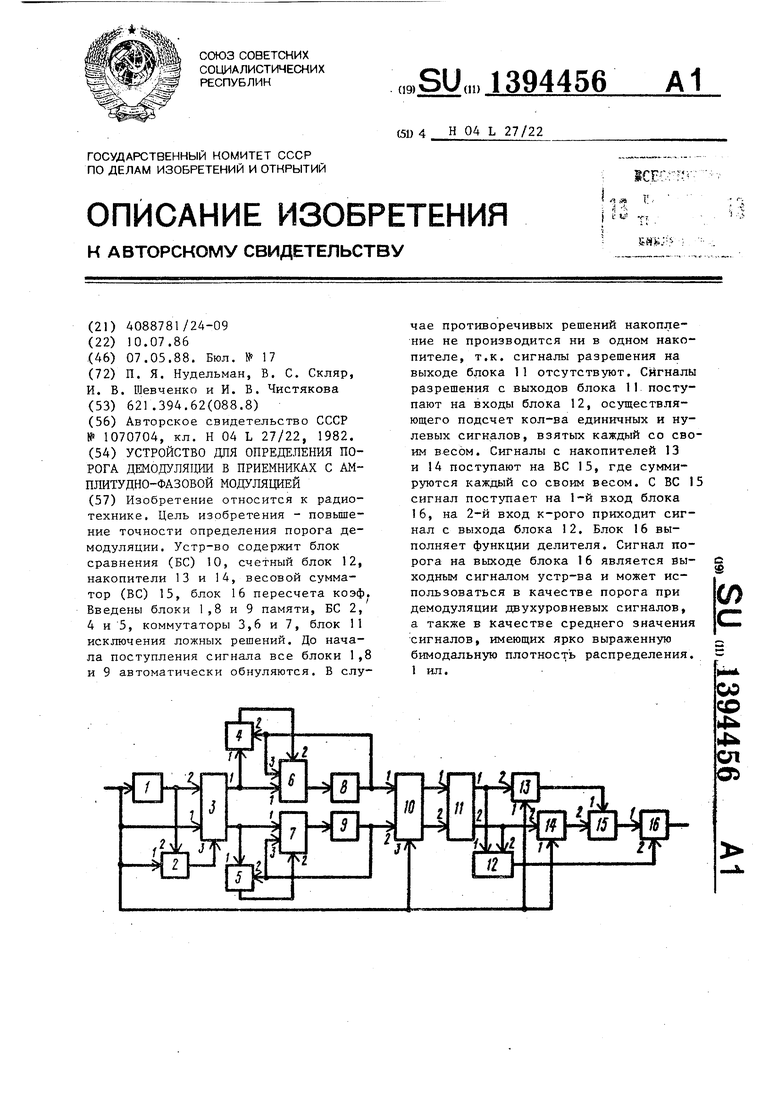

На чертеже приведена структурная схема устройства.

Устройство для определения порога демодуляции содержит первый блок 1 памяти, второй блок 2 сравнения, первый коммутатор 3, третий 4 и четвертый 5 блоки сравнения, второй 6 и третий 7 коммутаторы, второй 8 и третий 9 блоки памяти, первый блок 0 сравнения, блок 11 исключения ложных решений, счетный блок 12, первый 13 и второй 14 накопители, весовой сумматор 15 и блок 16 пересчета коэффициентов.

Устройство работает следующим образом.

Сигналы г. , представляющие собой амплитуды сигнальных элементов при амплитудно-фазовой модуляции (АФМ) или проекции на ортогональные оси приемника при квадратурной модуляции (КАМ)J поступают на вход первого блока 1 памяти, где они задерживаются н временной интервал /51, равный длителности одного элемента входного сигнала.

Второй блок 2 сравнения сравнивает по величине, входной сигнал и задержанный на время 4t сигнал г-. При этом йа его выходе формируются уровни логической 1, если г,-7, г-,, и логического О, если г :j г . , которые управляют работой коммутатора 3, При появлении на третьем управляющем входе коммутатора 3 уровня логической 1 на его первый выход поступает сигнал г -, а на второй - сиг

нал Г|,, и наоборот, при появлении на управляющем входе коммутатора 3 уровня логического О на его первый и второй выходы проходят соответственно сигналы г и т , Таким образом, на первом выходе коммутатора 3 всегда появляется больший по величине сигнал.

До начала поступления первого сигнала все три блока 1, 8 и 9 памяти

0

5

5

5 0

0

0

автоматически обнуляются, подготавливая все устройство к обработке входных сигналов. Сигнал с первого выхода коммутатора 3 поступает на первый вход третьего блока 4 сравнения, на второй вход которого приходит сигнал с выхода блока 8 памяти. Если сигнал на первом входе третьего блока 4 сравнения превышает сигнал на его втором входе, то на выходе этого блока образуется управляющий сигнал, по которому коммутатор 6 пропускает сигнал с первого выхода коммутатора 3 на вход блока 8 памяти. Если же большим по величине оказывается сигнал на втором входе третьего блока 4 сравнения, то коммутатор 6 пропускает на вход блока 8 памяти сигнал с выхода блока 8 памяти. В этом случае сигнал на входе блока 8 памяти не изменяется. Таким образом, из двух сигналов

г. (входного) и г ., (хранимого в памяти) блок 8 памяти на очередном такте работы устройства всегда сохраняет больший сигнал. В результате перебора всех входных сигналов (после поступления г.) на выходе блока 8 памяти появляется максимальный сигнал из всех пришедших на вход устройства.

Аналогичным образом работает вторая группа блоков, содержащая чет- верть й блок 5 сравнения, коммутатор 7 и блок 9 памяти. Отличие состоит в том, что коммутатор 7 управляется таким образом, что на вход блока 9 памяти всегда поступает меньший из двух сигналов, пришедших на входы четвертого блока 5 сравнения. На N-M такте работы устройства на выходе блока 9 памяти появляется минимальный из всех входных сигналов.

После N-ro такта работы на первом входе первого блока 10 сравнения устанавливается значение максимального сигнала втором входе - минимального сигнала г,. Начиная с этого момента состояние блоков 8 и 9 памяти остается неизменным. Третий вход первого блока 10 сравнения соединен с входом устройства. На этот вход после N-ro такта снова начинает поступать та же (или следующая)

последовательность сигналов г

ко- N

торая приходила во время первых тактов.

Первый блок 10 сравнения производит сравнение сиг галов г и г,,

соответственно с сигналами r-z

и

Г; Z

где Z J. и Z-P

т,

л li-i.v-tJT 4t-.-r весовые ко™ 1 1 1

эффициеиты. Если выполняется неравенство

МЯКС 1

(1)

то на первом выходе первого блока 10 сравнения появляется сигнал логической 1, в противном случае - ло-

гического О . На втором выходе первого блока 10 сравнения сигнал логической 1 появляется при выполнений неравенства

г

(2)

/мин 1 т,

Выполнение неравенства (1) свидетельствует о соответствии Г; нулевому информационному сигналу tj О, а выполнение неравенства (2) - единичному информационному сигналу т. .

При одновременном выполнении неравенств (1) и (2) возникают проти

счетного блока 12, осуществляющего подсчет количества единичных и нулевых сигналов, взятых каждый со своим весом. Сигнал на выходе счетного блока 12 после прохождения последнего входного элемента г bj равен

N

т, гао/ о+ т,/}, ,

(3)

т и т, соответственно количество нулевых и единичных сигналов; /5 и fbf постоянные весовые

коэффициенты, например

при приеме сигналов с

отношением разрешенных уровней, равным V, коэффициенты принимают значения Рр 1;

Р, -

Сигналы с выходов накопителей 13

и 14 поступают на весовой сумматор 15, где суммируются каждый со своим весом. После обработки последнего

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для демодуляции многочастотных амплитудно-фазомодулированных сигналов | 1982 |

|

SU1070704A1 |

| Устройство для определения граничных точек хроматографического пика | 1986 |

|

SU1456973A1 |

| РАНГОВЫЙ АДАПТИВНЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ ОБНАРУЖИТЕЛЬ СИГНАЛОВ | 1996 |

|

RU2100822C1 |

| Устройство тактовой синхронизации псевдослучайных последовательностей | 1988 |

|

SU1596473A1 |

| Устройство дя определения граничных точек хроматографического пика | 1988 |

|

SU1587547A2 |

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1992 |

|

RU2114514C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460224C1 |

| Цифровой согласованный фильтр сигналов с дискретной частотной манипуляцией | 1986 |

|

SU1438017A1 |

| Устройство для оценки фазы периодического импульсного сигнала | 1988 |

|

SU1610601A1 |

| Декодер сверточного кода | 1984 |

|

SU1319283A1 |

Изобретение относится к радиотехнике. Цель изобретения - повьппе- ние точности определения порога демодуляции. Устр-во содержит блок сравнения (БС) 10, счетный блок 12, накопители 13 и 14, весовой сумматор (ВС) 15, блок 16 пересчета коэф. Введены блоки I,8 и 9 памяти, БС 2, 4 и 5, коммутаторы 3,6 и 7, блок 11 исключения ложных решений. До начала поступления сигнала все блоки 1,8 и 9 автоматически обнуляются. В случае противоречивых решений накопление не производится ни в одном накопителе, т.к. сигналы разрешения на выходе блока 11 отсутствуют. Сигналы разрешения с выходов блока II поступают на входы блока 12, осуществляющего подсчет кол-ва единичных и нулевых сигналов, взятых каждый со своим весом. Сигналы с накопителей 13 и 14 поступают на ВС 15, где суммируются каждый со своим весом. С ВС 15 сигнал поступает на 1-й вход блока 16, на 2-й вход к-рого приходит сигнал с выхода блока 12. Блок 16 выполняет функции делителя. Сигнал порога на выходе блока 16 является выходным сигналом устр-ва и может использоваться в качестве порога при демодуляции двухуровневых сигналов, а также в качестве среднего значения сигналов, имеющих ярко выраженную бимодальную плотность распределения. 1 ил. $ (/)

воречивые решения, выявление которых 25 элемента г на выходе весового сум- осуществляет блок 11 исключения лож- матора 15 образуется сигнал вида ных решений.

Блок 11 представляет собой логичес- кую схему, на первом выходе которой появляется разрешающий сигнал (логи- 30 -

I-r; i,Z

J

(4)

ИГ; соответственно сигналы, относительно которых приняты нулевые и единичные решения; do тл d весовые коэффициенты, принимающие значения с(о З/г; , 3/rf, С выхода весового сумматора 15 суммарный сигнал поступает на первый вход блока 16 пересчета коэффициентов, на второй вход которого приходит сигнал с выхода, счетного блока 12о Блок 16 пересчета коэффициентов выполняет функции делителя, сигнал на выходе которого пропорционален сигналу на первом входе и обратно пропорционален сигналу на втором вхо де;

ческая 1) при выполнении неравенства (2) и неравенства,обратного (1), На втором выходе блока 11 сигнал логической 1 появляется при вьтолне- нии неравенства (1) и неравенства, обратного (2). Во всех остальных случаях на выходах блока 11 появляются сигналы логических О,

Таким образом, при решении г. разрешающий сигнал на первом выходе блока 11 исключения ложных решений пропускает входной сигнал г на вход первого накопителя 13, осуществляющего накопление сигналов с большими .информационными уровнями.

При решении г О разрешающий сигнал на втором выходе блока 11 пропускает сигнал г на вход второго накопителя 14, в котором происходит накопление сигналов с меньшими уровнями.

В случае противоречивых решений накопление не производится ни в одном накопителе, так как сигналы разрешения на выходе блока 11 отсутствуют.

Одновременно с этим сигналы разрешения с выходов блока 11 исключения ложных решений поступают на входы

та г на выходе весового сум- 15 образуется сигнал вида

I-r; i,Z

J

(4)

-

ИГ;

соответственно сигналы, относительно которых приняты нулевые и единичные решения; do тл d весовые коэффициенты, принимающие значения с(о З/г; , 3/rf, С выхода весового сумматора 15 суммарный сигнал поступает на первый вход блока 16 пересчета коэффициентов, на второй вход которого приходит сигнал с выхода, счетного блока 12о Блок 16 пересчета коэффициентов выполняет функции делителя, сигнал на выходе которого пропорционален сигналу на первом входе и обратно пропорционален сигналу на втором входе;

г. Ч-1У

0

РО.

1

J

(iT)

5

flo - -1 fti Сигнал порога на выходе блока 16 пересчета коэффициентов является выходным сигналом устройства и может использоваться в качестве порога при демодуляции двухуровневых сигналов (АФМ, КАМ), а также в качестве среднего значения (математического ожидания) сигналов, имеющих ярко выражен513

ную бимодальную плотность распределения .

В результате исключения ложных решений на этапе предварительного разделения сигналов дроизводится отбраковка сигналов, подверженных действию больших помех, в результате чего повьшается точность определения порога демодуляции сигналов или оценки среднего значения последовательности случайных величин.

Формула изобретения

Устройство для определения порога 15 второго коммутатора, выход которого демодуляции в приемниках с амплитуд- через второй блок памяти соединен с но-фазовой модуляцией, содержащее вторым входом первого блока сравне- первый блок сравнения, первьй вход которого соединен с первыми входами

ния, к первому входу третьего блока сравнения, выход которого соедин

первого и второго накопителей, вторые 20 с вторым входом второго коммутатора.

входы и выходы которых соединены соответственно с входами счетного блока и с входами весового сумматора, выход которого подключен к первому входу блока пересчета коэффициентов, второй вход которого соединен с выходом счетного блока, о т л и ч а - ю щ е е с я тем, что, с целью повышения точности определения порога демодуляции, введены три блока памяти, второй, третий и четвертый блоки сравнения, три коммутатора и блок исключения ложных решений, входы и выходы которого соединены соответственно с

выходами первого блока.сравнения и с входами счетного блока, причем вход первого блока памяти соединен с первым входом первого коммутатора, к второму входу которого подключен выход первого блока памяти, с первым входом первого блока сравнения и с первым входом второго блока сравнения, второй вход и выход которого соединены соответственно с выходом первого блока памяти и с третьим входом первого коммутатора, выходы которого подключены к первому входу

второго коммутатора, выход которого через второй блок памяти соединен с вторым входом первого блока сравне-

ния, к первому входу третьего блока сравнения, выход которого соединен

Q

к первому входу третьего коммутатора, выход которого через третий блок памяти соединен с третьим входом первого блока сравнения, и к первому 5 входу четвертого блока сравнения, выход которого соединен- с вторым входом третьего коммутатора, третий вход которого соединен с вторым входом четвертого блока сравнения и с вторым входом .первого блока сравнения, первьй вход которого соединен с вто-- рым входом третьего блока сравнения и с третьим входом второго коммутатора.

| Устройство для демодуляции многочастотных амплитудно-фазомодулированных сигналов | 1982 |

|

SU1070704A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-05-07—Публикация

1986-07-10—Подача