Изобретение относится к технике передачи данных и может быть использовано в системах передачи цифровой информации для декодирования корректирующих сверточ- ных кодов в системах связи с недвоичными способ ами модуляции.

Цель изобретения - расширение функциональных возможностей путем декодирования недвоичного сверточного кода.

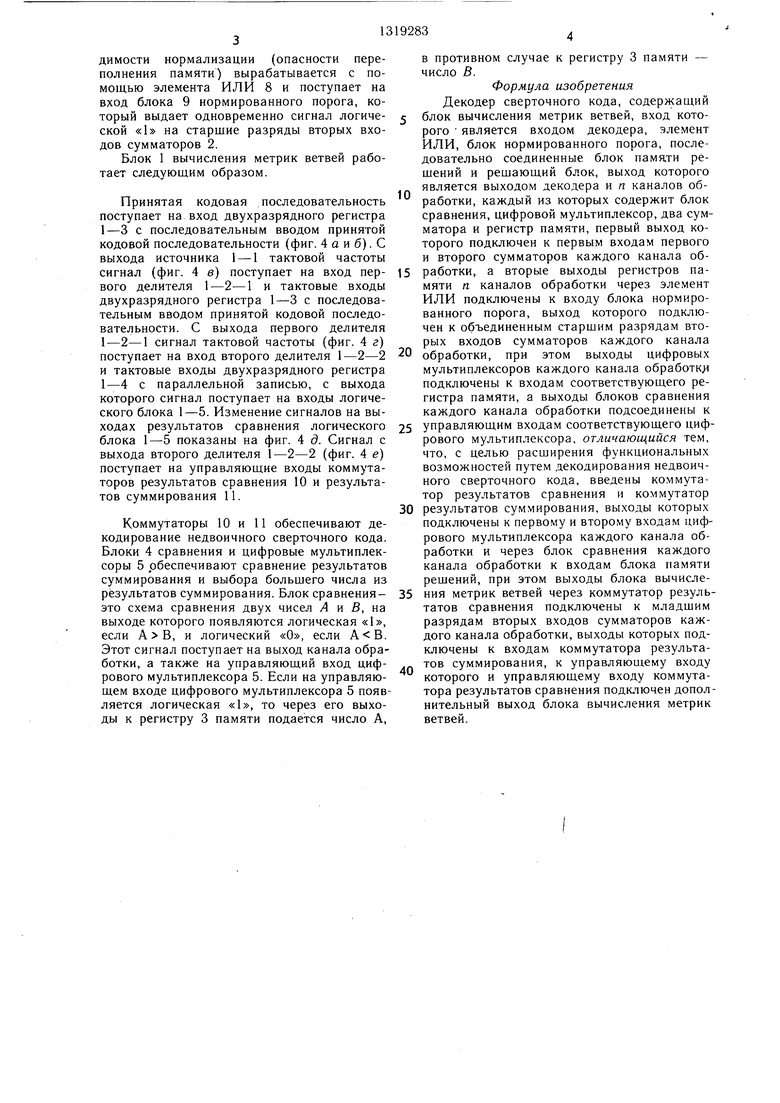

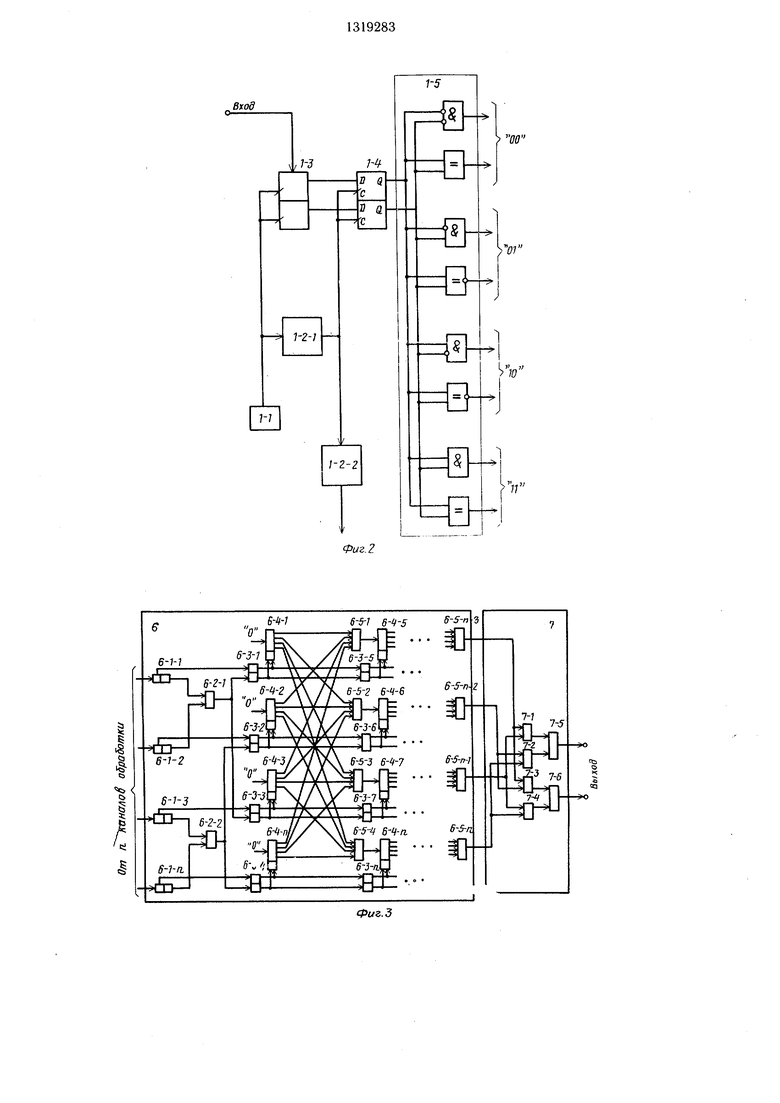

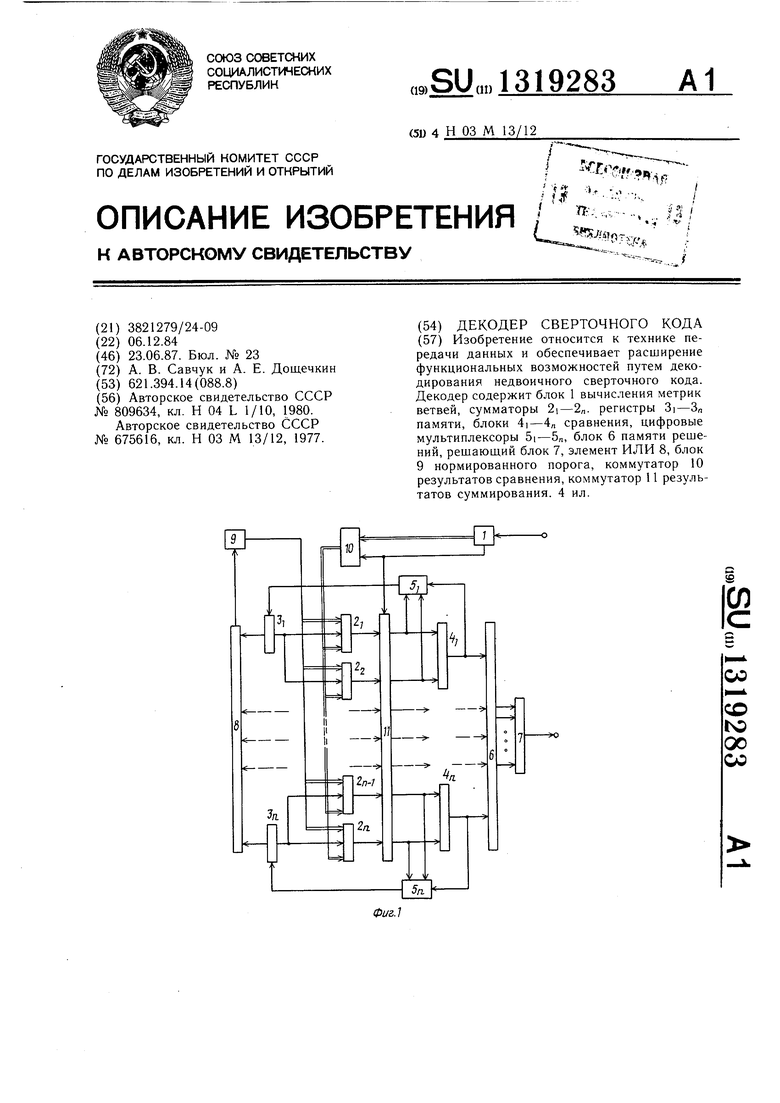

На фиг. 1 представлена структурная элеквен логической «1 на интервале времени, в течение которого поступает результат сравнения первого подблока принятой кодовой последовательности, и равен логическому «О на интервале времени, в течение которого поступает результат сравнения второго подблока принятой кодовой последовательности. В зависимости от указанных логических уровней управляющего сигнала состояние коммутатора 10 результата сравтрическая схема декодера сверточного кода; Ю нения изменяется так, что результаты срав- на фиг. 2 - блок вычисления метрик вет-нения (с двухсимвольными двоичными комвей; на фиг. 3 - блок памяти решений бинациями) первого подблока поступают на и решающий блок; на фиг. 4 - временныемладшие разряды вторых входов сумматодиаграммы работы блока вычисления метрик ров 2 одних каналов обработки, а результа- ветвей.АС ты сравнения второго подблока - на младДекодер сверточного кода содержит шие разряды вторых входов суммато- блок 1 вычисления метрик ветвей, сумма- ров 2 других каналов обработки в соответ- торь 2|...,2п, регистры 3i....,3,i памяти, блокиствии со структурой кода. Другие входы

4i,...,4n сравнения, цифровые мультиплексо- сумматоров подключены к выходам регистры 5u...,5n, блок 6 памяти решений, решаю- ров 3 памяти, в которых хранятся двоич- щий блок 7, элемент ИЛИ 8, блок 9 норми- 20 ные числа. Результаты суммирования (т.е. рованного порога, коммутатор 10 результатов сравнения, коммутатор 11 результатов суммирования, блок 1 вычисления метрик ветвей содержит источник 1 - 1 тактовой частоты, делители 1-2-1, 1-2-2, двухразрядный регистр 1-3 с последовательным вводом принятой кодовой последовательности, двухразрядный регистр 1-4 с параллельной записью, логический блок 1-5, блок

25

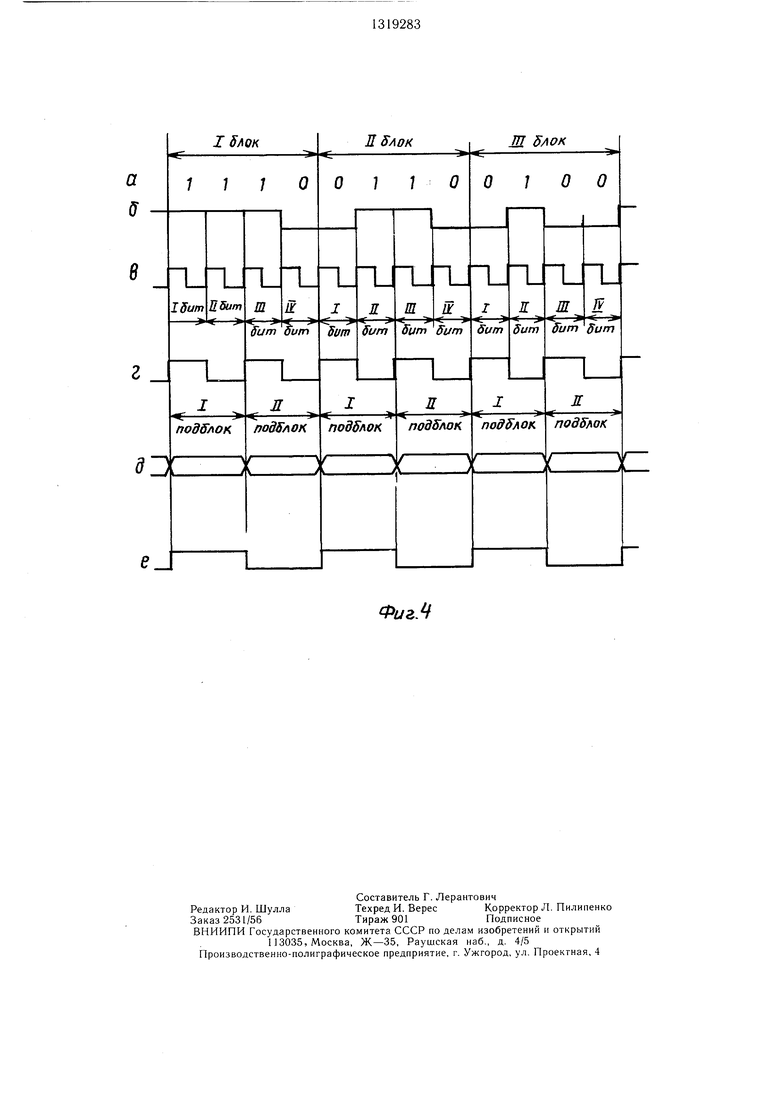

6 памяти решений содержит двухразрядные

суммирования между различными каналами обработки в соответствии со структурой кода. Выходной сигнал блока 4 сравнения воздействует на управляющий вход

выходные сигналы сумматоров 2) с выходов сумматоров 2 подаются на входы блоков 4 сравнения и одновременно на входы цифровых мультиплексоров 5 через коммутатор 11 результатов суммирования. Коммутатор 11 результатов суммирования работает так же, как и коммутатор 0 результатов сравнения. Он управляется логическими уровнями сигнала, который также поступает с блока 1 вычисления метрик ветвей. В зависимости

регистры 6-1 - 6-1-п с последователь- ..„ от этих уровней коммутатор 11 результатов ным вводом информации, элементы ИЛИ суммирования перераспределяет результаты б-2-1 и 6-2-2, двухразрядные регистры 6-3-1 - 6-3-п с параллельной записью, дешифраторы 6-4-1 - 6-4-п, элементы И 6-5-1 - 6-5-п, решающий блок 7 содержит элементы ИЛИ 7-1 - 7-4, RS-триг- цифрового мультиплексора 5 так, что на его геры 7-5 и 7-6.выход проходит больший из двух результаДекодер сверточного кода работает еле- тов суммирования, которые поступают на его дующим образом.входы. Этот больший результат суммироПринятая последовательность недвоич- вания записывается в соответствующий ре- ного сверточного кода разделяется на бло-гистр 3 памяти, где хранится до приема

ки, каждый из которых содержит четыре 40 следующего подблока принятой последова- двоичных символа. В блоке 1 вычисления тельности. Выходной сигнал блока 4 срав- метрик ветвей, куда она поступает, каждый четырехсимвольный блок последовательно рассматривается как совокупность двух двухсимвольных подблоков. Выходными сигналами блока 1 вычисления метрик ветвей являются результаты сравнения такого подблока с четырьмя всевозможными двухсимвольными двоичными комбинациями. Существует четыре результата сравнения для

каждого подблока принятой кодовой после- о непрерывно повторяются по мере поступле- довательности.ния двухсимвольных подблоков принятой коПолученные в блоке 1 вычисления метрик довой ветвей указанные результаты сравнения через коммутатор 10 результатов сравнения поступают на младшие разряды вторых входов сумматоров 2. На управляющий вход 55 димо периодически вычитать одно и то же чис- Коммутатора 10 результатов сравнения с до- ло из содержимого всех п регистров 3 памяти полнительного выхода блока 1 вычисления метрик ветвей подается сигнал, который ра45

нения является также выходным сигналом одного из каналов обработки и содержит информацию о принятой кодовой последовательности. Эта информация подается одновременно на п входов блока 6 памяти решений для дальнейшей обработки, а затем на вход решающего блока 7, выход которого является выходом декодера. Указанные операции суммирования, сравнения и выбора

последовательности. После обработки каждого подблока содержимое регистров 3 памяти увеличивается. Поэтому, чтобы избежать их переполнения, необхоЭту операцию одновременного вычитания называют нормализацией. Сигнал о необхосуммирования между различными каналами обработки в соответствии со структурой кода. Выходной сигнал блока 4 сравнения воздействует на управляющий вход

от этих уровней коммутатор 11 результатов суммирования перераспределяет результаты цифрового мультиплексора 5 так, что на его выход проходит больший из двух результаследующего подблока принятой последова- тельности. Выходной сигнал блока 4 срав-

непрерывно повторяются по мере поступле- ния двухсимвольных подблоков принятой ко

нения является также выходным сигналом одного из каналов обработки и содержит информацию о принятой кодовой последовательности. Эта информация подается одновременно на п входов блока 6 памяти решений для дальнейшей обработки, а затем на вход решающего блока 7, выход которого является выходом декодера. Указанные операции суммирования, сравнения и выбора

непрерывно повторяются по мере поступле- ния двухсимвольных подблоков принятой ко довой димо периодически вычитать одно и то же чис- ло из содержимого всех п регистров 3 памяти

последовательности. После обработки каждого подблока содержимое регистров 3 памяти увеличивается. Поэтому, чтобы избежать их переполнения, необхо довой димо периодически вычитать одно и то же чис- ло из содержимого всех п регистров 3 памяти

Эту операцию одновременного вычитания называют нормализацией. Сигнал о необходимости нормализации (опасности переполнения памяти) вырабатывается с помощью элемента ИЛИ 8 и поступает на вход блока 9 нормированного порога, который выдает одновременно сигнал логической «1 на старшие разряды вторых входов сумматоров 2.

Блок 1 вычисления метрик ветвей работает следующим образом.

Принятая кодовая последовательность поступает на вход двухразрядного регистра 1-3 с последовательным вводом принятой кодовой последовательности (фиг. 4 а и б). С выхода источника 1 - 1 тактовой частоты

Формула изобретения Декодер сверточного кода, содержащий блок вычисления метрик ветвей, вход которого является входом декодера, элемент ИЛИ, блок нормированного порога, последовательно соединенные блок памяти решений и решающий блок, выход которого является выходом декодера и п каналов обработки, каждый из которых содержит блок сравнения, цифровой мультиплексор, два сумматора и регистр памяти, первый выход которого подключен к первым входам первого и второго сумматоров каждого канала обсигнал (фиг. 4 в) поступает на вход пер- 15 работки, а вторые выходы регистров павого делителя 1-2-1 и тактовые входы двухразрядного регистра 1-3 с последовательным вводом принятой кодовой последовательности. С выхода первого делителя 1-2-1 сигнал тактовой частоты (фиг. 4 г)

мяти п каналов обработки через элемент ИЛИ подключены к входу блока нормированного порога, выход которого подключен к объединенным старшим разрядам вторых входов сумматоров каждого канала

поступает на вход второго делителя 1-2-2 обработки, при этом выходы цифровых

мультиплексоров каждого канала обработку подключены к входам соответствующего регистра памяти, а выходы блоков сравнения каждого канала обработки подсоединены к

ходах результатов сравнения логического 25 управляющим входам соответствующего цифи тактовые входы двухразрядного регистра 1-4 с параллельной записью, с выхода которого сигнал поступает на входы логического блока 1-5. Изменение сигналов на выблока I-5 показаны на фиг. 4 д. Сигнал с выхода второго делителя 1-2-2 (фиг. 4 е) поступает на управляющие входы коммутаторов результатов сравнения 10 и результатов суммирования 11.

рового мультиплексора, отличающийся тем, что, с целью расширения функциональных возможностей путем .декодирования недвоичного сверточного кода, введены коммутатор результатов сравнения и коммутатор 30 результатов суммирования, выходы которых подключены к первому и второму входам цифрового мультиплексора каждого канала обработки и через блок сравнения каждого канала обработки к входам блока памяти решений, при этом выходы блока вычислерового мультиплексора, отличающийся тем, что, с целью расширения функциональных возможностей путем .декодирования недвоичного сверточного кода, введены коммутатор результатов сравнения и коммутатор 30 результатов суммирования, выходы которых подключены к первому и второму входам цифрового мультиплексора каждого канала обработки и через блок сравнения каждого канала обработки к входам блока памяти решений, при этом выходы блока вычислеКоммутаторы 10 и 11 обеспечивают декодирование недвоичного сверточного кода. Блоки 4 сравнения и цифровые мультиплексоры 5 обеспечивают сравнение результатов суммирования и выбора большего числа из

результатов суммирования. Блок сравнения- 35 ния метрик ветвей через коммутатор резуль

это схема сравнения двух чисел Л и В, нататов сравнения подключены к младшим

выходе которого появляются логическая «1,разрядам вторых входов сумматоров кажесли , и логический «О, если .дого канала обработки, выходы которых подЭтот сигнал поступает на выход канала обра-ключены к входам коммутатора результа- ботки, а также на управляющий вход циф- ... тов суммирования, к управляющему входу

рового мультиплексора 5. Если на управляю-которого и управляющему входу коммутащем входе цифрового мультиплексора 5 появ-тора результатов сравнения подключен допол

ляется логическая «1, то через его выхо-нительный выход блока вычисления метрик

ды к регистру 3 памяти подается число А,ветвей.

в противном случае к регистру 3 памяти - число В.

Формула изобретения Декодер сверточного кода, содержащий блок вычисления метрик ветвей, вход которого является входом декодера, элемент ИЛИ, блок нормированного порога, последовательно соединенные блок памяти решений и решающий блок, выход которого является выходом декодера и п каналов обработки, каждый из которых содержит блок сравнения, цифровой мультиплексор, два сумматора и регистр памяти, первый выход которого подключен к первым входам первого и второго сумматоров каждого канала обмяти п каналов обработки через элемент ИЛИ подключены к входу блока нормированного порога, выход которого подключен к объединенным старшим разрядам вторых входов сумматоров каждого канала

обработки, при этом выходы цифровых

рового мультиплексора, отличающийся тем, что, с целью расширения функциональных возможностей путем .декодирования недвоичного сверточного кода, введены коммутатор результатов сравнения и коммутатор результатов суммирования, выходы которых подключены к первому и второму входам цифрового мультиплексора каждого канала обработки и через блок сравнения каждого канала обработки к входам блока памяти решений, при этом выходы блока вычисления метрик ветвей через коммутатор резуль

Ву:о6

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ВЫЧИСЛЕНИЯ МЕТРИК ПУТЕЙ ДЕКОДЕРА ВИТЕРБИ | 1990 |

|

RU2022473C1 |

| Декодер сверточного кода | 1988 |

|

SU1660178A1 |

| ДЕКОДЕР СВЕРТОЧНЫХ КОДОВ ДЛЯ DVB-T ПРИЕМНИКА | 2008 |

|

RU2399157C2 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2015621C1 |

| Устройство для декодирования сверточного кода | 1991 |

|

SU1839281A1 |

| Способ декодирования длинного блокового кода с помощью алгоритма Витерби | 2020 |

|

RU2747881C1 |

| Устройство для декодирования сверточного кода | 1989 |

|

SU1612378A1 |

| СПОСОБ ДЕКОДИРОВАНИЯ СВЕРТОЧНЫХ КОДОВ | 2012 |

|

RU2516624C1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМНО-ДЕМОДУЛИРУЮЩЕЕ УСТРОЙСТВО ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ СИСТЕМ СВЯЗИ | 2005 |

|

RU2305375C2 |

| ВЫСОКОСКОРОСТНОЙ МОДУЛЬ СЛОЖЕНИЯ (СРАВНЕНИЯ) ВЫБОРА ДЛЯ ДЕКОДЕРА ВИТЕРБИ | 2000 |

|

RU2246751C2 |

Изобретение относится к технике передачи данных и обеспечивает расширение функциональных возможностей путем декодирования недвоичного сверточного кода. Декодер содержит блок 1 вычисления метрик ветвей, сумматоры . регистры 3i-Зп памяти, блоки 4i-4„ сравнения, цифровые мультиплексоры 5i-5п, блок 6 памяти решений, решаюший блок 7, элемент ИЛИ 8, блок 9 нормированного порога, коммутатор 10 результатов сравнения, коммутатор 11 результатов суммирования. 4 ил. сл со со 1чЭ ас со

ФигМ

| Способ кодирования и декодированияСВЕРТОчНОгО КОдА | 1978 |

|

SU809634A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для декодирования сверточного кода | 1977 |

|

SU675616A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-06-23—Публикация

1984-12-06—Подача