оо со о го

со 05

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1980 |

|

SU951638A2 |

| Анализатор спектра сигналов | 1986 |

|

SU1399765A1 |

| Устройство формирования сигналов инфранизкой частоты | 1982 |

|

SU1269229A1 |

| Устройство для определения вектора дисбаланса | 1990 |

|

SU1755081A1 |

| СПОСОБ СИНХРОНИЗАЦИИ СИСТЕМЫ УПРАВЛЕНИЯ ТЯГОВЫМИ ПРЕОБРАЗОВАТЕЛЯМИ С ПИТАЮЩИМ НАПРЯЖЕНИЕМ ТЯГОВОЙ СЕТИ | 2016 |

|

RU2647792C1 |

| Устройство для измерения частотной характеристики входного сопротивления промышленной электрической сети | 1985 |

|

SU1439512A1 |

| Электропривод переменного тока | 1986 |

|

SU1334342A1 |

| Устройство для измерения среднего индикаторного давления двигателя внутреннего сгорания | 1984 |

|

SU1283559A1 |

| Измерительное устройство к балансировочному станку | 1990 |

|

SU1746232A1 |

| Устройство для взвешивания движущихся объектов | 1990 |

|

SU1789877A1 |

Изобретение относится к вычислительной технике, может использоваться в устр-вах релейной защиты объектов эл. станций и является дополнительным к изобретению по авт. св. № 951638. Цель изобретения повышение коэф. умножения в два раза, а также повышение коэф- умножения при входном сигнале умножителя частоты с начальной фазой, отличной от п- я/4 (п 0-7). Умножитель частоты содержит фазовращатель (ФВ) 1, сумматор 2, вычи- татель 3, компараторы 4-12, элемент ИЛИ 13, выпрямители 14-17, амплитудный детектор 18, делители напряжения (ДН) 19, 20, управляемый аналоговый сумматор (УАС) .21 и управляемый ключ 22. Входной синусоидальный сигнал с помощью ФВ 1 преобразуется в косинусоидальный. Из синусоиды и косинусоиды сумматор 2 и вычитатель 3 формируют сигналы. С помощью УАС 21 из входного сигнала, продетектированного амплитудным детектором 18, формируются три сигнала: сигнал с ДН 19, сигнал с ДН 20 и их суммарный сигнал. Полученные из входного сигнала семь сигналов сравниваются между собой и с постоянным напряжением в компараторах 4-12. Переключение управляемого ключа 22 и УАС 21 обеспечивает поочередное срабатывание компараторов 4-12 и появление на выходе элемента ИЛИ 13 импульсов. 2 з.п. ф-лы, 3 ил. I (Л

ISJ

Изобретение относится к устройствам релейной защиты и вычислительной техники, может быть использовано в качестве умножителя частоты для устройств с непосредственной связью с электрической сетью, а также для управления устройствами релейной защиты объектов электрических станций или электрических сетей и является усоверщенствованием изобретения по авт. св. № 951638.

Цель изобретения - повыщение коэф- фициента умножения в два раза, а также повыщение коэффициента умножения при входном сигнале умножителя частоты с начальной фазой,, отличной от пя/4, где .

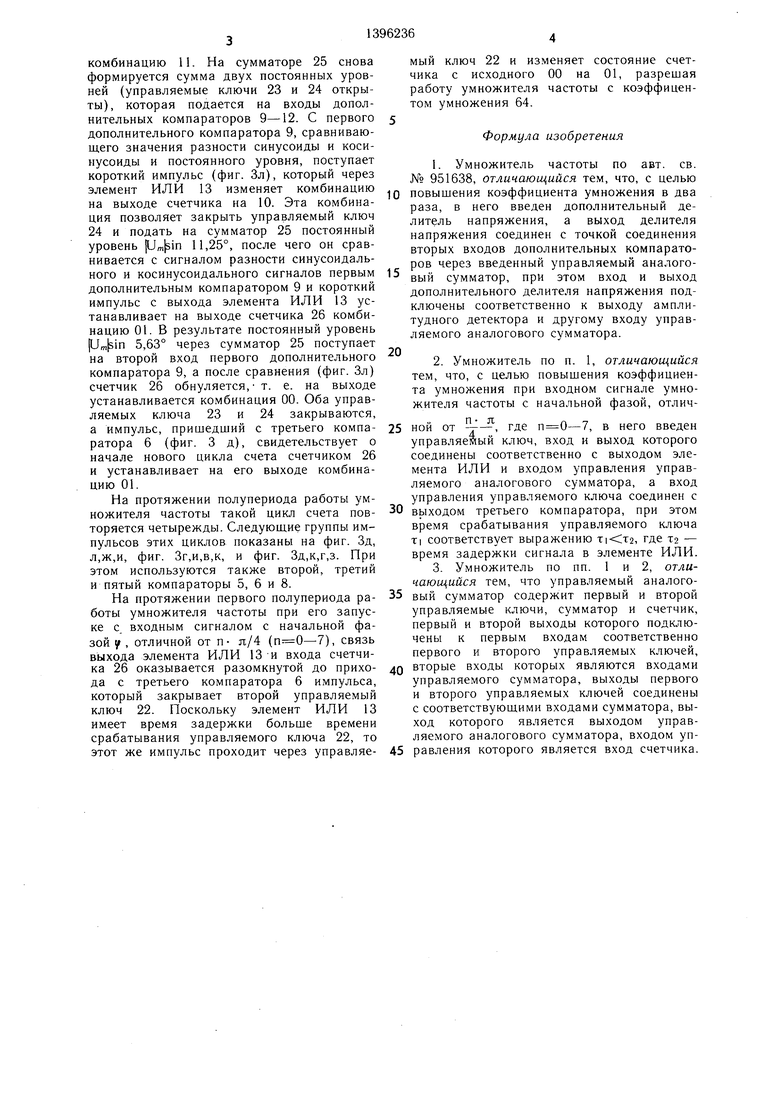

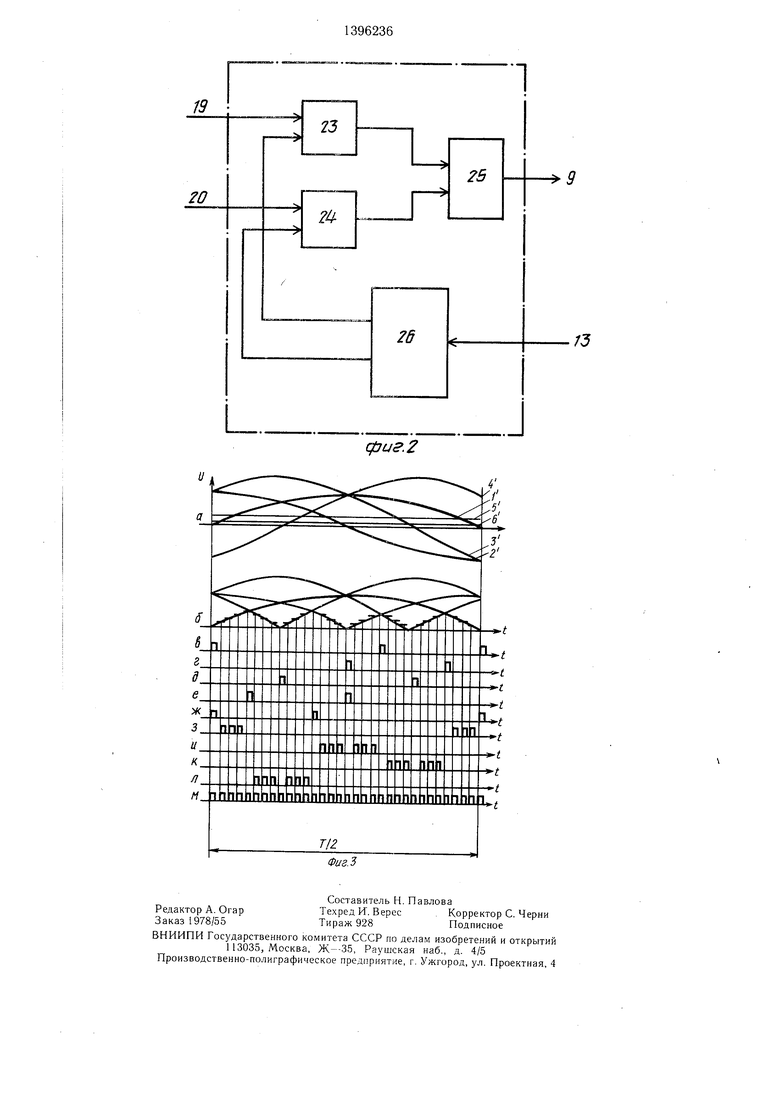

На фиг. 1 приведена структурная электрическая схема предлагаемого умножителя частоты; на фиг. 2 - структурная электрическая схема управляемого аналогового сумматора; на фиг. 3 - временные диаграммы преобразования сигналов в умножителе частоты.

Умножитель частоты содержит фазовращатель 1., сумматор 2, вычитатель 3, с первого по пятый компараторы 4-.8, с пер- |вого по четвертый дополнительные компа- |раторы 9-12, элемент ИЛИ 13, с перво- :го по четвертый выпрямители 14-17, амплитудный детектор 18, делитель 19 напряжения, дополнительный делитель 20 напряжения, управляемый аналоговый сумматор 21 и управляемый ключ 22.

Управляемый аналоговый сумматор 21 образуют первый 23 и второй 24 управляемые ключи, сумматор 25 и счетчик 26.

Умножитель частоты работает следующим образом.

На вход умножителя частоты подается входной сигнал синусоидальной формы, который фазовращателем 1 преобразуется в ко- синусоидальный. Сумматор 2 складывает синусоиду и косинусоиду, вычитатель 3 вычи- |тает от синусоиды косинусоиду {фиг. За, где 1 - синусоида; 2 - косинусоида; 3 - сумма синусоиды и косинусоиды; 4 - разность синусоиды и косинусоиды).

Амплитудный детектор 18 формирует сигнал постоянного напряжения, равный модулю Шт амплитуды входного сигнала.

С выхода амплитудного детектора 18 (сигнал постоянного напряжения поступает на делитель 19 и дополнительный делитель 20 напряжения, на выходах которых формируются также сигналы постоянного напряжения рш sin 11,25° и рт| sin 5,63° COOT- ветственно (фиг. За, 5 и 6 соответственно).

Входйой сигнал и сигналы с фазовращателя 1, сумматора 2, вычитателя 3 выпрямляются выпрямителями 14-17 (фиг. 36). На выходе управляемого аналого- вого сумматора 21 в соответствующий момент формируется сигнал, равный sin 5,63°, |Ur.|sin 11,25° или их сумме. Таким об

5

0

5

0

0

5

0

5

0

5

разом, получают группу из семи сигналов, которые подаются на компараторы и дополнительные компараторы для их сравнения между собой и с сигналами постоянного напряжения.

Исходным состоянием счетчика 26 является комбинация 00. Управляемые ключи 23 и 24 при такой комбинации на выходе счетчика закрыты, аналоговые сигналы с делителя 19 и дополнительного делителя 20 не поступают на второй вход первого дополнительного компаратора 9. При появлении на выходе элемента ИЛИ 13 короткого импульса, пришедщего, например, с первого компаратора 4 (фиг. Зв), состояние счетчика изменяется на 01. Такая комбинация позволяет вследствие отпирания ключа 24 подать уровень постоянного напряжения величиной pmjsin 5,63° на сумматор 25, а затем на второй вход первого дополнительного компаратора 9 и первые входы второго, третьего и четвертого дополнительных компараторов 10-12. Постоянный уровень напряжения pmjsin 5,63° сравнивается на первом дополнительном компараторе 12 с синусоидальным сигналом (фиг. Зз), и короткий импульс через элемент ИЛИ 13 устанавливает на счетчике комбинацию 10. Эта комбинация закрывает управляемый ключ 24 и открывает управляемый ключ 23, вследствие чего на сумматоре 25, а затем и на втором входе первого дополнительного компаратора 9 и первых входах второго, третьего и четвертого дополнительных компараторов 10- 12 устанавливается постоянный уровень напряжения pm|sin 11,25°. После сравнения этого уровня четвертым дополнительным компаратором 12 с синусидальным сигналом (фиг. Зз) импульс, прощедщий через элемент ИЛИ 13, устанавливает на счетчике комбинацию 11. При этом открываются управляемые ключи 23 и 24 и на сумматор 25 подаются два постоянных уровня pm|sin 11,25° и 5,63°. После их суммирования результат подается на второй вход первого дополнительного компаратора 9 и первые входы второго, третьего и четвертого дополнительных компараторов 10-

12и четвертым дополнительным компаратором 12 сравнивается с синусоидальным сигналом (фиг. Зз). Короткий импульс от четвертого дополнительного компаратора 12, прощедщий через элемент ИЛИ 13, устанавливает на выходе счетчика комбинацию 00. Оба управляемых ключа 23 и 24 закрываются, и постоянные уровни напряжения от делителя 19 и дополнительного делителя 20 не поступают на соответствующие входы дополнительных компараторов 9-12. После этого на элемент ИЛИ

13поступает импульс с четвертого компаратора 7 (фиг. Зе), который, поступив на вход счетчика переключает его на реверсивный счет, т. е. устанавливает на выходе

комбинацию 11. На сумматоре 25 снова формируется сумма двух постоянных уровней (управляемые ключи 23 и 24 открыты), которая подается на входы дополнительных компараторов 9-12. С первого дополнительного компаратора 9, сравнивающего значения разности синусоиды и косинусоиды и постоянного уровня, поступает короткий импульс (фиг. 3л), который через элемент ИЛИ 13 изменяет комбинацию на выходе счетчика на 10. Эта комбинация позволяет закрыть управляемый ключ 24 и подать на сумматор 25 постоянный уровень Um|sin 11,25°, после чего он сравнивается с сигналом разности синусоидального и косинусоидального сигналов первым дополнительным компаратором 9 и короткий импульс с выхода элемента ИЛИ 13 устанавливает на выходе счетчика 26 комбинацию 01. В результате постоянный уровень pm|sin 5,63° через сумматор 25 поступает на второй вход первого дополнительного компаратора 9, а после сравнения (фиг. 3л) счетчик 26 обнуляется, т. е. на выходе устанавливается комбинация 00. Оба управляемых ключа 23 и 24 закрываются, а импульс, пришедший с третьего компаратора 6 (фиг. 3 д), свидетельствует о начале нового цикла счета счетчиком 26 и устанавливает на его выходе комбинацию 01.

На протяжении полупериода работы умножителя частоты такой цикл счета повторяется четырежды. Следующие группы импульсов этих циклов показаны на фиг. Зд, л,ж,и, фиг. Зг,и,в,к, и фиг. Зд,к,г,з. При этом используются также второй, третий и пятый компараторы 5, 6 и 8.

На протяжении первого полупериода работы умножителя частоты при его запуске с входным сигналом с начальной фазой у , отличной от п- л/4 (), связь выхода элемента ИЛИ 13 и входа счетчика 26 оказывается разомкнутой до прихода с третьего компаратора 6 импульса, который закрывает второй управляемый ключ 22. Поскольку элемент ИЛИ 13 имеет время задержки больше времени срабатывания управляемого ключа 22, то этот же импульс проходит через управляе5

мый ключ 22 и изменяет состояние счетчика с исходного 00 на 01, разрешая работу умножителя частоты с коэффицен- том умножения 64.

Формула изобретения

0 повышения коэффициента умножения в два раза, в него введен дополнительный делитель напряжения, а выход делителя напряжения соединен с точкой соединения вторых входов дополнительных компараторов через введенный управляемый аналоговый сумматор, при этом вход и выход дополнительного делителя напряжения подключены соответственно к выходу амплитудного детектора и другому входу управляемого аналогового сумматора.

0 вь1ходом третьего компаратора, при этом время срабатывания управляемого ключа Т| соответствует выражению , где Т2 - время задержки сигнала в элементе ИЛИ.

0 вторые входы которых являются входами управляемого сумматора, выходы первого и второго управляемых ключей соединены с соответствующими входами сумматора, выход которого является выходом управляемого аналогового сумматора, входом уп5 равления которого является вход счетчика.

Фиг.З

фиг. 2

i,

| Умножитель частоты | 1980 |

|

SU951638A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-05-15—Публикация

1985-02-20—Подача