(21)AI01628/2A-24

(22)30.05.86

(46) 23.05.88. Бюл. № 19

(72) Ю.А.Воробьев, В.Н.Кодяева

и В.А.Федоров

(53)621.396(088.8)

(56)Авторское свидетельство СССР 542I13, кл. G 05 Б 19/00, 1977.

Авторское свидетельство СССР № 627447, кл. G 05 В 19/00, 1978.

Авторское свидетельство СССР № 1231486, кл. G 05 В 19/I8, 1984.

(54)МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ

(57)Изобретение относится к автома-- тичecкo cy управлению и может быть

использовано для программного управления технологическими процессами. Цель изобретения - повьппение качества управления путем устранения потерь управляющих команд. Устройство содержит объектные датчикиI, блок 2 управления объектом, дешифратор 5, элемент ИЛИ 6, группу одинаковых каналов 7 управления, ключ 14 и блок управления 23 входными сигналами. Устройство позволяет исключить влияние случайности во время поступления входных сигналов, которая может привести к сбою работы, и предотвратить потери входной информации. 2 з.п. ф-лы, 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для программного управления автоматической линией изготовления многослойных керамических конденсаторов | 1985 |

|

SU1297013A1 |

| Многоканальное устройство для программного управления | 1988 |

|

SU1585781A2 |

| Многоканальное устройство для программного управления автоматической линией изготовления многослойных керамических конденсаторов | 1990 |

|

SU1804642A3 |

| Многоканальное устройство для программного управления | 1986 |

|

SU1324012A1 |

| Многоканальное устройство для программного управления | 1984 |

|

SU1231486A1 |

| Многоканальное устройство управления технологическими объектами | 1989 |

|

SU1725186A1 |

| Система централизованного управления электроэнергетическим объектом | 1984 |

|

SU1201801A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ КАНАЛАМИ | 1973 |

|

SU386395A1 |

| Автоматизированная радиолиния | 1987 |

|

SU1443189A1 |

| УСТРОЙСТВО ДЛЯ ПОСТРОЕНИЯ ПРОГРАММИРУЕМЫХ ЦИФРОВЫХ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2004 |

|

RU2273042C2 |

1 fSf

«Г

/ / /

со со

СХ)

Изобретение относится к автоматическому управлению и может использоваться для программного управления различными технологическими процессами и объектами при выполнении групп технологических операций.

Целью изобретения является повьппе- ине качества работы устройства путем устранения потерь управляющих команд

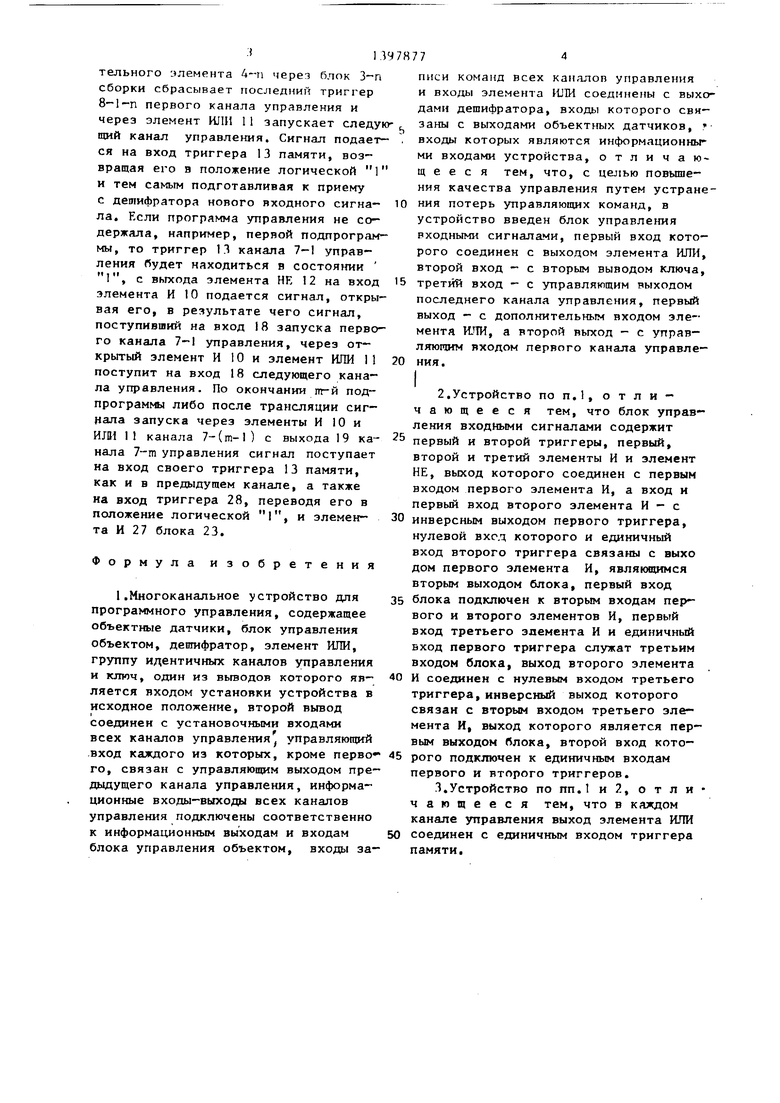

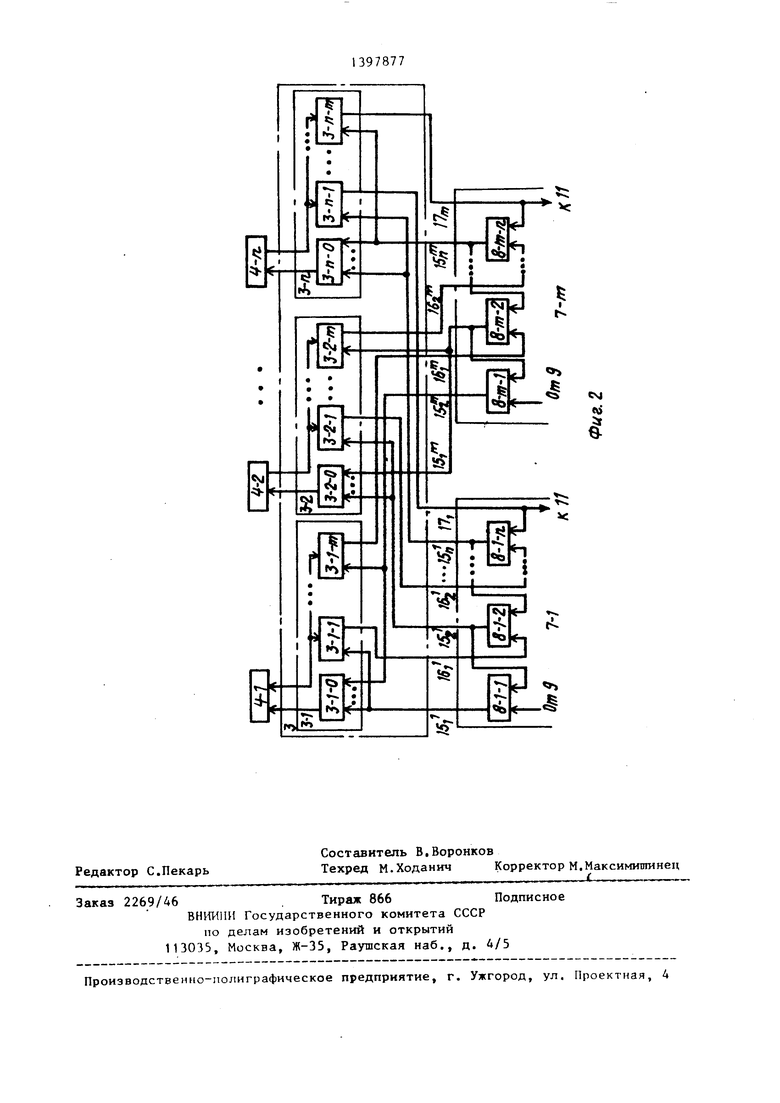

На фиг.1 представлена блок-схема устройства; на фиг.2 - схема узла сборки.

Устройство содержит объектные дат- чики 1, блок 2 управления объектом содержащий узел 3 сборки, который состоит из п (по числу исполнительных элементов) блоков сборки 3-i (i 1 , n) , каждый из которых включает

элемент ИЛИ 3-i-O (i - 1, n) и m

3-i-,1 (i 1 , n; .1 1 ,m)

элементов И

и исполнительные элементы А-1,..., Д-п, дешифратор 5 сигналов от объектных датчиков, элемент ИЛИ 6, каналы 7-1,...,7-1п управления, содержащие для каждого i-го канала (i I jin) К управляющих триггеров 8-i-K, первый элемент И 9, второй элемент И 10 первый элемент ИПП 11, элемент НЕ 12, триггер 13 памяти, ключ 14, ин- формационные входы 15 и выходы 16 и 17 блока 2, управляющие входы 18 каналов управления, управляющие выходы 19 каналов управления, вход 20 записи команд, установочный вход 21, счет- ный вход 22 триггера памяти, блок 23 управления входными сигналами, содержащий первый элемент И 24, элемент НЕ 25, второй 26 и третий 27 элементы И и первый 28 и второй 29 триггеры.

Устройство работает следующим образом.

В исходном состоянии, в которое переводится устройство с помощью ключа 14, все триггеры находятся в состоянии логической 1. При этом элемент И 10 канала управления и элемент И 24 блока 23 могут пропускать входные сигналы. Все остальные эле- менты И для прохождения сигналов закрыты. Сигналы с дешифратора через элемент ИЛИ 6 поступают на входы элемента И 24 и триггера 13 соответствующих каналов управления, переводя последние в положение логического О, что в свою очередь открывает элемент И 9 и закрьгоает элемент И 10 Задний фронт сигнала на выходе эле

0

5

0

5 0 5

мента И 24 переводит триггер 28 в положение логического О и поступает на вход 18 канала 7-1 управления.

Сигнал с триггера 28 через элемент НЕ 25 закрьгеает элемент И 24, препятствуя прохождению последующих сигналов в каналы управления.

Последующий сигнал с дешифратора 3, если сигнала на выходе 19 последнего канала управления не было, через открытый элемент И 26 переводит триггер 29 в положение логического О. Сигнал с триггера 29 открывает элемент И 27; тем самым запоминается наличие входного сигнала. Это состояние сохраняется до поступления сигнала с выхода 19 последнего канала управления, а входная информация с дешифратора сохраняется в триггерах 13 каналов управления. Сигнал с выхода последнего канала управления проходит открытый элемент И 27 и через элемент ИЛИ 6 и открытый элемент И 24 поступает на вход первого канала управления и одновременно на входы триггеров 28 и 29, переводя их соответственно в положение О и 1. Далее блок 23 работает аналогично описанному. Таким образом, блок 23, открывая канал управления первым сигналом с дешифратора, закрывает его для всех последующих входных сигналов до того момента времени, пока не закончится цикл управления и не поступит сигнал с выхода последнего канала управления об окончании цикла.

На выходе элемента И 9 канала 0 управления формируется сигнал на включение первого триггера 8-1-1 этого канала управления. С выхода данного триггера 8-1-1 первого канала 7-1 управления управляющий сигнал поступает на элемент ИЛИ 3-1-0 первого блока 3-1 сборки и одновременно открывает элемент И 3-1-1. После исполнения команды исполнительный элемент 4-1, запускаемый сигналом с выхода схемы ИЛИ 3-1-0, посьшает сигнал на элементы И блока 3-1 сборки, который проходит открытый элемент И 3-1-1 и запускает второй триггер 8-1-2 первого канала управления, управляющий сигнал с выхода которого сбрасывает предыдущий триггер 8-1-1 и запускает через блок 3-2 сборки второй исполнительный элемент 4-2 и т.д. Сигнал об окончании работы последнего исполни5

0

5

тельного элемента А-п через блок 3-п сборки сбрасывает последний триггер 8-1-п первого канала управления и

пи и да

через элемент ИЛИ 11 запускает следую-, заны с выходами o6beKTF{bix датчиков, г щий канал управления. Сигнал подает- , входы которых являются информационны

ся на вход триггера 13 памяти, возвращая его в положение логической 1 и тем самым подготавливая к приему с дешифратора нового входного сигнала. Если программа управления не содержала, например, первой подпрограммы, то триггер 13 канала 7-1 управления Лудет находиться в состоянии I, с выхода элемента НЕ 12 на вход элемента И 10 подается сигнал, открывая его, в результате чего сигнал, поступивший на вход 18 запуска первого канала 7-1 управления, через открытый элемент И 10 и элемент ИЛИ 11 поступит на вход 18 следующего канала управления. По окончании т-й подпрограммы либо после трансляции сигнала запуска через элементы И 10 и ИЛИ 11 канала 7-(m-l) с выхода 19 канала 7-т управления сигнал поступает на вход своего триггера 13 памяти, как и в предыдущем канапе, а также на вход триггера 28, переводя его в положение логической 1, и элемента И 27 блока 23.

Формула изобретения

исходное положение, второй вывод

I

соединен с установочными входами всех каналов управления управляющий вход каждого из которых, кроме перво го, связан с управляющим выходом предыдущего канала управления, информационные входы-выходы всех каналов управления подключены соответственно к информационным выходам и входам блока управления объектом, входы ваписи команд всех каналов управления и входы элемента ШШ соединены с выходами дешифратора, входы которого свн-

ми входами устройства, о т л и ч а ю- щ е е с я тем, что, с целью повышения качества управления путем устранения потерь управляющих команд, в устройство введен блок управления входными сигналами, первый вход которого соединен с выходом элемента ИЛИ, второй вход - с вторым выводом ключа,

третий вход - с управляющим выходом последнего канала управления, первый выход - с дополнительным входом элемента ИЛИ, а второй выход - с управляющим входом первого канала управления.

I

первый и второй триггеры, первый, второй и третий элементы И и элемент НЕ, выход которого соединен с первым входом первого элемента И, а вход и первый вход второго элемента И - с

инверсным выходом первого триггера, нулевой вход которого и единичный вход второго триггера связаны с выхо дом первого элемента И, являкяцимся вторым выходом блока, первый вход

блока подключен к вторым входам первого и второго элементов И, первый вход третьего элемента И и единичный вход первого триггера служат третьим входом блока, выход второго элемента

и соединен с нулевым входом третьего триггера, ииверсный выход которого связан с вторым входом третьего элемента И, выход которого является первым выходом блока, второй вход которого подключен к единичным входам первого и второго триггеров.

соединен с единичным входом триггера памяти.

evj со

Авторы

Даты

1988-05-23—Публикация

1986-05-30—Подача