1

Предлагаемое Мзобретение относйтсй к вы 1ислительной технике «, в частности, к организации структур устройств управления каналами ввода-вывода,

Известны устройства управления каналами, содержащие блоки запросов на передачу данЬых, блок управляющих сигналов и блоки сборки и передач, связанные посредством соответствующих Щ1ИН с процессором.

С целью сокращения общего количества Шин, связывающих каналы ввода-вывода с процессором, расширения функциональных возможностей устройства, предлагаемое устройство управления каналами содержит дополнительно блок адресации регистров и триггеров управляемых каналов, блок запросов на микропрограммное прерывание, блоки сборки информационных и адресных шин и шин ключей защиты каналов, блоки коммутации информационных шин каналов и процессора и блоки управления коммутацией информационных щин.

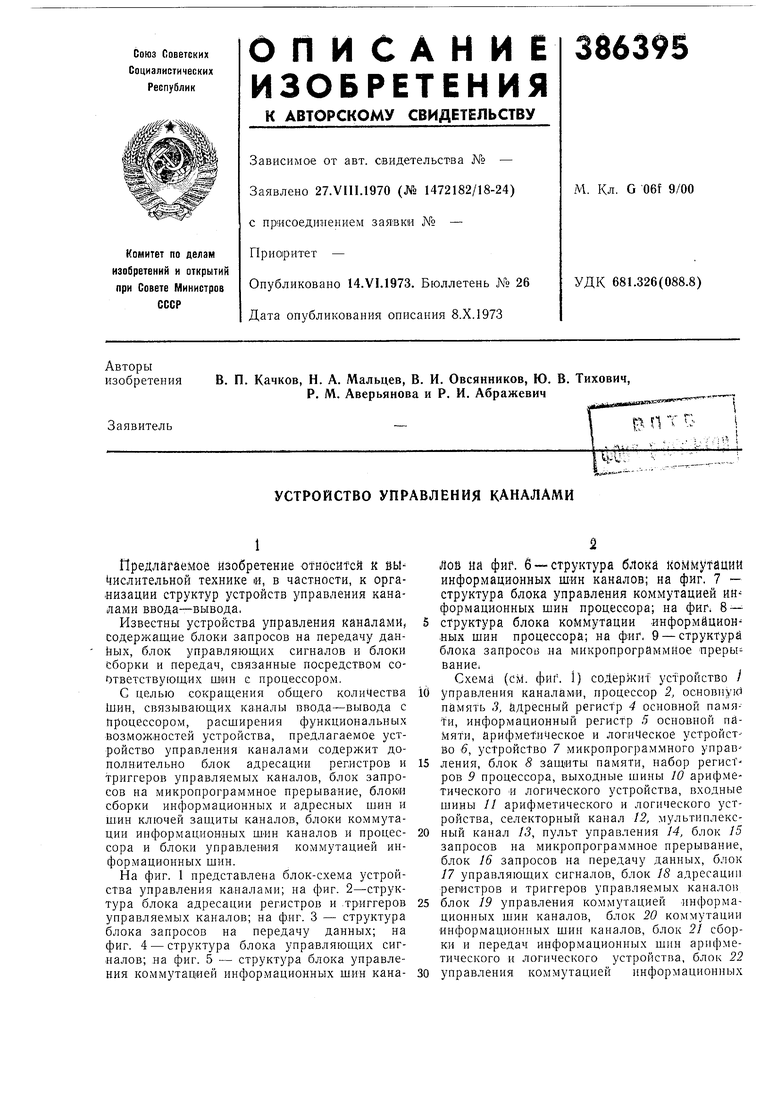

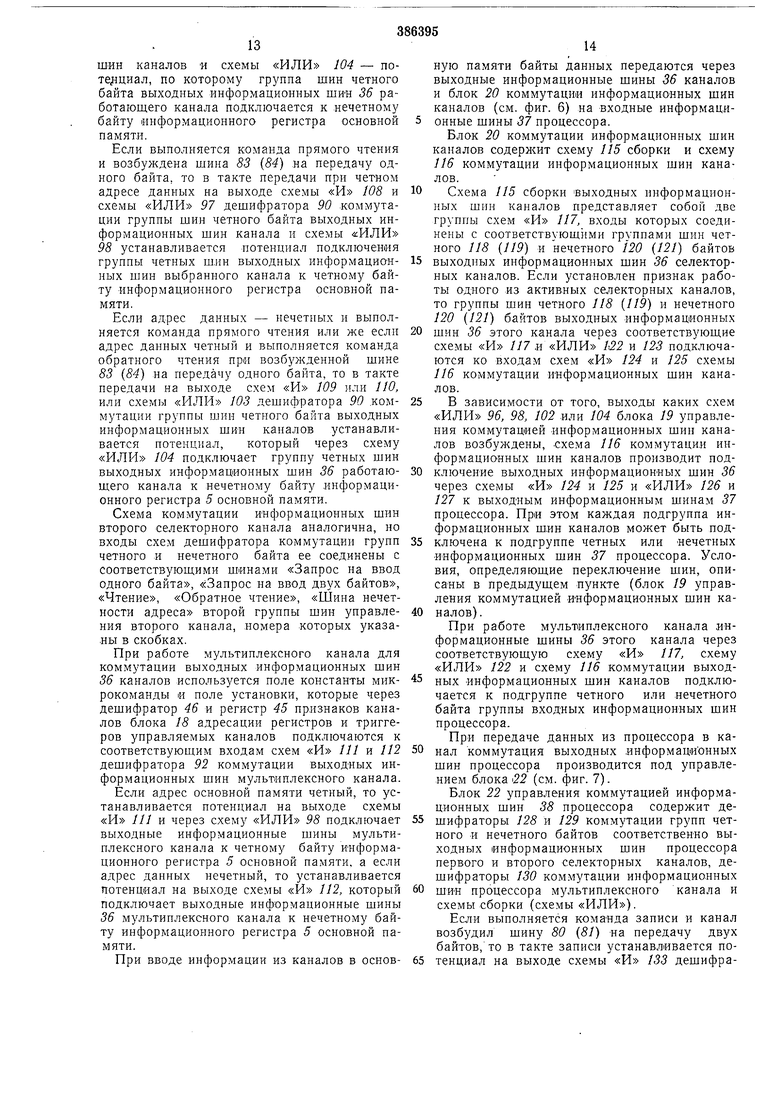

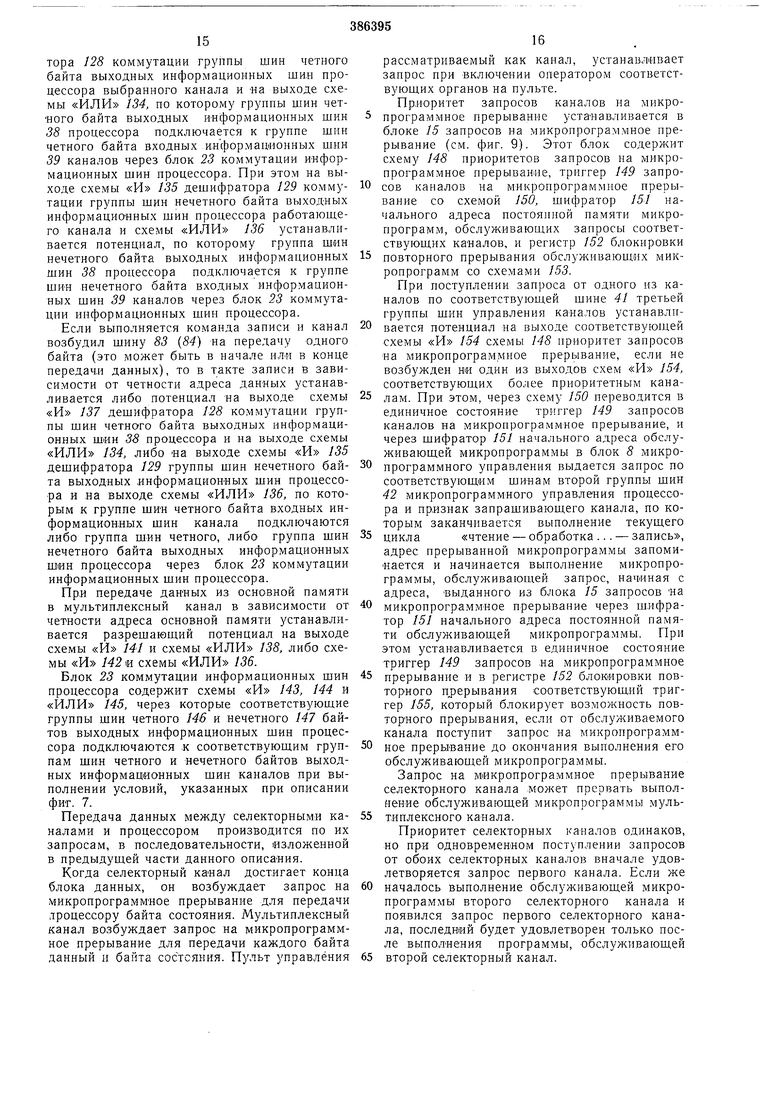

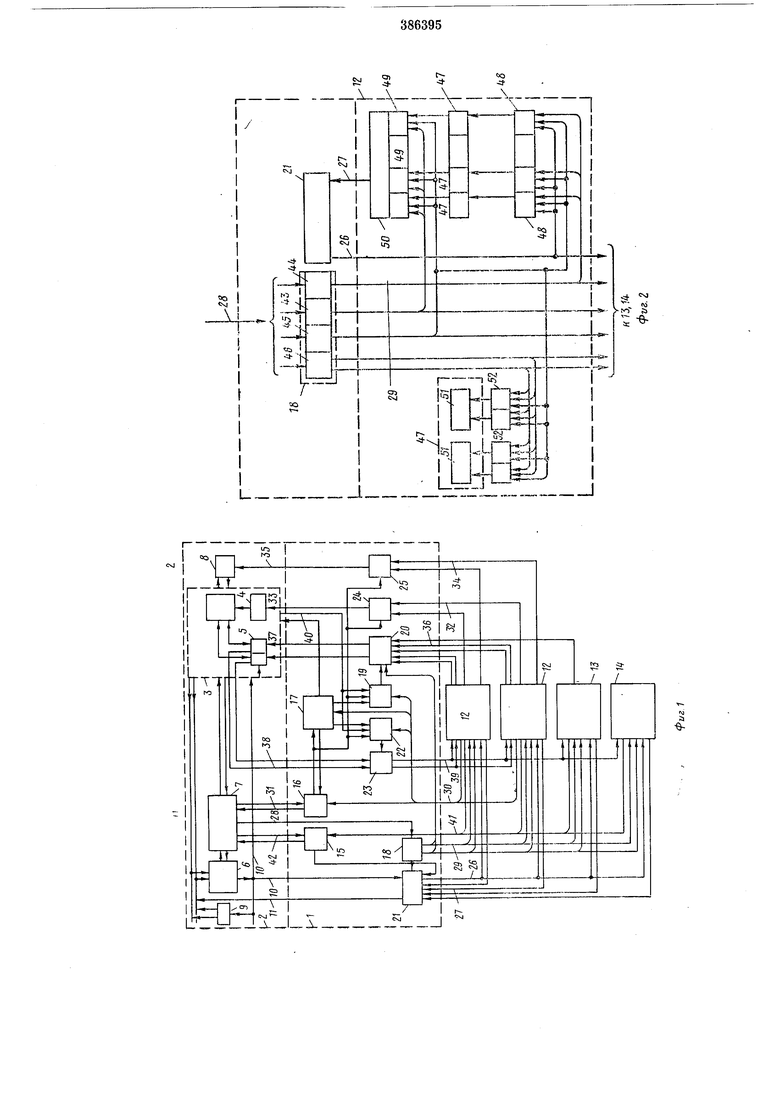

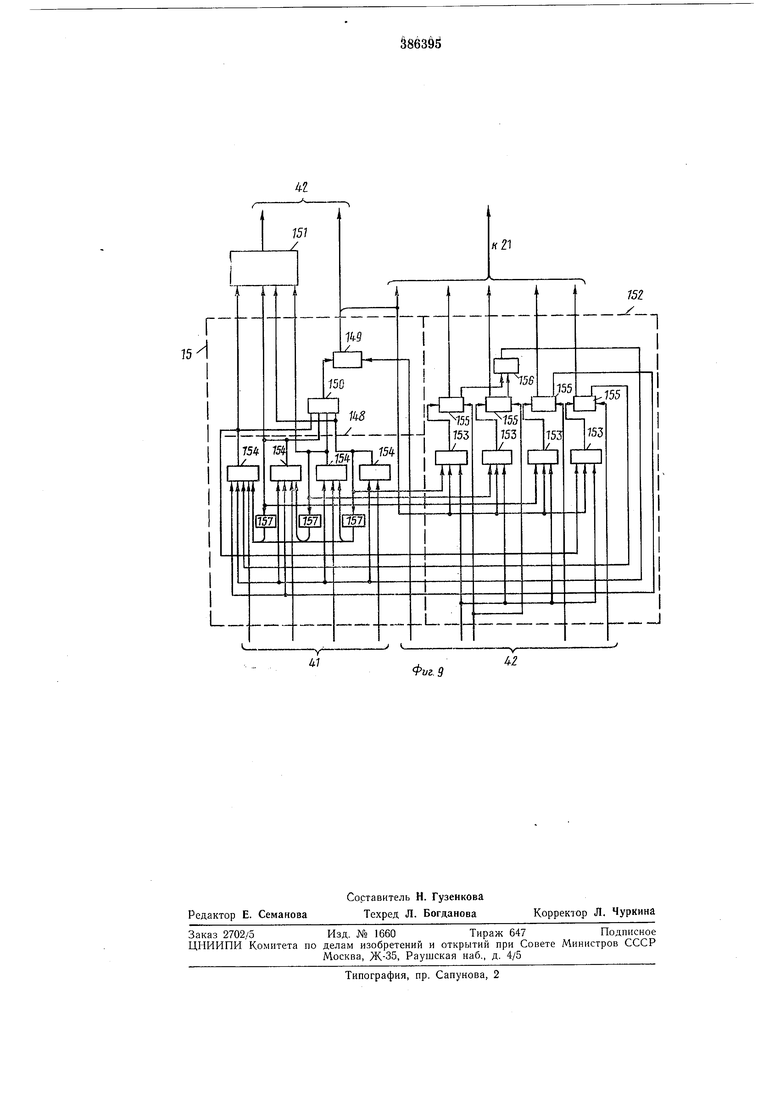

На фиг. 1 представлена блок-схема устройства управления ка.налами; на фиг. 2-структура блока адресации регистров и .триггеров управляемых каналов; на фиг. 3 - структура блока запросов на передачу данных; на фиг. 4 - структура блока управляющих сигналов; на фиг. 5 - структура блока управления коммутацией информационных шин каналой на фиг. б -структура блока коммутации

информационных ШИН каналов; на фиг. 7 -

структура блока управления коммутацией ин

формационных щин процессора; на фиг 8 -

структура блока коммутации информйцион

ных шин процессора; на фиг. 9 - структура

блока запросов на микропрограммное иреры

вание

Схема (см. фиг 1) содержит устройство /

управления каналами, процессор 2, основнукЗ память 3, адресный регистр 4 основной памяТи, информационный регистр 5 основной памяТи, арифметическое и логическое устройст-во 6, устройство 7 микропрограммного управления, блок 8 защиты памяти, набор регистров 9 процессора, выходные щины 10 арифметического и логического устройства, входные щины 11 арифметического и логического устройства, селекторный канал 12, мультиплексный канал 13, пульт управления 14, блок 15 запросов на микропрограммное прерывание, блок 16 запросов на передачу данных, блок 17 управляющих сигналов, блок 18 адресации регистров и триггеров управляемых канало

блок 19 управления коммутацией информационных шин каналов, блок 20 коммутации информационных шин каналов, блок 21 сборки и передач информационных шин арифметического и логического устройства, блок 22

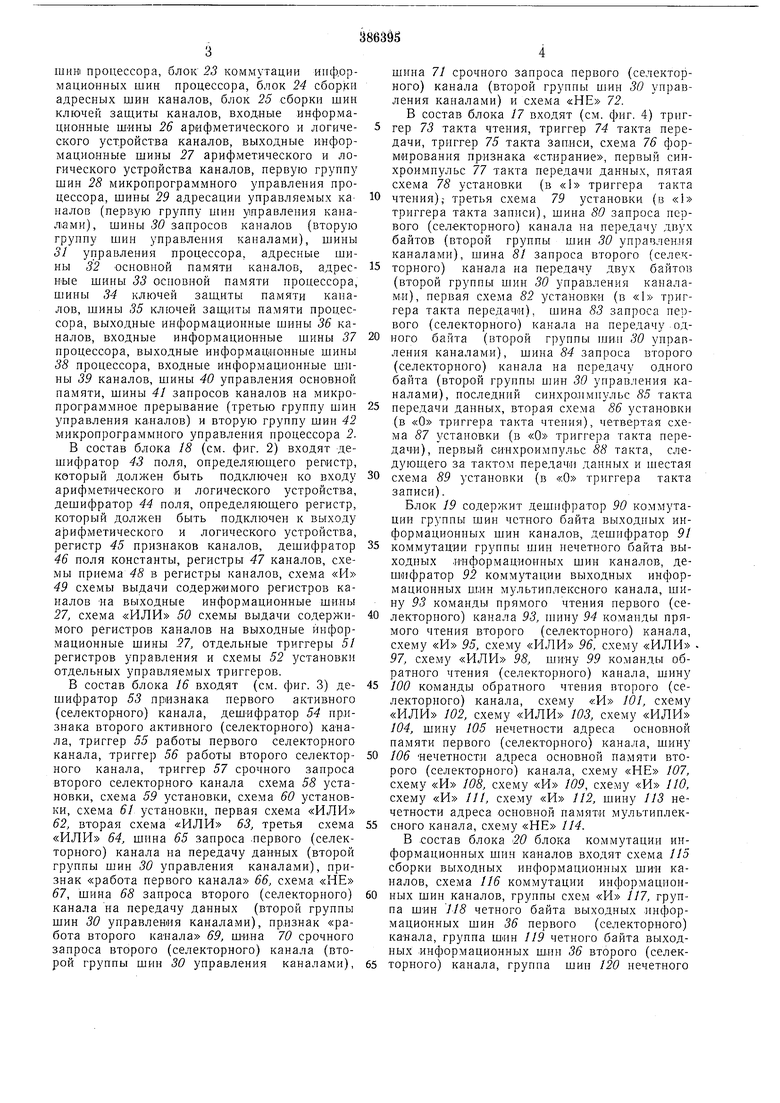

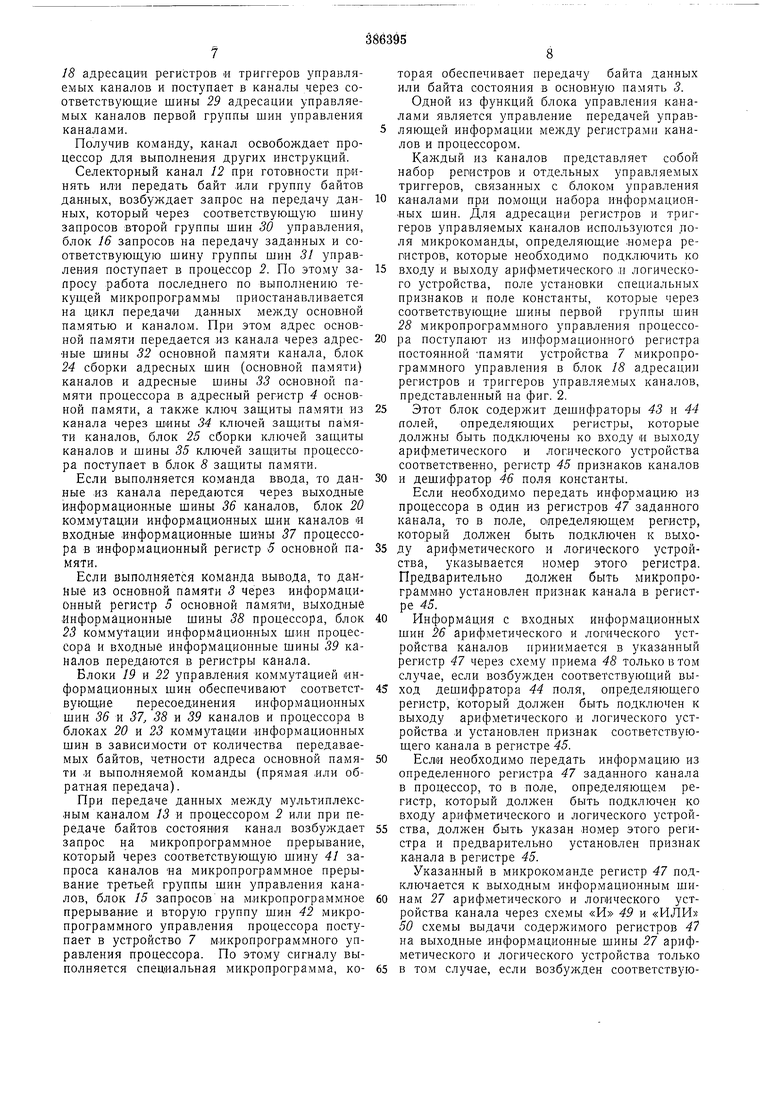

управления коммутацией информационных ШИН1 процессора, блок 23 коммутации ицф.ормационных шин процессора, блок 24 сборкп адресных шин каналов, блок 25 сборки шин ключей защиты каналов, входные информационные шины 26 арифметического и логического устройства каналов, выходные информационные шины 27 арифметического и логического устройства каналов, первую группу шин 28 микропрограммного управления процессора, шины 29 адресации управляемых каналов (первую группу шин управления каналами), шины 30 запросов каналов (вторую группу шин управления каналами), шины 31 управления процессора, адресные шины 32 основной памяти каналов, адресное шины 33 основной памяти процессора, шины 34 ключей защиты памяти каналов, шины 35 ключей защиты памяти процессора, выходные информационные шины 36 каналов, входные ин4зормационяые щины 37 процессора, выходные информационные шины 38 процессора, входные информационные шины 39 каналов, шины 40 управления основной памяти, шины 41 запросов каналов на микропрограммное прерывание (третью группу шин управления каналов) и вторую группу шин 42 микропрограммного управления процессора 2. В состав блока 18 (см. фиг. 2) входят дешифратор 43 поля, определяющего регистр, который должен быть подключен ко входу арифметического и логического устройства, дещифратор 44 поля, определяющего регистр, который быть подключен к выходу арифметического и логического устройства, регистр 45 признаков каналов, дешифратор 46 поля константы, регистры 47 каналов, схемы прнема #.§ в регистры каналов, схема «И 49 схемы выдачи содержимого регистров каналов На выходные информационные шины 27, схема «ИЛИ 50 схемы выдачи содержимого регистров каналов на выходные информационные шины 27, отдельные триггеры 51 регистров управления и схемы 52 установки отдельных управляемых триггеров. В состав блока 16 входят (см. фиг. 3) дещифратор 53 признака первого активного (селекторного) канала, дешифратор 54 признака второго активного (селекторного) канала, триггер 55 работы первого селекторного канала, триггер 56 работы второго селекторного канала, триггер 57 срочного запроса второго селекторного канала схема 58 установки, схема 59 установки, схема 60 установки, схема 61 установки, первая схема «ИЛИ 62, вторая схема «ИЛИ 63, третья схема «ИЛИ 64, шина 65 запроса .первого (селекторного) канала на передачу данных (второй группы шин 30 управления каналами), признак «работа первого канала 66, схема «НЕ 67, шина 68 запроса второго (селекторного) канала на передачу данных (второй группы шин 30 управления каналами), признак «работа второго канала 69, ш-ина 70 срочного запроса второго (селекторного) канала (второй группы шин 30 управления каналами). шина 71 срочного запроса первого (селекторного) канала (второй группы шин 30 управления каналами) и схема «НЕ 72. В состав блока 17 входят (см. фиг. 4) триггер 73 такта чтения, триггер 74 такта передачи, триггер 75 такта записи, схема 76 формировання признака «стирание, первый синхроимпульс 77 такта передачи данных, пятая схема 78 установки (в «I триггера такта чтения),- третья схема 79 установки (в «1 триггера такта записи), шина 80 запроса первого (селекторного) канала на передачу двух байтов (второй группы шин 30 управления каналами), шина 81 запроса второго (селекторного) канала на передачу двух байтов (второй группы шин 30 управления каналами), первая схема 82 установки (в «1 триггера такта передачи), шина 83 запроса первого (селекторного) канала на передачу одного байта (второй группы шил 30 управления каналами), шина 84 запроса второго (селекторного) канала на передачу одного байта (второй группы шин 30 управления каналами), последний синхроимпульс 85 такта передачи данных, вторая схема 86 установки (в «О триггера такта чтения), четвертая схема 87 установки (в «О триггера такта передачи), первый синхроимпульс 88 такта, следующего за тактом передачи данных и шестая схема 89 установки (в «О триггера такта записи). Блок 19 содержит дешифратор 90 коммутации группы шин четного байта выходных информационных шин каналов, дешифратор 91 коммутации группы щин нечетного банта выходных информационных щин каналов, дещифратор 92 коммутации выходных информационных шин мультиплексного канала, шину 93 команды прямого чтения первого (селекторного) канала 93, нишу 94 команды прямого чтения второго (селекторного) канала, схему «И 95, схему «ИЛИ 96, схему «ИЛИ 97, схему «ИЛИ 98, шину 99 команды обратного чтения (селекторного) канала, шину 100 команды обратного чтения второго (селекторного) канала, схему «И 101, схему «ИЛИ /612, схему «ИЛИ 103, схему «ИЛИ 104, шину 105 нечетности адреса основной памяти первого (селекторного) канала, шину 106 нечетности адреса основной памяти второго (селекторного) канала, схему «НЕ 107, схему «И 108, схему «И 109, схему «И 110, схему «И 111, схему «И 112, шину 113 нечетности адреса основной па.мяти мультиплексиого канала, схему «НЕ 114. В .состав блока 20 блока коммутации информационных шин каналов входят схема 115 сборки выходных информационных шин каналов, схема 116 коммутации информационных шин каналов, грунпы схем «И 117, группа шин 118 четного байта выходных информационных шии 36 первого (селекторного) канала, группа щин 119 четного байта выходных информационных щин 36 второго (селекторного) канала, группа шин 120 нечетного

байта выходных информационных шин 36 первого (селекторного) канала, группа шин i21 Нечетного байта выходных информацион.ных шин 36 второго (селекторного) канала, схема «ИЛИ 122, схема «ИЛИ 123, схема «И 124, схема «И 125, схема «ИЛИ 126 и схема «ИЛИ 127.

В состав блока 22 управления коммутацией информационных шин процессора входят дешифратор 128 коммутации группы шлн четного байта выходных информационных шин процессора первого (второго селекторного) канала, дешифратор 129 коммутации группы шин нечетного байта выходных информационных шин процессора первого (второго селекторного) канала, дешифратор 130 коммутации информационных шин процессора мультиплексного канала, шина 131 команды записи первого селекторного канала, шина 132 кома.нды-записи второго селекторного канала, схема «И 133, схема «ИЛИ 134, схема «И 135, схема «ИЛИ 136, схема «И 137, схема «ИЛИ 138, схема «НЕ 139, схема «НЕ 140, схема «И 141 и схема «И 142.

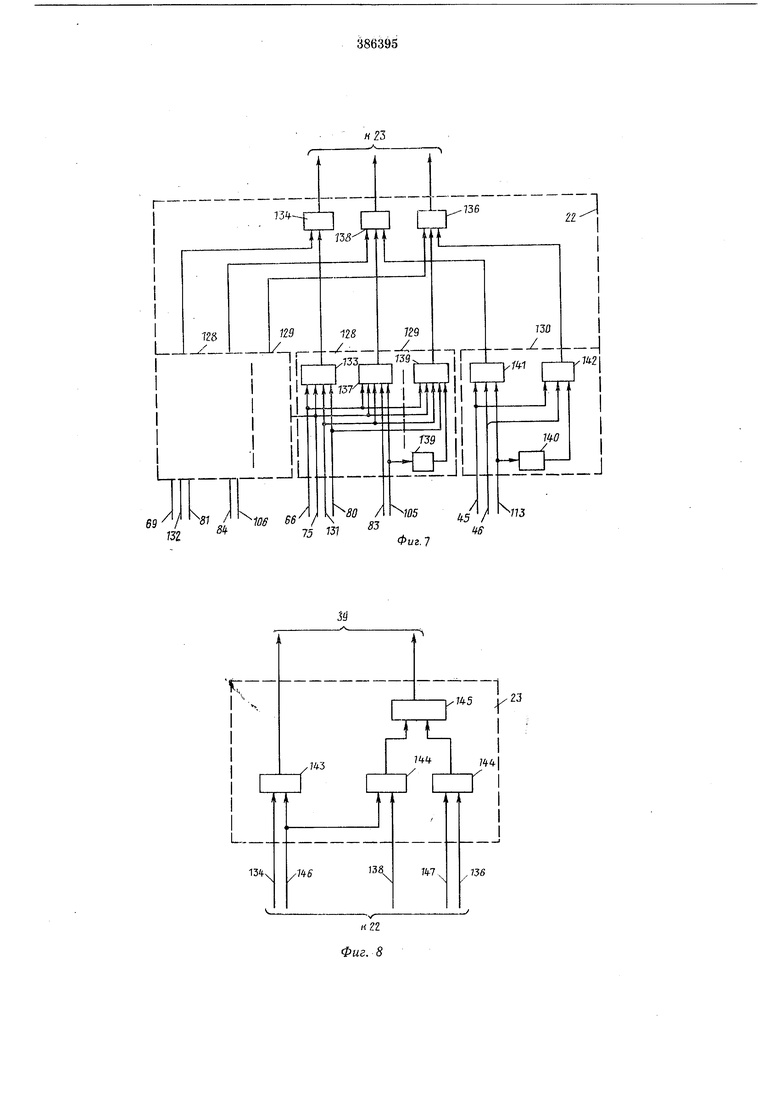

Блок 23 коммутации информационных шин процессора содержит схему «И 143, схему «И 144, схему «ИЛИ 145, группу шин 146 четного байта выходных информационных шин процессора и группу шин 147 нечетного байта выходных информационных шин процессора.

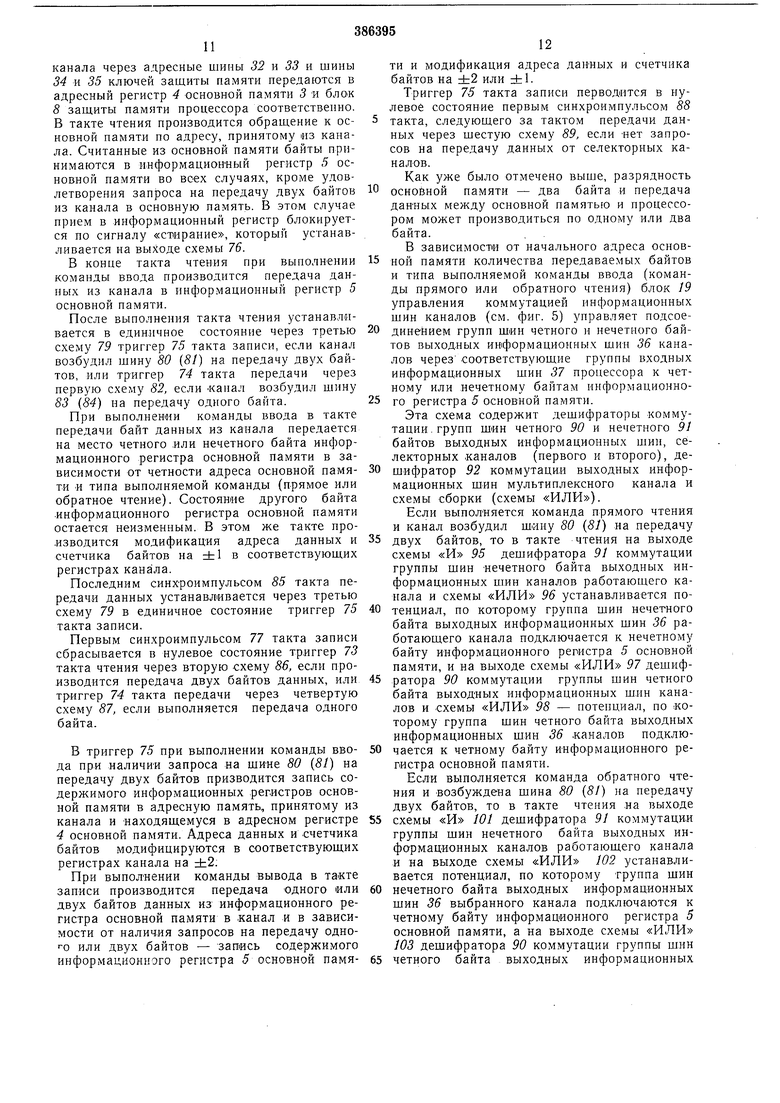

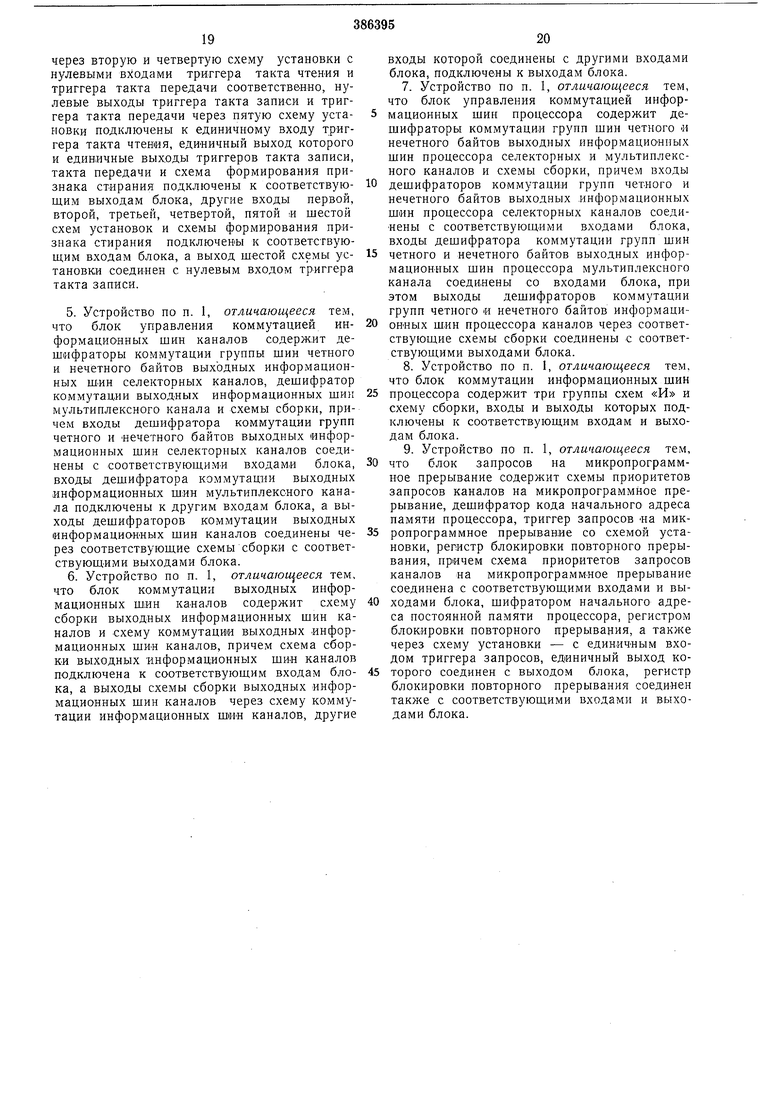

В состав блока 15 запросов на микропрограммное прерывание входят схема 148 приоритетов запросов каналов на микропрограммное прерывание, триггер 149 запросов каналов на микропрограммное прерывание, схема 150 установки в «1 триггера 149, шифратор 151 начального адреса постоянной памяти, регистр 157 блокировки повторного прерывания, схемы 153 установок регистра 152, схема «И 154, триггеры 155 регистра 152, схема «ИЛИ 156 и схема «НЕ /57.

Устройство / управления каналами, представленное на фиг. 1, предназначено для подключения к процессору каналов ввода -вывода и управления передачей данных между ними.

Процессор 2 содержит основную память 3 t адресным 4 и информационным 5 регистрами, арифметическое и логическое устройство 6, устройство 7 микропрограммного управления с постоянной памятью, адресным и информационным регистрами, блок 8 зашиты памяти, набор регистров 9, связанных между собой и основной памятью при помощи системы обш,их шин 10 и 11.

Через предлагаемое устройство / к процессору могут быть подключены две селекторных канала 12, один мультиплексный канал 13 и пульт управления 14, рассматриваемый как канал.

Каждый из каналов содержит набор регистров, отдельных управляемых триггеров, логических схем и необходимых шин.

Устройство 1 управления каналами состоит

из блока 15 запросов на микропрограммное прерывание, блока 16 запросов на передачу данных, блока 17 управляюш.их сигналов, блока М адресации регистров и -триггеров управляемых каналов, блока 19 управления коммутацией информационных шин каналов, блока 20 коммутации информационных шин каналов, блока 21 сборки и передач информационных шин арифметического и логического устройства, блока 22 управления коммутацией информационных шин процессора, блока 23 коммутации информационных шйн процессора, блоков 24 и 25 сброки адресных шин и шин ключей зашиты каналов соответственно.

Совокупность блоков 15-25 позволяет сократить количество шин, связывающих каналы с процессором, и рассматривать их как один физически подключенный к процессору

канал.

Управление вычислительной системой, в которой применено рассматриваемое устройство / управления каналами, осуществляется программно с использованием системы команд,

которые реализуются микропрограммно. Одной из основных системных функций является управление передачей данных между упомянутыми подсистемами. Операция передачи данных начинается по

специальной инструкции, которая задает адрес ка.нала и устройства ввода-вывода и при помощи специальных управляющих слов указывает код команды, начальный адрес основной памяти, количество байтов данных,

которые необходимо передать, управляющие признаки и ключ защиты. Канал формирует управляющее слово устройства и хранит его на своих регистрах или в специальной памяти,

Передача управляющей информации между процессором и регистрами каналов производится через арифмет1ическое и логическое устройство в, выходные информационные шины 10 арифметического и логического устройства

(процессора), блок 21 сборки и передач ннформационных шин арифметического л логического устройства и входные информационные шины 26 арифметического и логического устройства каналов.

Состояние регистров каналов может быть микропрограммно проанализировано через выходные информационные шины 27 арифметического и логического устройства каналов, блок 21 сборки и передач информационных

шин арифметического и логического устройства и входные шины 11 арифметического и логического устройства.

При передаче управляюп1ей информации между процессором 2 и регистрами каналов

12-14 признак регистра, в который необходимо принять или из которого необходимо выдать информацию, указывается в микрокоманде, принимается через соответствующие шины первой группы шин 28 микропрограммного управления процессора в блок

18 адресации регистров и триггеров управляемых каналов и поступает в каналы через соответствующие шины 29 адресации управляемых каналов первой группы шин управления каналами.

Получив команду, канал освобождает процессор для выполнения других инструкций.

Селекторный канал 12 при готовности принять или передать байт .или группу байтов дан.ных, возбуждает запрос на передачу данных, который через соответствующую щину запросов второй группы шин 30 управления, блок 16 запросов на передачу заданных и соответствующую щину группы щин 31 управлен-ия поступает в процессор 2. По этому запросу работа последнего по выполнению текущей микропрограммы приостанавливается на цикл передачи данных между основной памятью и каналом. При этом адрес основной памяти передается из канала через адресные щины 32 основной памяти канала, блок 24 сборки адресных щин (основной памяти) каналов и адресные щины 33 основной памяти процессора в адр есный регистр 4 основной памяти, а также ключ защиты памяти из канала через шины 34 ключей защиты памяти каналов, блок 25 сборки ключей защиты каналов и щины 35 ключей защиты процессора поступает в блок 8 защиты памяти.

Если выполняется команда ввода, то данные из канала передаются через выходные информациойные щины 36 каналов, блок 20 коммутации информационных шин каналов и входные информацион-ные шииы 37 процессора в информационный регистр б основной памяти.

Если выполняется команда вывода, то данные из основной памяти 3 через информационный регистр 5 основной памяти, выходные информационные щины 38 процессора, блок 55 коммутации информационных шин процессора и входные информационные шины 39 каналов передаются в регистры канала.

Блоки 19 и 22 управления коммутацией информационных шин обеспечивают соответствующие пересоединения информационных шин 36 и 37, 38 и 39 каналов и процессора в блоках 20 и 23 коммутации информационных шин в зависимости от количества передаваемых байтов, четности адреса основной памяти и выполняемой команды (прямая или обратная передача).

При передаче данных между мультиплексным каналом 13 и процессором 2 или при передаче байтов состояния канал возбуждает запрос на микропрограммное прерывание, который через соответствующую шину 41 запроса каналов на микропрограммное прерывание третьей группы щин управления каналов, блок 15 запросов на микропрограммное прерывание и вторую группу шин 42 микропрограммного управления процессора поступает в устройство 7 микропрограммного управления процессора. По этому сигналу выполняется специальная микропрограмма, которая обеспечивает передачу байта данных или байта состояния в основную память 5.

Одной из функций блока управления каналами является управление передачей управляющей информации между регистрами каналов и процессором.

Каждый из каналов представляет собой набор регистров и отдельных управляемых триггеров, связанных с блоком управления

каналами при помоши набора информационных щин. Для адресации регистров и триггеров управляемых каналов используются поля микрокоманды, определяющие .номера регистров, которые необходимо подключить ко

входу и выходу арифметического и логического устройства, поле установки специальных признаков и поле константы, которые через соответствующие шины первой группы шин 28 микропрограммного управления процессора поступают из информационного регистра постоянной памяти устройства 7 микропрограммного управления в блок 18 адресации регистров и триггеров управляемых каналов, представленный на фиг. 2.

Этот блок содержит дешифраторы 43 и 44 полей, определяющих регистры, которые должны быть подключены ко входу и выходу арифметического и логического устройства соответственно, регистр 45 признаков каналов

и дешифратор 4€ поля константы.

Если необходимо передать информацию из процессора в один из регистров 47 заданного канала, то в поле, определяющем регистр, который должен быть подключен к выходу арифметического и логического устройства, указывается номер этого регистра. Предварительно должен быть микропрограммно установлен признак канала в регистре 45.

Информация с входных информационных Шин 26 арифметического и логического устройства каналов принимается в указанный регистр 47 через схему приема 48 только в том случае, если возбужден соответствующий выход дещифратора 44 поля, определяющего регистр, который долж.ен быть подключен к выходу арифметического и логического устройства и установлен признак соответствующего канала в регистре 45.

Если необходимо передать информацию из определенного регистра 47 заданного канала в процессор, то в поле, определяющем регистр, который должен быть подключен ко входу арифметического и логического устройства, должен быть указан номер этого регистра и предварительно установлен признак канала в регистре 45.

Указанный в микрокоманде регистр 47 подключается к выходным информационным щинам 27 арифметического и логического устройства канала через схемы «И 49 и «ИЛИ 50 схемы выдачи содержимого регистров 47 на выходные информационные шины 27 арифметического и логического устройства только

в том случае, если возбужден соответствующий выход дешифратора 43 поля, определяющего регистр, который должен быть подключен ко входу арифметического и логического устройства, и установлен признак в регистре 45. Для установки отдельных триггеров 51 в регистрах управления каналов в определенные состояния используется поле константы микрокоманды. Дешифратор 46 константы имеет две группы выходов, которые через соответствующие шины 29 адресации управляемых каналов первой группы шин управления каналов, поступают в каналы. Каждый из отдельных триггеров 51 может быть установлен в нулевое или единичное состояние через соответствующую схему 52 установки (схему «И), если возбуждены соответствующие выходы дешифратора 46 константы микрокоманды, установлен признак канала в регистре 45 и возбужден соответствующий выход дешифратора 44 поля микрокоманды, определяющего регистр, который должен быть подключен к выходу арифметического и логического устройства. Каналы, приняв управляющую информацию, освобождают процессор. Передача данных между каналами и процессором может производиться одновременно с выполнением других инструкций и работой других каналов в порядке поступления запросов на передачу данных. Приоритет запросов селекторяых каналов определяется в блоке 16 запросов на передачу даиных (см. фиг. 3). Этот блок содержит дешифраторы 53 и 54 признаков активных каналов, триггеры 55 и 56работы каналов и триггер 57 срочного запроса второго канала со схемами 58-61 установок и схемы «ИЛИ 62-64. При возбуждении щины 65 запроса на перадачу данных первого (селекторного) канала второй группы шин 30 управления каналов устанавливается признак «работа первого канала 66 через дешифратор 53 первого активного канала в первую схему «ИЛИ 62, если не установлены в единичное состояние триггер 55 работы второго канала и триггер 57срочного запроса второго канала. Выход первой схемы «ИЛИ 62 («работа первого канала 66 через схему 58 связан с единичным установочным входом триггера 55 работы первого канала, единичное состояние которого поддерживает возбужденным признак «работа первого канала 66 после запроса первого канала на передачу данных. Выход первой схемы «ИЛИ 62 .соединен также через схему «НЕ 67 со входом дешифратора 54 признака второго активного канала, второй вход которого соединен с шиной 68 запроса второго канала на передачу данных второй группы шин 30 управления каналов. Выход дешифратора 54 признака второго активного канала («работа второго канала 69 через вторую схему «ИЛИ 63 и вторую схему 58 соединен с единичным установочным входом триггера 56 работы второго канала, единичное состояние которого поддерживает возбужденным выход второй схемы «ИЛИ 63 после сброса запроса второго канала на передачу данных. Выходы первой и второй схем «ИЛИ 62 и 63 соединены через третью схему «ИЛИ 64 и шину занроса каналов на передачу данных группы шин 31 управления процессора с устройством 7 микроирограммного управления. Если возбужден запрос на передачу давных только от одного канала, то устанавливается признак работы этого канала и остается возбужденным до конца выполнения цикла передачи данных между каналом и процессором, т. е. до сброса триггера работы соответствуюшего канала в нулевое состояние через схему 59. Если возбуждены запросы на передачу данных от обоих каналов одновременно, то вначале устанавливается признак работы первого канала и здовлетворяется его запрос. Обычно приоритет запроса на передачу данных первого канала выше, чем приоритет запроса на передачу данных второго канала. Но если во втором канале возбуждена шина 70 срочного запроса на передачу данных, а в первом канале срочного запроса не возникло, то через схему 60 устанавливается в единичное состояние триггер 57 срочного запроса второго канала на передачу данных и блокируется дешифратор 53 признака первого активного канала, если возбужден запрос первого канала на передачу данных. Срочный запрос возбуждается каналом в том случае, если -его буфер данных заполнен (в случае ввода) или пуст (в случае вывода). Триггер срочного запроса второго канала устанавливается в нулевое состояние через схему 61 одним из синхроимпульсов процессора, если срочный запрос канала сброшен. По запросу каналов на передачу данных устройство микропрограммного управления приостанавливает выполнение текущей микропрограммы и выполняет цикл передачи данных, состоящий из последовательности определенных тактов передачи данных каналом и процессором. Для задания последовательности тактов используется блок 17 управляющих сигналов (см. фиг. 4), который содержит триггер 73 такта чтения, триггер 74 такта передачи и триггер 75 такта записи и схему 76 формирования признака «стирание со схемами установок. Для выполнения каждого такта процессор вырабатывает специальную серию тактирующих синхроимпульсов. По первому синхроимпульсу 77 такта передачи данных, если установлен признак «работа первого канала 66 или «работа второго канала 69 через пятую схему 78, представляющую собой последовательно соединенные схемы «И и «ИЛИ, ус танавливается в единичное состояние триггер 73 такта чтения, и выполняется такт чтения, в котором адрес основной памяти и ключ защиты памятки из соответствующих регистров

11

канала через адресные шины 32 тл 33 ii шины 34 и 35 ключей защиты памяти нередаются в адресный регистр 4 основной памяти 3 и блОК 5 защиты памяти процессора соответственно. В такте чтения производится обращение к основной памяти по адресу, принятому из канала. Считанные из основной памяти байты принимаются в ийформационный регистр 5 основной памяти во всех случаях, кроме удовлетворения запроса на передачу двух байтов из канала в основную память. В этом случае прием в информационный регистр блокируется по сигналу «стирание, который устанавливается на выходе схемы 76.

В конце такта чтения при выполнении команды ввода производится передача данных из канала в информационный регистр 5 основной памяти.

После выполнення такта чтения устанавливается в единичное состояние через третью схему 79 триггер 75 такта записи, если канал возбудил щину 80 (81) на передачу двух байтов, или триггер 74 такта передачи через первую схему 82, если .канал возбудил шину 83 (84) на передачу одного байта.

При выполнении команды ввода в такте передачи байт данных из канала передается на место четного .или нечетного байта информационного регистра основной памяти в зависимости от четности адреса основной памяти -и типа выполняемой команды (прямое или обратное чтение). Состояние другого байта .информационного регистра основной памяти остается неизменным. В этОМ же такте про.изводится модификация адреса данных и счетчика байтов на ±1 в соответствующих регистрах канала.

Последним синхроимпульсом 85 такта передачи данных устанавливается через третью схему 79 в единичное состояние триггер 75 такта записи.

Первым синхроимпульсом 77 такта записи сбрасывается в нулевое состояние тр.иггер 73 такта чтения через вторую .схему 86, если производится передача двух байтов данных, или триггер 74 такта передачи через четвертую схему 87, если выполняется передача одного байта.

В триггер 75 при выполнении команды ввода при наличии запроса на ши-не 80 (81) на передачу двух байтов призводится запись содержимого информационных регистров основной памяти в адресную память,, принятому из канала и находящемуся в адресном регистре 4 основной памяти. Адреса данных и .счетчика байтов модифицируются в соответствующих регистрах канала на ±2;

При выполнении команды вывода в такте записи производится передача одного или двух байтов данных из информационного регистра основной памяти в .канал и в зависимости от наличия запросов на передачу одноо или двух байтов - запись содержимого информационного регистра 5 основной памя12

ти и модификация адреса данных и счетчика байтов на ±2 или ±1.

Триггер 75 такта записи перводится в нулевое состояние первым синхроимпульсом 88 5 такта, следующего за тактом передачи данных через шестую схему 89, если -нет запросов на передачу данных от селекторных каналов.

Как уже было отмечено выще, разрядность

0 оснобной памяти - два байта и передача данных между основной памятью и процессором может производиться по одному или два байта. В зависимости от начального адреса основной памяти количества передаваемых байтов и типа выполняемой команды ввода (команды прямого или обратного чтения) блок 19 управления коммутацией информационных шин каналов (см. фиг. 5) управляет подсоединением групп шин четного и нечетного байтов выходных информационных шин 36 каналов через соответствующие группы входных информационных щин 37 процессора к четному или нечетному байтам информационно5 го регистра 5 основной памяти.

Эта схема содержит дешифраторы коммутации, групп шин четного 90 и нечетного 9/ байтов выходных информационных шин, селекторных .каналов (первого и второго), дешифратор 92 коммутации выходных информационных щин мультиплексного канала и схемы сборки (схемы «ИЛИ).

Если выполняется команда прямого чтения и канал возбудил шану 80 (81) на передачу

5 двух байтов, то в такте чтения на выходе схемы «И 95 дешифратора 91 коммутации группы шин нечетного байта выходных информационных щин каналов работающего канала и схемы «ИЛИ 96 устанавливается потенциал, по которому группа шин нечетного байта выходных информационных шин 36 работающего канала подключается к нечетному байту информационного регистра 5 основной памяти, и на выходе схемы «ИЛИ 97 дешиф5 .ратора 90 коммутации группы шин четного байта выходных информационных шин каналов и схемы «ИЛИ 98 - потенциал, по которому группа шин четного байта выходных информационных щин 36 .каналов подключается к четному байту информационного регистра основной памяти.

Если выполняется команда обратного чтения и Возбуждена шина 80 (8) на передачу двух байтов, то в такте чтения .на выходе

5 схемы «И 101 дешифратора 91 коммутации группы щин нечетного байта выходных информационных каналов работающего канала и на выходе схемы «ИЛИ 102 устанавливается потенциал, по которому труппа щин

0 нечетного байта выходных информационных щин 36 выбранного канала подключаются к четному байту информационного регистра 5 основной памяти, а на выходе схемы «ИЛИ 103 дешифратора 90 коммутации группы щин

5 четного байта выходных информационных

13

шин каналов и схемы «ИЛИ 104 - потe циaл, по которому группа шин четного байта выходных информационных шин 36 работающего канала подключается к .нечетному байту информационного регистра основной памяти.

Если выполняется команда прямого чтения и возбуждена шина 83 (84 .на передачу одного байта, то в такте передачи при четном адресе данных на выходе схемы «И 108 и схемы «ИЛИ 97 дешифратора 90 коммутации группы шин четного байта выходных информационных шин канала и схемы :ИЛИ 98 устанавливается потенциал подключения группы четных ш.ин выходных информационных шин выбранного канала к четному байту информационного регистра основной памяти.

Если адрес данных - нечетных и выполняется команда прямого чтения или же если адрес данных четный и выполняется команда обратного чтения при возбужденной шине 83 (84) на передачу одного байта, то в такте передачи на выходе схем «И 109 или 110, или схемы «ИЛИ 103 дешифратора 90 .коммутации группы шин четного байта выходных информационных шин каналов устанавливается потенциал, который через схему «ИЛИ 104 подключает группу четных шин выходных информационных шин 36 работаюшего канала к нечетному байту .информационного регистра 5 основной памяти.

Схема коммутации информационных шин второго селекторного канала аналогична, но входы схем дешифратора коммутации групп четного и нечетного байта ее соединены с соответствующими шинами «Запрос на ввод одного байта, «Запрос на ввод двух байтов, «Чтение, «Обратное чтение, «Шина нечетности адреса второй группы шин управления второго канала, .номера которых указа.ны в скобках.

При работе мультиплексного канала для коммутации выходных информационных шин 36 каналов используется поле константы микрокоманды и поле установки, которые через дешифратор 46 и регистр 45 пр.изнаков каналов блока 18 адресации регистров и триггеров управляемых каналов подключаются к соответствуюшим входам схем «И 111 и 112 дешифратора 92 коммутации выходных информационных шин мультиплексного канала.

ЕСЛ.И адрес основной памяти четный, то устанавливается потенциал на выходе схемы «И 111 и через схему «ИЛИ 98 подключает выходные информационные шины мультиплексного канала к четному байту информационного регистра 5 основной памяти, а если адрес данных нечетный, то устанавливается потенциал на выходе схемы «И 112, который подключает выходные информационные шины 36 мультиплексного канала к нечетному байту информационного регистра 5 основной памяти.

При вводе информации из каналов в основ14

ную памяти байты данных передаются через выходные информационные шины 36 каналов и блок 20 коммутации информационных шин каналов (см. фиг. 6) на входные информационные шины 37 процессора.

Блок 20 коммутации информационных шин каналов содержит схему 115 сборки и схему 116 коммутации информационных шин каналов.

Схема 115 сборки выходных информационных шин каналов представляет собой две группы схем «И 117, входы которых соединены с соответствуюшйми группами шин четного 118 (119) и нечетного 120 (121) байтов

выходных информационных шин 36 селекторных каналов. Если установлен нризнак работы одного из активных селекторных каналов, то группы шин четного 118 (119) и нечетного 120 (121) байтов выходных информационных

шин 36 этого канала через соответствуюшие схемы «И /77 и «ИЛИ /i22 и 123 подключаются ко входам схем «И 124 и 125 схемы 116 коммутации информационных шин каналов.

В зависимости от того, выходы каких схем «ИЛИ 96, 98, 102 .или 104 блока 19 управления коммутацией информационных шин каналов возбуждены, .схема 116 коммутации информационных шин каналов производит подключение выходных информационных шин 36 через схемы «И 124 и 125 и «ИЛИ 126 и 127 к выходным информационным шинам 57 процессора. При этом каждая подгруппа информационных Ш.ИН каналов может быть подключена к подгруппе четных или нечетных информационных шин 37 процессора. Условия, определяющие переключение шин, описаны в предыдущем пункте (блок 19 управления коммутацией информационных шин каналов).

При работе мультиплексного канала информационные шины 36 этого канала через соответствующую схему «И 117, схему «ИЛИ 122 и схему 116 коммутации выходных информацио.нных шин каналов подключается к подгруппе четного или .нечетного байта группы входных информационных шин процессора. При передаче данных из процессора в канал коммутация выходных .информационных шин процессора производится под управлением блока 22 (см. фиг. 7).

Блок 22 управления коммутацией информационных шин 38 процессора содержит дешифраторы 128 и 129 коммутации групп четного и нечетного байтов соответственно выходных информационных шин процессора первого и второго селекторных каналов, дешифраторы 130 коммутации информационных

шин процессора мультиплексного канала и схемы сборки (схемы «ИЛИ).

Если выполняется команда записи и канал возбудил шину 80 (81) на передачу двух байтов, то в такте записи устанавливается потенциал на выходе схемы «И 133 дешифра15

тора 128 коммутации группы шин четного байта выходных информационных шин нроцессора выбранного канала и «а выходе схемы «ИЛИ 134, по которому группы шин четного байта выходных информационных шин

38процессора подключается к группе шин четного байта входных информационных шин

39каналов через блок 23 коммутации информационных шин процессора. При этом на выходе схемы «И 135 дешифратора 129 коммутации группы шин нечетного байта выходных информационных шин процессора работаюшего канала и схемы «ИЛИ 136 устанавливается потенциал, по которому группа шин нечетного байта выходных информационных шин 38 процессора подключается к группе шин нечетного банта входных информационных шин 39 каналов через блок 23 коммутации информационных шин процессора.

Если выполняется команда записи и канал возбудил шину 85 (84) на передачу одного байта (это может быть в начале ил« в конце передачи данных), то в такте записи в зависимости от четности адреса данных устанавливается либо потенциал на выходе схемы «И 137 дешифратора 128 коммутации группы шин четного байта выходных информационных шин 38 процессора и на выходе схемы «ИЛИ 134, либо на выходе схемы «И 135 дешифратора 129 группы шин нечетного байта выходных .информационных шин процессора и на выходе схемы «ИЛИ 136, по которым к группе шин четного байта входных информационных шин канала подключаются либо группа шин четного, либо группа шин нечетного байта выходных информационных шин процессора через блок 23 коммутации информационных шин процессора.

При передаче данных из основной памяти в мультиплексный канал в зависимости от четности адреса основной памяти устанавливается разрешающий потенциал на выходе схемы «И 141 и схемы «ИЛИ 138, либо схемы «И 142 и схемы «ИЛИ 136.

Блок 23 коммутации информационных шин процессора содержит схемы «И 143, 144 и «ИЛИ 145, через которые соответствующие группы шин четного 146 и нечетного 147 байтов выходных информационных шин процессора подключаются .к соответствующим группам шин четного и нечетного байтов выходных информационных щин каналов при выполнении условий, указанных при описании фит. 7.

Передача данных между селекторными каналами и процессором производится по их запросам, в последовательности, изложенной в предыдущей части данного описания.

Когда селекторный канал достигает конца блока данных, он возбуждает запрос на микропрограммное прерывание для передачи процессору байта состояния. Мультиплексный канал возбуждает запрос на микропрограммное прерывание для передачи каждого байта данный и байта состояния. Пульт управления

16

рассматриваемый как канал, устанавливает запрос при включении оператором соответствующих органов на пульте.

Приоритет запросов каналов на микропрограммное прерывание устанавливается в блоке 15 запросов на микропрограммное прерывание (см. фиг. 9). Этот блок содержит схему 148 приоритетов запросов на микропрограммное прерывание, триггер 149 запросов каналов на микропрограммное прерывание со схемой J50, шифратор 151 начального адреса постоянной памяти микропрограмм, обслуживающих запросы соответствующих каналов, и регистр 152 блокировки

повторного прерывания обслуживающих микропрограмм со схемами 153.

При поступлении запроса от одного из каналов по соответствуюпдей шине 41 третьей группы ш,ин управления каналов устанавливается потенциал на выходе соответствуюпдей схемы «И 154 схемы 148 приоритет запросов на микропрогра.ммное прерывание, если не возбужден ни один из выходов схем «И 154, соответствующих более приоритетным каналам. При этом, через схему 150 переводится в единичное состояние триггер 149 запросов каналов на микропрограммное прерывание, и через шифратор 151 начального адреса обслуживающей микропрограммы в блок 8 микропрограммного управления выдается запрос по соответствующим щивам второй группы шин 42 микропрограммного управления процессора и признак запрашивающего канала, по которым заканчивается выполнение текущего

цикла«чтение - обработка... - запись,

адрес прерыванной микропрограммы запоминается и начинается выполнение микропрограммы, обслуживающей запрос, начиная с адреса, выданного из блока 15 запросов на

микропрограммное прерывание через шифратор 151 начального адреса постоянной памяти обслуживающей микропрограммы. При этом устанавливается в единичное состояние триггер 149 запросов на микропрограммное

прерывание и в регистре 152 блокировки повторного прерывания соответствующий триггер 155, который блокирует возможность повторного прерывания, если от обслуживаемого канала поступит запрос на микропрограммное прерывание до окончания выполнения его обслуживающей микропрограммы.

Запрос на микропрограммное прерывание селекторного канала может прервать выполнение обслуживающей микропрограммы мультиплексного канала.

Приоритет селекторных каналов одинаков, но при одновременном поступлении запросов от обоих селекторных каналов вначале удовлетворяется запрос первого канала. Если же

началось выполнение обслуживающей микропрограммы второго селекторного канала и появился запрос первого селекторного канала, последний будет удовлетворен только после выполнения программы, обслуживающей

второй селекторный канал. Триггер /55 регистра 152 блокировки повторного прерывания по запросу пульта управления (крайний справа) соединен только со входом схемы «И 154 схемы 148 приоритетов запросов каналов «а микропрограммное прерывание, связанной с шиной 41 запросов пульта управления на микропрограммное прерывание. Триггер /55 блокировки повторного прерывавИя по запросу мультиплексного канала соединен со входами схем «И 154, связанных с шинами 41 запросов мультиплексного ка«ала и пульта управления на микропрограммное прерывание. Триггеры /55 блокировки повторного прерывания по запросам первого и второго селекторных каналов через схему «ИЛИ 156 связаны со входами всех схем «И схемы 148 приоритетов запросов каналов на микропрограммное прерывание, выход каждой из которых, исключая крайнюю левую, соединен через схемы «НЕ /57 со входами всех соседних слева схем «И 154. Таким образом обеспечивается приоритет и блокировки запросов на микропрограммное прерывание. Состояние регистра 152 блокировки повторного прерывания может быть передано в процессор через блок 21 сборки и .передач на входные .информационные шины // арифметического и логического устройства. Каждый из триггеров /55 регистра 152 переводится в нулевое состояние после выполнения соответствующей микропрограммы по сигналу из устройства 7 микропрограммного управления процессора 2 через соответствующую шину 42 управления процессора. Предмет изобретения 1. Устройство управления каналами, содержащее блок запросов на передачу данных, блок формирования управляющих сигналов и блоки сборки и передач, соединенные с процессором, а также с каналами, отличающееся тем, что, с целью упрощения структуры и сокращения количества шин, связывающих процессор и каналы, оно дополнительно содержит блок адресации регистров и триггеров управляемых каналов, блок запросов на микропрограммное прерывание, блоки сборки информационных и адресных шин и шин1 ключей защиты каналов, блоки коммутации информационных шин каналов и процессора, блоки управления коммутацией информационных шин, причем блок адресации регистров и триггеров управляемых каналов соединен с блоком запросов на микропрограммное прерывание .и блоком сборки и передач информационных шин, блок запросов на передачу данных подключен к блокам сборки адресных шин каналов и шин ключей защиты, а также к блокам управления коммутацией информационных щин, которые соединены с блоками коммутации информационных шин и блоком 5 10 15 20 25 30 35 40 45 50 55 60 65 управляющих сигналов, при этом другие входы и выходы блока запросов на микропрограммное прерывание, блока запросов на передачу данных, блока управляющих сигналов, блока сборки и передач информационных шин, блоков коммутации информационных шин, блоков управления коммутацией инфорционных шин, блока адресации регистров и триггеров управляемых каналов и блоков сборки адресных шин каналов и шин ключей защиты подключены к соответствующим выходам .и входам устройства управления каналами. 2. Устройство по п. 1, отличающееся тем, что блок адресации регистров и триггеров каналов содержит дешифратор поля константы, дешифраторы полей и регистр признаков каналов, соединенные с соответствуюи1ими входами и выходами блока. 3. Устройство по п. 1, отличающееся тем, что блок запросов ла передачу данных содержит дешифраторы признаков активных первого и второго (селекторных) -каналов, триггеры работы первого и второго каналов и триггер срочного запроса второго канала со схемами установок, и логические схемы, причем нулевой выход триггера работы второго канала соединен с дешифратором признака первого активного канала, другие входы которого подключены к соответствующей шине запроса первого канала на передачу данных и нулевому выходу триггера срочного запроса второго канала, а выход дешифратора признака первого активного канала и единичный выход триггера работы первого канала через первую схему «ИЛИ и схему «НЕ соединены с первым входом дешифратора признака .второго активного канала, другой вход которого подключен к шине запроса второго канала на передачу данных, а выход его и единичный выход триггера работы второго канала соединены со входом второй схемы «ИЛИ, выход которой и выход первой схемы «ИЛИ через третью схему «ИЛИ соединены с выходами блока, ,и, кроме того, входы триггеров работы первого и второго каналов через соответствуюшие схемы установок соединены с выходами первой и второй схем «ИЛИ соответственно и с входами блока, а входы триггера срочного запроса второго канала через другие схемы установок соединены с другими входами блока. 4. Устройство по п. 1, отличающееся тем, что блок управляюших сигналов содерл ит триггеры такта чтения, такта передачи и такта записи со схемами установок и схему формирования признака стирания, причем единичный выход триггера такта чтения подключен через первую схему установки к единичному входу триггера такта передачи, единичный выход которого соединен через вторую схему установки с нулевым входом триггера такта чтения и через третью схему установки - с единичным входом триггера такта записи, единичный выход последнего связан через вторую и четвертую схему установки с нулевыми входами триггера такта чтения и триггера такта передачи соответственно, нулевые выходы триггера такта записи и триггера такта передачи через пятую схему установки подключены к единичному входу триггера такта чтения, единичный выход которого и единичные вых.оды триггеров такта записи, такта передачи и схема формирования признака стирания подключены к соответствующим выходам блока, другие входы первой, второй, третьей, четвертой, пятой :и шестой схем установок и схемы формирования признака стирания подключены к соответствующим входам блока, а выход щестой схемы установки соединен с нулевым входом триггера такта записи. 5.Устройство по п. 1, отличающееся тем, что блок управления коммутацией информационных щин каналов содержит дещифраторы коммутации группы щин четного и нечетного байтов выходных информационных ЩИН селекторных каналов, дещифратор коммутации выходных информационных щик мультиплексного канала и схемы сборки, причем входы дешифратора коммутации групп четного и Нечетного байтов выходных информационных щин селекторных каналов соединены с соответствующими входами блока, входы дещифратора коммутации выходных информационных щ;ин мультиплексного канала подключены к другим входам блока, а выходы дещнфраторов коммутации выходных информациоННых щин каналов соединены через соответствующие схемы сборки с соответствуюЩИми выходами блока. 6.Устройство по п. 1, отличающееся тем, что блок коммутации выходных информационных Щ:Ин каналов содержит схему сборки выходных информационных щин каналов и схему коммутации выходных информационных ЩИН каналов, причем схема сборки выходных инфор.мационных щин каналов подключена к соответствующим входам блока, а выходы схемы сборки выходных информационных щин каналов через схему коммутации информационных ща-ж каналов, другие входы которой соединены с другими входами блока, подключены к выходам блока. 7.Устройство по п. 1, отличающееся тем, что блок управления коммутацией информационных щин процессора содержит дещифраторы коммутации групп щии четного и нечетного байтов выходных информационных щин процессора селекторных и мультиплексного каналов и схемы сборки, причем входы дещифраторов коммутации групп чет-ного и нечетного байтов выходных информационных щин процессора селекторных каналов соединены с соответствующими входами блока, входы дещифратора коммутации групп щин четного и нечетного байтов выходных информационных щин процессора мультиплексного канала соединены со входами блока, при этом выходы дещифраторов коммутации групп четного и нечетного байтов информационных щин процессора каналов через соответствующие схемы сборки соединены с соответствующими выходами блока. 8.Устройство по п. 1, отличающееся тем, что блок коммутации информационных щин процессора содержит три группы схем «И и схему сборки, входы и выходы которых подключены к соответствующим входам и выходам блока. 9.Устройство по п. 1, отличающееся тем, что блок запросов на микропрограммное прерывание содержит схемы приоритетов запросов каналов на микропрограммное прерывание, дещифратор кода начального адреса памяти процессора, триггер запросов на микропрограммное прерывание со схемой установки, регистр блокировки повторного прерывания, причем схема приоритетов запросов каналов на микропрограммное прерывание соединена с соответствующими входами и выходами блока, щифратором начального адреса постоянной памяти процессора, регистром блокировки повторного прерывания, а также через схему установки - с единичным входом триггера запросов, единичный выход которого соединен с выходом блока, регистр блокировки повторного прерывания соединен также с соответствующими входами и выходами блока.

.

N,-1-1 I i-H.

14 |-H Elf

.Uj

™u:fJn..I

r . f

«о

a

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления каналами | 1972 |

|

SU545983A1 |

| Устройство управления каналами | 1973 |

|

SU518769A1 |

| Селекторный канал | 1973 |

|

SU517019A1 |

| Устройство для управления каналами связи вычислительной системы | 1975 |

|

SU525095A1 |

| Мультиплексный канал | 1973 |

|

SU517022A1 |

| Устройство управления для селекторного канала | 1984 |

|

SU1238095A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для управления каналами | 1974 |

|

SU520592A1 |

| СШТШДА ОБРАБОТКИ ДАННЫХ1 Т Бii^f;'- ViJ- i^ О г^ ал | 1970 |

|

SU433484A1 |

| Устройство для управления диагностикой каналов | 1973 |

|

SU526876A1 |

L.

..

c

f

If

Д7

2

Фиг. 9

Авторы

Даты

1973-01-01—Публикация