(21) 4236116/24-24

(22) 25.03.8

(46) 23.04.89. Бюл. № 15

(72) А.Т. Клышбаев

(53)681.327.11(088.8)

(56)Авторское свидетельство СССР № 1182508, кл. G 06 F 3/153, 1983.

Авторское свидетельство СССР № 1231496, кл. G 06 F 3/14, 1984.

(54)УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ

(57)Изобретение относится к вычисли-- тельной технике, в частности к средствам вывода информации с ЭВМ, и . предназначено преимущественно для использования в составе вычислительного комплекса в -школах, училищах, вузах.. Цель изобретения - расширение области применения устройства путем отображения изменений изображения в реальном масштабе времени, которая достигается введением второго 5, третьего 7 и четвертого 17 регистров, блока 15 сопряжения, буферных регистров 2,1- 2.N, двух групп регистров 3.1-3.N и 18.1-18.N сдвига, коммутаторов 6 и 11 и переключателя 8 режимов работы и соответствующих функциональных связей. Изобретение позволяет при использовании его в составе вычислительной систем:, в школах, училищах и вузах динамически отображать экранную память одного пользователя на телевизионные экраны двух или группы j пользователей, при этом экранная память представляет собой ОЗУ и поэтому для модификации части изображения достаточно об этой части считать из ЭВМ, а затем снова записать в экранную память. 2 з.п. ф-лы, 10 ил.

so

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1462408A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Устройство для вывода графической информации | 1987 |

|

SU1437908A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1994 |

|

RU2108623C1 |

| Устройство для вывода графической информации | 1990 |

|

SU1783572A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1985 |

|

SU1287223A1 |

| Устройство для вывода графической информации | 1985 |

|

SU1339625A1 |

| Устройство для считывания графической информации | 1986 |

|

SU1377882A1 |

| Устройство для вывода графической информации | 1986 |

|

SU1399809A1 |

Изобретение относится к вычислительной технике, в частности к средствам вывода информации с ЭВМ, и предназначено преимущественно для использования в составе вычислительного комплекса в школах, училищах, вузах. Цель изобретения - расширение области применения устройства путем отображения изменений изображения в реальном масштабе времени, которая достигается введением второго 5, третьего 7 и четвертого 17 регистров, блока 15 сопряжения, буферных регистров 2.1 ÷ 2. N, двух групп регистров 3.1 ÷ 3. N и 18.1 ÷ 18. N сдвига, коммутаторов 6 и 11 и переключателя 8 режимов работы и соответствующих функциональных связей.Изобретение позволяет при использовании его в составе вычислительной системы в школах, училищах и вузах динамически отображать экранную память одного пользователя на телевизионные экраны двух или группы пользователей, при этом экранная память представляет собой ОЗУ и поэтому для модификации части изображения достаточно об этой части считать из ЭВМ, а затем снова записать в экранную память. 2 з.п. ф-лы, 10 ил.

л

-4

й

оэ

со

Изобретение относится к вычислительной технике и может быть использовано для вывода и отображения информации на экраны телевизионных приемников, преимущественно в составе вычислительных систем для школ, училищ и вузов.

Цель изобретения - расширение области применения устройства путем отображения изменений изображения в реальном масштабе времени.

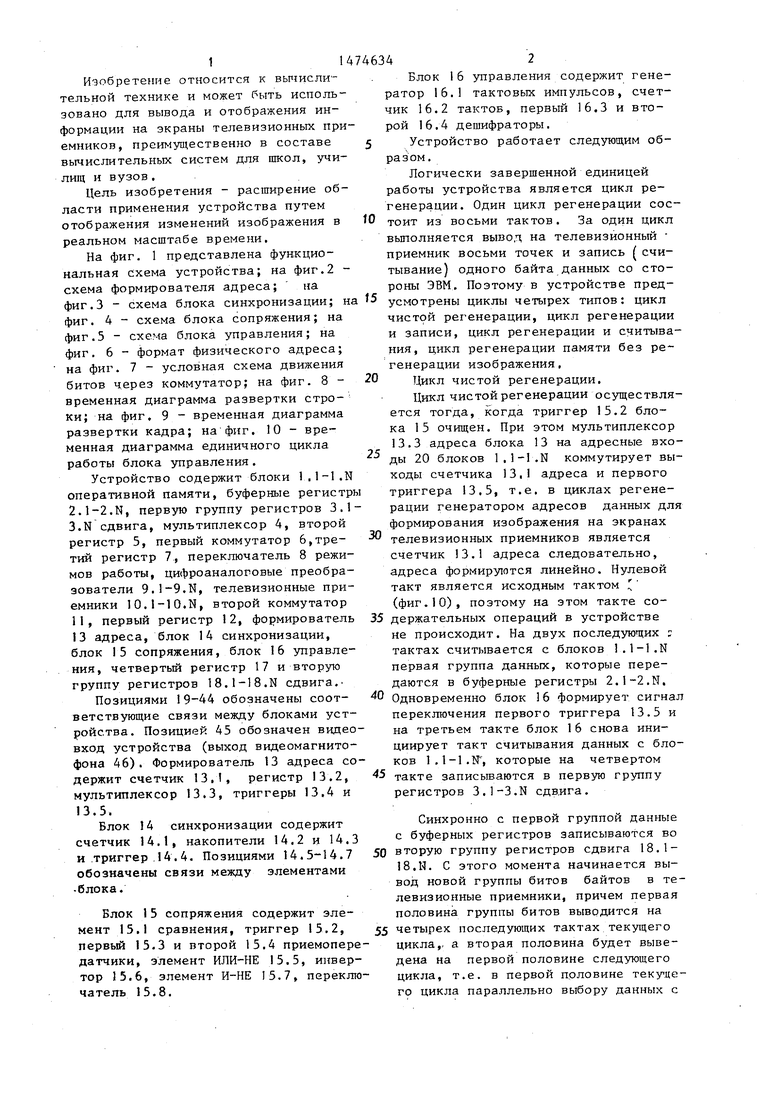

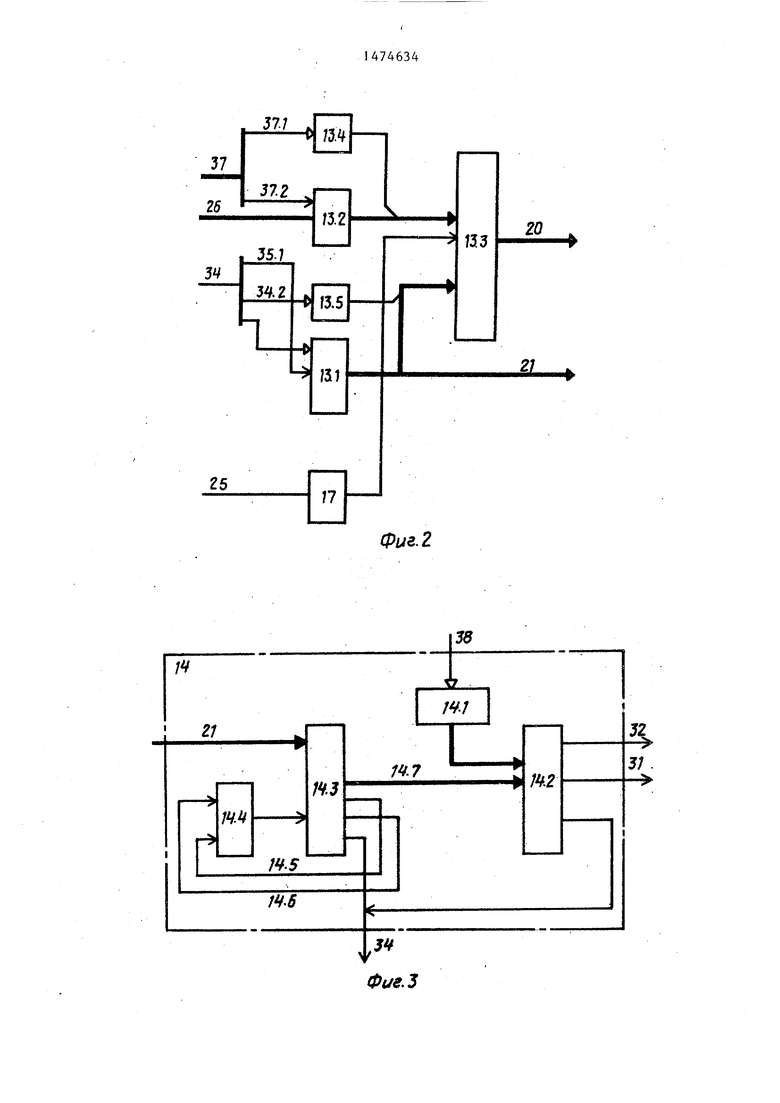

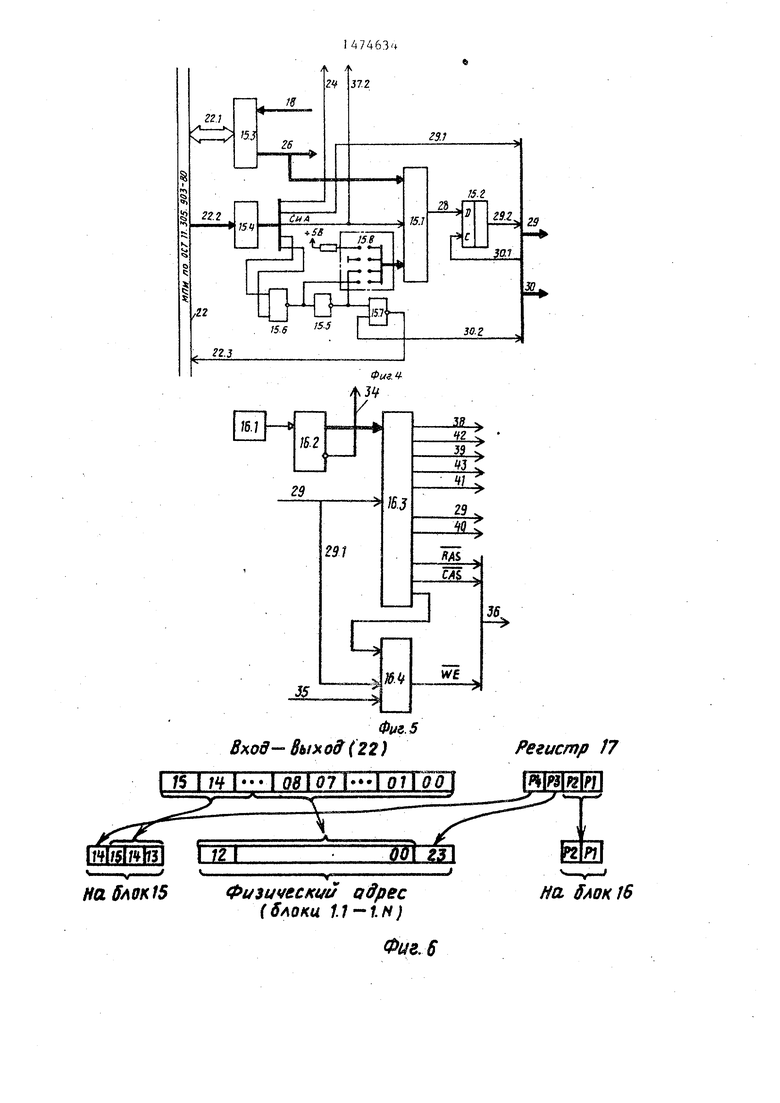

На фиг. 1 представлена функциональная схема устройства; на фиг.2 - схема формирователя адреса; на

10

Блок 16 управления содержит генератор 16.1 тактовых импульсов, счетчик 16.2 тактов, первый 16.3 и второй 16.4 дешифраторы.

Устройство работает следующим образом.

Логически завершенной единицей работы устройства является цикл регенерации. Один цикл регенерации сос тоит из восьми тактов. За один цикл выполняется вывод на телевизионный приемник восьми точек и запись ( считывание) одного байта данных со стороны ЭВМ. Поэтому в устройстве предфиг. 3 - схема блока синхронизации; на 5 усмотрены циклы четырех типов: цикл

фиг. 4 - схема блока сопряжения; на фиг.5 - схема блока управления; на фиг. 6 - формат физического адреса; на фиг. 7 - условная схема движения битов через коммутатор; на фиг. 8 - временная диаграмма развертки строки; на фиг, 9 - временная диаграмма развертки кадра; на фиг. 10 - временная диаграмма единичного цикла работы блока управления.

Устройство содержит блоки 1.1-1.N оперативной памяти, буферные регистры 2.1-2.N, первую группу регистров 3.1 3.N сдвига, мультиплексор 4, второй регистр 5, первый коммутатор 6,третий регистр 7, переключатель 8 режимов работы, цифроаналоговые преобразователи 9.1-9.N, телевизионные приемники 10.1-10.N, второй коммутатор 11, первый регистр 12, формирователь 13 адреса, блок 14 синхронизации, блок 15 сопряжения, блок 16 управления, четвертый регистр 17 и вторую группу регистров 18.1-18.N сдвига. Позициями 19-44 обозначены соответствующие связи между блоками устройства. Позицией 45 обозначен видеовход устройства (выход видеомагнитофона 46). Формирователь 13 адреса содержит счетчик 13.1, регистр 13.2, мультиплексор 13.3, триггеры 13.4 и 13.5.

Блок 14 синхронизации содержит счетчик 14.1, накопители 14.2 и 14.3 и триггер 14.4. Позициями 14.5-14.7 обозначены связи между элементами блока.

Блок 15 сопряжения содержит элемент 15.1 сравнения, триггер 15.2, первый 15.3 и второй 15.4 приемопередатчики, элемент ИЛИ-НЕ 15.5, инвертор 15.6, элемент И-НЕ чатель 15.8.

Блок 16 управления содержит генератор 16.1 тактовых импульсов, счетчик 16.2 тактов, первый 16.3 и второй 16.4 дешифраторы.

Устройство работает следующим образом.

Логически завершенной единицей работы устройства является цикл регенерации. Один цикл регенерации состоит из восьми тактов. За один цикл выполняется вывод на телевизионный приемник восьми точек и запись ( считывание) одного байта данных со стороны ЭВМ. Поэтому в устройстве пред5 усмотрены циклы четырех типов: цикл

0

5

чистой регенерации, цикл регенерации и записи, цикл регенерации и считывания, цикл регенерации памяти без регенерации изображения.

Цикл чистой регенерации. Цикл чистой регенерации осуществляется тогда, когда триггер 15.2 блока 15 очищен. При этом мультиплексор 13.3 адреса блока 13 на адресные входы 20 блоков 1.1-1.N коммутирует выходы счетчика 13,1 адреса и первого триггера 13,5, т.е. в циклах регенерации генератором адресов данных для формирования изображения на экранах телевизионных приемников является счетчик 13.1 адреса следовательно, адреса формируются линейно. Нулевой такт является исходным тактом (фиг.10), поэтому на этом такте со5 держательных операций в устройстве не происходит. На двух последующих г тактах считывается с блоков 1.1-1.N первая группа данных, которые передаются в буферные регистры 2.1-2.N.

® Одновременно блок 16 формирует сигнал переключения первого триггера 13.5 и на третьем такте блок 16 снова инициирует такт считывания данных с блоков 1.1-1.N , которые на четвертом

0

5

такте записываются в первую группу регистров 3.1-3.N сдвига.

Синхронно с первой группой данные с буферных регистров записываются во

вторую группу регистров сдвига 18.1- 18.Ы. С этого момента начинается вывод новой группы битов байтов в телевизионные приемники, причем первая половина группы битов выводится на

четырех последующих тактах текущего цикла, а вторая половина будет выведена на первой половине следующего цикла, т.е. в первой половине текущего цикла параллельно выбору данных с

блоков памяти осуществляется вывод на телевизионные мониторы данных, запи- санных в регистры сдвига на предыдущем цикле. Так как тактовые входы регистров сдвига объединены в общую шину, то регистры сдвига работают синхронно. После каждого такта регистры 3.1-3.N и 18.1-18.N сдвига синхронно подают на входы коммутато- ра 6 очередные биты, подлежащие выводу в телевизионные приемники. Цикл завершается очисткой первого триггера 13.5, увеличением счетчика 13.1 адреса на единицу и формированием сигнала опроса триггера 15.2 активности блока 15 путем формирования сигнала опробирования по входу 29.1 триггера 15.2. Если при этом триггер 15,2 активности установился, то еле- дующий цикл совмещается с записью (считыванием) в блоки 1.1-1.N данных с ЭВМ.

Цикл регенерации, и запись (считывание) .

Триггер 15.2 активности устанавливается при опросе только в том случае, если имеет место канальный сеанс ЭВМ, т.е. сигнал СИЛ имеет активный

уровень, который, поступая на элемент 30 переключается на регистр 13.2 адреса

Цля того, чтобы разграничить в канальном сеансе адресную часть сеанса, через переключатель 15.8 заведены сигналы направления передачи, сопровождающие данные с помощью элемента ИЛИ-НЕ 15.5. Сигнал направления через инвертор 15.6 поступает на вход элемента И-НЕ 15.7 и открывает его для

прохождения сигнала ответа устройства . торый по входу 29.2 поступает на элена запрос ЭВМ по концу канального сеанса (сигнал синхронизации пассивного устройства). По сигналу СНА адресный код с порта передачи магистмент PI-HE I5.6 и с выхода этого элемента передается в общую магистраль 22 ЭВМ. Канальный сеанс передачи данных с ЭВМ в устройство завершается,

ральных приемопередатчиков 15.3 защелкивается в регистре 13.2 адреса, а один разряд - во втором триггере 13.4. Следует отметить, что запись адреса в регистр адреса и сравнение адреса осуществляются асинхронно с процессами, происходящими в этот момент в устройстве. Факт запроса от ЭВМ устройство обнаруживает только при опросе триггера 15.2 активности независимо от типа канального сеанса поэтому до тех пор, пока триггер активности 15.2 не установится, блок 16 не реагирует на сигналы, поступающие в него по входам 30,1. По этим входам в блок 16 поступают сигналы направления передачи и число байтов (один байт, если сигнал единичный, и два байта, если сигнал нулевой 1). Первая часть рассматриваемого типа цикла устройства, независимо от направления передачи, в точности совпадает с первой половиной цикла чистой регенерации.

Запись или считывание данных осуществляется во второй части цикла. При этом на четвертом такте цикла мультиплексор 13.3 формирователя 13

с д

5

0

и триггер 13.4, одновременно блок 16 инициирует сигналы обращения к блокам 1.1-1.N. На шестом такте, в зависимости от кодов на группе выходов регистра 17, которые передаются в блок 16 по входам 35, возбуждается один из выходов 36 дешифратора 16.4 и осуществляется запись в i-й блок из блоков. 1.1-1.N непосредственно с младшей группы выходов порта передачи блока 15. Одновременно данные со старшей группы выходов порта передачи заносятся регистр 12. Если в одном канальном сеансе в устройство передаются два байта (слово), то очевидно, что в регистр 12 записывается старший байт. На последнем седьмом такте одновременно переключаются первый и второй триггеры 13,4 и 13.5, увеличивается счетчик 13.1 адреса на единицу, запираются магистральные приемопередатчики 15.3, открывается регистр 12 и формируется сигнал синхронизации пассивного устройства, который по входу 29.2 поступает на элемент PI-HE I5.6 и с выхода этого элемента передается в общую магистраль 22 ЭВМ. Канальный сеанс передачи данных с ЭВМ в устройство завершается,

но в устройстве полный цикл записи не закончен. Так как в конце первог цикла сигнал опроса триггера 15.2 активности не формируется, триггер 15.2 активности сохраняет свое состояние. Следовательно, цикл записи снова повторяется, но так как в конце предыдущего цикла второй триггер 13.4 переключается, то следующий байт, но уже с выхода регистра 12, записывается по следующему адресу.

Физический адрес, по которому записываются данные,отличается от канального адреса (по входу 22). Необходимость такого преобразования следует из того, что в одном из блоков 1.1-1.N размещаются экранные области двух пользователей, Разрядом разграничения этих областей служит разряд Р1, который поступает с регистра 12.

Модифицируемым разрядом при записи второго байта является разряд Р2, который поступает с выхода второго триггера 13.4,

Аналогично выполняется цикл считы вания за исключением того, что в циклах считывания данные с блоков 1.1- L.N считываются в буферные регистры

40

Цикл регенерации памяти без регенерации изображения.

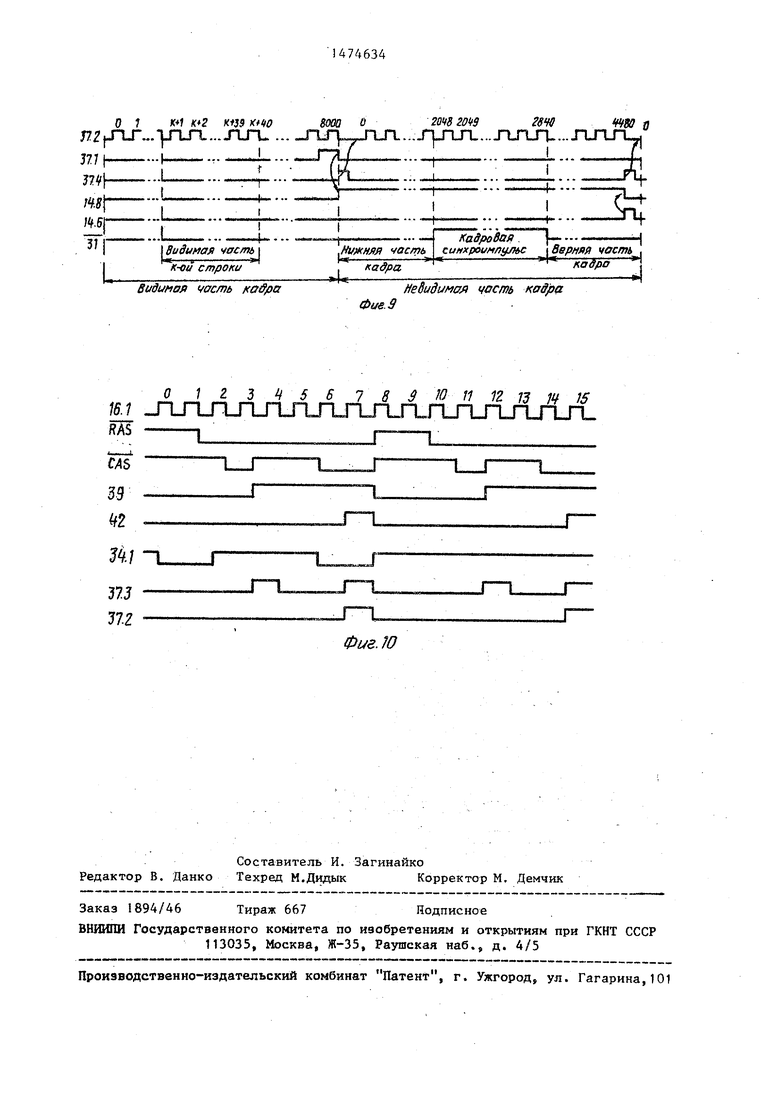

Цикл регенерации памяти осуществляется для того, чтобы сохранить информацию в блоках 1.1-1.N. Циклы регенерации памяти проводятся тогда, когда нет циклов регенерации изображения (фиг.9), т.е. в гашенной части телевизионного экрана. Работа устройства в циклах регенерации памяти совпадает с циклами регенерации изобра у жения за исключением того, что коммутатор 6 заблокирован и вывод информации не осуществляется.

Рассмотрим работу устройства при развертке одного кадра изображения.

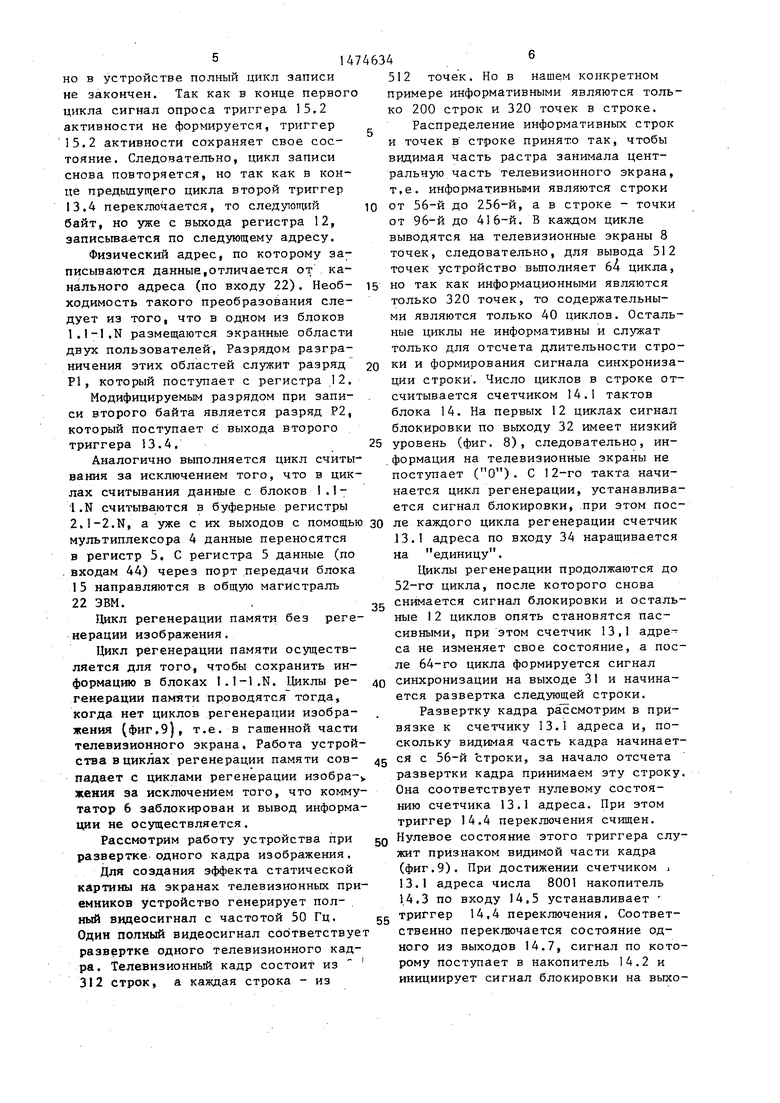

Для создания эффекта статической картины на экранах телевизионных приемников устройство генерирует полный видеосигнал с частотой 50 Гц. Один полный видеосигнал соответствует развертке одного телевизионного кадра. Телевизионный кадр состоит из 312 строк, а каждая строка - из

на единицу1

Циклы регенерации продолжаются до цикла, после которого снова ос снимается сигнал блокировки и остальные 12 циклов опять становятся пассивными, при этом счетчик 13,1 адреса не изменяет свое состояние, а после 64-го цикла формируется сигнал синхронизации на выходе 31 и начинается развертка следующей строки.

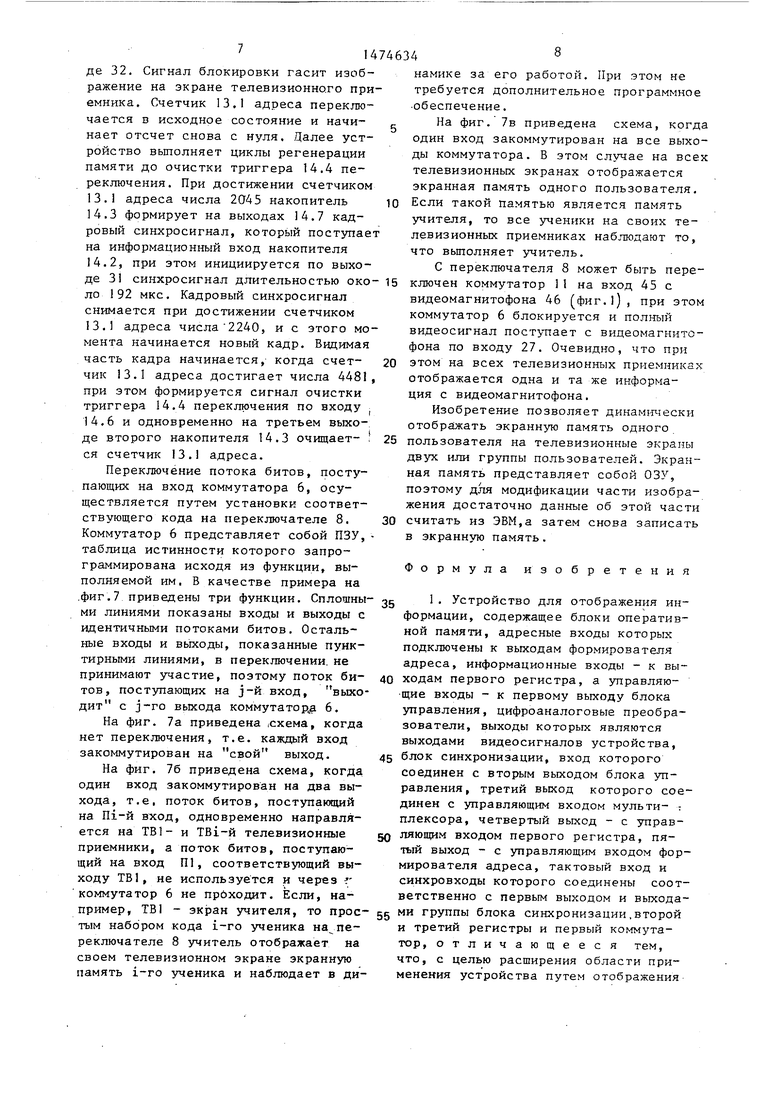

Развертку кадра рассмотрим в привязке к счетчику 13.1 адреса и, поскольку видимая часть кадра начинается с 56-й строки, за начало отсчета развертки кадра принимаем эту строку. Она соответствует нулевому состоянию счетчика 13.1 адреса. При этом триггер 14.4 переключения счищен. Нулевое состояние этого триггера служит признаком видимой части кадра (фиг.9). При достижении счетчиком i 13.1 адреса числа 8001 накопитель 14.3 по входу 14,5 устанавливает триггер 14,4 переключения. Соответственно переключается состояние одного из выходов 14.7, сигнал по которому поступает в накопитель 14.2 и инициирует сигнал блокировки на выхо45

50

55

512 точек. Но в нашем конкретном примере информативными являются только 200 строк и 320 точек в строке.

Распределение информативных строк и точек в строке принято так, чтобы видимая часть растра занимала центральную часть телевизионного экрана, т.е. информативными являются строки

от 56-й до 256-й, а в строке - точки от 96-й до 416-й. В каждом цикле выводятся на телевизионные экраны 8 точек, следовательно, для вывода 512 точек устройство выполняет б4 цикла,

5 но так как информационными являются только 320 точек, то содержательными являются только 40 циклов. Остальные циклы не информативны и служат только для отсчета длительности стро0 ки и формирования сигнала синхронизации строки. Число циклов в строке отсчитывается счетчиком 14.1 тактов блока 14. На первых 12 циклах сигнал блокировки по выходу 32 имеет низкий

5 уровень (фиг. 8), следовательно, информация на телевизионные экраны не поступает (О). С 12-го такта начинается цикл регенерации, устанавливается сигнал блокировки, при этом пос0

0 ле каждого цикла регенерации счетчик 13.1 адреса по входу 34 наращивается

на единицу1

Циклы регенерации продолжаются до цикла, после которого снова с снимается сигнал блокировки и остальные 12 циклов опять становятся пассивными, при этом счетчик 13,1 адреса не изменяет свое состояние, а после 64-го цикла формируется сигнал синхронизации на выходе 31 и начинается развертка следующей строки.

Развертку кадра рассмотрим в привязке к счетчику 13.1 адреса и, поскольку видимая часть кадра начинается с 56-й строки, за начало отсчета развертки кадра принимаем эту строку. Она соответствует нулевому состоянию счетчика 13.1 адреса. При этом триггер 14.4 переключения счищен. Нулевое состояние этого триггера служит признаком видимой части кадра (фиг.9). При достижении счетчиком i 13.1 адреса числа 8001 накопитель 14.3 по входу 14,5 устанавливает триггер 14,4 переключения. Соответственно переключается состояние одного из выходов 14.7, сигнал по которому поступает в накопитель 14.2 и инициирует сигнал блокировки на выхо5

0

5

де 32. Сигнал блокировки гасит изображение на экране телевизионного приемника. Счетчик 13.1 адреса переключается в исходное состояние и начи-

нает отсчет снова с нуля. Далее устройство выполняет циклы регенерации памяти до очистки триггера 14.4 переключения. При достижении счетчиком 13.1 адреса числа 2045 накопитель

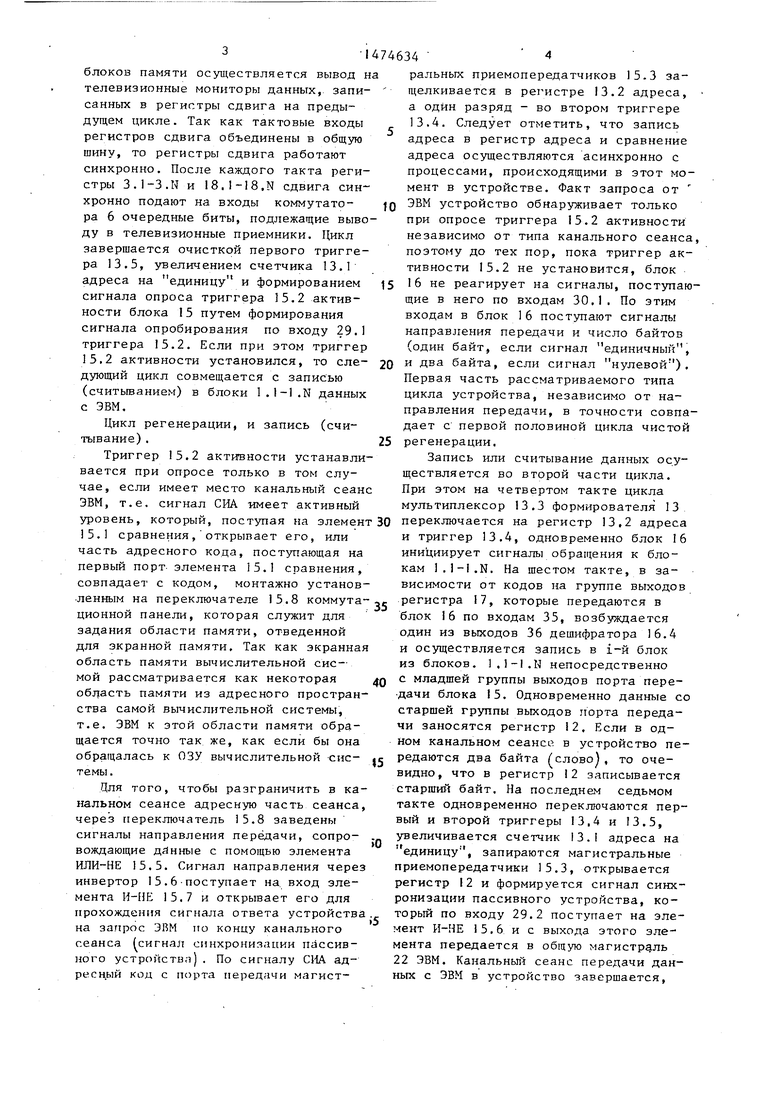

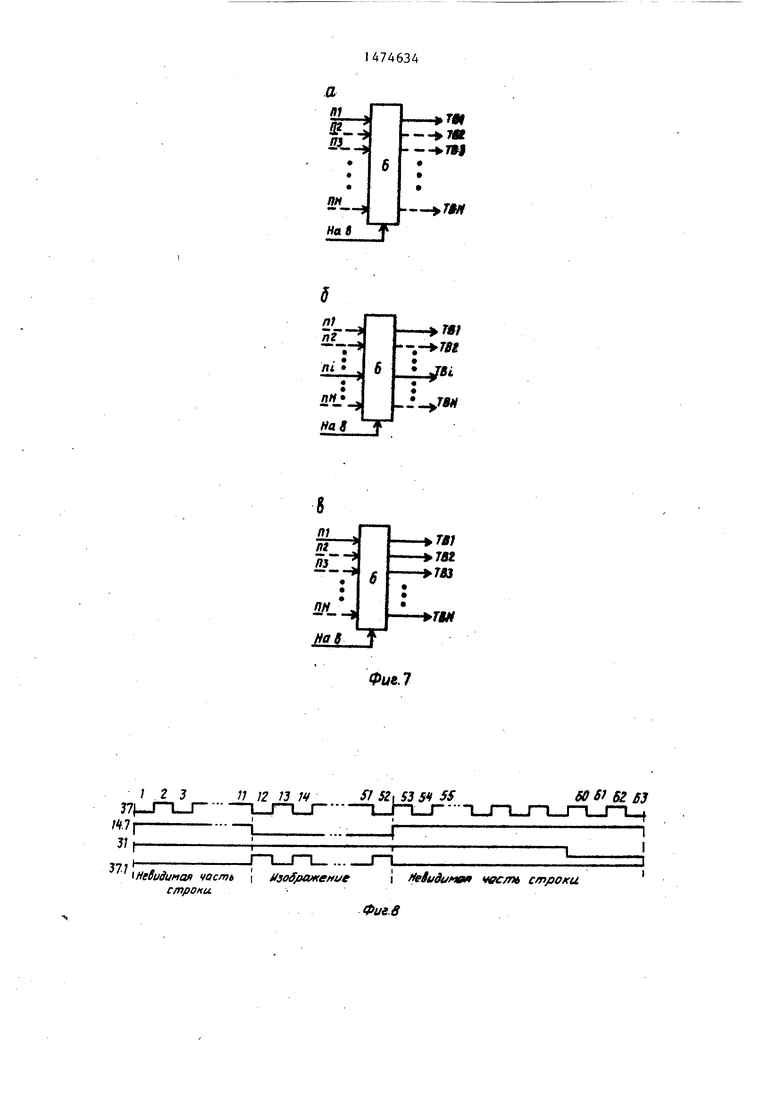

Переключение потока битов, поступающих на вход коммутатора 6, осуществляется путем установки соответствующего кода на переключателе 8. Коммутатор 6 представляет собой ПЗУ, таблица истинности которого запрограммирована исходя из функции, выполняемой им. В качестве примера на фиг.7 приведены три функции. Сплошны- ми линиями показаны входы и выходы с идентичными потоками битов. Остальные входы и выходы, показанные пунктирными линиями, в переключении не принимают участие, поэтому поток битов, поступающих на j-й вход, выходит с j-ro выхода коммутатору 6.

На фиг. 7а приведена .схема, когда нет переключения, т.е. каждый вход закоммутирован на свой выход.

На фиг. 76 приведена схема, когда один вход закоммутирован на два выхода, т.е. поток битов, поступающий на Oi-й вход, одновременно направляется на ТВ1- и TBi-й телевизионные приемники, а поток битов, поступаю50 ляющим входом первого регистра, пятый выход - с управляющим входом фор мирователя адреса, тактовый вход и синхровходы которого соединены соот ветственно с первым выходом и выхода

щий на вход Ш, соответствующий выходу ТВ1, не используется и через г коммутатор 6 не проходит. Если, например, ТВ1 - экран учителя, то прос- 55 ми ГРУППЫ блока синхронизации,второй тым набором кода 1-го ученика на пе-и третий регистры и первый коммутареключателе 8 учитель отображает натор, отличающееся тем,

своем телевизионном экране экраннуючто, с целью расширения области припамять 1-го ученика и наблюдает в ди- менения устройства путем отображения

намике за его работой. При этом не требуется дополнительное программное обеспечение.

На фиг. 7в приведена схема, когда один вход закоммутирован на все выходы коммутатора. В этом случае на всех телевизионных экранах отображается экранная память одного пользователя. Если такой памятью является память учителя, то все ученики на своих телевизионных приемниках наблюдают то, что выполняет учитель,

С переключателя 8 может быть переключен коммутатор 11 на вход 45 с видеомагнитофона 46 (фиг.), при этом коммутатор 6 блокируется и полный видеосигнал поступает с видеомагнитофона по входу 27. Очевидно, что при этом на всех телевизионных приемниках отображается одна и та же информация с видеомагнитофона.

Изобретение позволяет динамически отображать экранную память одного пользователя на телевизионные экраны двух или группы пользователей. Экранная память представляет собой ОЗУ, поэтому для модификации части изображения достаточно данные об этой части считать из ЭВМ,а затем снова записать в экранную память.

Формула изобретения

блок синхронизации, вход которого соединен с вторым выходом блока управления, третий выход которого соединен с управляющим входом мульти- т плексора, четвертый выход - с управляющим входом первого регистра, пятый выход - с управляющим входом формирователя адреса, тактовый вход и синхровходы которого соединены соответственно с первым выходом и выходами ГРУППЫ блока синхронизации,второй и третий регистры и первый коммута10

15

20

25

изменений изображения в реальном масштабе времени, оно содержит четвертый регистр, блок сопряжения, вход-выход которого является входом- выходом устройства, буферные регистры, первую и вторую группы регистров сдвига, второй коммутатор и переключатель режимов работы, первый и второй выходы которого соединены с управляющими входами соответственно первого и второго коммутаторов, син- хровходы которых подключены к второму и третьему выходам блока синхронизации, информационные входы первого коммутатора подключены к выходам ре-, гистров сдвига первой и второй групп, информационные входы регистров сдвига первой группы подключены к выходам соответствующих буферных регистров, соединенным с информационными входами мультиплексора, выход которого соединен с информационным входом второго регистра, информационные входы регистров сдвига второй группы подключены к выходам соответствующих блоков оперативной памяти, соединенным с информационными входами буферных регистров, управляющие входы регистров сдвига групп и управляющий вход третьего регистра соединены с шестым выходом блока управления, с седьмой выход которого подключен к управляющим входам буферных регистров, восьмой выход блока управления соединен с управляющим входом второго регистра, девятый выход - с управляющим входом блока сопряжения, первый выход которого подключен к информационному входу блока управления, управляющий вход которого соединен с вторым выходом блока сопряжения, третий выход которого соединен с управляющим входом формирователя адреса, а выходы группы - с информационными входами первого и четвертого регистров, формирователя адреса и блоков оперативной памяти, информационный вход блока сопряжения соединен с выходом второго регистра, выход первого коммутатора подключен к информационному входу третьего регистра, выходы которого соединены с информационными входами цифроаналоговых преобразователей, управляющие входы которых соединены с выходом второго коммутатора, информационный вход которого является видеовходом устройства.

47463410

1

о т л и 30

35

чающееся тем, что блок сопряжения содержит первый и второй приемопередатчики, вход-выход первого приемопередатчика является входом- выходом блока, информационный вход является информационным входом блока, выход первого приемопередатчика является выходом группы блока и соединен с первым входом элемента сравнения, выход которого соединен с информационным входом триггера, вход второго приемопередатчика соединен с входом-выходом блока, который подключен к выходу элемента И-НЕ, первый вход которого является управляющим входом блока, соедненным со стро40 бирующим входом триггера, выход которого является первым выходом блока, второй вход элемента И-НЕ соединен с выходом инвертора подключенным к одному из в ходов переключателя, выход которого соединен с вторым входом элемента сравнения, другой вход переключателя соединен с выходом элемента ИЛИ-НЕ, подключенным к входу инвертора, первый выход второго прие -ю5Q передатчика является вторым выходом блока, второй выход соединен с первым выходом блока, а третий выход является третьим выходом блока и соединен с третьим входом элемента сравнения, четвертый и пятый выходы вто45

55

рого приемопередатчика соединены с входами элемента ИЛИ-НЕ.

5

.

1

о т л и 0

5

чающееся тем, что блок сопряжения содержит первый и второй приемопередатчики, вход-выход первого приемопередатчика является входом- выходом блока, информационный вход является информационным входом блока, выход первого приемопередатчика является выходом группы блока и соединен с первым входом элемента сравнения, выход которого соединен с информационным входом триггера, вход второго приемопередатчика соединен с входом-выходом блока, который подключен к выходу элемента И-НЕ, первый вход которого является управляющим входом блока, соедненным со стро0 бирующим входом триггера, выход которого является первым выходом блока, второй вход элемента И-НЕ соединен с выходом инвертора подключенным к одному из в ходов переключателя, выход которого соединен с вторым входом элемента сравнения, другой вход переключателя соединен с выходом элемента ИЛИ-НЕ, подключенным к входу инвертора, первый выход второго передатчика является вторым выходом блока, второй выход соединен с первым выходом блока, а третий выход является третьим выходом блока и соединен с третьим входом элемента сравнения, четвертый и пятый выходы вто5

5

рого приемопередатчика соединены с входами элемента ИЛИ-НЕ.

14

Фиг. 2

I

Фие.З

s

Фиг 5 8хо8-$ыхо&(22)

У5 1Ч 08 07 ГоТТЪо

Л

МШШ иП

Наблок15

Физический адрес (блоки 1.1-1Н)

23

Регистр 17

Фиг. 6

r

ГО

Ю

-зг-. чг

§S5

лг-t

О 1 М W9 кто

ПЈ|ЛаГ...уТЛ....Г1Ги .

}Ч.8 ,

видимая часть к-ои строки

800U О

2048 2D492840

..T lnj-L....

Кадровая

№)

.Нижняя часть синхроимпульс Верная часть

кадра

кадро

Видимая часть ка&ра

RAS CAS

3В М

JT

Щ П.

37J

т

.

Фиг. Ю

2048 2D492840

..T lnj-L....

№) о

Кадровая

хроимпуль

няя часть синхроимпульс Верная часть

кадра

кадро

А

Фие9

Невидимая чость кадра

Авторы

Даты

1989-04-23—Публикация

1987-03-25—Подача