Изобретение относится к импульс- :ной технике и может (5ыть использова- :но, например, для связи вычислительных машин с объектами регулирования, в системах стабилизации суммы частот, для обработки выходних сигналов дифференциальных, струнных частотных датчиков .

Цель изобретения - повышение точ- кости преобразователя.

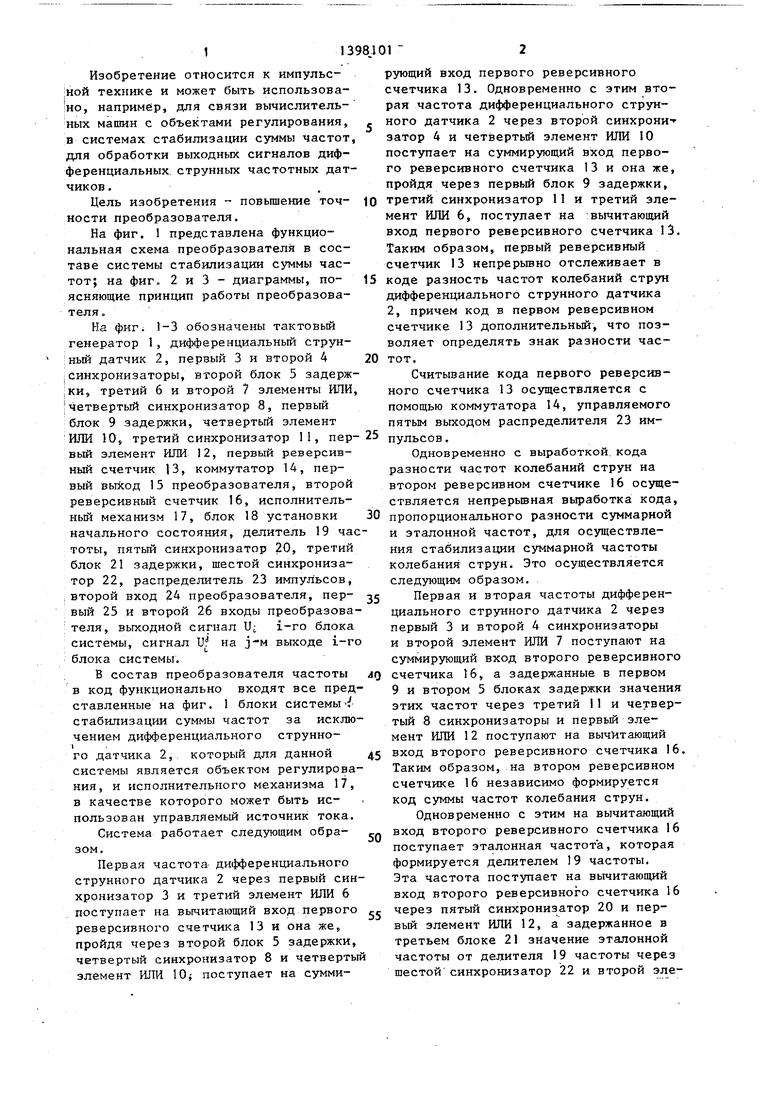

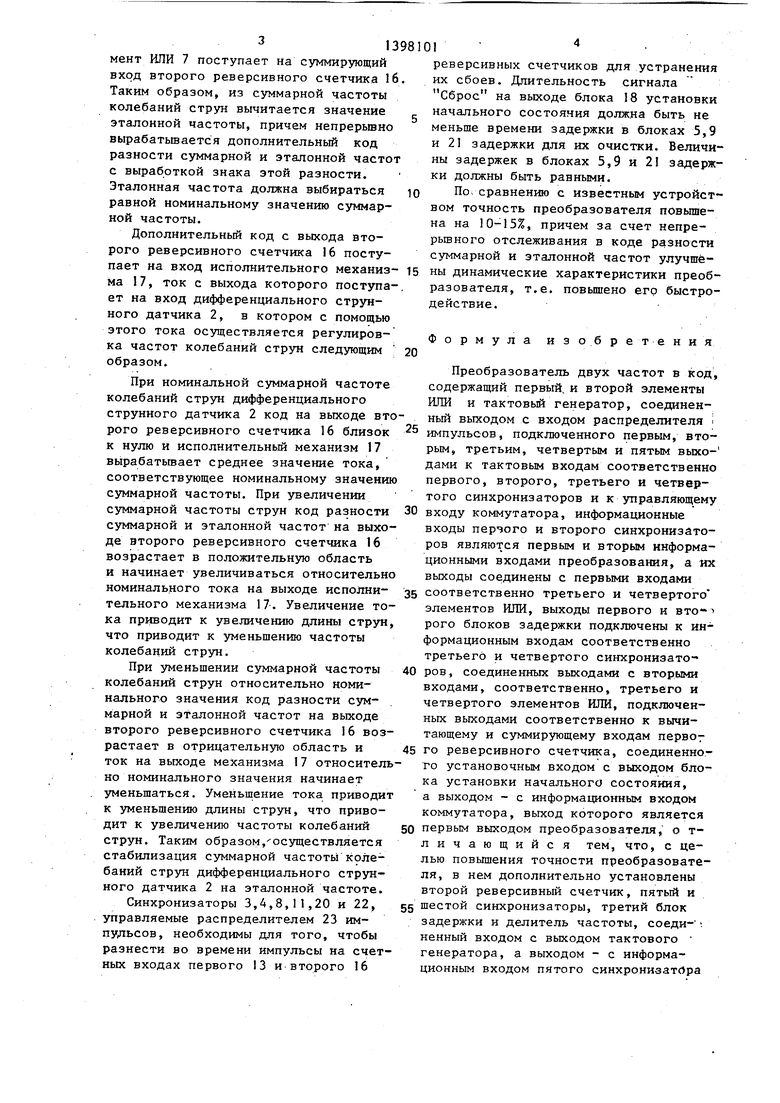

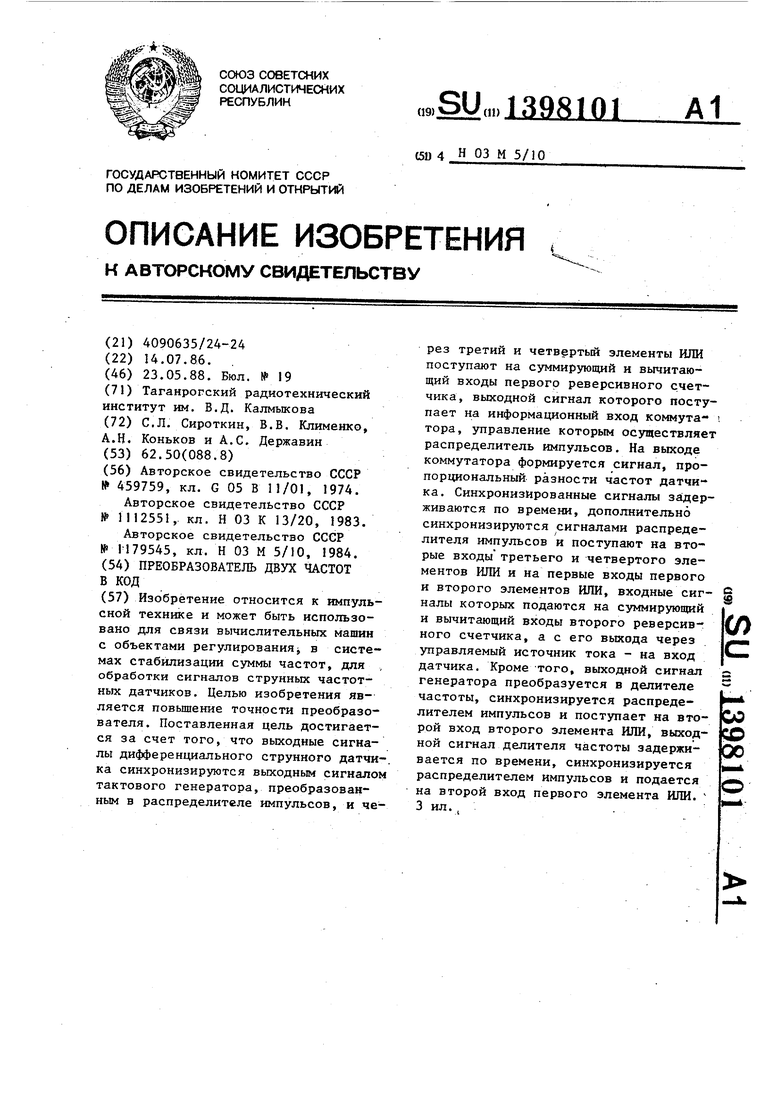

На фиг, 1 представлена функциональная схема преобразователя в составе системы стабилизации суммы частот; на фиг, 2 и 3 - диаграммы, по- ясняющие принцип работы преобразователя.

На фигi 1-3 обозначены тактовый генератор 1, дифференциальньй струн- :ный датчик 2, первый 3 и второй 4 ;синхронизаторы, второй блок 5 задерж- ;ки, третий 6 и второй 1 элементы ИЛИ, I четвертый синхронизатор 8, первый блок 9 задержки, четвертый элемент ИЛИ 10, третий синхронизатор 11, пер- вый элемент ИЛИ 12, первый реверсивный счетчик 13, коммутатор 14, первый выход 15 преобразователя, второй реверсивный счетчик 16, исполнительный механизм 17, блок 18 установки начального состояния, делитель 19 частоты, пятый синхронизатор 20, третий блок 21 задержки, шестой синхронизатор 22, распределитель 23 импул ьсов, . второй вход 24 преобразователя, пер- вый 25 и второй 26 входы преобразова- теля, выходной сигнал U i-ro блока системы, сигнал U на выходе i-ro блока системы.

; В состав преобразователя частоты в код функционально входят все представленные на фиг. 1 блоки системы V стабилизации суммы частот за исключением дифференциального струнно- I го датчика 2, который для данной

системы является объектом регулирования, и исполнительного механизма 17, в качестве которого может быть использован управляемый источник тока.

Система работает следующим образом.

Первая частота джМ еренцнального струнного датчика 2 через первый синхронизатор 3 и третий элемент ИЛИ 6 поступает на вычитающий вход первого , реверсивного счетчика 13 и она же, пройдя через второй блок 5 задержки, четвертый синхронизатор 8 и четвертый элемент ИЛИ 10 поступает на сумми,

O

5

0 5 0 5

5

0

рующий вход первого реверсивного счетчика 13. Одновременно с этим вторая частота дифференциального струнного датчика 2 через второй синхрони- затор 4 и четвертый элемент ИЛИ 10 поступает на суммирующий вход первого реверсивного счетчика 13 и она же, пройдя через первый блок 9 задержки, третий синхронизатор 11 и третий элемент ИЛИ 6, поступает на вычитающий вход первого реверсивного счетчика 13. Таким образом, первый реверсивный счетчик 13 непрерьшно отслеживает в коде разность частот колебаний струн дифференциального струнного датчика 2, причем код в первом реверсивном счетчике 13 дополнительньй, что позволяет определять знак разности частот.

Считывание кода первого реверсивного счетчика 13 осуществляется с помощью коммутатора 14, управляемого пятым выходом распределителя 23 импульсов .

Одновременно с выработкой, кода разности частот колебаний струн на втором реверсивном счетчике 16 осуществляется непрерьгоная вьфаботка кода, пропорционального разности суммарной и эталонной частот, для осуществления стабилизации суммарной частоты колебания струн. Это осуществляется следующим образом.

Первая и вторая частоты дифференциального струнного датчика 2 через первый 3 и второй 4 синхронизаторы и второй элемент ИЛИ 7 поступают на суммирующий вход второго реверсивного счетчика 16, а задержанные в первом 9 и втором 5 блоках задержки значения этих частот через третий 11 и четвертый 8 синхронизаторы и первый элемент ИЛИ 12 поступают на вычитающий вход второго реверсивного счетчика 16. Таким образом, на втором реверсивном счетчике 16 независимо формируется код суммы частот колебания струн.

Одновременно с этим на вычитающий вход второго реверсивного счетчика 16 поступает эталонная частота, которая формируется делителем 19 частоты. Эта частота поступает на вычитающий вход второго реверсивного счетчика 16 через пятый синхронизатор 20 и первый элемент ИЛИ 12, а задержанное в третьем блоке 21 значение эталонной частоты от делителя 19 частоты через шестой синхронизатор 22 и второй элемент ИЛИ 7 поступает на суммирующий вход второго реверсивного счетчика 16. Таким образом, из суммарной частоты колебаний струн вычитается значение эталонной частоты, причем непрерьшно вырабатьюается дополнительньй код разности суммарной и эталонной частот с выработкой знака этой разности. Эталонная частота должна выбираться равной номинальному значению суммарной частоты.

Дополнительный код с выхода второго реверсивного счетчика 16 посту

реверсивных счетчиков для устранения их сбоев. Длительность сигнала Сброс на выходе блока 18 установки начального состояния должна быть не меньше времени задержки в блоках 5,9 и 21 задержки для их очистки. Величины задержек в блоках 5,9 и 21 задержки должны быть ранными.

По. сравнению с известным устройством точность преобразователя повышена на 10-15%, причем за счет непре- рьтного отслеживания в коде разности суммарной и эталонной частот улучшё

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь частоты импульсов в код | 1984 |

|

SU1251329A1 |

| Преобразователь частоты в код | 1984 |

|

SU1179545A1 |

| Преобразователь частота-код | 1987 |

|

SU1410276A1 |

| Преобразователь частоты в код | 1987 |

|

SU1418906A2 |

| Преобразователь частоты в код | 1983 |

|

SU1112551A1 |

| Преобразователь частоты в код | 1985 |

|

SU1305857A1 |

| Преобразователь частота-код | 1987 |

|

SU1515368A1 |

| Преобразователь частоты импульсов в код | 1983 |

|

SU1156259A1 |

| Устройство для приема самосинхронизирующихся импульсных последовательностей | 1988 |

|

SU1601771A1 |

| Преобразователь частоты в код | 1984 |

|

SU1229959A1 |

Изобретение относится к импульсной технике и может быть использовано для связи вычислительных машин с объектами регулирования в системах стабилизации суммы частот, для , обработки сигналов струнных частотных датчиков. Целью изобретения является повьшение точности преобразователя. Поставленная цель достигается за счет того, что выходные сигналы дифференциального струнного датчи-. ка синхронизируются выходным сигналом тактового генератора, преобразованным в распределителе импульсов, и через третий и четвертый элементы ИЛИ поступают на суммирующий и вычитающий входы первого реверсивного счетчика, выходной сигнал которого поступает на информационный вход коммута- ; тора, управление которым осуществляет распределитель импульсов. На выходе коммутатора формируется сигнал, пропорциональный разности частот датчика. Синхронизированные сигналы задерживаются по времени, дополнительно синхронизируются сигналами распределителя импульсов и поступают ка вторые входы третьего и четвертого элементов ИЛИ и на первые входы первого и второго элементов ИЛИ, входные сигналы которых подаются на суммирующий и вычитающий входы второго реверсивного счетчика, а с его выхода через управляемый источник тока - на вход датчика. Кроме того, выходной сигнал генератора преобразуется в делителе частоты, синхронизируется распределителем импульсов и поступает на второй вход второго элемента ИЛИ, выходной сигнал делителя частоты задерживается по времени, синхронизируется распределителем импульсов и подается на второй вход первого элемента ИЛИ. 3 ил.,. с fS W 00 QO 00

пает на вход исполнительного механиз- 15 ны динамические характеристики преобма 17, ток с выхода которого поступает на вход дифференциального струнного датчика 2, в котором с помощью этого тока осуществляется регулировка частот колебаний струн следующим образом.

При номинальной суммарной частоте колебаний струн дифференциального струнного датчика 2 код на выходе второго реверсивного счетчика 16 близок к нулю и исполнительный механизм 17 вырабатывает среднее значение тока, соответствующее номинальному значению суммарной частоты. При увеличении суммарной частоты струн код разности суммарной и эталонной частот на выходе второго реверсивного счетчика 16 возрастает в положительную область и начинает увеличиваться относительно номинального тока на выходе исполнительного механизма 17. Увеличение тока приводит к увеличению длины струн, что приводит к уменьшению частоты колебаний струн.

При уменьшении суммарной частоты колебаний струн относительно номинального значения код разности суммарной и эталонной частот на выходе второго реверсивного счетчика 16 возрастает в отрицательную область и ток на выходе механизма 17 относительно номинального значения начинает уменьшаться. Уменьшение тока приводит к уменьшению длины струн, что приводит к увеличению частоты колебаний струн. Таким образом, осуществляется стабилизация суммарной частоты колебаний струн дифференциального струнного датчика 2 на эталонной частоте.

Синхронизаторы 3,4,8,11,20 и 22, управляемые распределителем 23 импульсов, необходимы для того, чтобы разнести во времени импульсы на счетных входах первого 13 и второго 16

20

разователя, т.е. повьшгено его быстродействие.

Формула изобретения

25

Преобразователь двух частот в код, содержащий первый, и второй элементы ИЛИ и тактовый генератор, соединенный выходом с входом распределителя i импульсов, подключенного первым, вторым, третьим, четвертым и пятым выхо- дами к тактовым входам соответственно первого, второго, третьего и четвертого синхронизаторов и к управляющему

30 входу коммутатора, информационные входы перчого и второго синхронизаторов являются первым и вторым информационными входами преобразования, а их выходы соединены с первыми входами

35 соответственно третьего и четвертого элементов ИЛИ, выходы первого и вто- рого блоков задержки подключены к информационным входам соответственно третьего и четвертого синхроиизато40 ров, соединенных выходами с вторыми входами, соответственно, третьего и четвертого элементов ИЛИ, подключенных выходами соответственно к вычитающему и суммирующему входам перво7

45 го реверсивного счетчика, соединенного установочным входом с выходом блока установки начального состояния, а выходом - с информационным входом коммутатора, выход которого является

50 первым выходом преобразователя, о т- личающийся тем, что, с целью повышения точности преобразователя, в нем дополнительно установлены второй реверсивный счетчик, пятый и

55 шестой синхронизаторы, третий блок задержки и делитель частоты, соеди- -. ненный входом с выходом тактового генератора, а вькодом - с информационным входом пятого синхронизатора

20

разователя, т.е. повьшгено его быстродействие.

Формула изобретения

5

Преобразователь двух частот в код, содержащий первый, и второй элементы ИЛИ и тактовый генератор, соединенный выходом с входом распределителя i импульсов, подключенного первым, вторым, третьим, четвертым и пятым выхо- дами к тактовым входам соответственно первого, второго, третьего и четвертого синхронизаторов и к управляющему

0 входу коммутатора, информационные входы перчого и второго синхронизаторов являются первым и вторым информационными входами преобразования, а их выходы соединены с первыми входами

5 соответственно третьего и четвертого элементов ИЛИ, выходы первого и вто- рого блоков задержки подключены к информационным входам соответственно третьего и четвертого синхроиизато0 ров, соединенных выходами с вторыми входами, соответственно, третьего и четвертого элементов ИЛИ, подключенных выходами соответственно к вычитающему и суммирующему входам перво7

5 го реверсивного счетчика, соединенного установочным входом с выходом блока установки начального состояния, а выходом - с информационным входом коммутатора, выход которого является

0 первым выходом преобразователя, о т- личающийся тем, что, с целью повышения точности преобразователя, в нем дополнительно установлены второй реверсивный счетчик, пятый и

5 шестой синхронизаторы, третий блок задержки и делитель частоты, соеди- -. ненный входом с выходом тактового генератора, а вькодом - с информационным входом пятого синхронизатора

513981

И: через третий блок задержки - с ин- ф|ормационным входом шестого синхронизатора, тактовые входы пятого и шестого синхронизаторов подключены соот- ветственно к шестому и седьмому выходам распределителя импульсов, а выходы - к первым входам соответственно первого и второго элементов ИЛИ, соединенных выходами соответственно С ю вЬмитающим и суммируюа1им входами второго реверсивного счетчика, выход

Фиг.1

16

которого является вторым выходом преобразователя, а установочный вход соединен с установочным входом первого реверсивного счетчика, второй и третий входы первого элемента ИЛИ подключены к выходам соответственно третьего и четвертого синхронизаторов., а второй и третий входы второго элемента ИЛИ соединены с выходами соответственно первого и второго синхронизаторов.

| Устройство для стабилизации суммарной частоты дифференциального струнного датчика | 1973 |

|

SU459759A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Преобразователь частоты в код | 1983 |

|

SU1112551A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-05-23—Публикация

1986-07-14—Подача