NU

о

kiMk

сл

СП N3

«.

Изобретение относится к радиотехнике и может быть использовано для построения цифровых приемников и передатчиков, управляемых генераторов функций, преобразователей цифровых величин в частоту, напряжение, ток.

Целью изобретения является расширение диапазона синтезируемых частот.

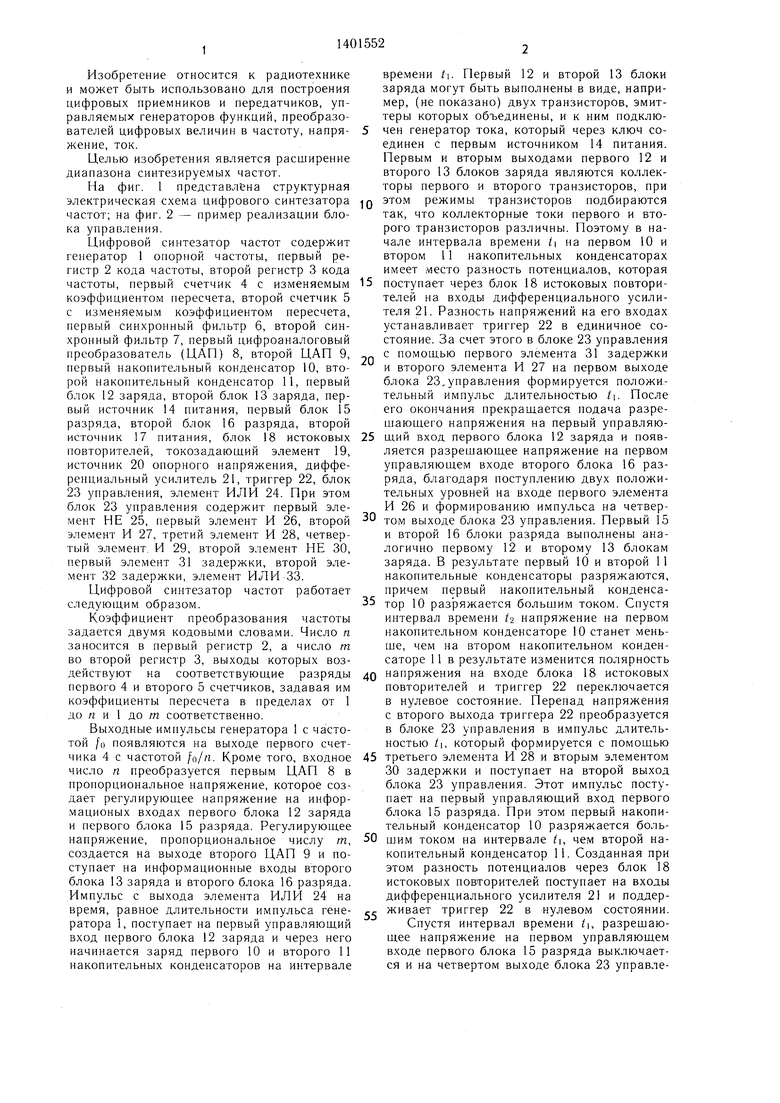

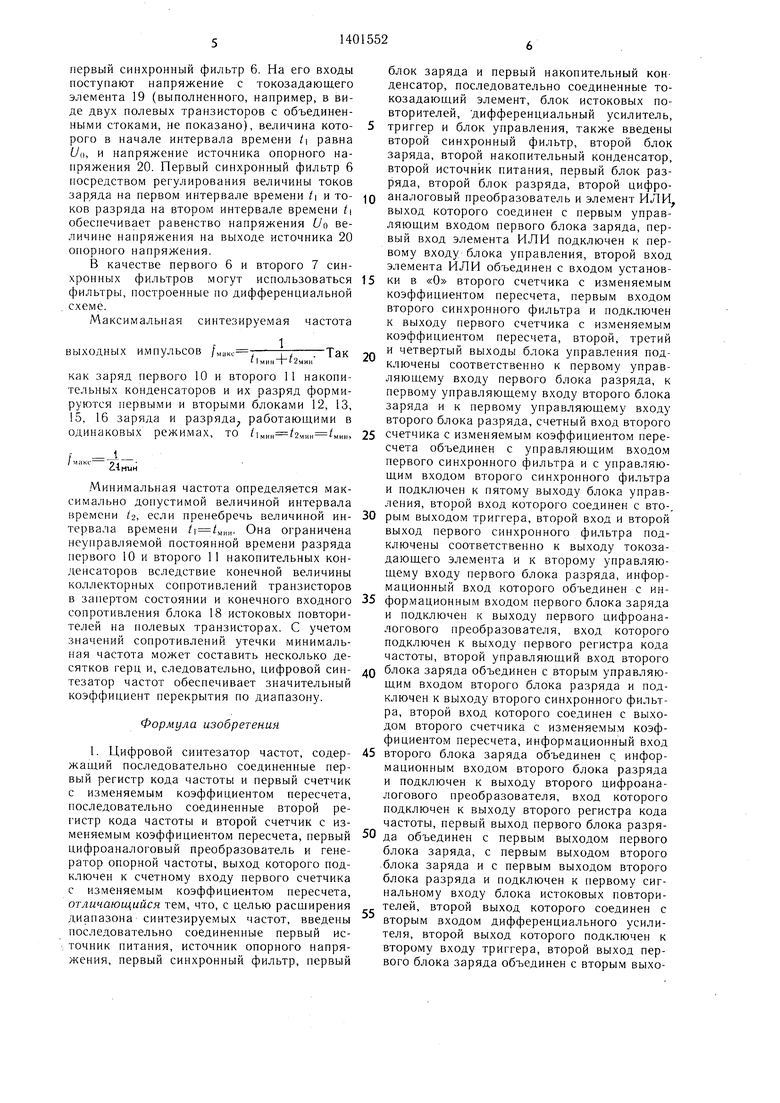

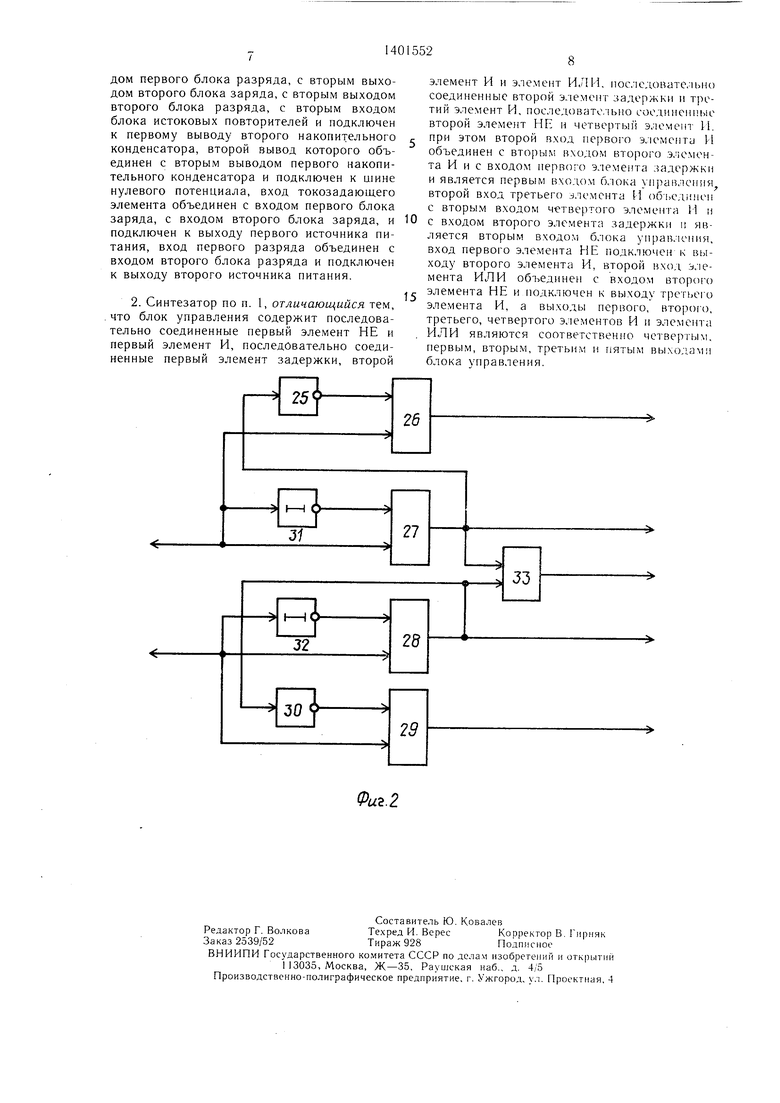

На фиг. 1 представлена структурная электрическая схема цифрового синтезатора частот; на фиг. 2 - пример реализации блока управления.

Цифровой синтезатор частот содержит генератор 1 опорной частоты, первый регистр 2 кода частоты, второй регистр 3 кода частоты, первый счетчик 4 с изменяемым коэффициентом пересчета, второй счетчик 5 с изменяемым коэффициентом пересчета, первый синхронный фильтр 6, второй синхронный фильтр 7, первый цифроаналоговый преобразователь (ЦАП) 8, второй ЦАП 9, первый накопительный конденсатор 10, второй накопительный конденсатор 11, первый блок 12 заряда, второй блок 13 заряда, первый источник 14 питания, первый блок 15 разряда, второй блок 16 разряда, второй источник 17 питания, блок 18 истоковых повторителей, токозадающий элемент 19, источник 20 опорного напряжения, дифференциальный усилитель 21, триггер 22, блок 23 управления, элемент ИЛИ 24. Цри этом блок 23 управления содержит первый элемент НЕ 25, первый элемент И 26, второй элемент И 27, третий элемент И 28, четвертый элемент. И 29, второй элемент НЕ 30, первый элемент 31 задержки, второй элемент 32 задержки, элемент ИЛИ 33.

Цифровой синтезатор частот работает следующим образом.

Коэффициент преобразования частоты задается двумя кодовыми словами. Число п заносится в первый регистр 2, а число т во второй регистр 3, выходы которых воздействуют на соответствующие разряды первого 4 и второго 5 счетчиков, задавая им коэффициенты пересчета в пределах От 1 до л и 1 до m соответственно.

Выходные импульсы генератора 1 с частотой /о появляются на выходе первого счетчика 4 с частотой fn/n. Кроме того, входное число п преобразуется первым ЦАП 8 в пропорциональное напряжение, которое создает регулирующее напряжение на инфор- мационых входах первого блока 12 заряда и первого блока 15 разряда. Регулирующее напряжение, пропорциональное числу т, создается на выходе второго ЦАЦ 9 и поступает на информационные входы второго блока 13 заряда и второго блока 16 разряда. Импульс с выхода элемента ИЛИ 24 на время, равное длительности импульса генератора 1, поступает на первый управляющий вход первого блока 12 заряда и через него начинается заряд первого 10 и второго 11 накопительных конденсаторов на интервале

0

времени t. Первый 12 и второй 13 блоки заряда могут быть выполнены в виде, например, (не показано) двух транзисторов, эмиттеры которых объединены, и к ним подключен генератор тока, который через ключ соединен с первым источником 14 питания. Первым и вторым выходами первого 12 и второго 13 блоков заряда являются коллекторы первого и второго транзисторов, при

этом режимы транзисторов подбираются так, что коллекторные токи первого и второго транзисторов различны. Поэтому в начале интервала времени /i па первом 10 и втором 11 накопительных конденсаторах имеет место разность потенциалов, которая

5 поступает через блок 18 истоковых повторителей на входы дифференциального усилителя 21. Разность напряжений на его входах устанавливает триггер 22 в единичное состояние. За счет этого в блоке 23 управления с помощью первого элемента 31 задержки и второго элемента И 27 на первом выходе блока 23,управления формируется положительный импульс длительностью t. После его окончания прекращается подача разрешающего напряжения на первый управляю5 щий вход первого блока 12 заряда и появляется разрещающее напряжение на первом управляющем входе второго блока 16 разряда, благодаря поступлению двух положительных уровней на входе первого элемента И 26 и формированию импульса на четвер0 том выходе блока 23 управления. Первый 15 и второй 16 блоки разряда выполнены аналогично первому 12 и второму 13 блокам заряда. В результате первый 10 и второй 11 накопительные конденсаторы разряжаются, причем первый накопительный конденса5 тор 10 разряжается больщим током. Спустя интервал времени /а напряжение на первом накопительном конденсаторе 10 станет мень- ще, чем на втором накопительном конденсаторе 11 в результате изменится полярность

0 напряжения на входе блока 18 истоковых повторителей и триггер 22 переключается в нулевое состояние. Перепад напряжения с второго выхода триггера 22 преобразуется в блоке 23 управления в импульс длительностью t, который формируется с помощью

5 третьего элемента И 28 и вторым элементом 30 задержки и поступает на второй выход блока 23 управления. Этот импульс поступает на первый управляющий вход первого блока 15 разряда. При этом первый накопительный конденсатор 10 разряжается боль0 щим током на интервале t, чем второй накопительный конденсатор 11. Созданная при этом разность потенциалов через блок 18 истоковых повторителей поступает на входы дифференциального усилителя 21 и поддерживает триггер 22 в нулевом состоянии. Спустя интервал времени t, разрещающее напряжение на первом управляющем входе первого блока 15 разряда выключается и на четвертом выходе блока 23 управления появляется импульс, поступающий на первый управляющий вход второго блока 13 заряда. Поскольку на информационный вход второго блока 13 заряда поступает напряжение с выхода второго ЦАП 9, то первый накопительный конденсатор 10 заряжается большим током чем второй накопительный конденсатор 11. Через время /2 наступает момент, когда напряжение на первом накопительном конденсаторе 10 превыщает напряжение на втором накопительном конденсаторе 11. В этот момент переключается триггер 22. При этом выключается импульс на четвертом выходе блока управления, а по положительному перепаду напряжения

10

потенциалы примерно равны. Т зом, частота импульсов на вых вого синтезатора частот, в качес используется пятый выход блока

ния, равна /,/о-

Заряд и разряд первого 10 и накопительных конденсаторов п относительно среднего уровня L U интервале времени t после импульса с первого счетчика 4 п пительный конденсатор 10 зар первого источника 14 питания п ком 12 заряда меньшим током

на единичном выходе триггера 22 форми- 5 накопительный конденсатор 1

током. Поэтому в конце интерва t первый накопительный конд оказывается заряженным до бо пряжения, чем второй накопите денсатор 11. На |ервом интерв

руется напряжение на первом выходе оло- ка 23 управления и цикл работы повторяется.

Количество циклов t и /2, укладывающихся в периоде поступления импульсов

с первого счетчика 4, определяется коэффи- 20 /2 первый накопите.чьный конденсатор 10 циентом пересчета второго счетчика 5. С этойразряжается вторым блоком 16 разряд;;,

который управляется с- выхода третьего элемента И 28 блока 23 управления большим

током. Поэтому в конце интерва.ча времени t первый накопительный конденсатор 10 оказывается заряженным до болыпего напряжения, чем второй накопительный кип- денсатор 11. На |ервом интервале времени

целью выходным импульсом первого счетчика 4 второй счетчик 5 усганавливается в нуль, количество переключений триггера 22

током, чем второй накопительным конденчерез элемент ИЛИ 33 блока 23 управления 25 - зтор 11. Конец интервала времени t-i соотпоступает на счетный вход второго счетчика 5. Если между двумя выходными импульсами первого счетчика 4 на вход второго счетчика 5 поступает меньше m импульсов, то в момент запуска второго синхронного

ветствует моменту времени, когда потенциал на первом накопительном конденсаторе 10 станет меньше потенциала на втором накопительном конденсаторе И. После этого момента времени начинается второй интер фильтра 7, совпадающим с переключением 30 взл времени t, на котором в отличие от перпервого счетчика 4, на вход второго синхронного фильтра 7 от второго счетчика 5 поступает положительный уровень, который превышает уровень на выходе первого счетчика 4 в момент стробирования. Разность

вого интервала времени t, первый накопительный конденсатор 10 разряжается током первого блока 5 разряда большей величины, чем ток разряда второго накопительного конденсатора 11. В конце второго интервала

уровней запоминается вторым синхронным35 времени t первый накопительный конденфильтром 7 и используется для регулиро-сатор 10 оказывается разряженным до бования величины тока заряда и разряда пер-лее низкого потенциала, чем второй накопивого 10 и второго 11 накопительных конден-тельный конденсатор 11. На втором интерсаторов через второй блок 13 заряда от пер-вале времени tz первый накопительный конвого источника 14 питания и через второйденсатор 10 заряжается от второго блока 13

блок 16 разряда от второго источника 17 заряда быстрее чем второй накопительный

питания. Увеличение тока приводит к умень-конденсатор 11, после чего второй блок 13

шению времени заряда и, следовательно,заряда выключается и включается первый

к увеличению количества импульсов, по-блок 12 заряда и начинается следующий

ступающих на второй счетчик 5 за периодцикл работы устройства. Длительность инмежду импульсами первого счетчика 5. Если.г тервалов времени i постоянна и задается

количество таких импульсов больше, то вдлительностью импульсов на первом и третьмомент стробирования второго синхронного фильтра 7 запоминается отрицательная разность напряжений на его входах, что приводит к уменьшению тока второго блока 13

ем выходах блока 23 управления (задержками первого 31 и второго 32 элементов задержки), а длительность инте1 )валов времени /2 определяется соотношением величин

заряда и второго блока 16 разряда и к умень- 50 токов на выходах второго блока 16 разряда

щению количества импульсов на втором счетчике 5. В связи с тем, что второй синхронный фильтр 7 имеет большую постоянную времени по сравнению с периодом стробирования, на его выходе устанавливается такое

для первого интервала времени i- и величины токов на выходах второго блока 13 заряда для второго интервала времени t-i.

Для выполнения баланса величин токов заряда и разряда первого 10 и второго 1

выходное напряжение, при котором на вто-55 накопительных конденсаторов на периоде порой счетчик 7 поступает ровно т импульсовступления импульсов первого счетчика 4 и, за период. При этом в моменты стробирова-следовательно, чтобь подд(Г| й ивать неиз- ния на входах второго синхронного фильтраменным начальный уровень заряд&4..(| введен

0

потенциалы примерно равны. Таким об; . зом, частота импульсов на выходе циф)п- вого синтезатора частот, в качестве которого используется пятый выход блока 23 управ, 1ения, равна /,/о-

Заряд и разряд первого 10 и второго И накопительных конденсаторов производится относительно среднего уровня L U. На первом интервале времени t после поступления импульса с первого счетчика 4 первый накопительный конденсатор 10 заряжается o l первого источника 14 питания первым б. ю- ком 12 заряда меньшим током, а второй

О( 1ЬШ11М

накопительный конденсатор 1

/2 первый накопите.чьный конденсатор 10 разряжается вторым блоком 16 разряд;;,

током. Поэтому в конце интерва.ча времени t первый накопительный конденсатор 10 оказывается заряженным до болыпего напряжения, чем второй накопительный кип- денсатор 11. На |ервом интервале времени

током, чем второй накопительным конден - зтор 11. Конец интервала времени t-i соответствует моменту времени, когда потенциал на первом накопительном конденсаторе 10 станет меньше потенциала на втором накопительном конденсаторе И. После этого момента времени начинается второй интервого интервала времени t, первый накопительный конденсатор 10 разряжается током первого блока 5 разряда большей величины, чем ток разряда второго накопительного конденсатора 11. В конце второго интервала

длительностью импульсов на первом и третьем выходах блока 23 управления (задержками первого 31 и второго 32 элементов задержки), а длительность инте1 )валов времени /2 определяется соотношением величин

для первого интервала времени i- и величины токов на выходах второго блока 13 заряда для второго интервала времени t-i.

Для выполнения баланса величин токов заряда и разряда первого 10 и второго 1

накопительных конденсаторов на периоде поступления импульсов первого счетчика 4 и, следовательно, чтобь подд(Г| й ивать неиз- менным начальный уровень заряд&4..(| введен

первый синхронный фильтр 6. На его входы поступают напряжение с токозадающего э пемента 19 (выполненного, например, в виде двух полевых транзисторов с объединенными стоками, не показано), величина которого в начале интервала времени t равна UH, и напряжение источника опорного напряжения 20. Первый синхронный фильтр 6 посредством регулирования величины токов заряда на первом интервале времени t и токов разряда на втором интервале времени ti обеспечивает равенство напряжения UQ величине напряжения на выходе источника 20 опорного напряжения.

В качестве первого 6 и второго 7 синхронных фильтров могут использоваться фильтры, построенные по дифференциальной схеме.

Максимальная синтезируемая частота

выходных импульсов /макс : ПГ Так

1ми1| г 2мин

как заряд первого 10 и второго 11 накопительных конденсаторов и их разряд формируются первыми и вторыми блоками 12, 13, 15, 16 заряда и разряда работающими в одинаковых режимах, то 1„„„ /2мин мин

/ -Л - ,.н

Минимальная частота определяется максимально допустимой величиной интервала времени t, если пренебречь величиной интервала времени 1 1,„„. Она ограничена неуправляемой постоянной времени разряда первого 10 и второго 11 накопительных конденсаторов вследствие конечной величины коллекторных сопротивлений транзисторов в запертом состоянии и конечного входного сопротивления блока 18 истоковых повторителей на полевых транзисторах. С учетом значений сопротивлений утечки минимальная частота может составить несколько десятков герц и, следовательно, цифровой синтезатор частот обеспечивает значительный коэффициент перекрытия по диапазону.

Формула изобретения

1. Цифровой синтезатор частот, содержащий последовательно соединенные первый регистр кода частоты и первый счетчик с изменяемым коэффициентом пересчета, последовательно соединенные второй регистр кода частоты и второй счетчик с изменяемым коэффициентом пересчета, первый цифроаналоговый преобразователь и генератор опорной частоты, выход которого подключен к счетному входу первого счетчика с изменяемым коэффициентом пересчета, отличающийся тем, что, с целью расщирения диапазона синтезируемых частот, введены последовательно соединенные первый ис- , точник питания, источник опорного напряжения, первый синхронный фильтр, первый

блок заряда и первый накопительный конденсатор, последовательно соединенные то- козадающий элемент, блок истоковых повторителей, дифференциальный усилитель,

триггер и блок управления, также введены второй синхронный фильтр, второй блок заряда, второй накопительный конденсатор, второй источник питания, первый блок разряда, второй блок разряда, второй цифроаналоговый преобразователь и элемент ИЛИ выход которого соединен с первым управляющим входом первого блока заряда, первый вход элемента ИЛИ подключен к первому входу блока управления, второй вход эле.мента ИЛИ объединен с входом установ5 ки в «О второго счетчика с изменяемым коэффициентом пересчета, первым входом второго синхронного фильтра и подключен к выходу первого счетчика с изменяемым коэффициентом пересчета, второй, третий

и четвертый выходы блока управления под- к.тючены соответственно к первому управляющему входу первого блока разряда, к первому управляющему входу второго блока заряда и к первому управляющему входу второго блока разряда, счетный вход второго

5 счетчика с изменяемым коэффициентом пересчета объединен с управляющим входом первого синхронного фильтра и с управляющим входом второго синхронного фильтра и подключен к пятому выходу блока управления, второй вход которого соединен с вто-,

0 рым выходом триггера, второй вход и второй выход первого синхронного фильтра подключены соответственно к выходу токозадающего элемента и к второму управляющему входу первого блока разряда, информационный вход которого объединен с ин5 формационным входом первого блока заряда и подключен к выходу первого цифроана- логового преобразователя, вход которого подключен к выходу первого регистра кода частоты, второй управляющий вход второго

0 блока заряда объединен с вторым управляющим входом второго блока разряда и подключен к выходу второго синхронного фильтра, второй вход которого соединен с выходом второго счетчика с изменяемым коэффициентом пересчета, информационный вход

5 второго блока заряда объединен Q информационным входом второго блока разряда и подключен к выходу второго цифроана- логового преобразователя, вход которого подключен к выходу второго регистра кода частоты, первый выход первого блока разря0 да объединен с первым выходом первого блока заряда, с первым выходо.м второго блока заряда и с первым выходом второго блока разряда и подключен к первому сигнальному входу блока истоковых повторителей, второй выход которого соединен с вторым входом дифференциального усилителя, второй выход которого подключен к второму входу триггера, второй выход первого блока заряда объединен с вторым выходом первого блока разряда, с вторым выходом второго блока заряда, с вторым выходом второго блока разряда, с вторым входом блока истоковых повторителей и подключен к первому выводу второго накопительного конденсатора, второй вывод которого объединен с вторым выводом первого накопительного конденсатора и подключен к шине нулевого потенциала, вход токозадающего элемента объединен с входом первого блока заряда, с входом второго блока заряда, и подключен к выходу первого источника питания, вход первого разряда объединен с входом второго блока разряда и подключен к выходу второго источника питания.

2. Синтезатор по п. 1, отличающийся тем, . что блок управления содержит последовательно соединенные первый элемент НЕ и первый элемент И, последовательно соединенные первый элемент задержки, второй

элемент И и элемент ИЛИ, последовате, 1ЬН(:) соединенные второй элемент задержки и третий элемент И, последовато.чьно соодиненные второй элеме)1т НЕ: и четвертый элемент 11. при этом второй вход первого элемента Н объединен с вторым входом второго э.1е.1ен- та И и с входом первого элемента задержки и является первым входо.м блока управления второй вход третьего элемента И с вторым входом ч твертого элемента И и

с входом второго элемента задержки is является вторым в.чодом блока управ.юния, вход первого элемента НЕ подключен к выходу второго элемента И, второй вход элемента ИЛИ объединен с входом вторсич)

элемента НЕ и подключен к выходу третьего элемента И, а выходы первого, второ1Ч), третьего, четвертого элементов И и эле.мента ИЛИ являются соответственно четвертым, первым, вторым, третьим и пятым выходами блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство следящей блокировки аппаратуры акустического каротажа | 1980 |

|

SU898368A2 |

| Преобразователь напряжения в частоту | 1988 |

|

SU1522407A1 |

| Способ измерения проводимости и диэлектрической проницаемости и устройство для его осуществления | 1989 |

|

SU1698824A1 |

| Времяимпульсный амплитудный преобразователь | 1986 |

|

SU1435131A1 |

| Устройство для измерения электрической проводимости и магнитной проницаемости | 1989 |

|

SU1659928A1 |

| Емкостное накопительное устройство | 1975 |

|

SU555540A1 |

| Устройство для фиксации уровня аналоговых сигналов | 1973 |

|

SU439019A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| Устройство для измерения рассогласования между углом и кодом | 1985 |

|

SU1277397A1 |

| Синтезатор частот | 1984 |

|

SU1283964A1 |

Изобретение относится к радиотехнике. Целью изобретения является расширение диапазона синтезируемых частот. Для достижения цели в устр-во введены последовательно соединенные источник 14 питания, источник 20 опорного напряжения, синхронный фильтр (СФ) 6, блок 12 заряда (53) и накопительный конд-р (НК) 10, последовательно соединенные токозадаюпхий элемент 19, Г), К)К 18 нетоковых поиторито. icii, дифференциальный у-.1ь 21. триггер 22 и блок 23 управло 111я, а также введены СФ 7, 53 13, НК 11, источник 17 нитания, б. юки 15 и 16 разряда, ЦА11 9 и э,:1емент ИЛИ 24. Максимальная синтезируемая частота ходных и.мпульсов /,iiKi 1/2/,,iui- Минима.чь- ная частота определяется максима.льно допустимой величиной интервала в)еме1{и l, если пренебречь величиной интервала времени /| /„„,1- Она ограничена неуправ,:1яемой постоянной времени разряда НК И) и 11 вследствие конечной величины ко. 1лекторных сопротивлений транзисто)ов в запертом состоянии и конечного входного сопротивления блока 18 истоковых повторителей. С учетом значений сопротивлений утечки ми- пим. частота может состави 1 ь несколько десятков герц и. следова1е;1ьно, устр-во обеспечивает значительный коэф. нерекры- тия по дианазону. 1 з. п. ф-лы, 2 нл. (О (Л

| Шапиро Д | |||

| Н | |||

| и др | |||

| Основы теории синтеза частот | |||

| Радио и связь, 1981, с | |||

| Вагонетка для движения по одной колее в обоих направлениях | 1920 |

|

SU179A1 |

| Патент США № 3735269, кл | |||

| Способ переработки сплавов меди и цинка (латуни) | 1922 |

|

SU328A1 |

Авторы

Даты

1988-06-07—Публикация

1986-03-31—Подача