(

4:

О ОО

о ел

5

Р

Изобретение относится к вь)1числительной технике и может быть использовано в автоматизированных системах управления различными физическими нроцессами для сбора аналоговой информации с датчиков объекта и ввода ее в ЭВМ.

Цель изобретения - повышение быстродействия устройства и исключение избыточности вводимой информации.

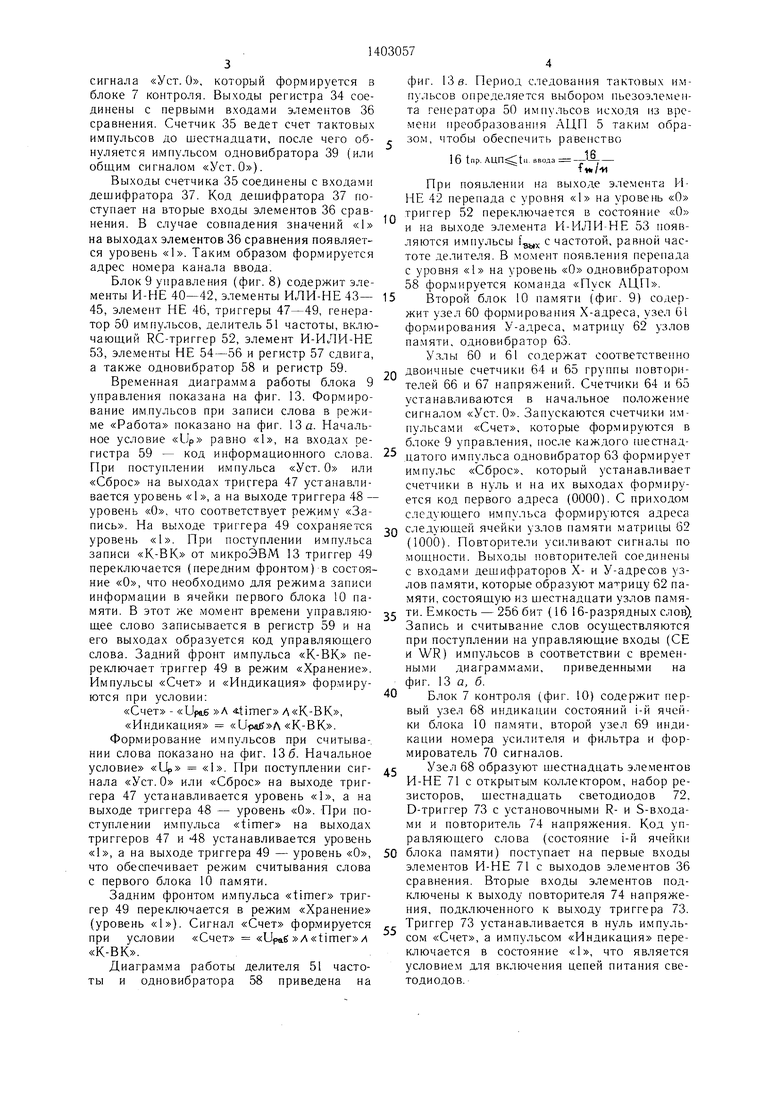

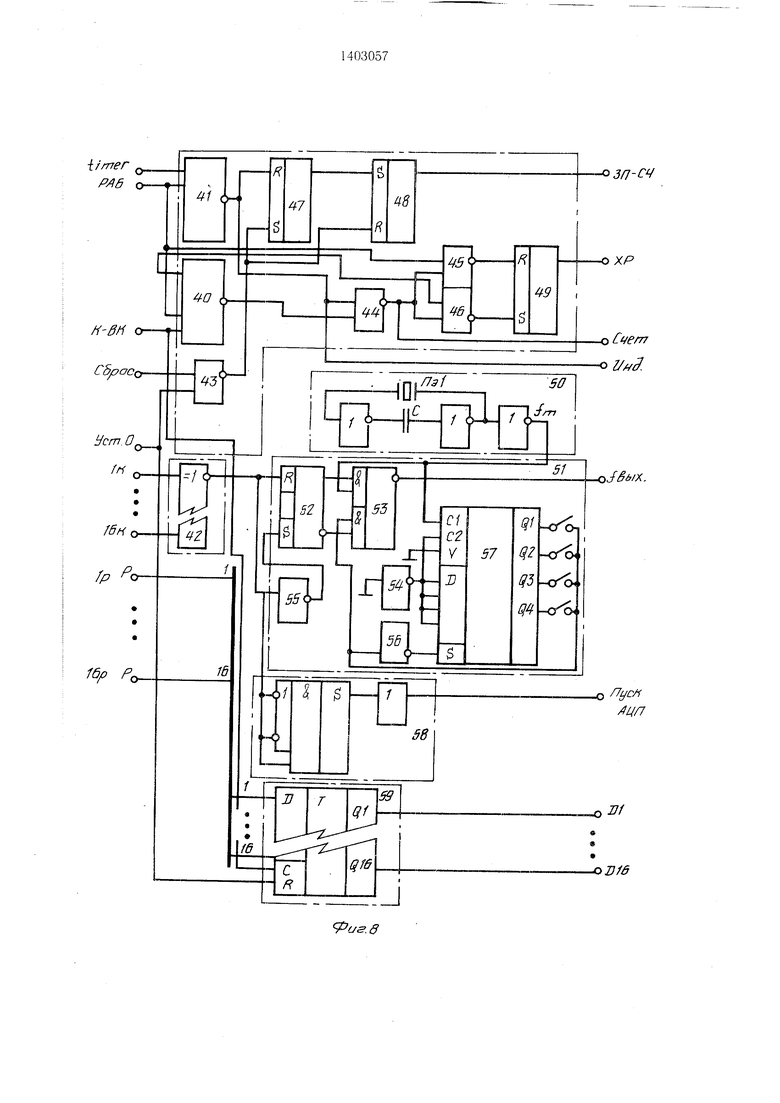

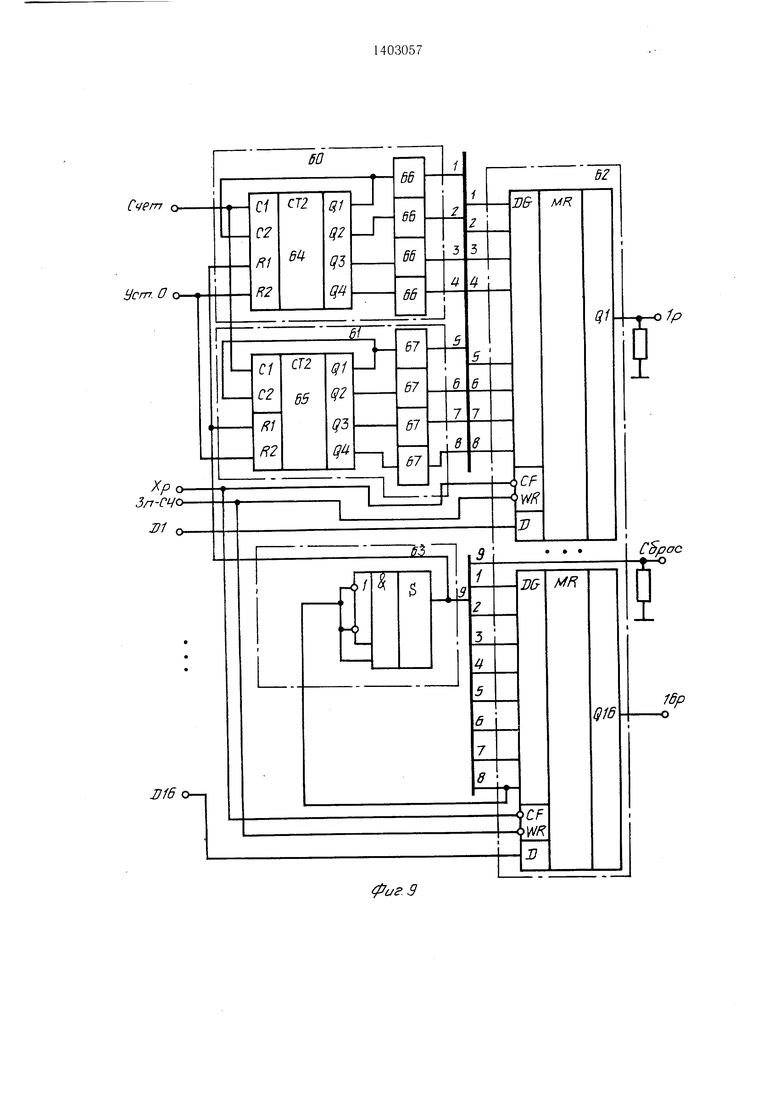

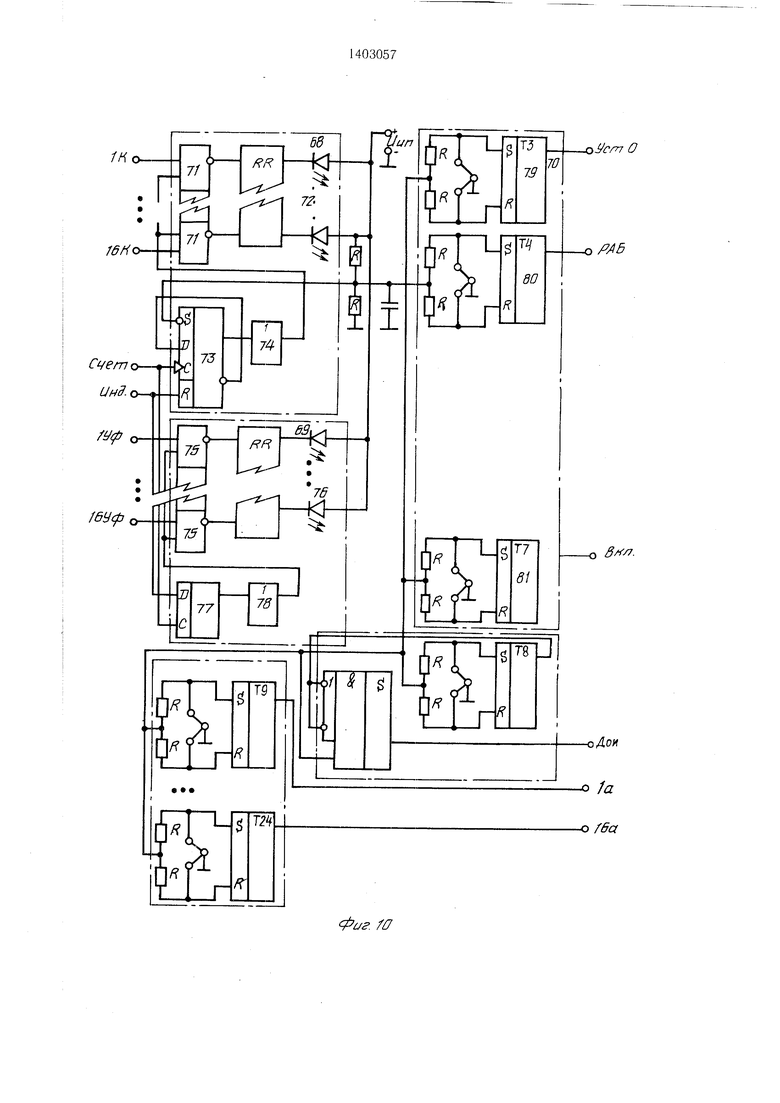

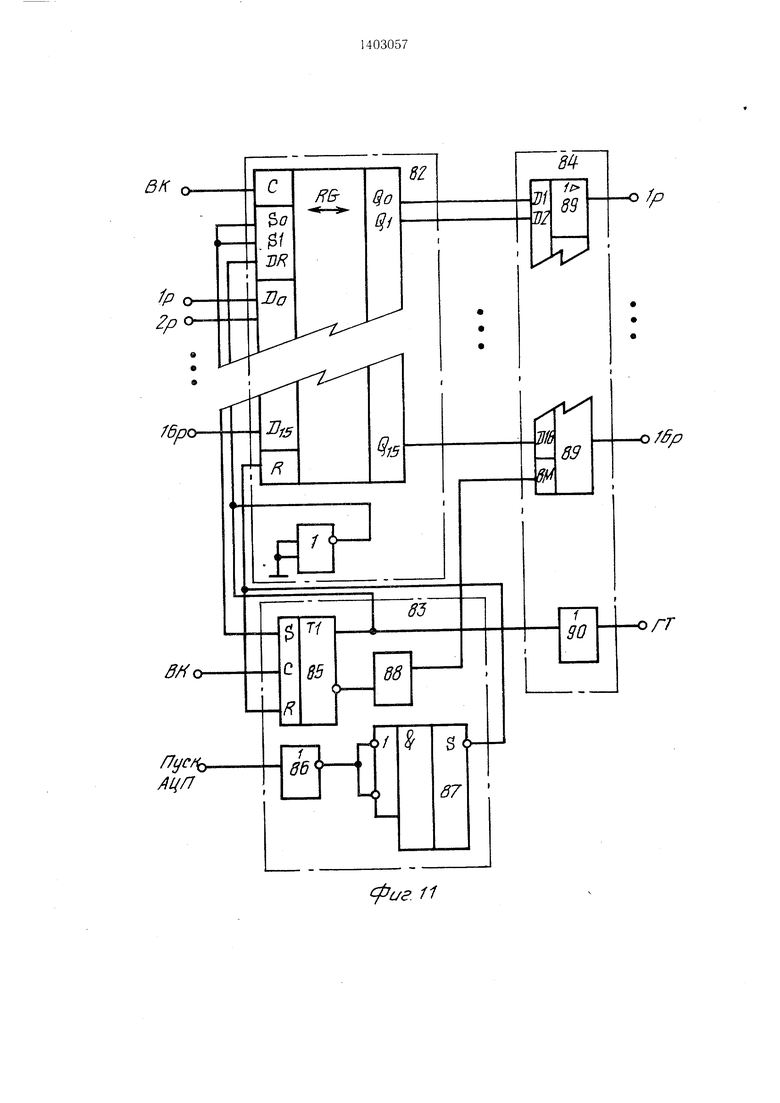

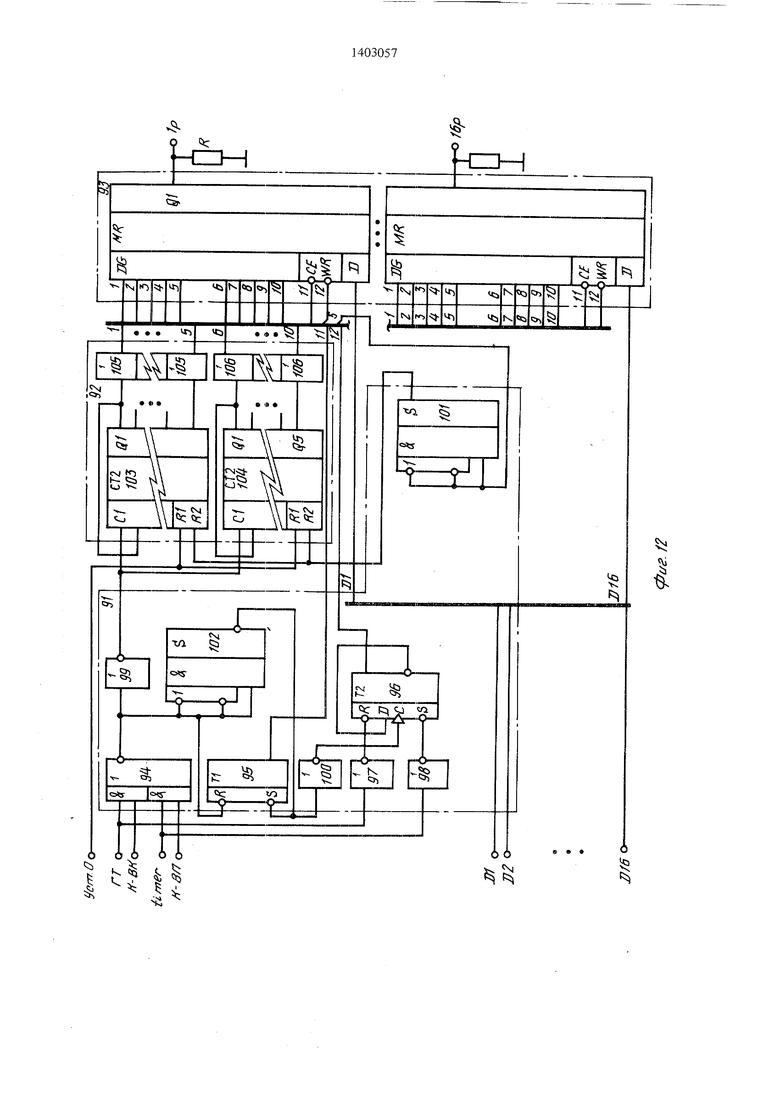

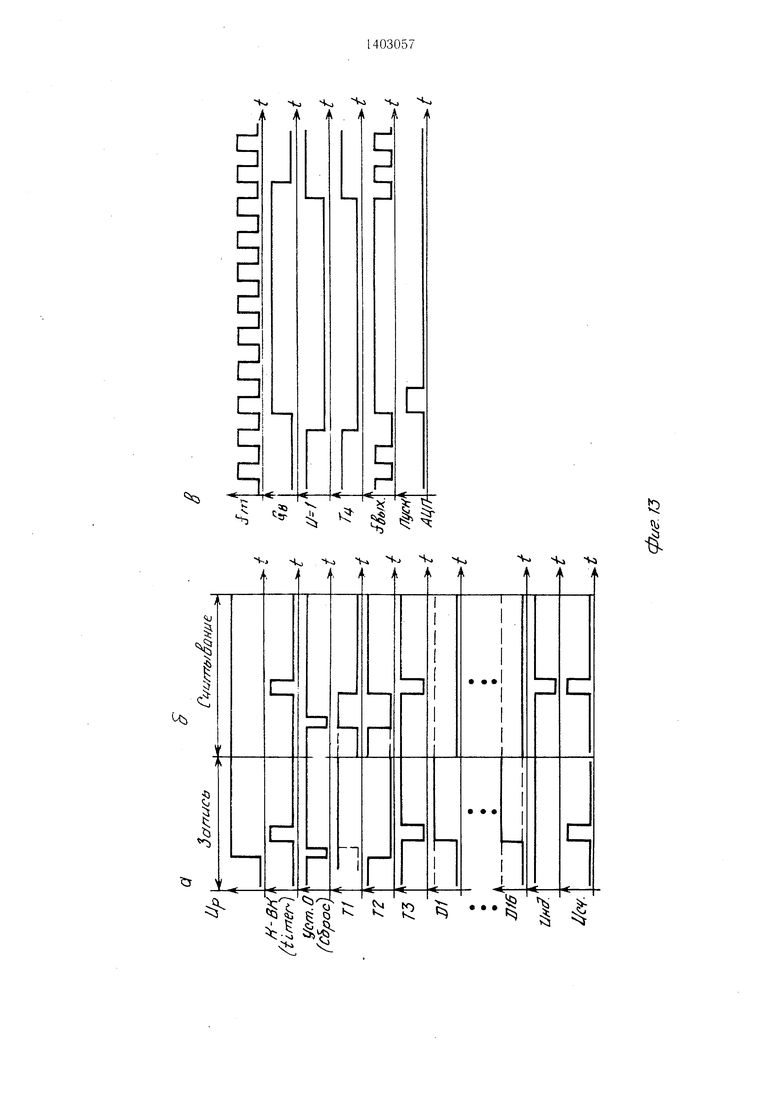

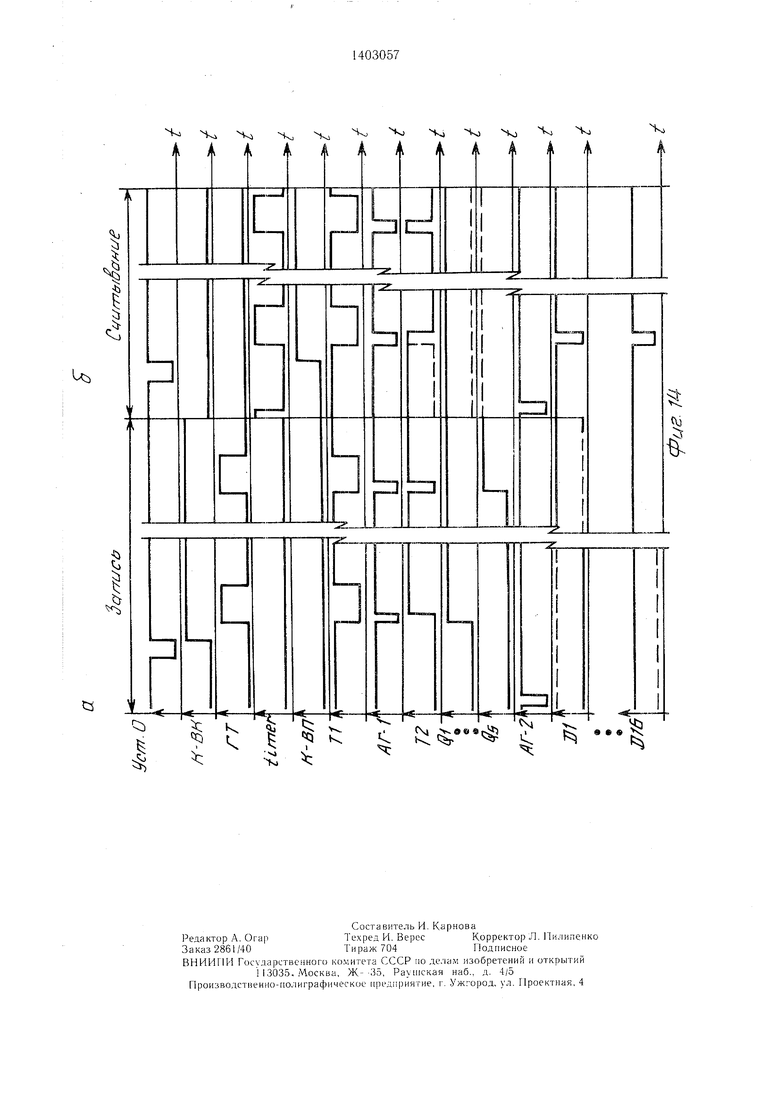

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - функциональная схема блока усилителей; на фиг. 3 - функциональная схе.ма блока фильтров нижних частот; на фиг. 4 - функциональная схема регистра управляющих слов; на фиг. 5 - функциональная схема коммутатора каналов; на фиг. 6 - функциональная схема блока узлов выборки и хранения; на фиг. 7 - функциональная схема блока выбора каналов; на фиг. 8 - cxe.via блока управления; на фиг . 9 - схема второго блока памяти; на фиг. 10 - функциональная схема блока контроля; на фиг. 11 - схема вы- ходног о регистра; на фи1 . 12 - функциональная схема первого блока памяти; на фиг. 13 и 14 - временные диаграммы работы.

Многоканальное устройство ввода аналоговой информации содержит усилители 1, фильтры 2 нижних частот, узлы 3 выборки и хранения, коммутатор 4 каналов, аналого- цифровой преобразователь (АЦП) 5, ре- | истр 6 управляющих слов, блок 7 контроля, блок 8 выбора каналов, блок 9 управления, второй блок 10 памяти, выходной регистр 1 1, первый блок 12 памяти и микроЭВМ 13. На фиг. 1 обозначены также входы 14 и выходы 15 устройства.

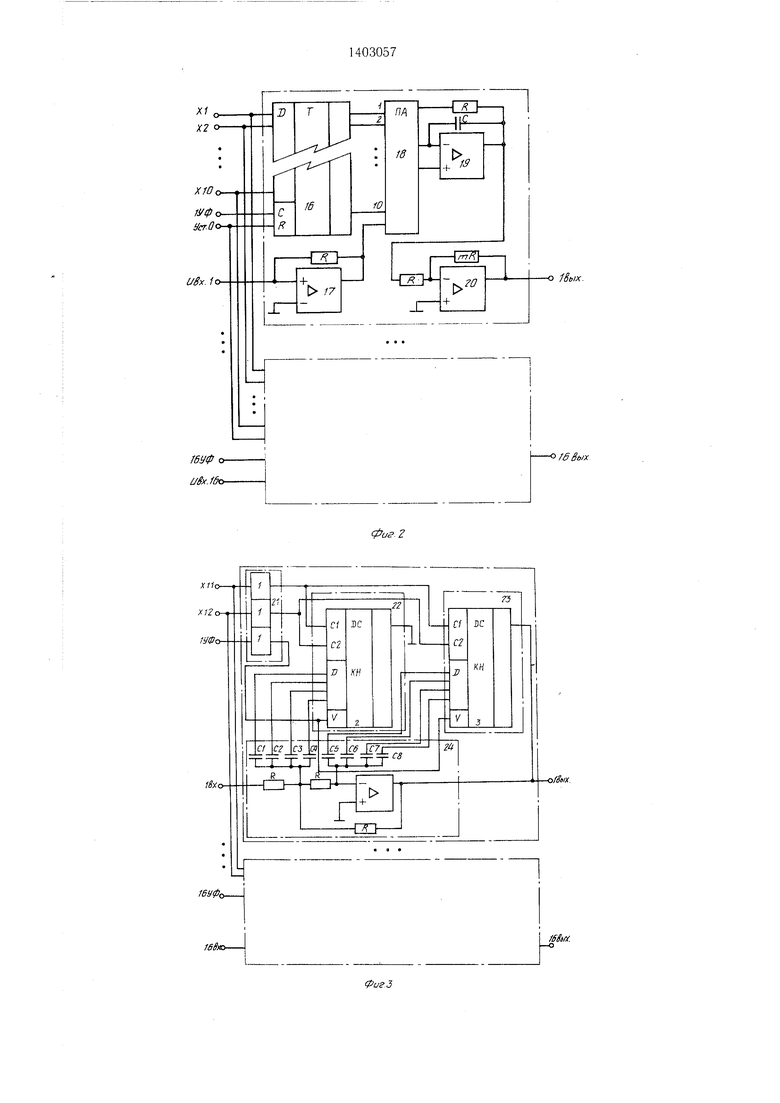

Усилители (масштабирующие) но числу каналов ввода содержат каждый (фиг. 2) регистр 16 кода, повторитель 17 на онера- ЦИО1ПЮ.М усилителе, умножающий цифро- аналоговый преобразователь 18, интегратор 19 на операционном усилителе, нормирующий усилитель 20 на операционном усилителе.

Блок фильтров нижних частот (по числу каналов ввода) содержит 16 активных RC- фильтров, каждый из которых включает узел 21 входных новторителей, аналоговый коммутатор 22 конденсаторов С1-С4, аналоговый коммутатор 23 конденсаторов С5 - С8 и RC-звено 24 второго порядка, выполненное на операционном усилителе с много- цетлевой обратной связью.

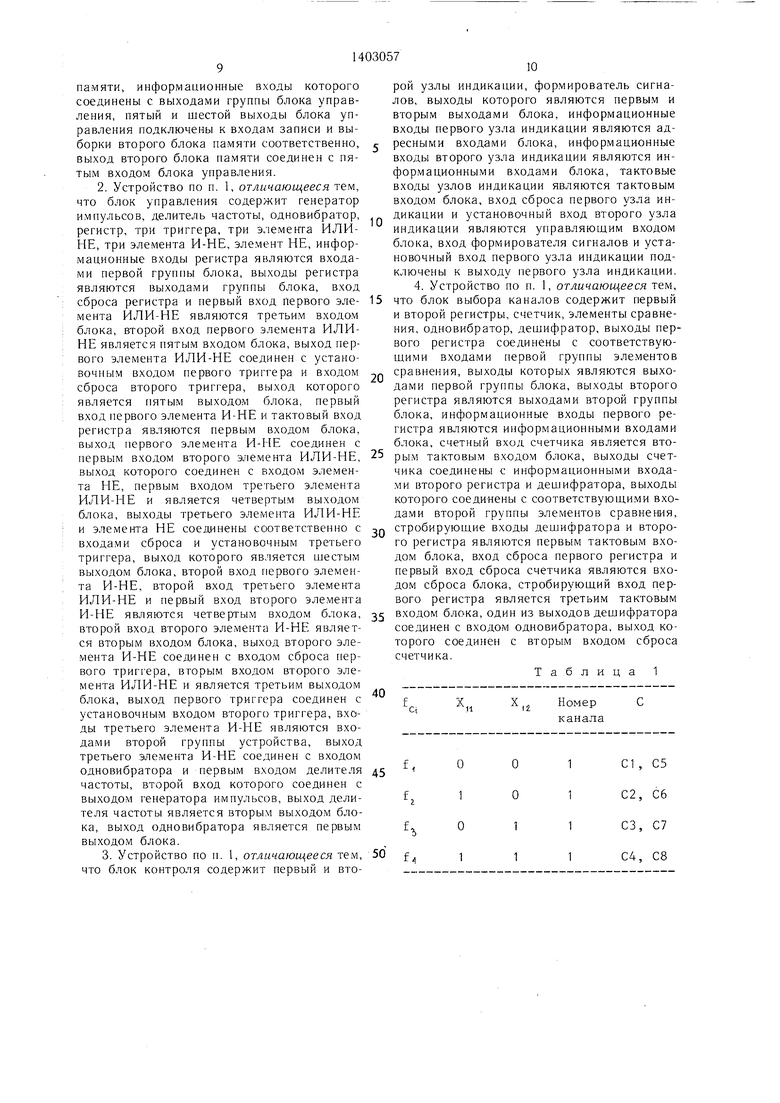

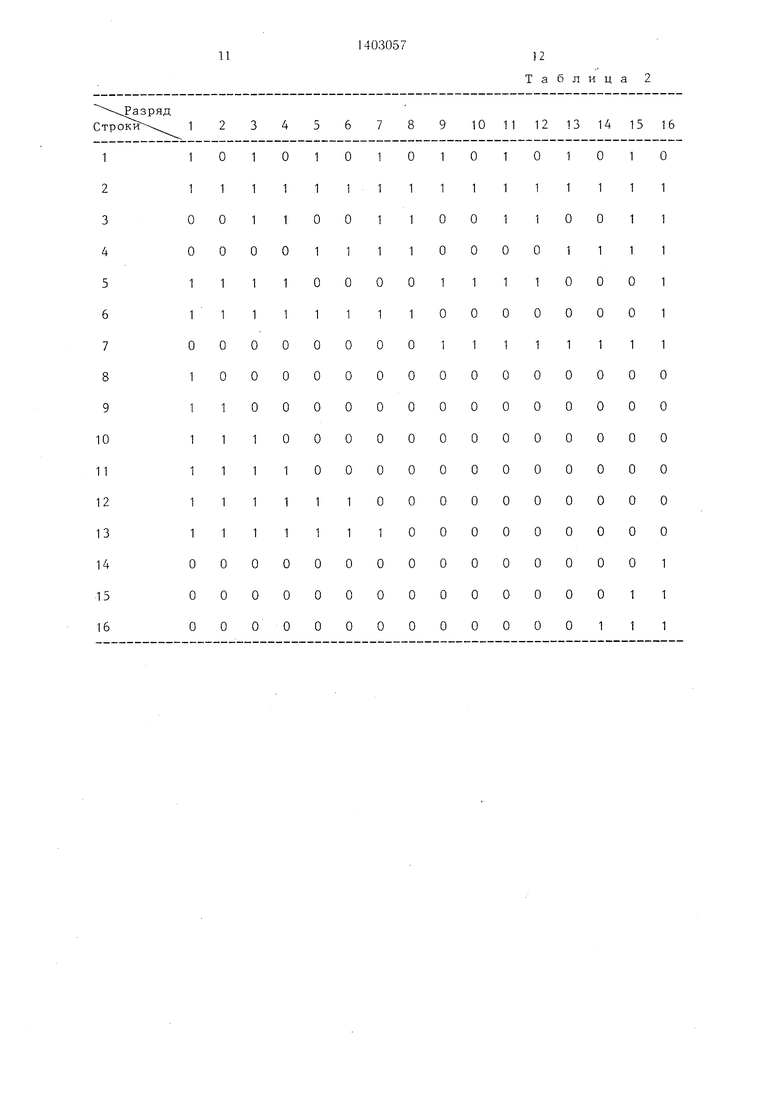

Выбор номера фильтра нижних частот и полосы пропускания частот определяется кодом управляющего слова. Соответствие значений кода и полосы пропускания частот приведено в .табл. 1.

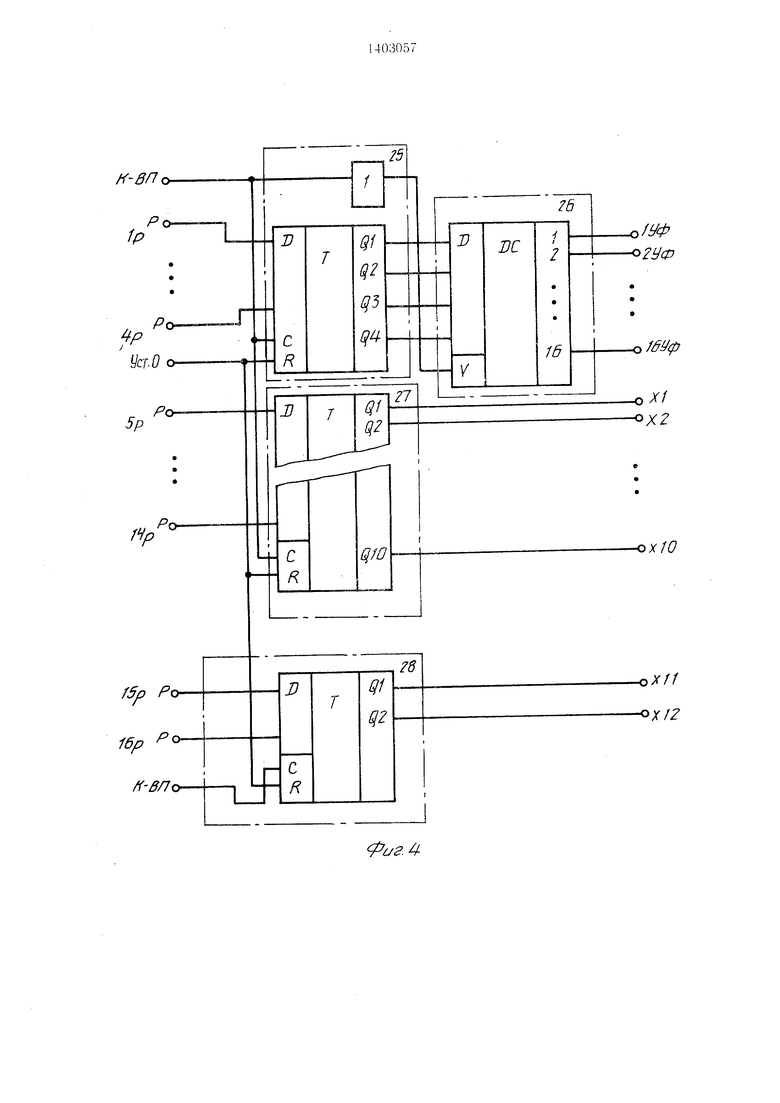

Регистр управляющих слов (фиг. 1) содержит регистр 25 кода номера канала, дешифратор 26 номера канала, регистр 27 ко

да коэффициентов усиления и регистр 28 кода полосы нропускания.

Коды номера канала, коды коэффициентов усиления задаются от микроЭВМ 13. Старшие четыре разряда (1-4) отведены для записи (в двоичном коде) номера канала. Коду 0000 соответствует 1-й канал, коду 0001 - 2-й канал и т. д. Носледующие 10 разрядов (5--14) слова отведены для значений коэффициента усиления. Коду 0000000001 соответствует коэффициент усиления К, ,,

где N 1,2,

т, вели5

0

5

0

5

0

5

0

5

tiR.

чина гп зависит от отноншния ; в схеме

к.

(фиг. 2) нормирующего усилителя 20. Последующие два разряда (15 и 16) отведены для записи кода выбираемой полосы пропускания f., - 4.

Запись управляющего слова в соответствующие регистры осуп|ествляется при значениях «1 и «О на входах регистров 25, 27 и 28 при поступлении импульса записи «К-ВГГ от микроэвм 13 в режиме «Работа.

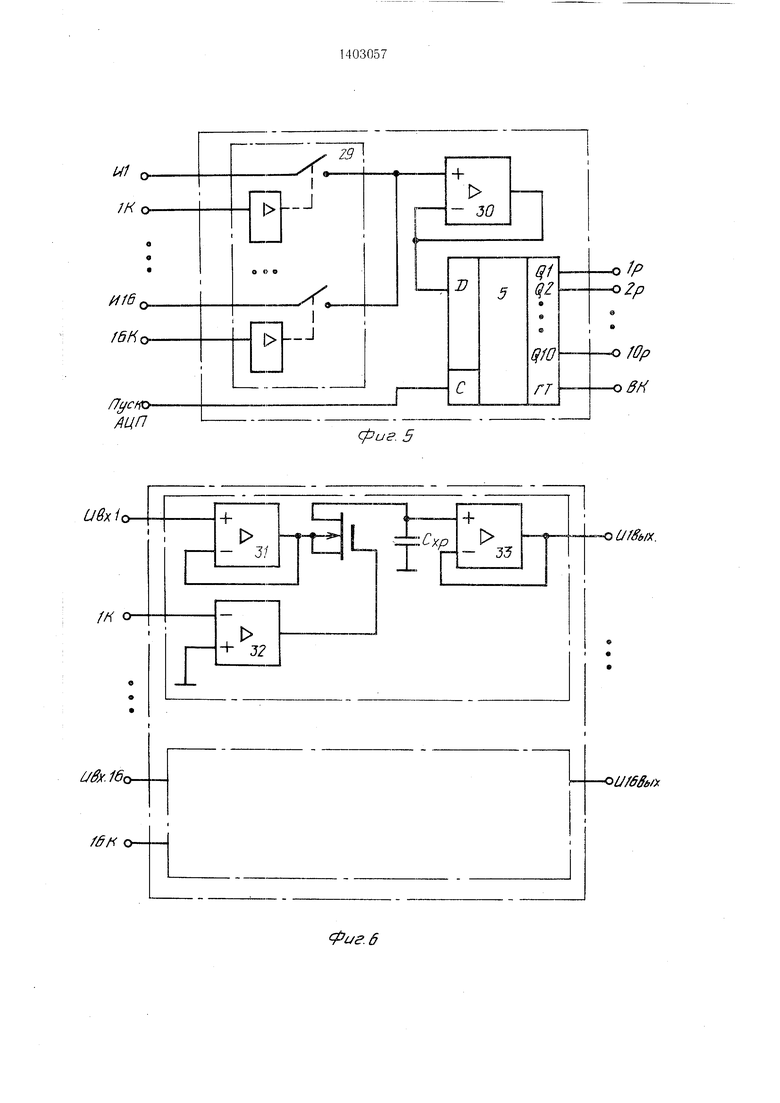

Коммутатор каналов (фиг. 5) содержит узел 29 ана. юговьгч коммутаторов, повторитель 30 на операционном усилителе. Коммутатор каналов имеет 16 аналоговых входов и один выход. Выбор канала коммутации осуществляется при поступлении на управляющие ВХОДЕ) коммутатора 4 каналов слова с блока выбора каналов. Если уровень сигнала i-ro разряда равен «О, то замыкается аналоговый ключ соответствующего канала. Если уровень сигнала, равен «1, то ключ разомкнут и аналоговые сигналы не проходят на вход повторителя 30 напряжения. Выход коммутатора подключен на из.меритель- ный вход АЦП 5.

Блок узлов выборки и хранения (фиг. 6) содержит 16 элементов выборки и хранения.

Аналоговый сигнал с выходов блока 2 |1оступает на вход операционного усилителя 31 узла выборки и хранения. Управляющим сигналом является и.мпульс «№ канала, который поступает на операционный усилитель 32 из блока 8 и перек-тючает узел выборки и хранения в режим «Храпение. Переключение в режим «Выборка осуществляется при сбросе импульса «№ канала. Операционный усилитель 33 является выходным повторителем

Блок 8 выбора каналов (фиг. 7) содержит первый регистр 34, счетчик 35, элемент 36 сравнения, дещифратор 37, второй регистр 38 и одновибратор 39.

Код выбора каналов ввода считывается с второго блока 10 памяти. Код поступает на входы первого регистра 34, который состоит из четырех D-триггеров, и записывается в регистр после поступления импульса считывания «Сч. им с блока 9. Обнуляется регистр 34 при поступлении на его вход сброса

сигнала «Уст. О, который формируется в блоке 7 контроля. Выходы регистра 34 соединены с первыми входами элементов 36 сравнения. Счетчик 35 ведет счет тактовых имнульсов до и естнадцати, после чего обнуляется импульсом одновибратора 39 (или обндим сигналом «Уст. О).

Выходы счетчика 35 соединены с входами дешифратора 37. Код дешифратора 37 поступает на вторые входы элементов 36 сравнения. В случае совпадения значений «1 на выходах элементов 36 сравнения появляется уровень «1. Таким образом формируется адрес номера канала ввода.

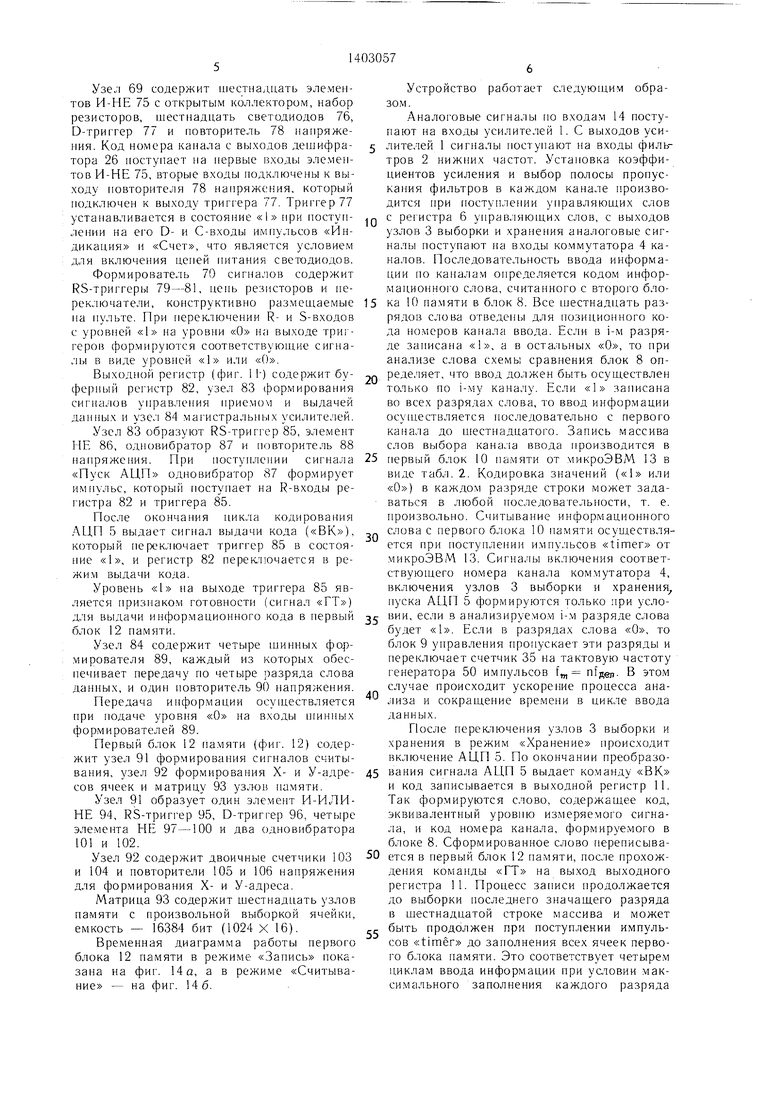

Блок 9 управления (фиг. 8) содержит элементы И-НЕ 40-42, элементы ИЛИ-НЕ 43- 45, элемент НЕ 46, триггеры 47-49, генератор 50 импульсов, делитель 51 частоты, вклю- чаюш,ий RC-триггер 52, элемент И-ИЛИ-НЕ 53, элементы НЕ 54-56 и регистр 57 сдвига, а также одновибратор 58 и регистр 59.

Временная диаграмма работы блока 9 управления показана на фиг. 13. Формирование им.пульсов при записи слова в режиме «Работа показано на фиг. 13 а. Начальное условие «Up равно «Ь, на входах регистра 59 - код информационного слова. При поступлении импульса «Уст. О или «Сброс на выходах триггера 47 устанавливается уровень «1, а на выходе триггера 48 - уровень «О, что соответствует режиму «Запись. На выходе триггера 49 сохраняется уровень «1. При поступлении импульса записи «К-ВК от микроЭВМ 13 триггер 49 переключается (передни.м фронтом) в состояние «О, что необходимо для режима записи информации в ячейки первого блока 10 памяти. В этот же момент времени управляю- шее слово записывается в регистр 59 и на его выходах образуется код управляющего слова. Задний фронт импульса «К-ВК переключает триггер 49 в режим «Хранение. Импульсы «Счет и «Ипдикация формируются при условии;

«Счет - «Ufa.6 Л timer Л «К-ВК, «Индикация «U pa A «К-ВК.

Формирование импульсов при считыва-. НИИ слова показано на фиг. 136. Начальное условие «Up «1. При поступлении сигнала «Уст. О или «Сброс на выходе триггера 47 устанавливается уровень «1, а на выходе триггера 48 - уровень «О. При поступлении импульса «timer на выходах триггеров 47 и 48 устанавливается уровень «1, а на выходе триггера 49 - уровень «О, что обеспечивает режим считывания слова с первого блока 10 памяти.

Задним фронтом импульса «timer триггер 49 переключается в режим «Хранение (уровень «1). Сигнал «Счет фор.мируется при условии «Счет «Upag A«timer /A «К-ВК.

Диаграмма работы делителя 51 частоты и одновибратора 58 приведена на

фиг. 130. Период следования тактовых импульсов определяется выбором пьезоэлемеп- та генератора 50 импульсов исходя из времени преобразования АЦП 5 таким обра- зом, чтобы обеспечить равенство

1 6 tnp. . ввода

./«

При появлении на выходе элемента И- НЕ 42 перепада с уровня «1 на уровень «О

,. триггер 52 переключается в состояние «О и на выходе элемента И-ИЛИ-НЕ 53 появляются импульсы „х с частотой, равной частоте делителя. В момент появления перепада с уровня «1 на уровень «О одновибратором 58 формируется команда «Пуск .ЛЦП.

5 Второй блок 10 памяти (фиг. 9) содержит узел 60 формирования Х-адреса, узел 61 формирования У-адреса, матрицу 62 узлов па.мяти, одновибратор 63.

Узлы 60 и 61 содержат соответственно

Q двоичные счетчики 64 и 65 группы повторителей 66 и 67 напряжений. Счетчики 64 и 65 устанавливаются в начальное положение сигналом «Уст. О. Запускаются счетчики импульсами «Счет, которые формируются в блоке 9 управления, после каждого иестнад5 цатого импульса одновибратор 63 формирует импульс «Сброс, который устанавливает счетчики в нуль и на их выходах формируется код первого адреса (0000). С приходом следующего импульса формируются адреса

0 следующей ячейки узлов памяти матрицы 62 (1000). Повторители усиливают сигналы по мощности. Выходы повторителей соединены с входами дешифраторов Х- и У-адресов узлов па.мяти, которые образуют 62 памяти, состоящую из шестнадцати узлов памя5 ти. Емкость - 256 бит (16 16-разрядных слов). Запись и считывание слов осуществляются при поступлении на управляющие входы (СЕ и WR) импульсов в соответствии с временными диаграммами, приведенными на фиг. 13 а, б.

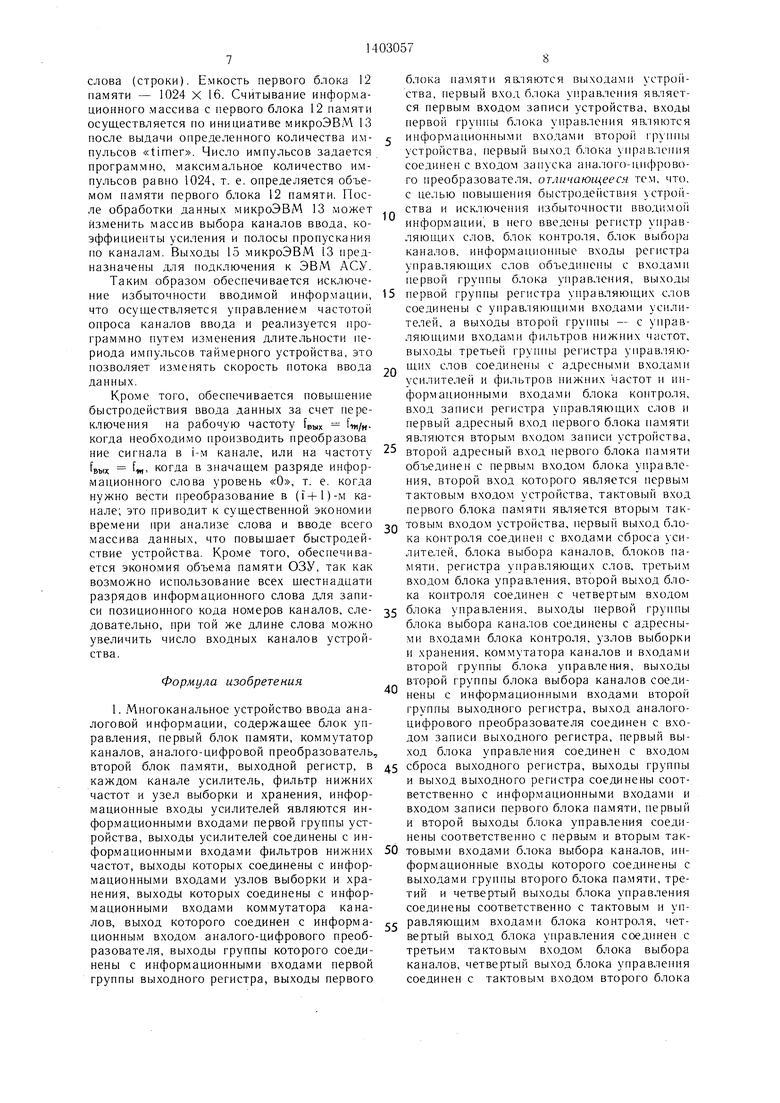

0 Блок 7 контроля (фиг. 10) содержит первый узел 68 индикации состояний i-й ячейки блока 10 памяти, второй узел 69 индикации номера усилителя и фильтра и формирователь 70 сигналов.

с Узел 68 образуют шестнадцать элементов И-НЕ 71 с открытым коллектором, набор резисторов, шестнадцать светодиодов 72, D-триггер 73 с установочными R- и S-входа- ми и повторитель 74 напряжения. Код управляющего слова (состояние i-й ячейки

0 блока памяти) поступает на первые входы эле.ментов И-НЕ 71 с выходов эле.ментов 36 сравнения. Вторые входы элементов под- к.тючены к выходу повторителя 74 напряжения, подключенного к выходу триггера 73. Триггер 73 устанавливается в нуль импульсом «Счет, а импульсом «Индикация переключается в состояние «1, что является условием для включения цепей питания светодиодов.

Узел 69 содержит шестнадцать элементов И-НЕ 75 с открытым коллектором, набор резисторов, шестнадцать светодиодов 76, D-триггер 77 и повторитель 78 напряжения. Код номера канала с выходов дешифратора 26 ностунает на первые входы элементов И-НЕ 75, вторые входы подключены к выходу повторителя 78 напряжения, который нодключен к выходу триггера 77. Триггер 77 устанавливается в состояние «I нри поступ- лепии на его D- и С-входы нмпульсов «Индикация и «Счет, что является условием для включения цепей питания светодиодов.

Формирователь 70 сигналов содержит Р5-три1теры 79-81, цень резисторов и це- реключатели, конструктивно размещаемые па пульте. При переключении R- и S-входов с уровней «1 на уровни «О на выходе триггеров формируются соответствуюп1,ие сигна- ;ibi в виде уровней «1 или «О.

Выходной регистр (фиг. 11-) содержит буферный регистр 82, узел 83 формирования сигналов управления ириемом и выдачей данных и узе.1 84 магистральных усилителей.

Узел 83 образуют RS-триггер 85, элемент НЕ 86, одновибратор 87 и повторитель 88 напряжения. Нри ноступлепии сигнала «Пуск АЦП одповибратор 87 формирует имнульс, который поступает на R-входы регистра 82 и триггера 85.

После окопчапия цикла кодирования АЦП 5 выдает сигнал выдачи кода («ВК), который переключает триггер 85 в состояние «1, и регистр 82 переключается в режим выдачи кода.

Уровень «1 на выходе триггера 85 является признако.м готовности (сигнал «ГТ) для выдачи информационного кода в первый блок 12 памяти.

Узел 84 содержит четыре шинных формирователя 89, каждый из которых обеспечивает передачу по четыре разряда слова данных, и один повторитель 90 напряжения.

Передача информации осуществляется при нодаче уровня «О па входы шинных формирователей 89.

Первый блок 12 памяти (фиг. 12) содержит узел 91 формирования сигналов считывания, узел 92 формирования Х- и У-адре- сов ячеек и матрицу 93 узлов на.мяти.

Узел 91 образует один элемент И-ИЛИ- НЕ 94, RS-триггер 95, D-триггер 96, четыре элемента НЕ 97-100 и два одновибратора 101 и 102.

Узел 92 содержит двоичные счетчики 103 и 104 и повторители 105 и 106 нанряжения для формирования Х- и У-адреса.

Матрица 93 содержит шестнадцать узлов памяти с произвольной выборкой ячейки, емкость - 16384 бит (1024 X 16).

Временная диаграмма работы первого блока 12 памяти в режиме «Запись показана на фиг. 14 а, а в режиме «Считывание - на фиг. 146.

0

5

0

5

0

5

0

5

0

5

Устройство работает следующим образом.

Аналоговые сигналы по входам 14 поступают на входы усилителей 1. С выходов усилителей 1 сигналы поступают на входы фильтров 2 нижних частот. Установка коэффициентов усиления и выбор полосы пропускания фильтров в каждом канале нроизво- дится нри поступлении управляющих слов с ре1истра 6 унрав.ляющих слов, е выходов узлов 3 выборки и хранения аналоговые сигналы поступают па входы коммутатора 4 каналов. Последовательность ввода информации по каналам определяется кодом информационного слова, считанного с второго блока 10 памяти в блок 8. Все шестнадцать разрядов слова отведены для позиционного кода номеров канала ввода. Если в i-м разряде записана «1, а в остальных «О, то при анализе слова схемы сравпения блок 8 определяет, что ввод должен быть осуществлен только по i-му каналу. Если «1 записана во всех разрядах слова, то ввод информации оеу цествляется последовательно с первого канала до шестнадцатого. Запись .массива слов выбора кана.:1а ввода производится в первый блок 10 па.мяти от микроЭВМ 13 в виде табл. 2. Кодировка значений («1 или «О) в каждом разряде строки может задаваться в любой последовательности, т. е. нроизвольно. Считывание информационного слова с первого блока 10 памяти осуществляется при поступлении импу.льсов «timer от микроэвм 13. Сигналы включения соответствующего fiOMepa канала коммутатора 4, включения узлов 3 выборки и хранения, нуска АЦП 5 формируются только при условии, если в анализируемом i-м разряде слова будет «1. Если в разрядах слова «О, то блок 9 управления пропускает эти разряды и переключает счетчик 35 на тактовую частоту генератора 50 импульсов f В этом случае происходит ускорение процесса анализа и сокращение вре.мени в цикле ввода данных.

После перек тючения узлов 3 выборки и хранения в режим «Хранение происходит включение АЦП 5. По окончании преобразования сигнала АЦП 5 выдает команду «ВК и код записывается в выходной регистр 11. Так формируются слово, содержащее код, эквивалентный уровню измеряемого сигнала, и код номера канала, формируемого в блоке 8. Сформированное слово переписывается в первый блок 12 памяти, после прохождения команды «ГТ на выход выходного регистра 11. Процеес засшси продолжается до выборки последнего значащего разряда в шестнадцатой строке массива и может быть продолжен при поступлении импульсов «timer до заполнения всех ячеек первого блока намяти. Это соответствует четыре.м циклам ввода информации при условии максимального заполнения каждого разряда

слова (строки). Емкость первого блока 12 памяти - 1024 X 16. Считывание информационного массива с первого блока 12 памяти осуществляется по инициативе микроЭВМ 13 после выдачи определенного количества им- пульсов «timer. Число импульсов задается программно, максимальное количество импульсов равно 1024, т. е. определяется объемом памяти первого блока 12 памяти. После обработки данны.х микроЭВМ 13 может изменить массив выбора каналов ввода, коэффициенты усиления и полосы пропускания по каналам. Выходы 15 микроЭВМ 13 предназначены для подключения к ЭВМ АСУ.

Таким образом обеспечивается исключение избыточности вводимой информации, что осуществляется управлением частотой опроса каналов ввода и реализуется программно путем изменения длительности периода импульсов таймерного устройства, это позволяет изменять скорость потока ввода данных.

Кроме того, обеспечивается повышение быстродействия ввода данных за счет переключения на рабочую частоту fpy , когда необходимо производить преобразова ние сигнала в i-м канале, или на частоту fbwx f. когда в значащем разряде информационного слова уровень «О, т. е. когда нужно вести преобразование в (1 + 1)-м канале; это приводит к существенной экономии времени при анализе слова и вводе всего массива данных, что повыщает быстродействие устройства. Кроме того, обеспечивается экономия объема памяти ОЗУ, так как возможно использование всех щестнадцати разрядов информационного слова для записи позиционного кода номеров каналов, еле- довательно, при той же длине слова можно увеличить число входных каналов устройства.

Формула изобретения

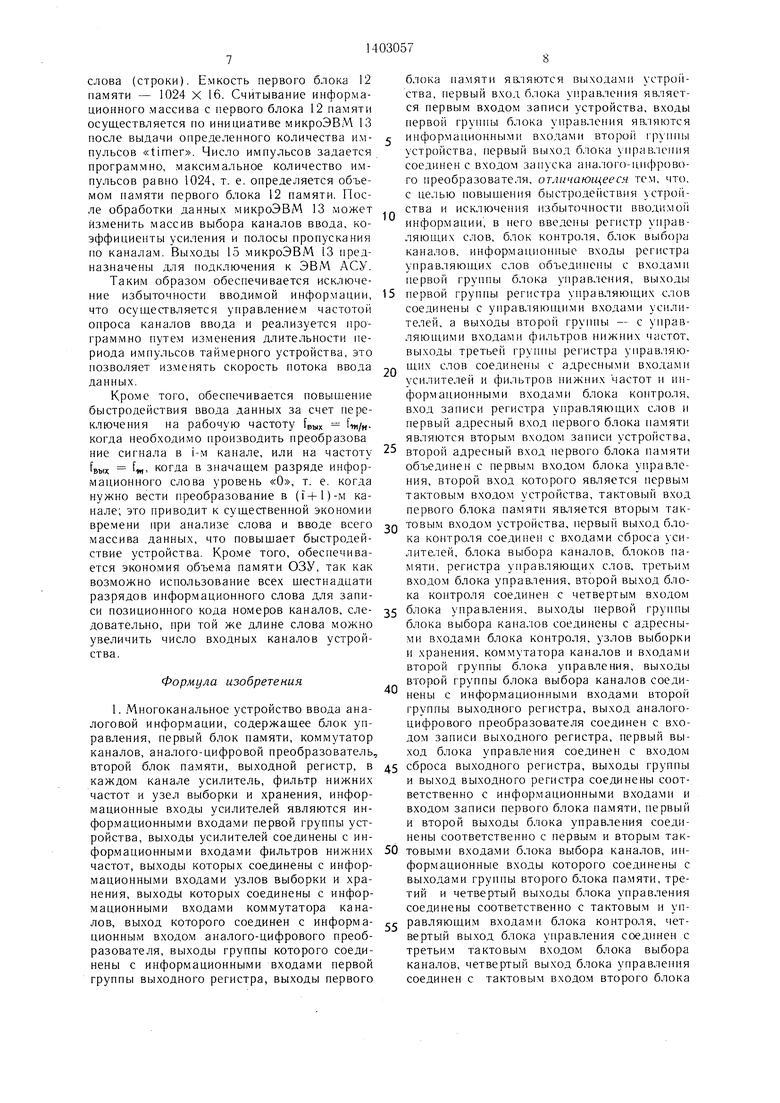

1. Многоканальное устройство ввода аналоговой информации, содержащее блок управления, первый блок памяти, коммутатор каналов, аналого-цифровой преобразователь второй блок памяти, выходной регистр, в каждом канале усилитель, фильтр нижних частот и узел выборки и хранения, информационные входы усилителей являются информационными входами первой группы устройства, выходы усилителей соединены с информационными входами фильтров нижних частот, выходы которых соединены с информационными входами узлов выборки и хранения, выходы которых соединены с информационными входами коммутатора каналов, выход которого соединен с информа- ционным входом аналого-цифрового преобразователя, выходы группы которого соединены с информационными входами первой группы выходного регистра, выходы первого

5 п

5 п 5

0

5 0 е

блока памяти яаляются выходами устройства, первый вход блока управлепия является первым входом записи устройства, входы первой rpyinibi блока управления являются информационными входами BTopoii группы устройства, первый выход блока управ.чеппя соединен с входом запуска аналого-цифрового преобразователя, отличающееся тем, что, с целью повышения быстродействия устройства и исключения избыточности вводп.мой информации, в него введены регистр управляющих слов, блок контроля, блок выбора каналов, информационные входы регистра управляюца,их слов объедппены с входамп первой группы блока управления, выходы первой группы регистра управляющих слов соединены с управляющими входами усилителей, а выходы второй rpyinibi - с управляющими входами фильтров нижних частот, выходы третьей rpyrnibi регистра управляющих слов соединены с адресными входами усилителей и фильтров 1тжних частот п информационными входами блока контроля, вход записи регистра управляющих слов п первый адресный вход первого блока памяти являются вторым входом записи устройства, второй адресный вход первого блока памяти объедипен с первым входом блока управления, второй вход которого является первым тактовым входо.м устройства, тактовый вход первого блока памяти является вторым тактовым входо.м устройства, первый выход б,1о- ка контроля соединен с входами сброса усилителей, блока выбора каналов, блоков памяти, регистра управляющих слов, третьим входом блока управления, второй выход блока контроля соединен с четвертым входом блока управления, выходы первой группы блока выбора каналов соединены с адресными входами блока контроля, узлов выборки и хранения, коммутатора каналов и входами второй группы блока управления, выходы второй группы блока выбора каналов соединены с информационными входами второй группы выходного регистра, выход аналого- цифрового преобразователя соединен с входом записи выходного регистра, первый выход блока управления соединен с входом сброса выходного регистра, выходы группы и выход выходного регистра соединены соответственно с информационными входа.ми и входом записи первого блока памяти, первый и второй выходы блока управления соединены соответственно с первым и вторым так- товы.ми входа.ми блока выбора каналов, информационные входы которого соединены с выходами группы второго блока па.мяти, третий и четвертый выходы блока управления соединены соответственно с тактовы.м и управляющим входами блока контроля, четвертый вы.ход блока управления соединен с третьим тактовым входом блока выбора каналов, четвертый выход блока управлепия соедипен с тактовым входом второго блока

памяти, информационные входы которого соединены с выходами группы блока управления, пятый и шестой выходы блока управления подключены к входам записи и выборки второго блока памяти соответственно, выход второго блока памяти соединен с пятым входом блока управления.

2. Устройство по п. 1, отличающееся тем, что блок управления содержит генератор импульсов, делитель частоты, одновибратор, регистр, три триггера, три элемента ИЛИ- НЕ, три элемента И-НЕ, элемент НЕ, информационные входы регистра являются входами первой группы блока, выходы регистра являются выходами группы блока, вход

рой узлы индикации, формирователь сигналов, выходы которого являются первым и вторым выходами блока, информационные входы первого узла индикации являются адресными входами блока, информационные входы второго узла индикации являются информационными входами блока, тактовые входы узлов индикации являются тактовым входом блока, вход сброса первого узла индикации и установочный вход второго узла индикации являются управляющим входом блока, вход формирователя сигналов и установочный вход первого узла индикации подключены к выходу первого узла индикации. 4. Устройство по п. 1, отличающееся тем.

сброса регистра и первый вход первого эле- 15 что блок выбора каналов содержит первый

мента ИЛИ-НЕ являются третьим входом блока, второй вход первого элемента ИЛИ- НЕ является пятым входом блока, выход первого элемента ИЛИ-НЕ соединен с установочным входом первого триггера и входом сброса второго триггера, выход которого является пятым выходом блока, первый вход первого элемента И-НЕ и тактовый вход регистра являются первым входом блока, выход первого эле.мепта И-НЕ соединен с

20

и второй регистры, счетчик, элементы сравнения, одновибратор, дешифратор, выходы первого регистра соединены с соответствующими входами первой группы элементов сравнения, выходы которых являются выходами первой группы блока, выходы второго регистра являются выходами второй группы блока, информационные входы первого регистра являются информационными входами блока, счетнь й вход счетчика является втопервым входом второго элемента ИЛИ-НЕ, 25 рым тактовы.м входом блока, выходы счетвыход которого соединен с входом эле.мен- та НЕ, первым входом третьего элемента ИЛИ-НЕ и является четверты.м выходом блока, выходы третьего элемента ИЛИ-НЕ и элемента НЕ соединены соответственно с входами сброса и установочным третьего триггера, выход которого является шестым выходом блока, второй вход первого элемента И-НЕ, второй вход третьего элемента ИЛИ-НЕ и первый вход второго элемента

чика соединены с информационными входами второго регистра и лтешифратора, выходы которого соединены с соответствующими входами второй группы элементов сравнения, oQ стробирующие входы дешифратора и второго регистра являются первым тактовым входом блока, вход сброса первого регистра и первый вход сброса счетчика являются входом сброса блока, стробируюший вход первого регистра является третьим тактовым

торого соединен счетчика.

с вторым входом сброса Таблица 1

40

И-НЕ являются четвертым входом блока, 35 входом блока, один из выходов дешифратора второй вход второго элемента И-НЕ являет- соединен с входом одновибратора, выход кося вторым входо.м блока, выход второго элемента И-НЕ соединен с входом сброса первого триггера, вторым входом второго элемента ИЛИ-НЕ и является третьим выходом блока, выход первого триггера соединен с установочным входом второго триггера, входы третьего элемента И-НЕ являются входами второй группы устройства, выход третьего элемента И-НЕ соединен с входом одновибратора и перв1з1м входом делителя частоты, второй вход которого соединен с выходом генератора импульсов, выход делителя частоты является вторым выходом блока, выход одновибратора является первым выходом блока.

3. Устройство по п. 1, отличающееся тем, 50 что блок контроля содержит первый и вто45

рой узлы индикации, формирователь сигналов, выходы которого являются первым и вторым выходами блока, информационные входы первого узла индикации являются адресными входами блока, информационные входы второго узла индикации являются информационными входами блока, тактовые входы узлов индикации являются тактовым входом блока, вход сброса первого узла индикации и установочный вход второго узла индикации являются управляющим входом блока, вход формирователя сигналов и установочный вход первого узла индикации подключены к выходу первого узла индикации. 4. Устройство по п. 1, отличающееся тем.

0

и второй регистры, счетчик, элементы сравнения, одновибратор, дешифратор, выходы первого регистра соединены с соответствующими входами первой группы элементов сравнения, выходы которых являются выходами первой группы блока, выходы второго регистра являются выходами второй группы блока, информационные входы первого регистра являются информационными входами блока, счетнь й вход счетчика является вточика соединены с информационными входами второго регистра и лтешифратора, выходы которого соединены с соответствующими входами второй группы элементов сравнения, стробирующие входы дешифратора и второго регистра являются первым тактовым входом блока, вход сброса первого регистра и первый вход сброса счетчика являются входом сброса блока, стробируюший вход первого регистра является третьим тактовым

торого соединен счетчика.

с вторым входом сброса Таблица 1

входом блока, один из выходов дешифратора соединен с входом одновибратора, выход кофиг. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО РЕГИСТРАЦИИ СТАТИЧЕСКИХ ТЕЛЕВИЗИОННЫХ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2054818C1 |

| Распределитель импульсов | 1988 |

|

SU1511747A1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Устройство для синхронизации распределенной вычислительной системы | 1988 |

|

SU1508201A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1987 |

|

SU1439609A1 |

Изобретение относится к области вычислительной техники и может быть исноль- зовано в автоматизированных системах управления для сбора аналоговой информации с датчиков объекта и ввода ее в ЭВМ. Целью изобретения является повышение быстродействия устройства и исключение избыточности вводимой информации. Устройство содержит блок 1 усилителей, блок 2 фильтров нижних частот, блок 3 выборки и хранения, коммутатор каналов 4, аналого-цифровой преобразователь 5, регистр управляющих слов 6, блок 7 контроля, блок 8 выбора каналов, блок 9 управления, блоки памяти 10 и 12, выходной регистр 11. За счет управления частотой опроса каналов ввода с помощью таймерного устройства появляется возможность изменять скорость потока данных. Переключение на рабочую частоту при необходимости преобразования сигнала в i-M канале приводит к существенной экономии времени при анализе слова и вводе всего массива данных, что позволяет повысить быстродействие устройства. Кроме того, за счет использования всех разрядов информационного слова для записи номеров каналов можно увеличить число входных каналов устройства и создается экономия объема памяти. 3 3. п. ф-лы, 14 ил., 2 табл. i (Л

.16г

фиг. 6

о Ufgb/x.

U/6ffi,/

11

1403057

12 Таблица 2

XI Х2 о

Xfffo

(7о

ii/Лг. /о

16УФ1

rsfyo

о fgf/x.

f68blX

G/SM.

/Лил

Фиг 7

if те Г Р/16

Н вИ CBjyocQ

Уст. О, /л№н/р о

Гбр р,

us.g

о ЗП-СЧ

.

oJSb/K.

/7угЛ ЦП

иг.9

/

f6ycfi

фцг. fO

с/ О

РАБ

в ffue. 11

vS

1

Mil

i§

|ЕИ

N

i

Vj Sv, v,

А А А А А А

4 11§

с . v5 . . ;3

ST

J Чо -- V +vl

-

-

Svj -vi

t:2

i

| Устройство для ввода информации в эвм | 1977 |

|

SU737943A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гриценко В | |||

| И | |||

| и др | |||

| Программируемый контроллер многоканальных АЦП в системах с распределенной структурой обработки данных | |||

| - Управляющие системы и машины, 1984, № 1, с | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-15—Публикация

1986-02-11—Подача