Изобретение относится к вычислительной и информационно-измерительной технике и может быть использовано в автоматизированных системах регистрации быстропротекающих процессов.

Целью предлагаемого изобретения является расширение функциональных возможностей, уменьшение динамической погрешности, повышение быстродействия и надежности при регистрации аналоговых сигналов.

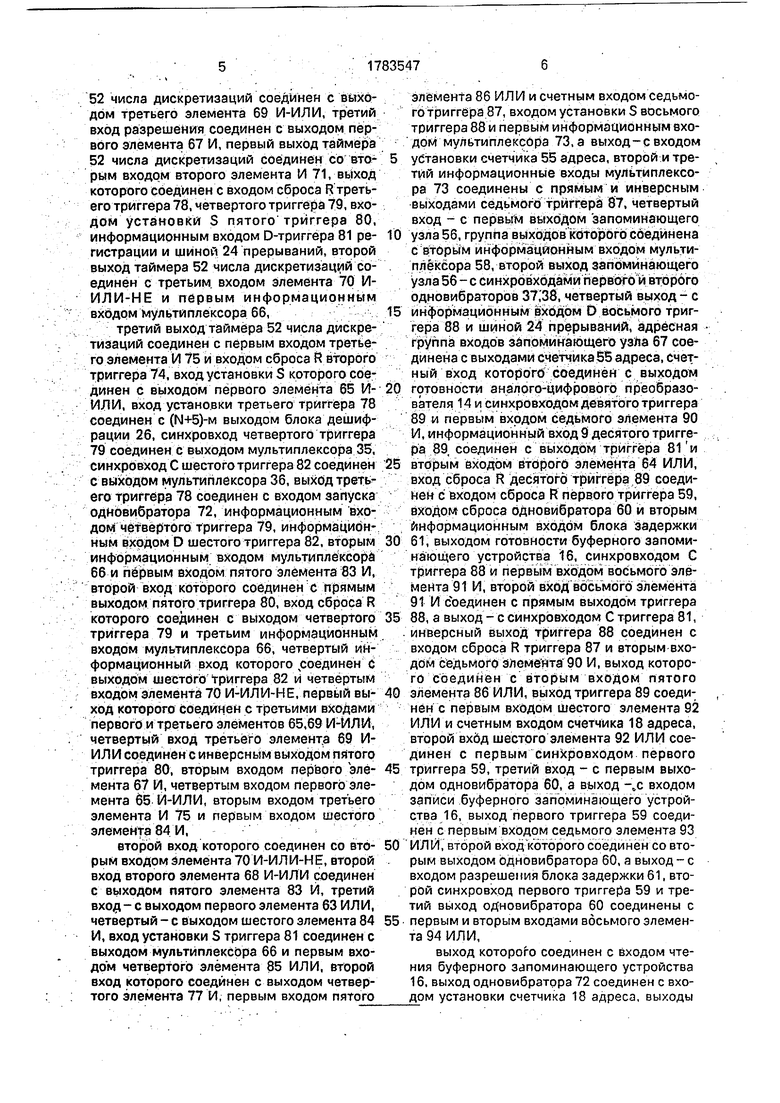

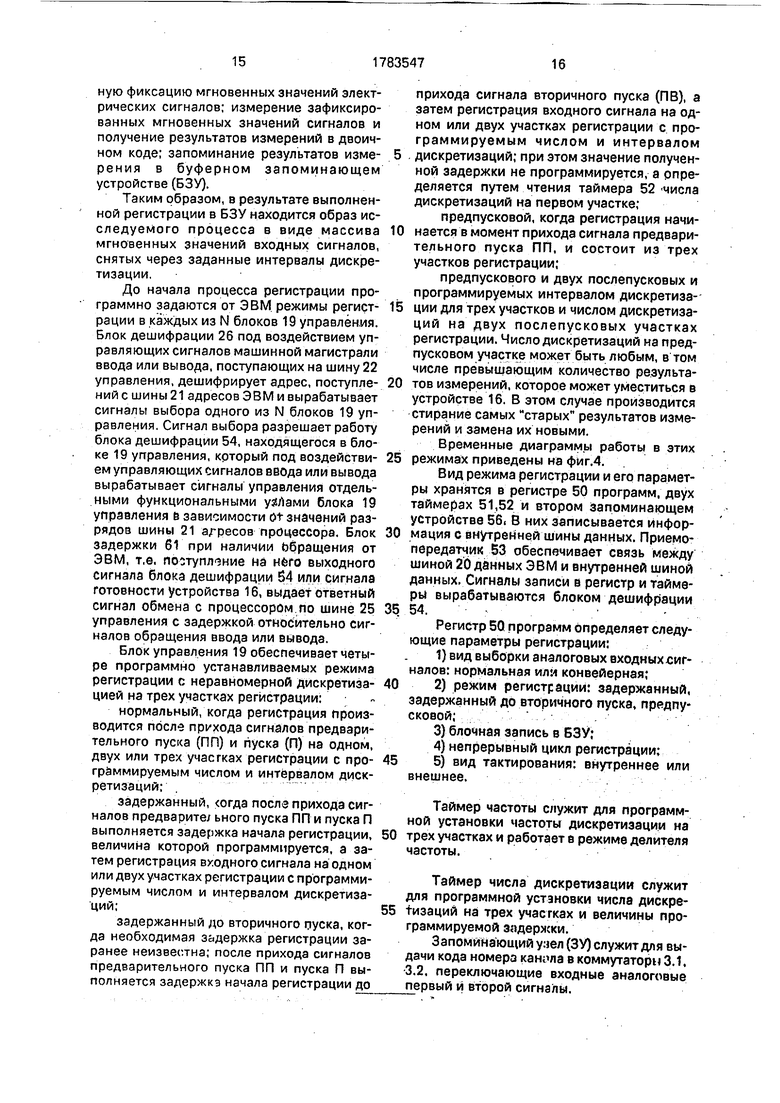

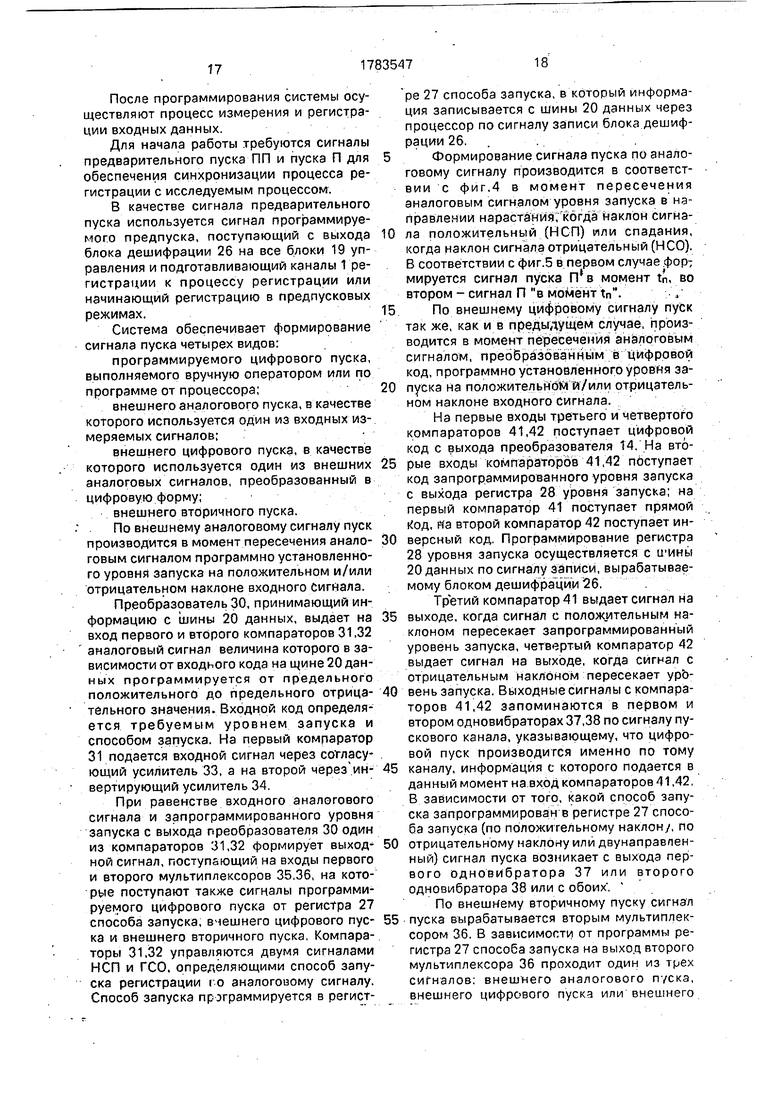

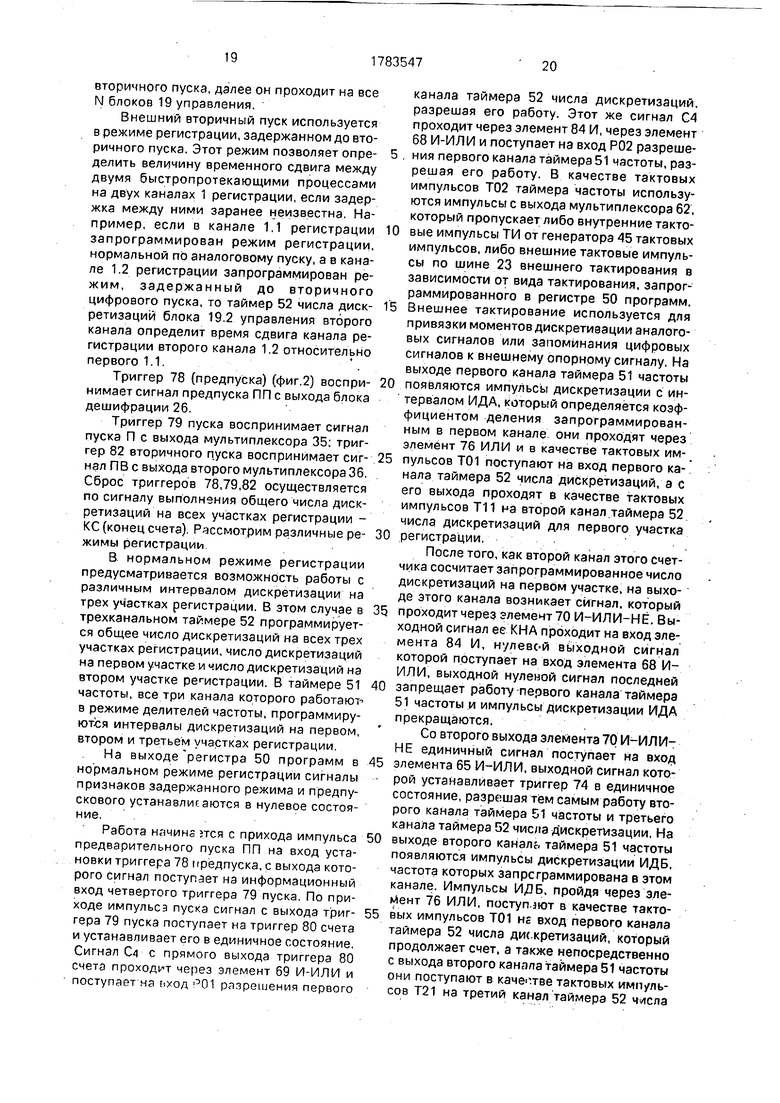

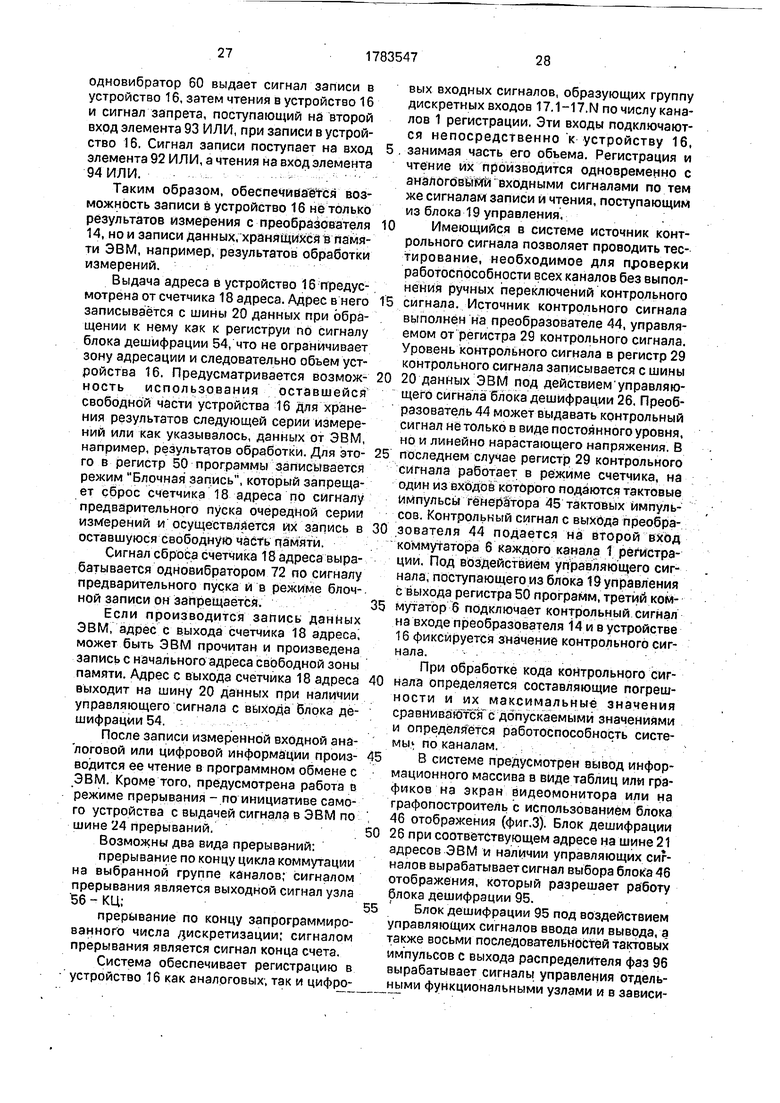

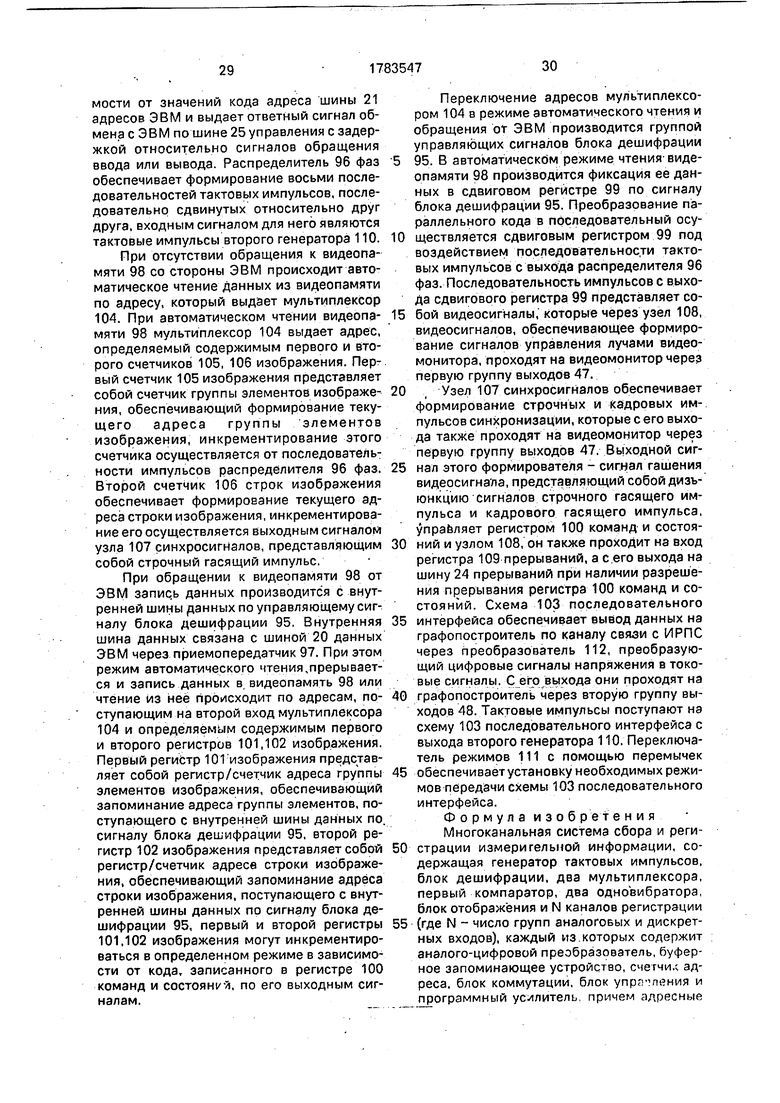

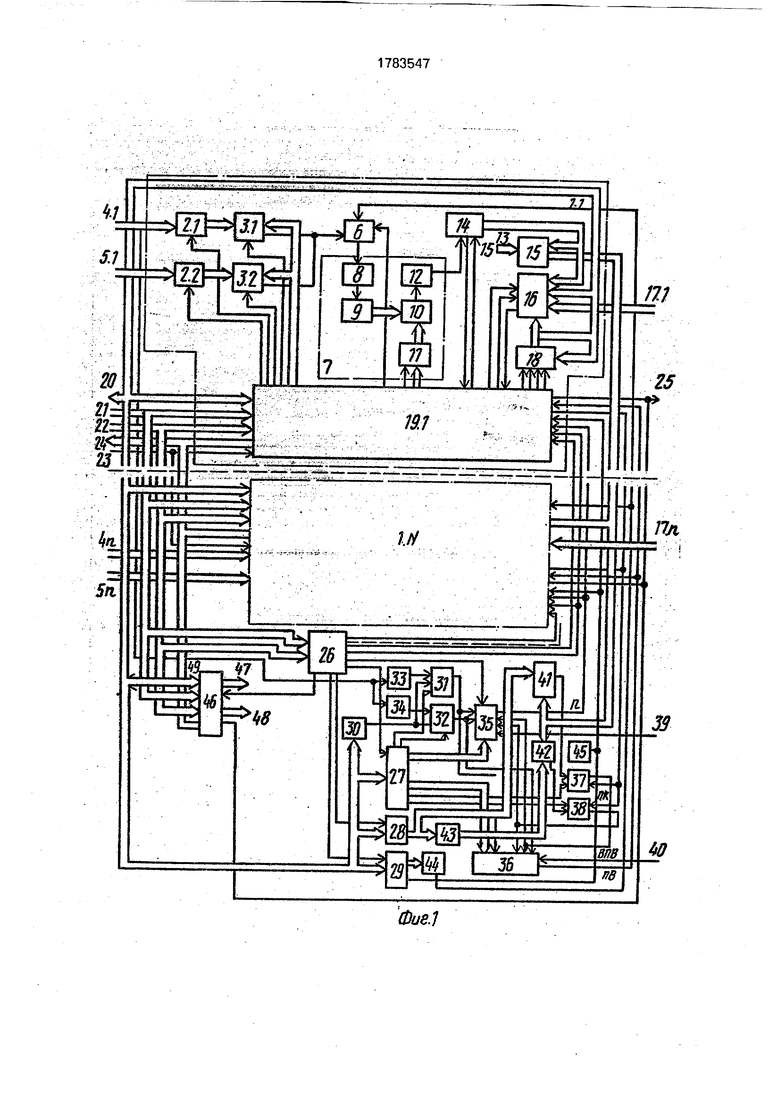

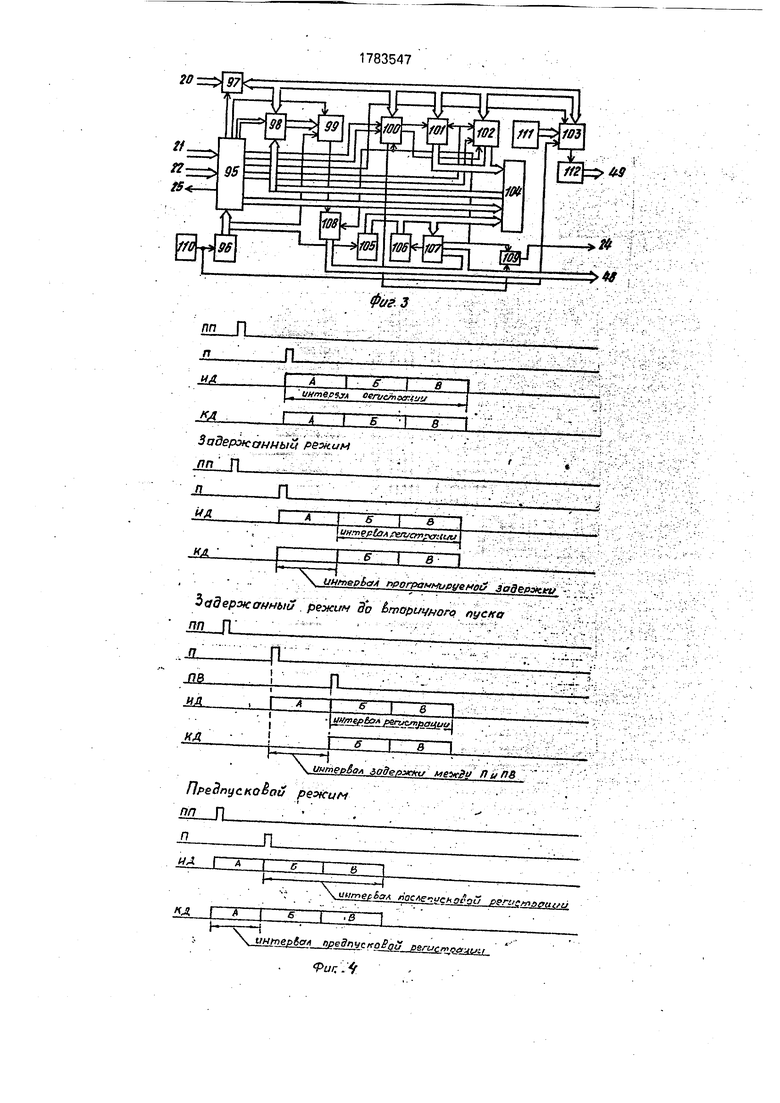

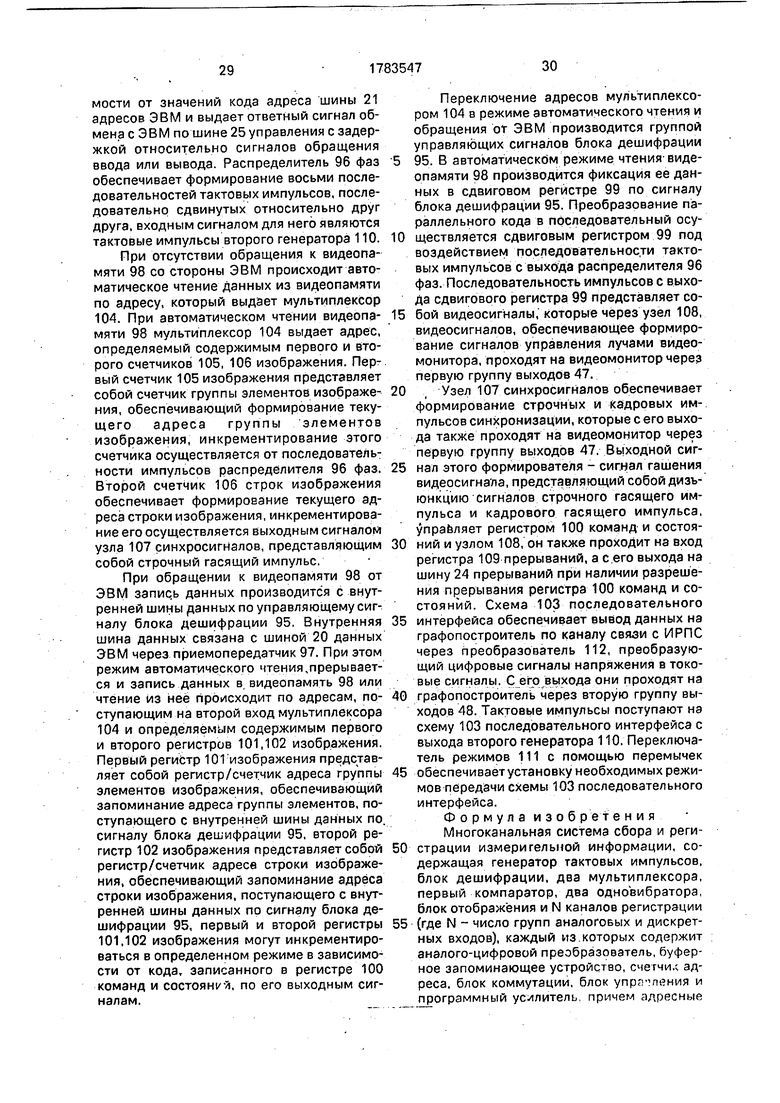

На фиг.1 представлена блок-схема предлагаемой системы; на фиг,2 - функциональная схема блока управления: на фиг.З - функциональная схема блока отображения;

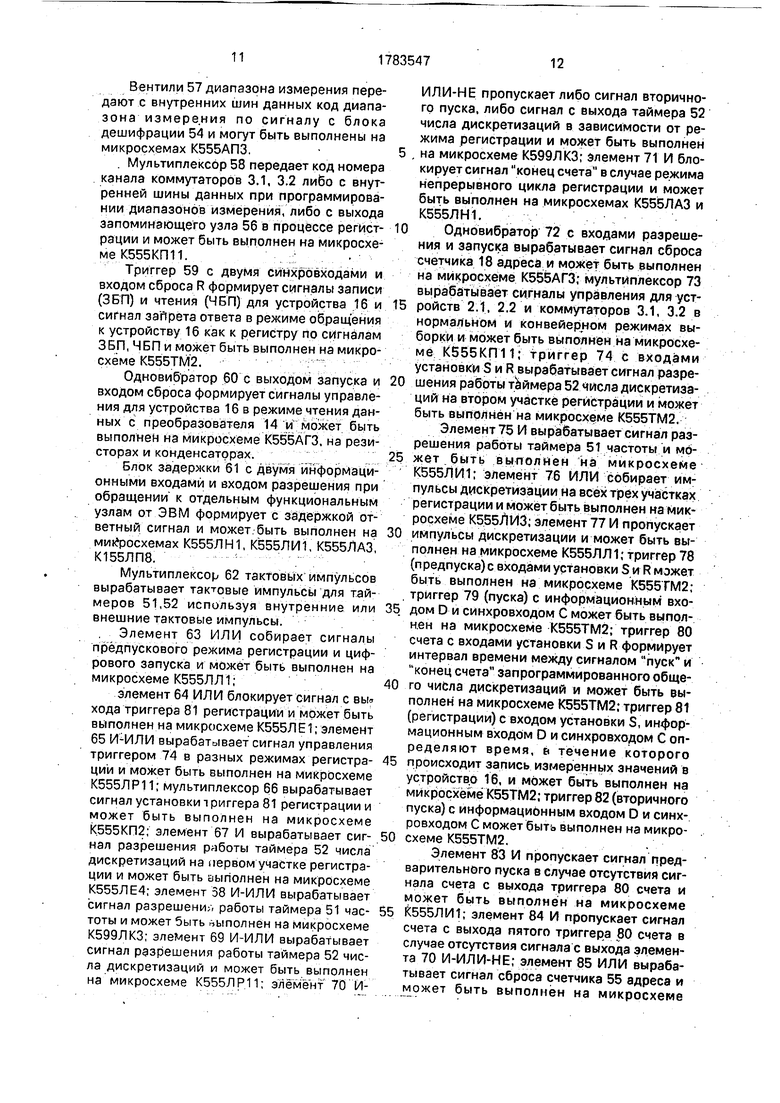

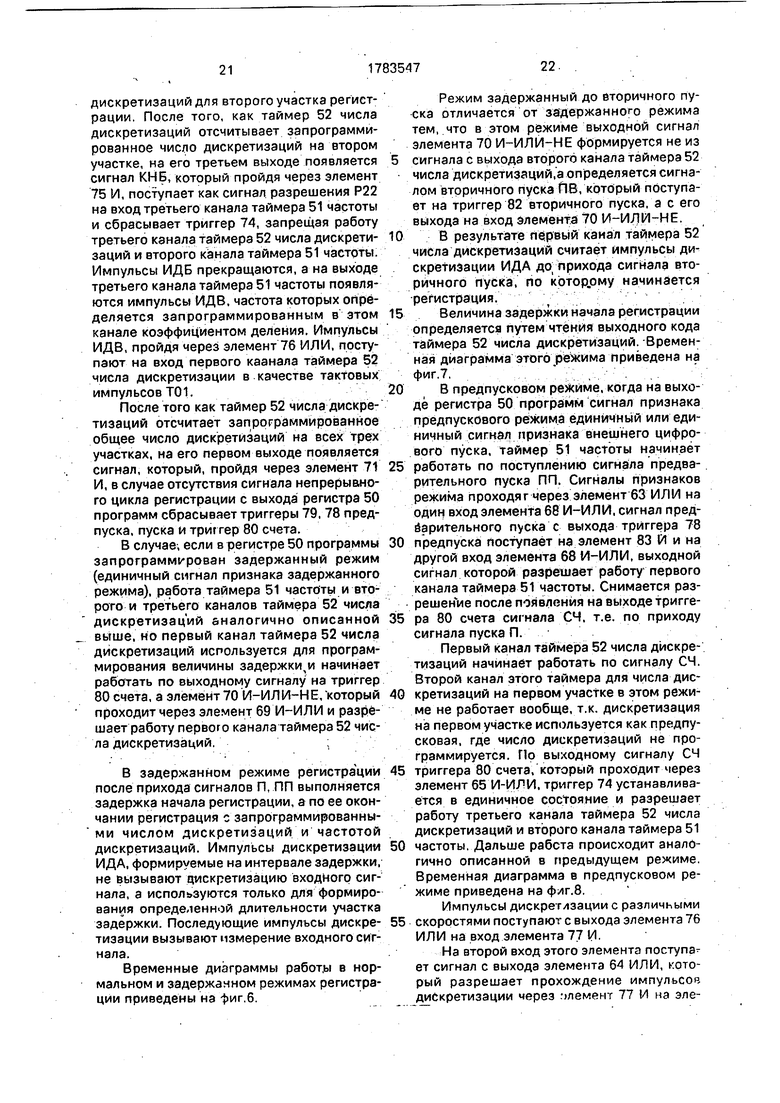

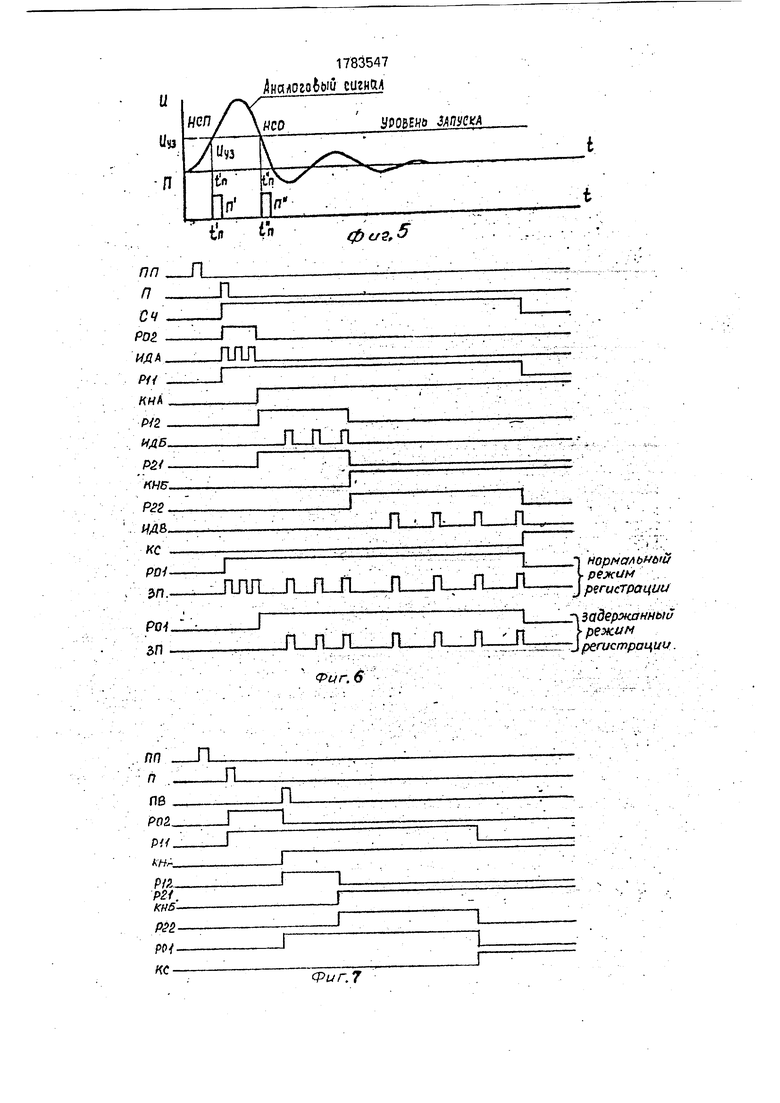

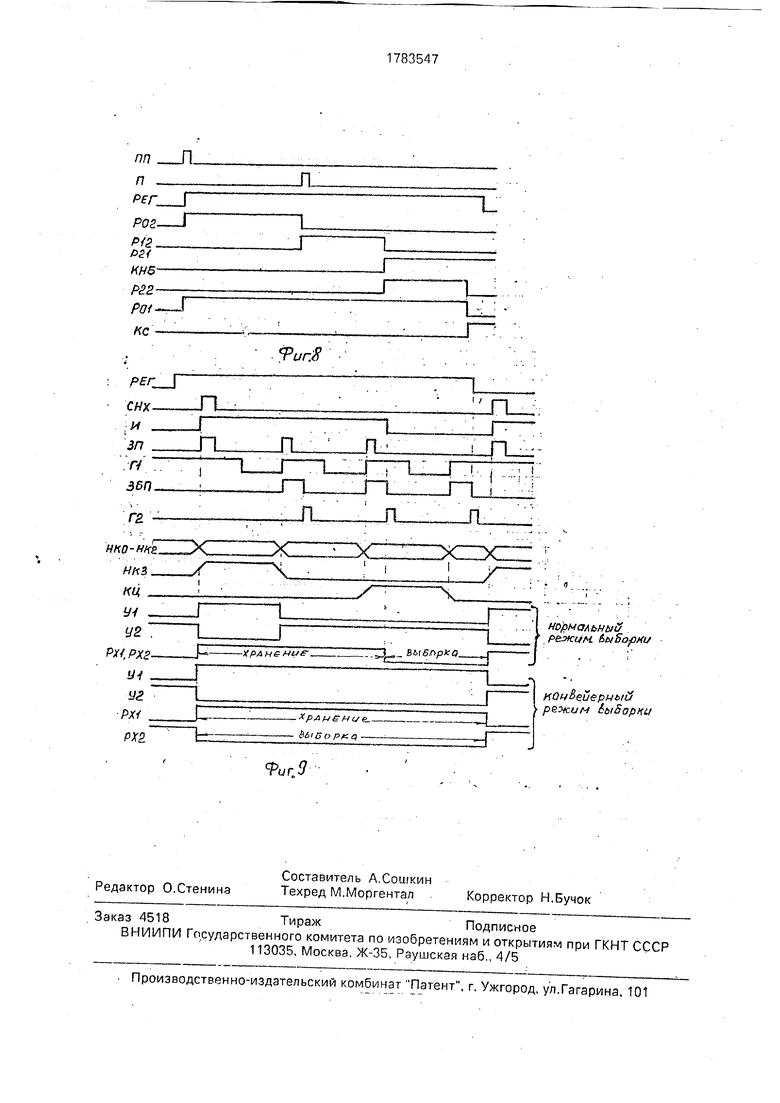

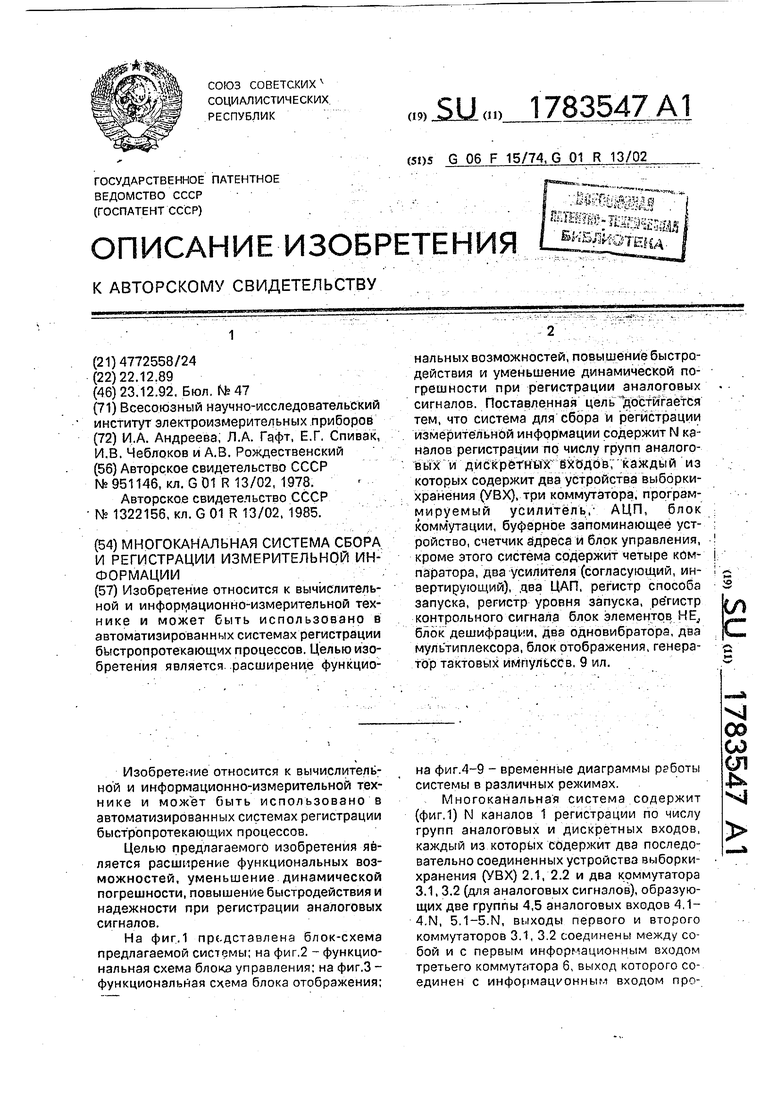

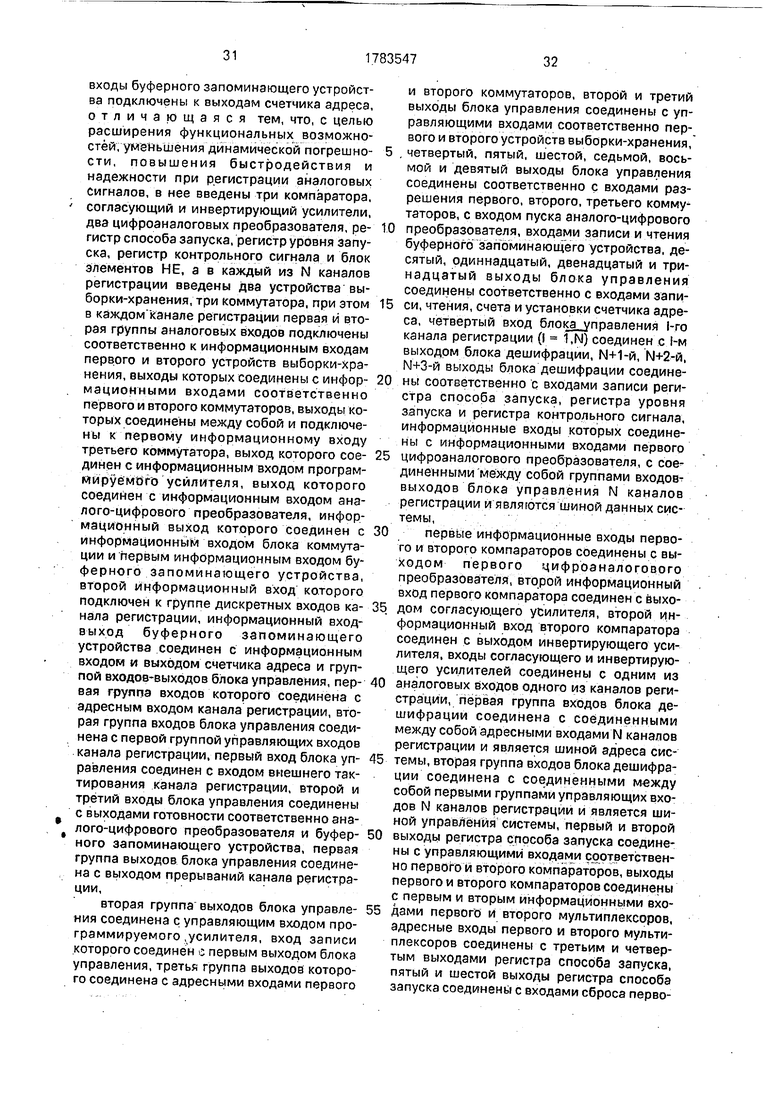

на фиг.4-9 - временные диаграммы реботы системы в различных режимах.

Многоканальная система содержит (фиг.1) N каналов 1 регистрации по числу групп аналоговых и дискретных входов, каждый из которых содержит два последовательно соединенных устройства выборки- хранения (УВХ) 2.1, 2.2 и два коммутатора 3.1, 3.2 (для аналоговых сигналов), образующих две группы 4,5 аналоговых входов 4.1- 4.N, 5.1-5.N, выходы первого и второго коммутаторов 3.1, 3.2 соединены между собой и с первым информационным входом третьего коммутгпчэра б, выход которого соединен с информационным входом

00

00

ел

4

J

граммируемого усилителя 7, содержащего усилитель 8, делитель сопротивлений 9, коммутатор 10, регистр диапазона 11 и буферный усилитель 12, вторую группу 13 управляющих входов, аналого-цифровой преобразователь (АЦП) 14, блок 15 коммутации, буферное запоминающее устройство 16, группы 17.1-17.N дискретных входов, счетчик 18 адреса, блок 19 управления, шину 20 данных, шину 21 адреса, шину 22 управления, вход 23 внешнего тактирования, шину 24 прерываний, управляющий выход 25, блок 26 дешифрации, регистр 27 способа запуска, регистр 28 уровня запуска, регистр 29 контрольного сигнала, цифро-аналоговый преобразователь (ЦАП) 30, компараторы 31,32, согласующий 33 и инвертирующий 34 усилители, мультиплексоры 35,36, одно- вибраторы 37,38, вход 29 внешнего пуска, вход 40 внешнего вторичного пуска, компараторы 41,42,

блок 43 элементов НЕ, цифроаналого- вый преобразователь 44, генератор 45 тактовых импульсов, блок 46 отображения, выход 47 для подключения к видеомонитору, выход 48 для подключения к графопостроителю, .группа 49 информационных входов-выходов блока отображения.

Блок 19 управления (фиг.2) содержит регистр 50 программ, таймер 51 частоты и таймер 52 числа дискретизаций, информационные входы которых соединены с первыми информационными входами-выходами приемопередатчика 53, вторые информационные входы-выходы которого соединены с шиной 20 данных, вход записи регистра 50 программ, таймера 51 частоты и таймера 52 числа дискретизаций соединены с первым и вторым выходами блока дешифрации 54; выходы чтения таймера 51 частоты и таймера 52 числа дискретизаций соединены с третьим выходом второго блока дешифрации 54, первая группа входов которого соединена с шиной 21 адресов и группой информационных входов счетчика 55 адреса, группа входов разрешения блока дешифрации 54 соединена с шиной 22 управлений, вход разрешения - с одним из выходов первого блока дешифрации 26, чет- верый выход блока дешифрации 54 соединен свходом управления приемопередатчика 53, пятый выход с входами записи счетчика 55 адреса, запоминающего узла 56, входами управления вентилей 57 и мультиплексора 58 и входом записи программируемого усилителя 7, шестой и седьмой выходы - с первым и вторым синхровходами первого триггера 59, восьмой выход - с входом запуска одновибрато- ра 60, девятый и десятый выходы - с

входами записи и чтения счетчика 18 адреса, одиннадцатый выход - с первым информационным входом блока задержки 61, выход которого соединен с шиной 25

управлений, информационные входы запоминающего узла 56, вентилей 57 и мультиплексора 58 соединены с информационными ЁХОДЭМИ таймера 51 частоты, первый выход регистра 50 программ соединен с

0 входом управления мультиплексора 62, первый информационный вход которого соединен с входом 23 внешнего тактирования, а второй информационный вход - с выходом генератора 45 тактовых импульсов, второй

5 выход регистра 50 программ с первыми входами первого и второго элементов ИЛИ 63,64, третий выход - с первым входом первого элемента И-ИЛИ 65, вторым входом первого элемента ИЛИ 63 и первым управ0 ляющим входом мультиплексора 66, четвертый выход - со вторым входом первого элемента И-ИЛИ 65, первым входом первого элемента И 67 и первым входом второго элемента И-ИЛИ 68, пятый выход - с пер5 вым входом третьего элемента И-ИЛИ 69, шестой выход - с вторым входом третьего элемента И-ИЛИ 69 и вторым управляющим входом мультиплексора 66, седьмой выход - с первым входом элемента 70 И-ИЛИ-НЕ и

0 третьим управляющим входом мультиплексора 66, восьмой выход - со вторым входом элемента 70 И-ИЛИ-НЕ, девятый выход - с первым входом второго элемента И 71, десятый выход - с- входом разрешения Ъдно5 вибратора 72, одиннадцатый выход - с управляющим входом мультиплексора 73, двенадцатый выход - с входом разрешения коммутатора 6, выход четвертого мультиплексора 62 соединен с тремя тактовыми

0 входами таймера 51 частоты, первый вход разрешения которого соединен с выходом второго элемента 68 И-ИЛИ, второй вход разрешения - с выходом второго триггера 74 и первым входом разрешения таймера 52

5 числа дискретизаций, третий вход разрешения - соединен с выходом третьего элемента 75 И, первый выход таймера 51 частоты соединен с первым входом третьего элемента 76 ИЛИ и первым тактовым входом тай0 мера 52 числа дискретизаций, второй выход - со вторым вводом третьего элемента 76 ИЛИ и вторым тактовым входом таймера 52 числа дискретизаций, третий выход - с третьим входом третьего элемента 76

5 ИЛИ, выход которого соединен с третьим тактовым входом таймера 52 числа дискретизаций и первым входом четвертого элемента И 77, второй вход которого соединен с выходом второго элемента ИЛИ 64, второй вход разрешения таймера

52 числа дискретизаций соединен с выходом третьего элемента 69 И-ИЛИ, третий вход разрешения соединен с выходом первого элемента 67 И, первый выход таймера 52 числа дискретизаций соединен со вто- рым входом второго элемента И 71, выход которого соединен с входом сброса R третьего триггера 78, четвертого триггера 79, входом установки S пятого триггера 80, информационным входом D-триггера 81 ре- гистрации и шиной 24 прерываний, второй выход таймера 52 числа дискретизаций соединен с третьим входом элемента 70 И- ИЛИ-НЕ и первым информационным входом мультиплексора 66,

третий выход таймера 52 числа дискре- тизаций соединен с первым входом третьего элемента И 75 и входом сброса R второго триггера 74, вход установки S которого соединен с выходом первого элемента 65 И- ИЛИ, вход установки третьего триггера 78 соединен с (М+5)-м выходом блока дешифрации 26, синхровход четвертого триггера 79 соединен с выходом мультиплексора 35, синхровход С шестого триггера 82 соединен с выходом мультиплексора 36, выход третьего триггера 78 соединен с входом запуска одновибратора 72, информационным входом четвертого триггера 79, информационным входом D шестого триггера 82, вторым информационным входом мультиплексора 66 и первым входом пятого элемента 83 И, второй вход которого соединен с прямым выходом пятого триггера 80, вход сброса R которого соединен с выходом четвертого триггера 79 и третьим информационным входом мультиплексора 66, четвертый информационный вход которого соединен с выходом шестого триггера 82 и четвертым входом элемента 70 И-ИЛИ-НЕ, первый вы- ход которого соединен с третьими входами первого и третьего элементов 65,69 И-ЙЛИ, четвертый вход третьего элемента 69 И- ИЛИ соединен с инверсным выходом пятого триггера 80, вторым входом пер вого эле- мента 67 И, четвертым входом первого элемента 65 И-ИЛИ, вторым входом третьего элемента И 75 и первым входом шестого элемента 84 И,

второй вход которого соединен со вто- рым входом Элемента 70 И-ИЛИ-НЕ, второй вход второго элемента 68 И-ИЛИ соединен с выходом пятого элемента 83 И, третий вход - с выходом первого элемента 63 ИЛИ, четвертый - с выходом шестого элемента 84 И, вход установки S триггера 81 соединен с выходом мультиплексора 66 и первым входом четвертого элемента 85 ИЛИ, второй вход которого соединен с выходом четвертого элемента 77 И, первым входом пятого

элемента 86 ИЛИ и счетным входом седьмого триггера 87, входом установки S восьмого триггера 88 и первым информационным входом мультиплексора 73,а выход-свходом убтановки счетчика 55 адреса, второй и третий информационные входы мультиплексора 73 соединены с прямым и инверсным выходами седьмого триггера 87, четвертый вход - с первым выходом запоминающего узла 56, группа выходов которого соединена с вторым информационным входом мультиплексора 58, второй выход запоминающего узла 56 - с синхровходами первого и второго одновибраторов 37, 38, четвертый выход - с информационным входом D восьмого триггера 88 и шиной 24 прерываний, адресная группа входов запоминающего узла 67 соединена с выходами счетчика55 адреса, счетный вход которого соединен с выходом готовности аналого-цифрового преобразователя 14 и синхровходом девятого триггера 89 и первым входом седьмого элемента 90 И, информационный вход 9 десятого триггера 89 соединен с выходом триггера 81 и вторым входом второго элемента 64 ИЛИ, вход сброса R десятого триггера 89 соединен с входом сброса R первого триггера 59, входом сброса одновибратора 60 и вторым информационным входом блока задержки 61, выходом готовности буферного запоминающего устройства 16, синхровходом С триггера 88 и первым входом восьмого элемента 91 И, второй вход восьмого элемента 91 И соединен с прямым выходом триггера 88, а выход - с синхровходом С триггера 81, инверсный выход триггера 88 соединен с входом сброса R триггера 87 и вторым входом седьмого элемента 90 И, выход которого соединен с вторым входом пятого элемента 86 ИЛИ, выход триггера 89 соединен с первым входом шестого элемента 92 ИЛИ и счетным входом счетчика 18 адреса, второй вхОд шестого элемента 92 ИЛИ соединен с первым синхровходом первого триггера 59, третий вход - с первым выходом одновибратора 60, а выход -„с входом записи буферного запоминающего устройства 16, выход первого триггера 59 соединен с первым входом седьмого элемента 93 ИЛИ, второй вход которого соединен со вторым выходом одновибратора 60, а выход - с входом разрешения блока задержки 61, второй синхровход первого триггера 59 и третий выход одновибратора 60 соединены с первым и вторым входами восьмого элемента 94 ИЛИ,

выход которого соединен с входом чтения буферного запоминающего устройства 16, выход одновибратора 72 соединен с входом установки счетчика 18 адреса, выходы

мультиплексора 58 соединены с адресными входами первого и второго коммутаторов 3.1, 3.2, выходы вентилей 57 соединены с первой группой входов программируемого усилителя 7, четыре выходы мультиплексора 73 соединены с входами разрешения первого и второго устройств выборки-хранения 2.1, 2.2 и первого и второго коммутаторов 3.1.3.2.

Блок 46 отображения (фиг.З) содержит блок дешифрации 95, адресные входы которого соединены с шиной адресов 21, входы управления - с входной шиной 22 управления, входы синхронизации - с фазовыми выходами распределителя фаз 96, первый выход блока дешифрации 95 соединен с шиной 25 управления, второй - с входом разрешения приемопередатчика 97, первые входы-выходы которого соединены с шиной 20 данных,

а вторые входы-выходы соединены с информационными входами видеопамяти 98, последовательно соединенной со сдвиговым регистром 99, первыми информационными входами регистра 100 команд и состояний, первого и второго регистров 101. 102 изображения и схемы 103 последовательно интерфейса, первая группа выходов и третий выход блока дешифрации 95 соединены с входами управления видеопамяти 98 и сдвигового регистра 99, четвертый и пятый выходы - с входами записи и разрешения регистра 100 команд и состояний, шестой выход - с первыми входами записи первого и второго регистров 101. 102 изображения, седьмой выход - со вторым входом записи второго регистра 102 изображения, вторая группа выходов - с адресными входами мультиплексора 104, первая группа информационных входов которого соединена с выходами первого и второго регистров 101 102 изображения, а вторая группа информационных входов - с выходами первого и второго счетчиков 105, 106 изображения и входами первого запоминающего узла 107, первый выход которого соединен со счетным входом второго счетчика 106 изображения, второй выход - с входами разрешения второго запоминающего узла 108 и регистра 109 прерываний и вторым информационным входом регистра 100 команд и состояний, восьмой выход блока дешифрации 95 соединен с управляющим входом схемы 103 последовательного интерфейса,

тактовый вход которой соединен с выходом генератора 110 тактовых импульсов и входом распределителя фаз 96, второй вход второго запоминающего узла 108 соединен с выходом сдвигового регистра 99 вход записи которого соединен с первым фазовым

выходом распределителя фаз 96, первый выход регистра 100 команд и состояний соединен с входом сброса первого регистра 101 изображения, второй выход- с входом

сброса второго регистра 102 изображения, третий выход с входом разрешения регистра прерывания 109, выход которого соединен с шиной 24 прерываний, счетный вход первого счетчика 105 изображения соединен с вторым фазовым выходом распределителя фаз 96, входы состояния схемы 103 последовательного интерфейса соединены с выходами переключателя режимов 111, а выход -с входом преобразователя 112, выходы которого Ъоединены с группой выходов 49, выходы мультиплексора 104 соединены с адресными входами видеопамяти 98, выходы запоминающих узлов 107, 108 соединены с группой выходов 48.

Устройства 2,1, 2.2 обеспечивают фиксацию мгновенных значения аналоговых сигналов и могут быть выполнены на микросхемах типа 1100 СК 4, представляющих собой быстродействующее интегральное

устройство выборки и хранения, конденсаторах хранения и буферных усилителях с коэффициентом передачи 1, построенных на операционных усилителях КР544УД2. Первый, второй и третий коммутаторы

3.1,3.2, 6 коммутируют входные аналоговые сигналы и контрольный сигнал на вход преобразователя 14 и могут быть выполнены на микросхемах КР590КН6 и КР590КН4.

Усилитель 8 представляет собой операционный усилитель с программно переклю- чающими коэффициентами передачи, обеспечивающий согласование диапазона входных сигналов, поступающих на группы 4.1-4 IM, 5.1-5.N входов с входным диапазоном устройств 2.1, 2.2 и может быть выполнен на быстродействующем усилителе КАР544УД2А.

Делитель 9 сопротивлений представляет собой операционные цепи усилителя 8 и

может быть выполнен на точных резисторах

типа С2-29 и переменном резисторе типа

СЗ-39.

Коммутатор диапазона 10 коммутирует операционные цепм усилителя 8 и может быть выполнен на микросхеме КР590КН4.

Регистр 11 диапазона обеспечивает управление коммутатором диапазона 10 и может быть выполнен на микросхемах К555ТМ8.

Буферный усилитель 12 имеет коэффициент передачи, равный 1, и обеспечивает буферизацию делителя 9 сопротивлений, может быть выполнен на операционном усилителе КР544УД2.

Преобразователь 14 может быть выполнен на микросхеме К1108ПВ2А, представляющий собой быстродействующий АЦП последовательного приближения, включающий в себя источник опорного напряжения.

Блок коммутации 15 осуществляет передачу выходных данных АЦП в устройство синхронизации и может быть выполнен на микросхемах К555АПЗ, движковом вылюча- теле В ДМ 1-4,

Буферное запоминающее устройство 16 содержит собственные накопитель, который может быть выполнен на микросхемах КР565РУ6Б, схему управления и синхронизации, которая может быть выполнена на микросхеме КМ18ЮВТЗ,

Счетчик 18 адреса может быть выполнен на микросхемах К555 ИЕ 15, К555 ИЕ7.

Блок дешифрации 26 служит для выбора одного из N каналов регистрации, задания режимов запуска в устройстве синхронизации в соответствии с адресом, установленным на шине 21 адресов и управляющими сигналами шины 22 управления и может быть выполнен на ммкросхемах К555СП1, К555ИД4 и выключателе движковом ВДМ1- 4.

Регистри 27 способа запуска принимает информацию с шины 20 данных, управляет (аналоговыми) компаратора 31,32 и (цифровыми) компаратора 41,42 и может быть выполнен на микросхемах К555ТМ8.

Регистр 28 уровня запуска выдает информацию на (цифровые) компараторы 41,42 и может быть выполнен на микросхемах К555ТМ8.

Регистр 29 контрольного сигнала управляет вторым ЦАП 44 и может быть выполнен на микросхемах К555ТМ8.

Преобразователь 30 принимает информацию с шины 20 данных и выдает аналоговый сигнал и может быть выполнен на микросхемах К572ПА2А и КР140УД608.

Первый и второй компараторы 31,32 выдают сигналы аналогового запуска по положительному или отрицательному фронту и могут быть выполнены на микросхемах КР554СА4.

Согласующий и инвертирующие усилители 33,34 могут быть выполнены на микросхемах КР544УД2А.

Первый и второй мультиплексоры 35,36 формируют сигналы пуска и вторичного пуска в зависимости от управляющих сигналов и могут быть выполнены на микросхемах К55КГ12.

Первый и второй одновибраторы 37,38 (цифрового пуска) с информационным входом, входом сброса и синхровходом могут

быть выполнены на микросхемах КП555ТМ2 и К555АГЗ.

Третий и четвертый компараторы 41,42 выдают сигналы цифрового запуска по на- 5 растающему или спадающему фронту и могут быть выполнены на микросхемах К555СП1.

Блок 43 элементов НЕ инвертирует информацию регистра 28 уровня запуска и мо0 жет быть выполнена на- микросхеме К555ЛН1.

Преобразователь 44 принимает информацию с регистра контрольного сигнала и выдает аналоговый контрольный сигнал, ве5 личина которого программируется в регистре 29 контрольного сигнала и можёт быть выполнена на микросхемах К1108ПА1А и КР140УД6.

Генератор 45 тактовых импульсов

0 представляет собой кварцевый генератор, может быть выполнен на резонаторе РК169МА5ВС, микросхемах К55ИЕ7. К555ЛН1, резисторах, конденсаторе.

Регистр 50 программ принимает инфор5 мацию с внутренних шин данных и выдает сигналы .управления режимами регистрации, работой УВХ 2.1, 2.2 коммутаторов 3.1, 3.2, 6 и может быть выполнен на микросхе- ма х- К55ИР23. К555ЛИ1. К555ИД4,

0 К555ЛН1.

Таймеры 51,52 частоты и числа дискретизации служат для программирования параметров регистрации.

Приемопередатчик 53 осуществляет пе5 редачу данных с шины 20 данных ЭВМ на внутреннюю магистраль данных для программирования и наоборот, при любой операции чтения, может быть выполнен на магистральных микросхемах К555АП9.

0 Блок дешифрации. 54 формирует сигналы управления отдельными функциональными узлами в соответствии с адресом, установленным на шине 21 адресов, и управляющими сигналами шины 22 упрэвле5 ния и может быть выполнен на микросхемах 555СП1, К555ЛИЗ, К555ИД7, К555ЛА4, К555ЛН1, К555ЛАЗ, К555ЛЛ1 и движковом выключателе ВДМ1-8.

Счетчик 55 адресе выдает адреса ячеек

0 запоминающего узла 56 при программировании от ЭВЗ и формирует адреса при чтении из запоминающего узла 56 и может быть выполнен на микросхемах К555ИЕ7.

5 Запоминающий узел 56 содержит последовательность номеров каналов, составляющих цикл измерений с указанием конца цикла, программируется от ЭВМ по шине 20 данных и может быть выполнен на микросхемах КР185РУ9, К555ПН1. К555ПАЗ.

Вентили 57 диапазона измерения передают с внутренних шин данных код диапазона измерения по сигналу с блока дешифрации 54 и могут быть выполнены на микросхемах К555АПЗ

Мультиплексор 58 передает код номера канала коммутаторов 3.1, 3.2 либо с внутренней шины данных при программировании диапазонов измерения, либо с выхода запоминающего узла 56 в процессе регистрации и может быть выполнен на микросхеме К555КП11.

Триггер 59 с двумя синхровходами и входом сброса R формирует сигналы записи (ЗБП) и чтения (ЧБП) для устройства 16 и сигнал загфета ответа в режиме обращения к устройству 16 как к регистру по сигналам ЗБП, ЧБП и может быть выполнен на микросхеме К555ТМ2.

Одновибратор 60 с выходом запуска и входом сброса формирует сигналы управления для устройства 16 в режиме чтения данных с преобразователя 14 и может быть выполнен на микросхеме К555АГЗ, на резисторах и конденсаторах.

Блок задержки 61 с двумя информационными входами и входом разрешения при обращении к отдельным функциональным узлам от ЭВМ формирует с задержкой ответный сигнал и может быть выполнен на микросхемах К555ЛН1, К555ЛИ1, К555ЛАЗ, К155ЛП8.

Мультиплексор 62 тактовых импульсов вырабатывает тактовые импульсы для таймеров 51,52 используя внутренние или внешние тактовые импульсы.

Элемент 63 ИЛИ собирает сигналы предпускового режима регистрации и цифрового запуска и может быть выполнен на микросхеме К555ЛЛ1;

элемент 64 ИЛИ блокирует сигнал с вы хода триггера 81 регистрации и может быть выполнен на микросхеме К555ЛЕ1; элемент 65 И-ИЛИ вырабатывает сигнал управления триггером 74 в разных режимах регистрации и может быть выполнен на микросхеме К555ЛР11; мультиплексор 66 вырабатывает сигнал установки риггера 81 регистрации и может быть выполнен на микросхеме К555КП2, элемент 67 И вырабатывает сигнал разрешения работы таймера 52 числа дискретизаций на первом участке регистрации и может быть иыполнен на микросхеме К555ЛЕ4; элемент 38 И-ИЛИ вырабатывает сигнал разрешена, работы таймера 51 частоты и может быть выполнен на микросхеме К599ЛКЗ, элемент 69 И-ИЛИ вырабатывает сигнал разрешения работы таймера 52 числа дискретизаций и может быть выполнен на микросхеме К555ЛР11, элемент 70 ИИЛИ-НЕ пропускает либо сигнал вторичного пуска, либо сигнал с выхода таймера 52 числа дискретизаций в зависимости от режима регистрации и может быть выполнен

на микросхеме К599ЛКЗ; элемент 71 И блокирует сигнал конец счета в случае режима непрерывного цикла регистрации и может быть выполнен на микросхемах К555ЛАЗ и К555ЛН1.

0 Одновибратор 72 с входами разрешения и запуска вырабатывает сигнал сброса счетчика 18 адреса и может быть выполнен на микросхеме К555АГЗ; мультиплексор 73 вырабатывает сигналы управления для уст5 ройств 2.1. 2.2 и коммутаторов 3.1, 3.2 в нормальном и конвейерном режимах выборки и может быть выполнен на микросхеме К555КП11; триггер 74 с входами установки S и R вырабатывает сигнал разре0 шения работы тЬймера 52 числа дискретизаций на втором участке регистрации и может быть выполнен на микросхеме К555ТМ2.

Элемент 75 И вырабатывает сигнал разрешения работы таймера 51 частоты и мо5 жет быть выполнен на микросхеме К555ЛИ1; элемент 76 ИЛИ собирает импульсы дискретизации на всех трех участках регистрации и может быть выполнен на микросхеме К555ЛИЗ; элемент 77 И пропускает

0 импульсы дискретизации и может быть выполнен на микросхеме К555ЛЛ1; триггер 78 (предпуска) с входами установки S и R может быть выполнен на микросхеме К555ГМ2; триггер 79 (пуска) с информационным вхо5 дом D и синхровходом С может быть выполнен на микросхеме К555ТМ2; триггер 80 счета с входами установки S и R формирует интервал времени между сигналом пуск и конец счета запрограммированного обще0 го числа дискретизаций и может быть выполнен на микросхеме К555ТМ2; триггер 81 (регистрации) с входом установки S, информационным входом D и синхровходом С оп- ределяют время, в течение которого

5 происходит запись измеренных значений в устройство 16, и может быть выполнен на микросхеме К55ТМ2; триггер 82 (вторичного пуска) с информационным входом D и синхровходом С может быт выполнен на микро0 схеме К555ТМ2.

Элемент 83 И пропускает сигнал предварительного пуска в случае отсутствия сигнала счета с выхода триггера 80 счета и может быть выполнен на микросхеме

5 К555ЛИ1; элемент 84 И пропускает сигнал счета с выхода пятого триггера 80 счета в случае отсутствия сигнала с выхода элемента 70 И-ИЛИ-НЕ; элемент 85 ИЛИ вырабатывает сигнал сброса счетчика 55 адреса и может быть выполнен на микросхеме

К555ЛЕ1; элемент 86 ИЛИ вырабатывает сигнал запуска для преобразования 14 и может быть выполнен на микросхеме К555ЛИ1. , ,

Триггер 87 со счетным входом С и вхо- дом сброса R вырабатывает входные сигналы для мультиплексора 73 и может быть выполнен на микросхеме К555ТМ2; триггер 88 (измерения) с информационным входом D, с синхровходом С и входом установки S определяет время измерения группы каналов (одного цикла) и может быть выполнен на микросхеме К555ТМ2; триггер 89 с информационным входом D, синхровходом С и входом сброса R вырабатывает сигнал за- писи в устройстве 16 по заданному фронту сигнала готовности преобразователя 14 и может быть выполнен на микросхеме К555ТМ2.

Элемент 90 И пропускает сигнал го- товности с преобразователя 14 для формирования сигнала след/ющего пуска преобразователя 14 и может быть выполнен на микросхеме К555ЛАЗ; элемент 91 И вырабатывает сигнал сброса триггера 81 реги- страции и быть выполнен -на микросхеме К555ЛИ1; элемент 92 ИЛИ вырабатывает сигнал записи в устройство 16 и может быть выполнен на микросхеме К555ЛИЗ; элемент 93 ИЛИ вырабатывает сигнал запрета ответа и может быть выполнен на микросхеме К555ЛАЗ, элемент 94 ИЛИ вырабатывает сигнал чтения для устройства 16 и может быть выполнен на микросхеме К555ЛИ1

Блок дешифрации 95 формирует сигналы управления отдельными функциональными узлами блока 46 отображения в соответствии с адресом, установленным на шине 21 адресов, и управляющими сигнала- ми шины 22 управления и может быть выполнен на микросхемах К555СП1, К555ИД4, К555ЛА2, К555ЛИ1, К55ЛАЗ, К555ЛН1, К155ЛП8 и выключателе движковом ВДМ1- 4.

Распределитель 96 фаз обеспечивает формирование восьми последовательностей тактовых импульсов, последовательно сдвинутых относительно друг друга, и может быть выполнен на микросхеме К555ИР8; приемопередатчик 97 связывает шину 20 данных ЭВМ с внутренней шиной данных и может быть выполнен на микросхемах К555АП9; видеопамять 98 обеспечивает запоминание одного кадра изображения и может быть выполнена на микросхемах К565РУ5Б.

Сдвиговый регистр 99 обеспечивает прием данных, соответствующих одной группе элементов изображения, от видеопамяти 98 и преобразует его в последовательность импульсов, может быть выполнен на микросхеме К555РУ9; регистр 100 команд и состояний может быть выполнен на микросхеме К1804ИР1;

первый регистр 101 изображения обеспечивает запоминание адреса группы элементов изображения, а также инкремен- тирование адреса, может быть выполнен на микросхемах К555ИЕ7; второй регистр 102 изображения .обеспечивает запоминание адреса сборки изображения, а также инкре- ментирование адреса, может быть выполнен на элементах К555ИЕ7.

Схема 103 последовательного интерфейса обеспечивает вывод данных на графопостроитель и может быть выполнена на микросхеме КР581ВА1; мультиплексор 104 адреса видеопамяти обеспечивает выдачу адреса видеопамяти 98- при внешнем обращении и чтении видеомонитора, может быть выполнен на микросхеме К555КП12, счетчик 105 изображения обеспечивает формирование текущего адреса группы элементов изображения и инкрементирование адреса, может быть выполнен на микросхемах К555ИЕ7; счетчик 106 изображения обеспечивает формирование текущего адреса с троки изображения и инкрементирование адреса, может быть выполнен на микросхеме К555ИЕ7.

Запоминающий узел 107 (синхросигналов) формирует импульсы синхронизации, может быть выполнен на микросхемах К556 Т5; запоминающий узел 108 (видеосигналов) обеспечивает управление цветом и может быть выполнен на микросхемах К556Т5,

Регистр 109 прерывания формирует сигнал прерывания и может быть выполнен на микросхемах К555ТМ2, К155ЛП8, генератор 110 тактовых импульсов представляет собой кварцевый генератор, может быть выполнен на микросхеме К531ГТ1 и резонаторе; переключатель режимов 111 программирует режим работы схемы 103 последовательного интерфейса и может быть выполнен с помощью перемычек, преобразователь 112 преобразует цифровые сигналы напряжения в токовые и может быть выполнен на микросхеме К155ЛН5, транзисторах КТ361 Г, транзисторах КТ361Г и резисторах.

Предлагаемая многоканальная система сбора и регистрации работает следующим образом.

Для регистрации аналоговых сигналов используется принцип автоматической цифровой регистрации, включающий1 дискретизацию процесса во времени с заданными параметрами дискретизации и одновременную фиксацию мгновенных значений электрических сигналов; измерение зафиксированных мгновенных значений сигналов и получение результатов измерений в двоичном коде; запоминание результатов измерения в буферном запоминающем устройстве (БЗУ).

Таким образом, в результате выполненной регистрации в БЗУ находится образ исследуемого процесса в виде массива мгновенных значений входных сигналов, снятых через заданные интервалы дискретизации.

До начала процесса регистрации программно задаются от ЭВМ режимы регистрации в каждых из N блоков 19 управления. Блок дешифрации 26 под воздействием управляющих сигналов машинной магистрали ввода или вывода, поступающих на шину 22 управления, дешифрирует адрес, поступлений с шины 21 адресов ЭВМ и вырабатывает сигналы выбора одного из N блоков 19 управления. Сигнал выбора разрешает работу блока дешифрации 54, находящегося в блоке 19 управления, крторый под воздействием управляющих сигналов ввода или вывода вырабатывает сигналы управления отдельными функциональными узлами блока 19 управления в зависимости от значений разрядов шины 21 адресов процессора. Блок задержки 61 при наличии обращения от ЭВМ, т,е. поотупл-эние на нбго выходного сигнала блока дешифрации 54 или сигнала готовности устройства 16, выдает ответный сигнал обмена с процессором по шине 25 управления с задержкой относительно сигналов обращения ввода или вывода.

Блок управления 19 обеспечивает четыре программно устанавливаемых режима регистрации с неравномерной дискретизацией на трех участках регистрации:

нормальный, когда регистрация производится после прихода сигналов предварительного пуска (ПП) и пуска (П) на одном, двух или трех участках регистрации с программируемым числом и интервалом дискретизаций; .

задержанный, огда после прихода сигналов предварите; ьного пуска ПП и пуска П выполняется задержка начала регистрации, величина которой программируется, а затем регистрация входного сигнала на одном или двух участках регистрации с программируемым числом и интервалом дискретизаций;

задержанный до вторичного пуска, когда необходимая задержка регистрации заранее неизвестна; после прихода сигналов предварительного пуска ПП и пуска П выполняется задержка начала регистрации до

прихода сигнала вторичного пуска (ПВ), а затем регистрация входного сигнала на одном или двух участках регистрации с программируемым числом и интервалом дискретизаций; при этом значение полученной задержки не программируется, а определяется путем чтения таймера 52 числа дискретизаций на первом участке;

предпусковой, когда регистрация начи- нается в момент прихода сигнала предварительного пуска ПП, и состоит из трех участков регистрации;

предпускового и двух послепусковых и программируемых интервалом дискретиза- ции для трех участков и числом дискретиза- ций на двух послепусковых участках регистрации. Число дискретизаций на предпусковом участке может быть любым, в том числе превышающим количество результа- тов измерений, которое может уместиться в устройстве 16. В этом случае производится стирание самых старых результатов измерений и замена их новыми.

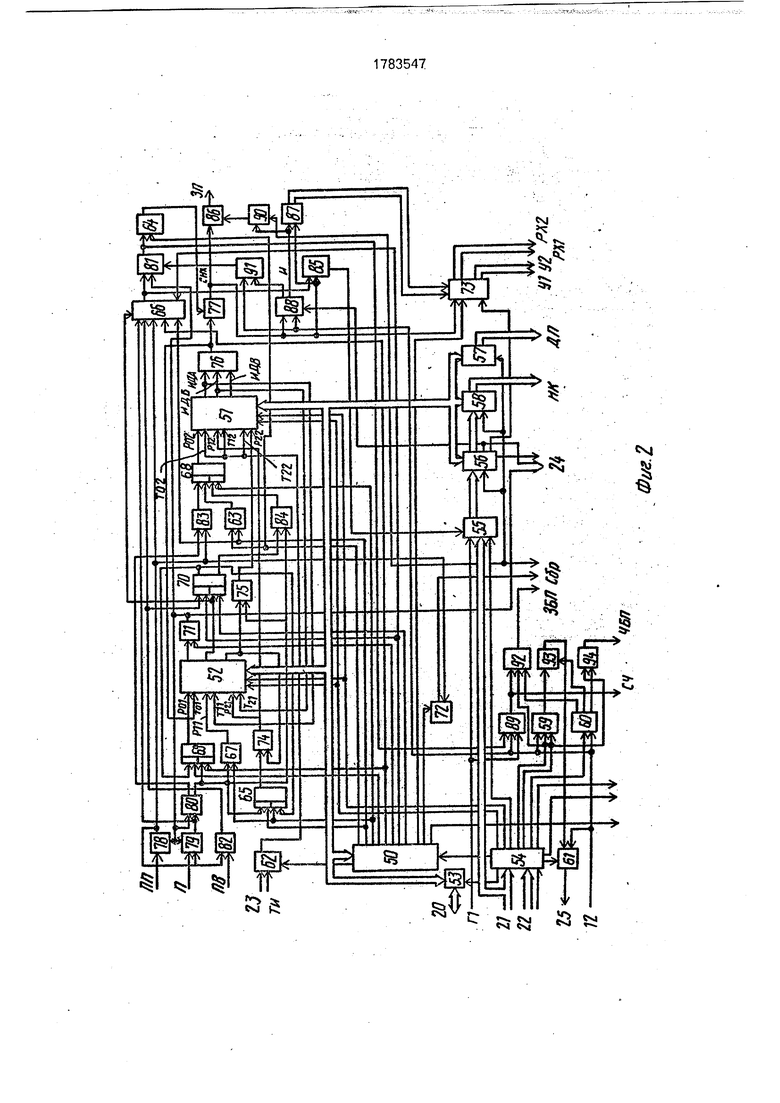

Временные диаграммы работы в этих режимах приведены на фиг.4.

Вид режима регистрации и его параметры хранятся в регистре 50 программ, двух таймерах 51,52 и втором запоминающем устройстве 56, В них записывается инфор- мация с внутренней шины данных. Приемопередатчик 53 обеспечивает связь между шиной 20 данных ЭВМ и внутренней шиной данных. Сигналы записи в регистр и таймеры вырабатываются блоком дешифрации 54.

Регистр 50 программ определяет следующие параметры регистрации:

1} вид выборки аналоговых входных сигналов: нормальная или конвейерная; 2) режим регистрации: задержанный, задержанный до вторичного пуска, предпусковой;

3) блочная запись в БЗУ;

4} непрерывный цикл регистрации; 5) вид тактирования: внутреннее или внешнее.

Таймер частоты служит для программной установки частоты дискретизации на трех участках и работает в режиме делителя частоты.

Таймер числа дискретизации служит для программной установки числа дискре- тизаций на трех участках и величины программируемой задержки.

Запоминающий уиел (ЗУ) служит для выдачи кода номера канала в коммутаторы 3.1, 3.2, переключающие входные аналоговые первый и второй сигналы.

После программирования системы осуществляют процесс измерения и регистрации входных данных.

Для начала работы требуются сигналы предварительного пуска ПП и пуска П для обеспечения синхронизации процесса регистрации с исследуемым процессом.

В качестве сигнала предварительного пуска используется сигнал программируемого предпуска, поступающий с выхода блока дешифрации 26 на все блоки 19 управления и подготавливающий каналы 1 регистрации к процессу регистрации или начинающий регистрацию в предпусковых режимах.

Система обеспечивает формирование сигнала пуска четырех видов:

программируемого цифрового пуска, выполняемого вручную оператором или по программе от процессора;

внешнего аналогового пуска, в качестве которого используется один из входных измеряемых сигналов;

внешнего цифрового пуска, в качестве которого используется один из внешних аналоговых сигналов, преобразованный в цифровую форму;

внешнего вторичного пуска.

По внешнему аналоговому сигналу пуск производится в момент пересечения знало- говым сигналом программно установленного уровня запуска на положительном и/или отрицательном наклоне входного сигнала.

Преобразователь 30, принимающий информацию с шины 20 данных, выдает на вход первого и второго компараторов 31,32 аналоговый сигнал величина которого в зависимости от входного кода на щине 20 дан- ных программируется от предельного положительного до предельного отрица- тельного значения. Входной код определяется требуемым уровнем запуска и способом запуска. На первый компаратор 31 подается входной сигнал через согласующий усилитель 33, а на второй через ин- вертирующий усилитель 34.

При равенстве входного аналогового сигнала и запрограммированного уровня запуска с выхода преобразователя 30 один из компараторов 31,32 формирует выход- ной сигнал, поступающий на входы первого и второго мультиплексоров 35,36, на которые поступают также сигналы программируемого цифрового пуска от регистра 27 способа запуска, внешнего цифрового пус- ка и внешнего вторичного пуска. Компараторы 31,32 управляются двумя сигналами НСП и ГСО. определяющими способ запуска регистрации iо аналоговому сигналу. Способ запуска программируется в регистре 27 способа запуска, в который информация записывается с шины 20 данных через процессор по сигналу записи блока дешифрации 26.

Формирование сигнала пуска по аналоговому сигналу производится в соответствии с фиг.4 в момент пересечения аналоговым сигналом уровня запуска в направлении нарастания, когда наклон сигнала положительный (НСП) или спадания, когда наклон сигнала отрицательный (НСО). В соответствии с фиг.5 в первом случае фор; мируется сигнал пуска момент tn, во втором - сигнал П в момент tn.

По внешнему цифровому сигналу пуск так же, как и в предыдущем случае, производится в момент пересечения аналоговым сигналом, преобразованным в цифровой код, программно установленного уровня запуска на положительном и/или отрицательном наклоне входного сигнала.

На первые входы третьего и четвертого компараторов 41,42 поступает цифровой код с выхода преобразователя 14. На вторые входы компараторов 41,42 поступает код запрограммированного уровня запуска с выхода регистра 28 уровня запуска; на первый компаратор 41 поступает прямой , йа второй компаратор 42 поступает инверсный код. Программирование регистра 28 уровня запуска осуществляется с и-ины 20 данных по сигналу записи, вырабатываемому блоком дешифрации 26,

Третий компаратор 41 выдает сигнал на выходе, когда сигнал с положительным наклоном пересекает запрограммированный уровень запуска, четвертый компаратор 42 выдает сигнал на выходе, когда сигнал с отрицательным наклоном пересекает уровень запуска. Выходные сигналы с компараторов 41,42 запоминаются в первом и втором одновибраторах 37,38 по сигналу пускового канала, указывающему, что цифровой пуск производится именно по тому каналу, информация с которого подается в данный момент на вход компараторов 41,42, В зависимости от того, какой способ запуска запрограммирован в регистре 27 способа запуска (по положительному наклон/, по отрицательному наклону или двунаправпен- ный) сигнал пуска возникает с выхода первого одновибратора 37 или второго одновибратора 38 или с обоих.

По внешнему вторичному пуску сигнал пуска вырабатывается вторым мультиплексором 36. В зависимости от программы регистра 27 способа запуска на выход второго мультиплексора 36 проходит один из трех сигналов: внешнего аналогового пуска, внешнего цифрового пуска или внешнего

вторичного пуска, далее он проходит на все N блоков 19 управления.

Внешний вторичный пуск используется в режиме регистрации, задержанном до вторичного пуска. Этот режим позволяет опре- делить величину временного сдвига между двумя быстропротекающими процессами на двух каналах 1 регистрации, если задержка между ними заранее неизвестна. Например, если в канале 1.1 регистрации запрограммирован режим регистрации, нормальной по аналоговому пуску, а в канале 1.2 регистрации запрограммирован режим, задержанный до вторичного цифрового пуска, то таймер 52 числа диск- ретизаций блока 19.2 управления второго канала определит время сдвига канала регистрации второго канала 1.2 относительно первого 1.1.

Триггер 78 (предпуска) (фиг.2) воспри- нимает сигнал предпуска ПП с выхода блока дешифрации 26.

Триггер 79 пуска воспринимает сигнал пуска П с выхода мультиплексора 35: триггер 82 вторичного пуска воспринимает сиг- нал ПВ с выхода второго мультиплексора 36. Сброс триггеров 78,79,82 осуществляется по сигналу выполнения общего числа дискретизаций на всех участках регистрации - КС (конец счета) Рассмотрим различные ре- жимы регистрации

В нормальном режиме регистрации предусматривается возможность работы с различным интервалом дискретизации на трех участках регистрации. В этом случае в трехканальном таймере 52 программируется общее число дискретизаций на всех трех участках регистрации, число дискретизаций на первом участке и число дискретизаций на втором участке регистрации. В таймере 51 частоты, все три канала которого работают в режиме делителей частоты, программируются интервалы дискретизаций на первом, втором и третьем участках регистрации.

На выходе регистра 50 программ в нормальном режиме регистрации сигналы признаков задержанного режима и предпускового устанавлиг аются в нулевое состояние.

Работа начина ггся с прихода импульса предварительного пуска ПП на вход установки триггера 78 предпуска, с выхода которого сигнал поступает на информационный вход четвертого триггера 79 пуска. По приходе импульса пуска сигнал с выхода триг- гера 79 пуска поступает на триггер 80 счета и устанавливает его в единичное состояние. Сигнал С4 с прямого выхода триггера 80 счета проходит через элемент 69 И-ИЛИ и поступает на Е5ход Р01 разрешения первого

канала таймера 52 числа дискретизаций, разрешая его работу. Этот же сигнал С4 проходит через элемент 84 И, через элемент 68 И-ИЛИ и поступает на вход Р02 разрешения первого канала таймера 51 частоты, разрешая его работу. В качестве тактовых импульсов Т02 таймера частоты используются импульсы с выхода мультиплексора 62, который пропускает либо внутренние тактовые импульсы ТИ от генератора 45 тактовых импульсов, либо внешние тактовые импульсы по шине 23 внешнего тактирования в зависимости от вида тактирования, запрограммированного в регистре 50 программ. Внешнее тактирование используется для привязки моментов дискретизации аналоговых сигналов или запоминания цифровых сигналов к внешнему опорному сигналу. На выходе первого канала таймера 51 частоты появляются импульсы дискретизации с интервалом ИДА, который определяется коэффициентом деления запрограммированным в первом канале они проходят через элемент 76 ИЛИ и в качестве тактовых импульсов Т01 поступают на вход первого канала таймера 52 числа дискретизаций, а с его выхода проходят в качестве тактовых импульсов Т11 на второй канал таймера 52 числа дискретизаций для первого участка регистрации.

После того, как второй канал этого счетчика сосчитает запрограммированное число дискретизаций на первом участке, на выходе этого канала возникает сигнал, который проходит через элемент 70 И-ИЛИ-НЕ. Выходной сигнал ее КНА проходит на вход элемента 84 И, нулевой выходной сигнал которой поступает на вход элемента 68 И-ИЛИ, выходной нулевой сигнал последней запрещает работу первого канала таймера 51 частоты и импульсы дискретизации ИДА прекращаются.

Со второго выхода элемента 70 И-ИЛИ- НЕ единичный сигнал поступает на вход элемента 65 И-ИЛИ, выходной сигнал которой устанавливает триггер 74 в единичное состояние, разрешая тем самым работу второго канала таймера 51 частоты и третьего канала таймера 52 числа дискретизации, На выходе второго канале, таймера 51 частоты появляются импульсы дискретизации ИДБ, частота которых запрограммирована в этом канале. Импульсы ИДБ, пройдя через элемент 76 ИЛИ, поступ эют в качестве тактовых импульсов Т01 на вход первого канала таймера 52 числа ди( кретизаций, который продолжает счет, а также непосредственно с выхода второго канала таймера 51 частоты они поступают в качестве тактовых имп/ль- сов Т21 на третий канал таймера 52 числа

дискретизаций для второго участка регистрации. После того, как таймер 52 числа дискретизаций отсчитывает запрограммированное число дискретизаций на втором участке, на его третьем выходе появляется сигнал КНБ, который пройдя через элемент 75 И, поступает как сигнал разрешения Р22 на вход третьего канала таймера 51 частоты и сбрасывает триггер 74, запрещая работу третьего канала таймера 52 числа дискретизаций и второго канала таймера 51 частоты. Импульсы ИДБ прекращаются, а на выходе третьего канала таймера 51 частоты появляются импульсы ИДВ, частота которых определяется запрограммированным в этом канале коэффициентом деления. Импульсы ИДВ, пройдя через элемент 76 ИЛИ, поступают на вход первого каанала таймера 52 числа дискретизации в качестве тактовых импульсов Т01.

После того как таймер 52 числа дискретизаций отсчитает запрограммированное общее число дискретизаций на всех трех участках, на его первом выходе появляется сигнал, который, пройдя через элемент 71 И, в случае отсутствия сигнала непрерывного цикла регистрации с выхода регистра 50 программ сбрасывает триггеры 79, 78 пред- пуска, пуска и триггер 80 счета.

В случае, если в регистре 50 программы запрограммирован задержанный режим (единичный сигнал признака задержанного режима), работа таймера 51 частоты и второго и третьего каналов таймера 52 числа дискретизаций аналогично описанной выше, но первый канал таймера 52 числа дискретизаций используется для программирования величины задержки,и начинает работать по выходному сигналу на триггер 80 счета, а элемент 70 И-ИЛИ-НЕ,который проходит через элемент 69 И-ИЛИ и разрешает работу первого канала таймера 52 числа дискретизаций,

В задержанном режиме регистрации после прихода сигналов П, ПП выполняется задержка начала регистрации, а по ее окончании регистрация с запрограммированными числом дискретизаций и частотой дискретизаций. Импульсы дискретизации ИДА, формируемые на интервале задержки, не вызывают дискретизацию входного сигнала, а используются только для формирования определенной длительности участка задержки. Последующие импульсы дискретизации вызывают измерение входного сигнала.

Временные диаграммы работы в нормальном и задержанном режимах регистрации приведены на фиг,6.

Режим задержанный до вторичного пуска отличается от задержанного режима тем, что в этом режиме выходной сигнал элемента 70 И-ИЛИ-НЕ формируется не из 5 сигнала с выхода второго канала таймера 52 числа дискретизаций,а определяется сигналом вторичного пуска ПВ, который поступает на триггер 82 вторичного пуска, а с его выхода на вход элемента 70 И-ИЛИ-НЕ.

0 В результате первый канал таймера 52 числа дискретизаций считает импульсы дискретизации ИДА до прихода сигнала вторичного пуска, по которому начинается регистрация.

5 Величина задержки начала регистрации определяется путем чтения выходного кода таймера 52 числа дискретизаций. Временная диаграмма этого режима приведена на фиг.7,

0 В предпусковом режиме, когда на выходе регистра 50 программ сигнал признака предпускового режима единичный или единичный сигнал признака внешнего цифрового пуска, таймер 51 частоты начинает

5 работать по поступлению сигнала предварительного пуска ПП. Сигналы признаков режима проходят через элемент 63 ИЛИ на один вход элемента 68 И-ИЛИ, сигнал пред- йарительного пуска с выхода триггера 78

0 предпуска поступает на элемент 83 И и на другой вход элемента 68 И-ИЛИ, выходной сигнал которой разрешает работу первого канала таймера 51 частоты. Снимается разрешение после появления на выходе тригге5 ра 80 счета сигнала СЧ. т.е. по приходу сигнала пуска П.

Первый канал таймера 52 числа дискретизаций начинает работать по сигналу СЧ. Второй канал этого таймера для числа дис0 кретизаций на первом участке в этом режиме не работает вообще, т.к. дискретизация на первом участке используется как предпусковая, где число дискретизаций не программируется. По выходному сигналу СЧ

5 триггера 80 счета, который проходит через элемент 65 И-ИЛИ, триггер 74 устанавливается в единичное состояние и разрешает работу третьего канала таймера 52 числа дискретизаций и второго канала таймера 51

0 частоты, Дальше работа происходит аналогично описанной в предыдущем режиме. Временная диаграмма в предпусковом режиме приведена на флг.8.

Импульсы дискремзацми с различными

5 скоростями поступают с выхода элемента 76 ИЛИ на вход элемента 77 И.

На второй вход этого элемента поступает сигнал с выхода элемента 64 ИЛИ, который разрешает прохождение импульсов дискретизации через элемент 77 И на элемент 86 ИЛИ для формирования сигналов запуска ЗП преобразователя 14, На вход элемента 64 ИЛИ поступает сигнал внешнего цифрового запуска с выхода регистра 50 программ и сигнал с выхода триггера 81 регистрации, который определяет время регистрации, т.е. время в течение которого производится запись результатов измерений в устройстве 16. Триггер 81 регистрации устанавливается в зависимости от выбранного режима регистрации бДнймГиз сигналов, подаваемых на вход мультиплексора 66. В нормальном режиме регистрации это сигнал пуска, в задержанном - сигнал КС конца счета числа дискретизаций со скоростью ИДА, в задержанном по вторичному пуску - сигнал вторичного пуска, в предпусковом режиме - сигнал предварительного пуска. Триггер 81 регистрации сбрасывается сигналом готовности Г2 устройства 16 после регистрации последнего измерения, сигнал сброса формируется элементом 91 И.

Сигналы ЗП преобразователя 14 существуют на выходе в.течение единичного состояния триггера 81 регистрации, а в случае цифрового запуска ЗП АЦП появляются сразу по сигналу предварительного пуска, а заканчиваются по сбросу триггера 81 регистрации.

На каждый сигнал ЗП приходит сигнал готовности с преобразователя 14 П, поступающий на синхровход триггера 89, который вырабатывает выходной сигнал, который проходит через элемент 92 ИЛИ и с ее выхода на вход записи в устройство, 16-ЗБП. Сигнал с выхода триггера 89 как сигнал СЧ инкрементирует счетчик 18 адреса. Сброс триггера 89 производится сигналом готовности с устройства 16.

Блок 19 управления выдает сигналы управления первым, вторым и третьим коммутаторами 3.1,3.2,6, номера каналов первого и второго коммутаторов 3.1, 3.2, сигналы управления УВХ 2.1, 2.2 и диапазоны измерения преобразователя 14.

Диапазоны измерения преобразователя 14 ДП передаются при программировании с внутренних шин данных через вентили 57 и записываются в регистр 11 диапазона, обеспечивающий управление коммутатором 10 диапазона, который переключает операционные цепи усилителя 9. В результате обеспечивается программное переключение коэффициентов передачи этого усилителя, операционные цепи которого выполнены ча точных резисторах делителя сопротивлений 9.

При программировании в запоминающий узел 56 с внутренних шин данных записывается последовательность слов, каждое из которых включает в себя код номера канала, признак пускового канала и на последнем канале в цикле признак конца цикла.

. Такимобразом, цикл может быть сформирован из любого количества и любой последовательности номеров каналов первого и второго коммутаторов 3.1, 3.2. Адрес ячеек запоминающего узла 56 при программиро0 вании записываются в счетчик 65 адреса с шины 21 адресов по сигналу блока дешифрации 54.

При регистрации происходит считывание слов из узла 56, начиная с нулевого

5 адреса. Начальный сброс счетчика 55 адреса производится сигналом выхода мультиплексора 56, поступающему на первый вход элемента 85 ИЛИ, а сброс счетчика в начале каждого цикла - сигналом с выхода элемен0 та 77 И, поступающему на второй вход элемента 85 ИЛИ, выходной сигнал которого сбрасывает счетчик 55 адреса. Дальнейшее переключение адресов внутри цикла производится путем инкрементирования счетчика

5 55 адреса сигналом готовности преобразователя 14-Г1.

Код номера канала с выхода узла 56 поступает на одну группу входов мультиплексора 58, с выхода которого код номера

0 канала поступает на адресные входы первого и второго коммутаторов 3.1, 3.2. Мультиплексор 58 предлагает код номера канала первого и второго коммутаторов 3.1, 3.2 с выхода узла 56 в процессе регистрации, а в

5 процессе программирования передает код номера канала с внутренних шин данных одновременно с передачей диапазонов измерения преобразователя 14. Сигнал признака пускового канала ПК, который

0 указывает, что внешний цифровой пуск производится именно на этом канале, с выхода узла 56 поступает на первый и второй одно- вибраторы 37,38 (пуска). Сигналы управления первым и вторым устройствами 2.1, 2.2

5 и коммутаторами 3.1,3.2 снимаются с выхода мультиплексора 73 - У1, У2, РХ1, РХ2.

Для уменьшения динамической погрешности при регистрации аналоговых входных сигналов возможно использование конвей0 ерной выборки устройств 2.1, 2.2.

Все аналоговые входы каждого блока 1.N измерения аналоговых сигналов разбиты на две группы.

Первая и вторая группы 4,5 аналоговых

5 входов содержат по восемь каналов каждая. Фиксация мгновенных значений производится установленными на входе каждого канала устройств 2.1,2.2. Два многоканальных устройства 2Л, 2.2 представляют собой многоканальные устройства, каждое из которых

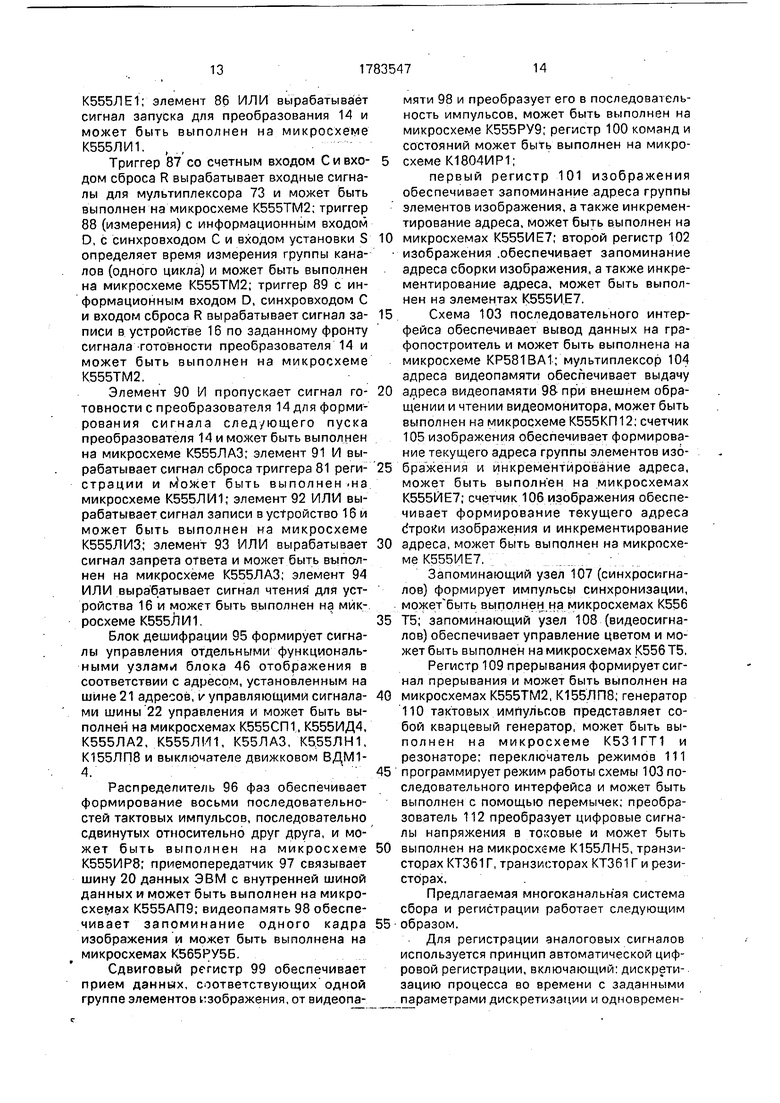

состоит из восьми УВХ и управляется раздельными сигналами разрешения хранения РХ1 и РХ2; при подаче на входы устройств 2.1,2.2 сигнала РХ1 или РХ2 обеспечивается запоминание мгновенного значения измеряемого сигнала соответствующими устройствами 2.1, 2.2. Два коммутатора 3.1, 3.2 с объединенными выходами подключают на вход преобра ователя 14 аналоговые сигналы, зафиксированные в устройствах 2.1, 2.2. При работе с нормальной выборкой 16 измеряемых входных сигналов подключаются на вход каждого из восьми каналов устройств 2.1, 2.2 на управляющие входы устройств 2.1, 2L2 подаются управляющие сигналы РХ2 0, разрешающие перевод обоих устройств 2,1, 2.2 в режим хранения; они формируются из выходного сигнала триггера 88 измерения. В нормальном режиме выборки сигнал признака конвейерной выборки с выхода регистра 50 программ равен нулю и с выхода мультиплексора 73 на управляющие входы коммутаторов 3.1, 3.2 подаются сигналы в соответствии с условием У1 У2. После перевода обоих устройств 2,3 в режим хранения производится последовательное измерение входных сигналов по всем каналам, коммутируемым первым и вторым коммутаторами 3.1, 3.2 в течение 16 циклов преобразования. После измеренеия по всем каналам оба УВХ переводятся в режим вы- борки путем установки сигналов РХ1 РХ2 1. При конвейерной выработке две группы аналоговых входов 4,5 объединяются, каждый датчик измеряемого сигнала подключается на входы двух устройств 2.1, 2.2. Управляющие сигналы устройств 2.1, 2.2 взаимоинверсные РХ1 РХ2, а управляющие сигналы первого и второго коммутаторов 3.1. 3.2 и У2 изменяются в соответствии с сигналами РХ1 и РХ2 и находятся также в противофазе, т.е. коммутаторы 3.1, 3.2 выбираются поочередно,

В результате в момент фиксации значений входных сигналов один из устройств 2.1, 2.2 переходит в режим хранения, а другой в режим выборки. Выходы устройства 2.1 или устройства 2.2, который находится в режиме хранения последовательно опрашиваются соответствующим коммутатором 3.1, 3.2 и измеряются преобразователем 14 в течение восьм циклов преобразования. После окончания измерения может быть произведена фиксация следующих значений входных сигналов по этим же каналам, т.е. время выборки устройств 2.1,2.2 исключается из времени измерения входного сигнала.

В конвейерном режиме выборки сигнал признака конвейерного режима с выхода регистра 50 программ - единичный. Сигналы управления первым и вторым коммутато- 5 рами 3.1, 3.2, а также устройствами 2.1, 2.2 в этом режиме формируются триггером 87 из сигнала СНХ с выхода элемента 77 И и выходного сигнала триггера 88 измерения. Запуск преобразователя 14 независимо

0 от режима работы формируется по его сигналам готовности, что увеличивает быстродействие системы. Первый сигнал ЗП запуска преобразователя 14 в цикле представляет собой сигнал импульсов дискрети5 зации СНХ, последующие сигналы ЗП внутри цикла формируются из сигнала готовности преобразователя 14 П, который поступает на вход элемента И 90, на другой вход этого элемента поступает сигнал с вы0 хода триггера 88, который устанавливается в единичное состояние сигналом СНХ с выхода элемента 77 И, а сбрасывается сигналом готовности устройства 16 на последнем канале цикла, т.е. когда узел 56 выдает сиг5 нал конца цикла КЦ. С выхода элемента 90 И сигнал проходит через элемент 86 ИЛИ, на второй вход которого поступает сигнал СНХ, Выходной сигнал элемента 86 ИЛИ Осуществляет запуска преобразователя 14,

0 Формирование сигналов ЗП из сигналов П в течение цикла увеличивает быстродействие, т.е. происходит параллельно запись результата измерения в устройстве 16 и измерение следующего значения вход5 ного сигнала с преобразователя 14.

Временная диаграмма описанных сигналов приведена на фиг.9.

Блока 19 управления кроме режима регистрации записи результатов измерения в

0 устройство 16 непосредственно от преобразователя 14 обеспечивает запись и чтение от ЭВМ, обращаясь к нему как к регистру по сигналам ЗБП и ЧБП. Формирование этих сигналов записи и чтения производится с

5 помощью триггера 59. Сигнал записи поступает с первого синхровхода триггера 59 на вход элемента 92 ИЛИ, а сигнал чтения на вход элемента 94 ИЛИ, а с выходов на соответствующие входы устройства 16. Кроме

0 того на выходе триггера 59 формируется сигнал запрета ответа при появлении сигналов ЗБП и ЧБП, ответ в этом режиме должен появиться толькао после окончания этих сигналов. Сигнал с выхода триггера 59 по5 ступает на вход элемента 93 ИЛИ, а с его выхода на блока задержки 61, как разрешающий сигнал.

Блок 19 управления обеспечивает режим чтения преобразовптеля 14 по сигналу с выхода блока дешифрации 54, при этом

одновибратор 60 выдает сигнал записи в устройство 16, затем чтения в устройство 16 и сигнал запрета, поступающий на второй вход элемента 93 ИЛИ, при записи в устройство 16, Сигнал записи поступает на вход элемента 92 ИЛИ, а чтения на вход элемента 94 ИЛИ.

Таким образом, обеспечивается возможность записи в устройство 16 не только результатов измерения с преобразователя 14, но и записи данных, хранящихся в памяти ЭВМ, например, результатов обработки измерений.

Выдача адреса в устройство 16 предусмотрена от счетчика 18 адреса. Адрес в него записывается с шины 20 данных при обращении к нему как к региструи по сигналу блока дешифрации 54, что не ограничивает зону адресации и следовательно объем устройства 16. Предусматривается возможность использования оставшейся свободной части устройства 16 для хранения результатов следующей серии измерений или как указывалось, данных от ЭВМ, например, результатов обработки. Для этого в регистр 50 программы записывается режим Блочная запись, который запрещает сброс счетчика 18 адреса по сигналу предварительного пуска очередной серии измерений и осуществляется их запись в оставшуюся свободную часть памяти.

Сигнал сброса счетчика 18 адреса вырабатывается одновибратором 72 по сигналу предварительного пуска и в режиме блочной записи он запрещается.

Если производится запись данных ЭВМ, адрес с выхода счетчика 18 адреса, может быть ЭВМ прочитан и произведена запись с начального адреса свободной зоны памяти. Адрес с выхода счетчика 18 адреса выходит на шину 20 данных при наличии управляющего сигнала с выхода блока дешифрации 54.

После записи измеренной входной аналоговой или цифровой информации производится ее чтение в программном обмене с ЭВМ. Кроме того, предусмотрена работа в режиме прерывания - по инициативе самого устройства с выдачей сигнала в ЭВМ по шине 24 прерываний.

Возможны два вида прерываний:

прерывание по концу цикла коммутации на выбранной группе каналов; сигналом прерывания является выходной сигнал узла 56 - КЦ;

прерывание по концу запрограммированного числа дискретизации; сигналом прерывания является сигнал конца счета.

Система обеспечивает регистрацию в устройство 16 как аналоговых, так и цифровых входных сигналов, образующих группу дискретных входов 17.1-17.N по числу каналов 1 регистрации. Эти входы подключаются непосредственно к устройству 16,

5 занимая часть его объема. Регистрация и чтение их производится одновременно с аналоговыми входными сигналами по тем же сигналам записи и чтения, поступающим из блока 19 управления,

0 Имеющийся в системе источник контрольного сигнала позволяет проводить тестирование, необходимое для проверки работоспособности всех каналов без выполнения ручных переключений контрольного

5 сигнала. Источник контрольного сигнала выполнен на преобразователе 44, управляемом от регистра 29 контрольного сигнала. Уровень контрольного сигнала в регистр 29 контрольного сигнала записывается с шины

0 20 данных ЭВМ под действием управляющего сигнала блока дешифрации 26. Преобразователь 44 может выдавать контрольный сигнал не только в виде постоянного уровня, но и линейно нарастающего напряжения. В

5 последнем случае регистр 29 контрольного сигнала работает в режиме счетчика, на один из входов которого подаются тактовые импульсы генератора 45 тактовых импульсов. Контрольный сигнал с выхода преобра0 зователя 44 подается на второй вход коммутатора 6 каждого канала 1 регистрации. Под воздействием управляющего сигнала, поступающего из блока 19 управления с выхода регистра 50 программ, третий ком5 мутатор 6 подключает контрольный сигнал на входе преобразователя 14 и в устройстве 16 фиксируется значение контрольного сигнала.

При обработке кода контрольного смг0 нала определяется составляющие погрешности и их максимальные значения сравниваются с допускаемыми значениями и определяется работоспособность системы по каналам,

5 В системе предусмотрен вывод информационного массива в виде таблиц или графиков на экран видеомонитора или на графопостроитель с использованием блока 46 отображения (фиг.З). Блок дешифрации

0 26 при соответствующем адресе на шине 21 адресов ЭВМ и наличии управляющих сигналов вырабатываетсигнал выбора блока 46 отображения, который разрешает работу блока дешифрации 95.

5 Блок дешифрации 95 под воздействием управляющих сигналов ввода или вывода, а также восьми последовательностей тактовых импульсов с выхода распределителя фаз 96 вырабатывает сигналы управления отдельными функциональными узлами и в зависимости от значений кода адреса шины 21 адресов ЭВМ и выдает ответный сигнал обмена с ЭВМ по шине 25 управления с задержкой относительно сигналов обращения ввода или вывода. Распределитель 96 фаз обеспечивает формирование восьми последовательностей тактовых импульсов, последовательно сдвинутых относительно друг друга, входным сигналом для него являются тактовые импульсы второго генератора 110.

При отсутствии обращения к видеопамяти 98 со стороны ЭВМ происходит автоматическое чтение данных из видеопамяти по адресу, который выдает мультиплексор 104. При автоматическом чтении видеопамяти 98 мультиплексор 104 выдает адрес, определяемый содержимым первого и второго счетчиков 105, 106 изображения. Первый счетчик 105 изображения представляет собой счетчик группы элементов изображения, обеспечивающий формирование текущего адреса группы элементов изображения, инкрементирование этого счетчика осуществляется от последовательности импульсов распределителя 96 фаз. Второй счетчик 106 строк изображения обеспечивает формирование текущего адреса строки изображения, инкрементирование его осуществляется выходным сигналом узла 107 синхросигналов, представляющим собой строчный гасящий импульс.

При обращении к видеопамяти 98 от ЭВМ запис.ь данных производится с внутренней шины данных по управляющему сигналу блока дешифрации 95. Внутренняя шина данных связана с шиной 20 данных ЭВМ через приемопередатчик 97. При этом режим автоматического чтения прерывается и запись данных в видеопамять 98 или чтение из нее происходит по адресам, поступающим на второй вход мультиплексора 104 и определяемым содержимым первого и второго регистров 101,102 изображения. Первый регистр 101 изображения представляет собой регистр/счетчик адреса группы элементов изображения, обеспечивающий запоминание адреса группы элементов, поступающего с внутренней шины данных по. сигналу блока дешифрации 95, второй регистр 102 изображения представляет собой регистр/счетчик адресе строки изображения, обеспечивающий запоминание адреса строки изображения, поступающего с внутренней шины данных по сигналу блока дешифрации 95, первый и второй регистры 101,102 изображения могут инкрементиро- ваться в определенном режиме в зависимости от кода, записанного в регистре 100 команд и состояний, по его выходным сигналам.

Переключение адресов мультиплексором 104 в режиме автоматического чтения и обращения от ЭВМ производится группой управляющих сигналов блока дешифрации 5 95. В автоматическом режиме чтения видеопамяти 98 производится фиксация ее данных в сдвиговом регистре 99 по сигналу блока дешифрации 95. Преобразование параллельного кода в последовательный осу0 ществляется сдвиговым регистром 99 под воздействием последовательности тактовых импульсов с выхода распределителя 96 фаз. Последовательность импульсов с выхода сдвигового регистра 99 представляет со5 бой видеосигналы, которые через узел 108, видеосигналов, обеспечивающее формирование сигналов управления лучами видеомонитора, проходят на видеомонитор через первую группу выходов 47.

0 ( Узел 107 синхросигналов обеспечивает формирование строчных и кадровых импульсов синхронизации, которые с его выхода также проходят на видеомонитор через первую группу выходов 47. Выходной сиг5 нал этого формирователя - сигнал гашения видеосигнала, представляющий собой дизъюнкцию сигналов строчного гасящего импульса и кадрового гасящего импульса, управляет регистром 100 команд и состоя0 ний и узлом 108, он также проходит на вход регистра 109 прерываний, а с его выхода на шину 24 прерываний при наличии разрешения прерывания регистра 100 команд и состояний. Схема 103 последовательного

5 интерфейса обеспечивает вывод данных на графопостроитель по каналу связи с ИРПС через преобразователь 112, преобразующий цифровые сигналы напряжения в токовые сигналы. С его выхода они проходят на

0 графопостроитель через вторую группу выходов 48. Тактовые импульсы поступают на схему 103 последовательного интерфейса с выхода второго генератора 110. Переключатель режимов 111 с помощью перемычек

5 обеспечивает установку необходимых режимов передачи схемы 103 последовательного интерфейса.

Формула изобретения Многоканальная система сбора и реги0 страции измерительной информации, содержащая генератор тактовых импульсов, блок дешифрации, два мультиплексора, первый компаратор, два одновибратора, блок отображения и N каналов регистрации

5 (где N - число групп аналоговых и дискретных входов), каждый из которых содержит аналого-цифровой преобразователь, буферное запоминающее устройство, счегчил адреса, блок коммутации, блок упр пения и программный усилитель причем адресные

входы буферного запоминающего устройства подключены к выходам счетчика адреса, отличающаяся тем, что, с целью расширения функциональных возможностей, ум&ньшения динамической погрешно- 5 сти, повышения быстродействия и надежности при регистрации аналоговых сигналов, в нее введены три компаратора, согласующий и инвертирующий усилители, два цифроаналоговых преобразователя, ре- 10 гистр способа запуска, регистр уровня запуска, регистр контрольного сигнала и блок элементов НЕ, а в каждый из N каналов регистрации введены два устройства выборки-хранения, три коммутатора, при этом 15 в каждом канале регистрации первая и вторая группы аналоговых входов подключены соответственно к информационным входам первого и второго устройств выборки-хранения, выходы которых соединены с инфор- 20 мационными входами соответственно первого и второго коммутаторов, выходы которых соединены между собой и подключены к первому информационному входу третьего коммутатора, выход которого сое- 25 динен с информационным входом программируемого усилителя, выход которого соединен с информационным входом аналого-цифрового преобразователя, информационный выход которого соединен с 30 информационным входом блока коммутации и первым информационным входом буферного запоминающего устройства, второй информационный вход которого подключен к группе дискретных входов ка- 35 нала регистрации, информационный вход- выход буферного запоминающего устройства соединен с информационным входом и выходом счетчика адреса и группой входов-выходов блока управления, пер- 40 вая группа входов которого соединена с адресным входом канала регистрации, вторая группа входов блока управления соединена с первой группой управляющих входов канала регистрации, первый вход блока уп- 45 равления соединен с входом внешнего тактирования канала регистрации, второй и третий входы блока управления соединены с выходами готовности соответственно ана- лого-цифрового преобразователя и буфер- 50 ного запоминающего устройства, первая группа выходов блока управления соединена с выходом прерываний канала регистрации,

вторая группа выходов блока управле- 55 ния соединена с управляющим входом программируемого усилителя, вход записи которого соединен ; первым выходом блока управления, третьи группа выходов которого соединена с адресными входами первого

и второго коммутаторов, второй и третий выходы блока управления соединены с управляющими входами соответственно первого и второго устройств выборки-хранения, четвертый, пятый, шестой, седьмой, восьмой и девятый выходы блока управления соединены соответственно с входами разрешения первого, второго, третьего коммутаторов, с входом пуска аналого-цифрового преобразователя, входами записи и чтения буферного запоминающего устройства, десятый, одиннадцатый, двенадцатый и тринадцатый выходы блока управления соединены соответственно с входами записи, чтения, счета и установки счетчика адреса, четвертый вход блока управления 1-го канала регистрации (I 1.N) соединен с 1-м выходом блока дешифрации, N+1-й, N+2-й, N+3-й выходы блока дешифрации соединены соответственно с входами записи регистра способа запуска, регистра уровня запуска и регистра контрольного сигнала, информационные входы которых соединены с информационными входами первого цифроаналогового преобразователя, с соединенными между собой группами входов- выходов блока управления N каналов регистрации и являются шиной данных системы,

первые информационные входы первого и второго компараторов соединены с выходом первого цифроаналогового преобразователя, второй информационный вход первого компаратора соединен с выходом согласующего усилителя, второй информационный вход второго компаратора соединен с выходом инвертирующего усилителя, входы согласующего и инвертирующего усилителей соединены с одним из аналоговых входов одного из каналов регистрации, первая группа входов блока дешифрации соединена с соединенными между собой адресными входами N каналов регистрации и является шиной адреса системы, вторая группа входов блока дешифрации соединена с соединенными между собой первыми группами управляющих входов N каналов регистрации и является шиной управления системы, первый и второй выходы регистра способа запуска соединены с управляющими входами соответственно первого и второго компараторов, выходы первого и второго компараторов соединены с первым и вторым информационными входами первого и второго мультиплексоров, адресные входы первого и второго мультиплексоров соединены с третьим и четвертым выходами регистра способа запуска, пятый и шестой выходы регистра способа запуска соединены с входами сброса первого и второго одновибраторов, выходы которых соединены с третьим и четвертым информационными входами первого и второго мультиплексоров, пятый информационный вход первого мультиплексора соединен с шиной внешнего пуска системы,

пятый информационный вход второго мультиплексора соединен с шиной внешне- го вторичного пуска системы, шестой информационный вход первого мультиплексора соединен с N+4-м выходом первого блока дешифрации, N+5-й выход которого соединен с пятыми входами блоков управления N каналов регистрации, выходы первого и второго мультиплексоров соединены с шестыми и седьмыми входами блоков управления N каналов регистрации, информационные входы первого и второго одновибраторов соединены с выходами третьего и четвертого компараторов, третьи синхровходы одновибраторов соединены между собой и с четырнадцатыми выходами блоков управления N каналов регистрации, первые группы входов третьего и четвертого компараторов соединены между собой вы- ходами блоков коммутации N каналов регистрации, вторая группа входов третьего компаратора соединена с выходами регистра уровня запуска и группой входов блока элементов НЕ, выходы которого соединены с второй группой входов четвертого компаратора, выходы регистра контрольного сигнала соединены с входами второго цифроаналогового преобразователя, выход которого соединен с информационными входами третьих коммутаторов N каналов

регистрации, счетный вход регистра контрольного сигнала соединен с выходом генератора тактовых импульсов и с восьмыми входами блоков управления N каналов регистрации,

группа информационных входов-выходов блока отображения соединена с шиной данных системы, группа адресных входов блока отображения соединена с шиной адресов системы, группа управляющих входов блока отображения соединена с шиной управления системы, управляющий вход блока отображения соединен с N+6-м выходом блока дешифрации, первая группа выходов блока отображения соединена с выходами прерываний N каналов регистрации и с шиной прерываний системы, первый выход блока отображения соединен с пятнадцатыми выходами блоков управления N каналов регистрации и является управляющим входом системы, вторая и третья группы выходов блока отображения являются соответственно выходом для подключения к видеомонитору системы и выходом для подключения к графопостроителю системы, первая и вторая группы аналоговых и группа дискретных входов N каналов регистрации являются соответственно 2N группами аналоговых и N группами дискретных входов системы, входы внешнего тактирования N групп каналов регистрации соединены между собой и подключены к входу внешнего тактирования системы, управляющие входы блоков коммутации N каналов регистрации являются вторыми группами управляющих входов N каналов регистрации.

;

т

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИГНАЛА ЗАПУСКА МНОГОКАНАЛЬНОЙ ИНФОРМАЦИОННО-ИЗМЕРИТЕЛЬНОЙ СИСТЕМЫ | 1994 |

|

RU2079880C1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

| Многоканальное устройство для ввода информации | 1988 |

|

SU1536369A1 |

| СПОСОБ ГЕОЭЛЕКТРОРАЗВЕДКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2006886C1 |

| УСТРОЙСТВО РЕГИСТРАЦИИ СТАТИЧЕСКИХ ТЕЛЕВИЗИОННЫХ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2054818C1 |

| УСТРОЙСТВО ДЛЯ СБОРА И ОБРАБОТКИ ДАННЫХ | 2002 |

|

RU2218597C2 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

Изобретение относится к вычислительной и информационно-измерительной технике и может быть использовано в автоматизированных системах регистрации быстропротекающчх процессов. Целью изобретения является расширение функциональных возможностей, повышение быстродействия и уменьшение динамической погрешности при регистрации аналоговых сигналов. Поставленная цель достигается тем, что система для сбора и регистрации измерительной информации содержит N каналов регистрации по числу групп аналоговых и дискретных ЁХЙДОВ, каждый из которых содержит два устройства выборки- хранения (УВХ), три коммутатора, программируемый усилитель,- АЦП, блок коммутации, буферное запоминающее устройство, счетчик адреса и блок управления, кроме этого система содержит четыре компаратора, два усилителя (согласующий, инвертирующий), два ЦАП, регистр способа запуска, регистр уровня запуска, ре гистр контрольного сигнала блок элементов НЕ,, блок дешифрации, два одновибратора, два мультиплексора, блок отображения, генератор тактовых импульссв, 9 ил.

Фие.1

Ǥl I5;l

&Ј

$ ,

И

пг)го&шэгмъ& подох JMjgacfc

. X -j

| g. } a | у j Й7

плпоешзя зз ncjO4Sn 3vyoa усузэим1п

ojtsfio QjOHhndQuuy og нпзкэс n(iHHO3KdaQDc

ляэкаэдае (онаЯапнно ио4и Ч

f e T

V | ГН

If

U

ЫПЛсдс ПОдОУЭКирЭ Ц

vx

И

и

U w цп-жд4 мчннажс/ддо

№Ш1

1783547

ЛшомбыО сигнад

и f

Фиг.7

физ,5

ппП.

/7

Л

Рог-Г

Ы2. №

КН5

ргв

КС

W

rs.

Л

L

J1

JL

нормальный v режим. ЬыБарки

кОиВейерныС резким Јьг5ор/а/

| Многоканальная система регистрации аналоговых процессов | 1981 |

|

SU951146A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-12-23—Публикация

1989-12-22—Подача