4

О со

о

О5 СП

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1987 |

|

SU1524054A1 |

| Устройство для контроля двоичных последовательностей | 1983 |

|

SU1116431A1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1995 |

|

RU2087030C1 |

| Устройство для контроля двоичной последовательности | 1983 |

|

SU1128259A1 |

| Генератор L-ичных последовательностей | 1986 |

|

SU1406586A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1185338A1 |

| Устройство для диагностирования цифровых объектов | 1989 |

|

SU1705829A1 |

| Устройство для контроля дискретных объектов | 1987 |

|

SU1594540A1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1996 |

|

RU2120136C1 |

| Многовходовой сигнатурный анализатор | 1987 |

|

SU1478219A1 |

Изобретение относится к вычислительной технике и может быть использовано в система.х тестового диагностирования цифровых устройств в качестве анализатора выходных реакций. Целью изобретения является повышение надежности анализатора и увеличение достоверности контроля. Анализатор сигнатур содержит регистр 3, разрядность Л которого равна степени образующего многочлена, и группу из М сумматоров 4 по модулю два, причем К. М Л , где К - число контролируемых входов анализатора. Принцип работы анализатора основан на алгоритме ускоренного деления многочленов. При /V К надежность анализатора достигается за счет существенного упрощения его конструкции. 6 ил.

фиг. г

Изобретение относится к 1 ычислитель- ной технике и может быть использовано в системах тестового диагностирования цифровых устройств в качестве анализатора выходных реакций проверяемого изделия.

Цель изобретения - повышение надежности анализатора и увеличение достоверности контроля.

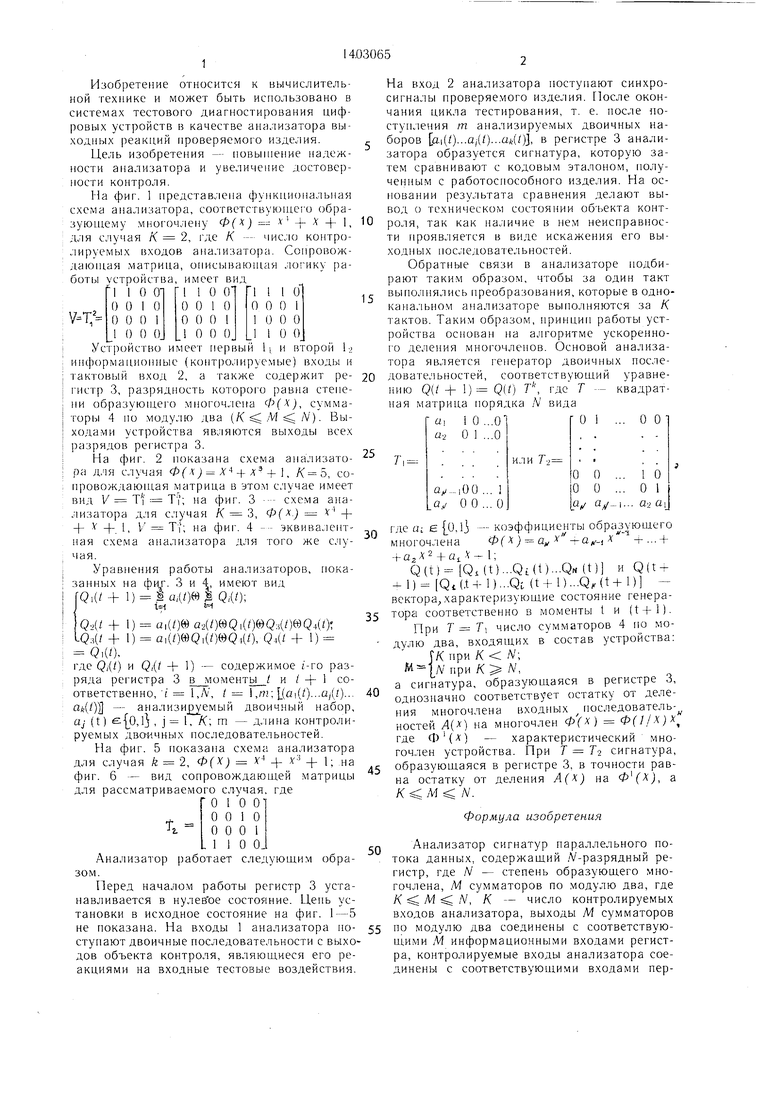

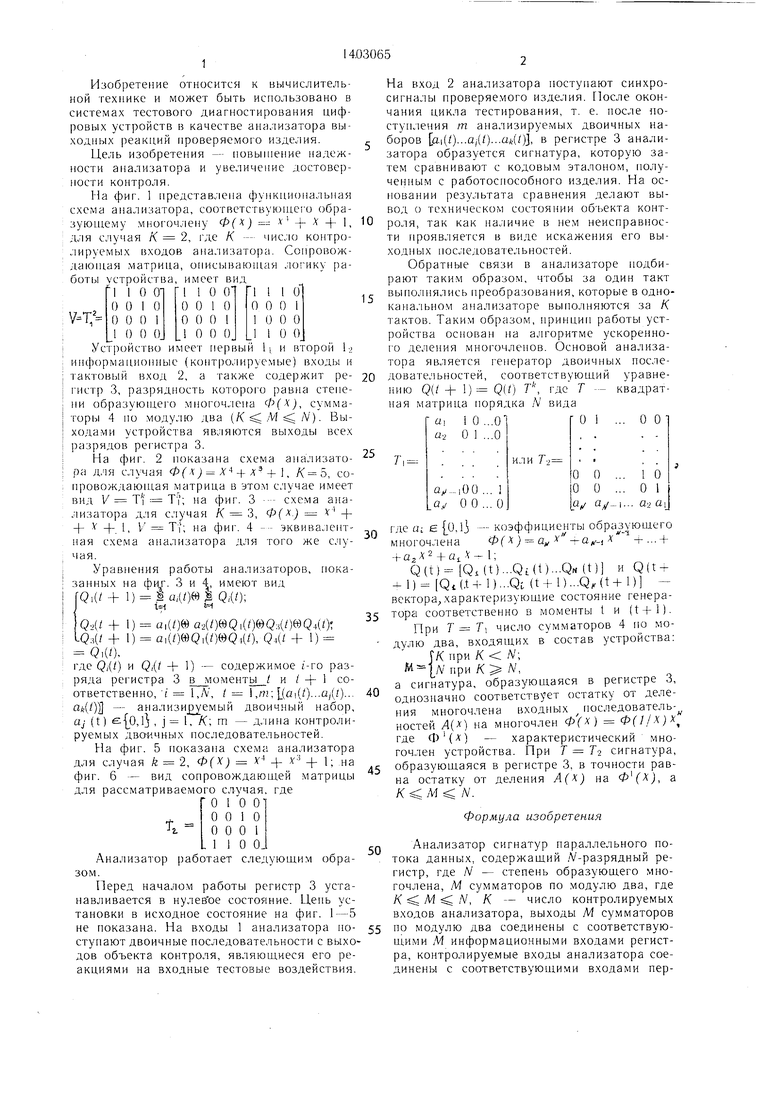

На фиг. 1 представлена функциональная схема а}1ализатора, соответствуюн1его образующему многочлену Ф() + + К для случая /( 2, где К -- число контро- „ шруемых входов анализатора. Сопровож- даюн1ая матрица, описываюн1ая логику работы устройства, имеет вид

Т.

информационные (контролируемые) входы и тактовый вход 2, а также содержит регистр 3, разрядность которог о равна степени образуюндего многоч„ 1ена ), сумматоры 4 но моду:1Ю два (). Выходами устройства являются выходы всех разрядов регистра 3.

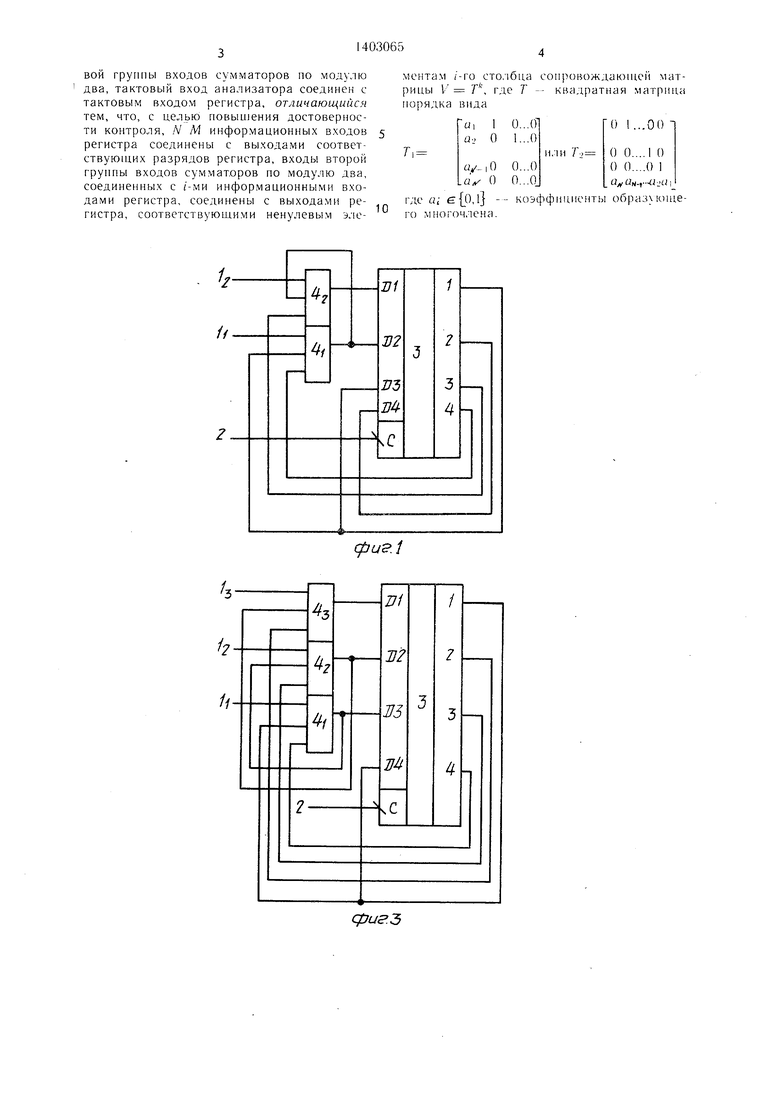

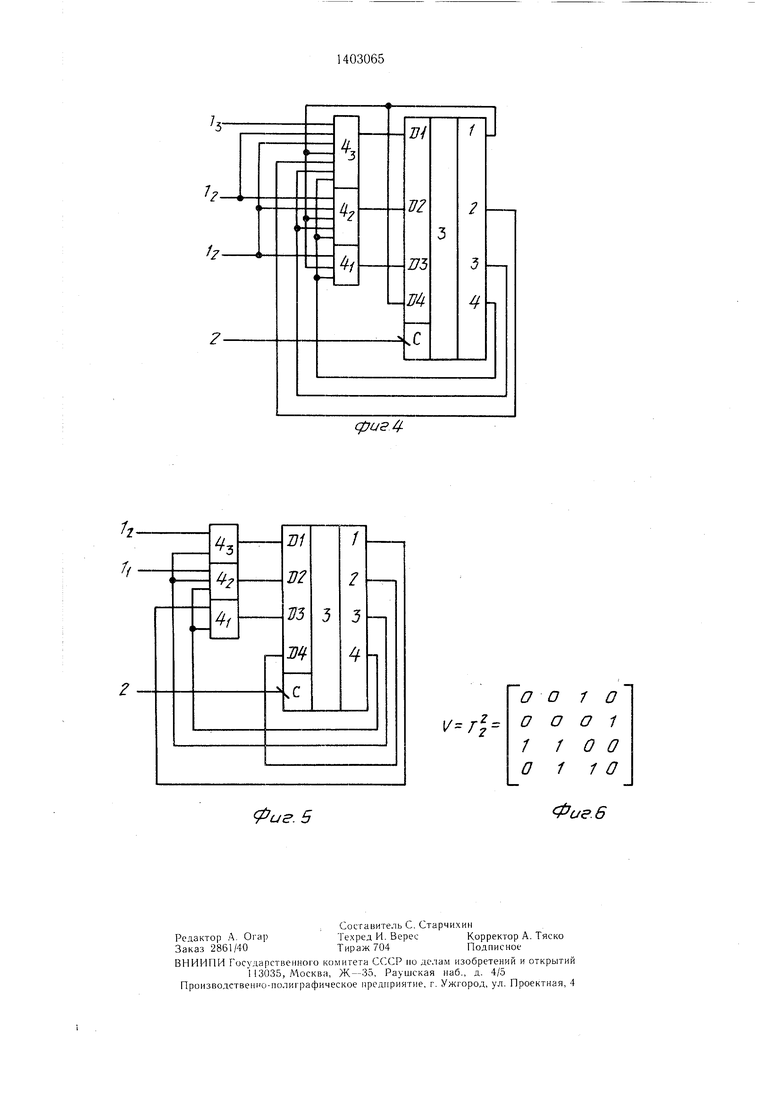

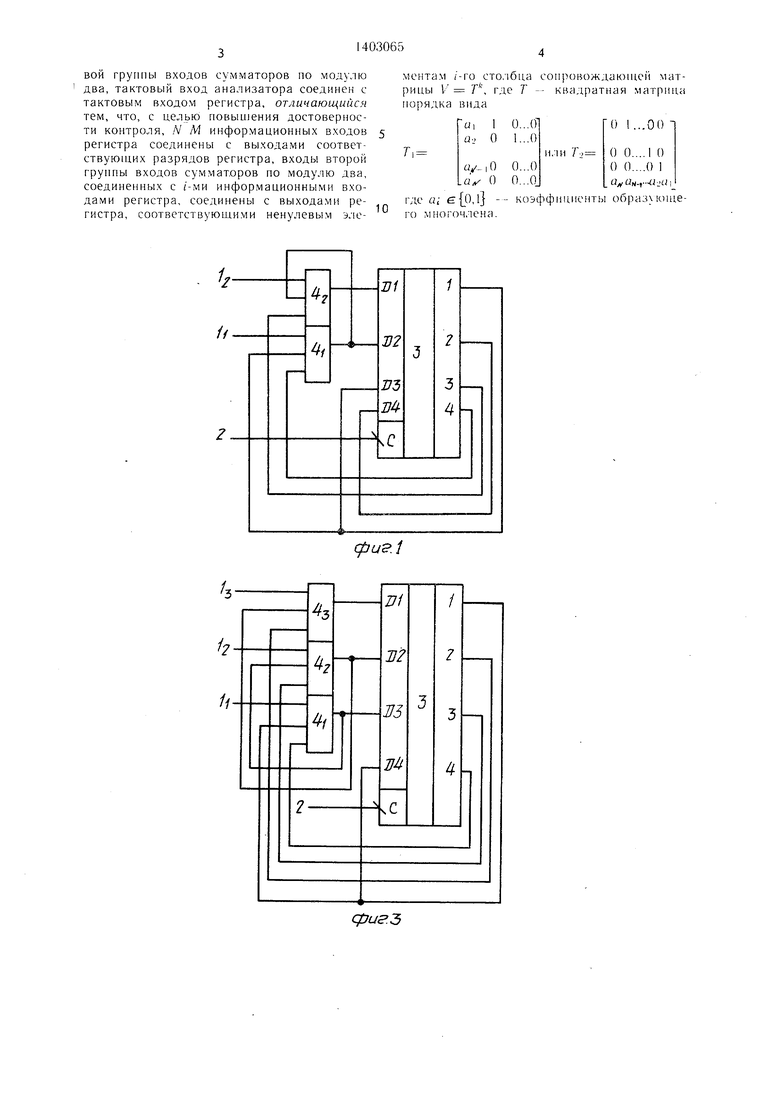

На фиг. 2 показана схема ана„чизато- ра д, 1я случая Ф(.() х + + l , со- провождаюншя матрица в этом случае имеет вид У Т : Т : ; на фиг. 3 - схема анализатора для случая К 3, Ф() Ч -f- +. 1, V TI; на фиг. 4 -- эквивалентная схема анализатора для того же случая.

Уравнения работы анализаторов, показанных на фиг. 3 и 4, имеют вид

ю,(/ + i) s o,(/)Q Q,(0;

1иw

Q-,(i -f 1) ai(/)® a2(0®Qi(0®Q3()QQ4(Ot LQ3(/ -f 1) a,(/)(-eQ,(/)©Q,(/), Q,(i + 1)

Qi(0.

где Q,(/) и Q,(/ + 1) - содержимое t-ro разряда регистра 3 .ioMeHTbi / и / + 1 соответственно,( 1,Л , / ,(t...a,(t)... (0 - анализи уемый двоичный набор, uj (t) 0,1} , j 1, /(; m - длина контролируемых дваичных последовательностей.

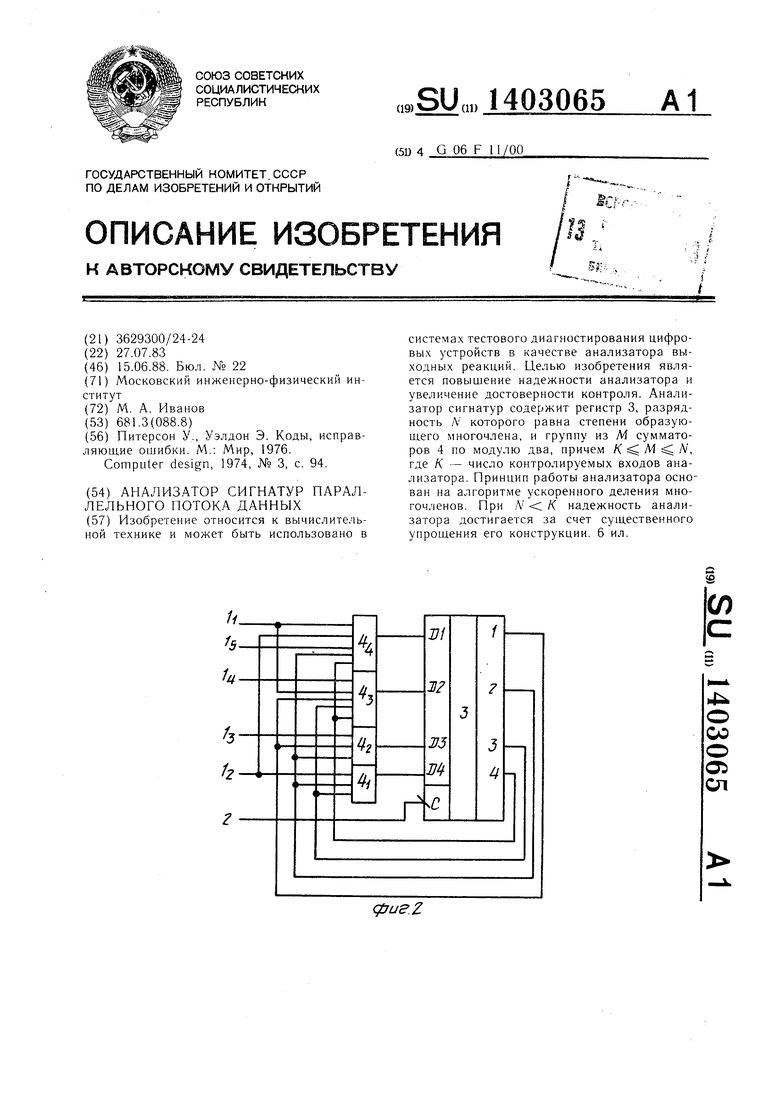

На фиг. 5 показана схема анализатора для случая fe 2, Ф() + + U на фиг. 6 - вид сопровождающей матрицы для рассматриваемого случая, где

О Го 01

0010

О О

О О OJ

Анализатор работает следующим образом.

Перед началом работы регистр 3 устанавливается в нулев ое состояние. Цепь установки в исходное состояние на фиг. 1-5 не показана. На входы 1 анализатора но- ступают двоичные последовательности с выходов объекта контроля, являющиеся его реакциями на входные тестовые воздействия.

0

На вход 2 анализатора ностунают синхросигналы проверяемого изделия. После окончания цикла тестирования, т. е. после поступления m анализируемых двоичных наборов a.(t)...aj(t)...ak(t}, в регистре 3 анализатора образуется сигнатура, которую затем сравнивают с кодовы.м эталоном, нолу- ченным с работоспособного изделия. На основании результата сравнения делают вывод о техническом состоянии об ьекта контроля, так как наличие в нем неисправности прояв;1яется в виде искажения его выходных последовательностей.

Обратные связи в анализаторе подбирают таким образом, чтобы за один такт выполнялись преобразования,которые в одно- канальном анализаторе выполняются за К тактов. Таким образом, нринцин работы устройства основан на алгоритме ускоренного деления многочленов. Основой анализатора является генератор двоичных последовательностей, соответствующий уравнению Q(t -|- 1) Q(/) 7, где Т - квадратная матрица порядка N вида

о. а-1

О ...О О 1 ...о

25

/,

или Т-1

Qy-,iOO... LO. О О ... О

0

5

0

5

где Ц; е {0,li - коэффициенты образующего

, / . v i t/;I

многочлена Ф() а ,А2

Q(tQ(t) Q,(t)...Qt(t)...QN (t) и ) Qi(.t+l)...Qu (t+l)...QHt+l) - вектора,характеризующие состояние генератора соответственно в моменты t и (t+1). При Т Т число сумматоров 4 по модулю два, входящих в состав устройства: JK при К Л ; при /О W,

М-а сигнатура, образуюнгаяся в регистре 3, однозначно соответствует остатку от деления многочлена входных носледователь- ностей Л() на многочлен Ф(х } Ф() , где Ф () - характеристический многочлен устройства. При Т Т сигнатура, образующаяся в регистре 3, в точности равна остатку от К М Л- .

деления А(Х) на Ф(), а

Формула изобретения

Анализатор сигнатур параллельного но- тока данных, содержащий /V-разрядный регистр, где N - степень образующего многочлена, М сумматоров по модулю два, где К М N, К - число контролируемых входов анализатора, выходы М сумматоров по модулю два соединены с еоответствую- щими М информационными входами регистра, контролируемые входы анализатора соединены с соответствующими входами первой группы входов сумматоров по модулю два, тактовый вход анализатора соединен с тактовым входом регистра, отличающийся тем, что, с целью повышения достоверности контроля. Л/ М информационных входов регистра соединены с выходами соответствующих разрядов регистра, входы второй группы входов сумматоров по модулю два, соединенных с /-ми информационными входами регистра, соединены с выходами регистра, соответствующими ненулевым эле/7- //

ментам /-го столбца сопровождающей матрицы V 7 , где порядка вида

квадратная матрица

О

0...0 1...0

О 1...00

Г|

О 0....1 О О 0....0 1 Uj аы.,-а2Ч I

су IО 1а О

где ai Q,l - коэффициенты образующего многочлена.

(ригЛ

Hi U2

лз

2

фиг.5

(иг.5

/IО О ГО

0О О 1

1Г О О О 1 1 О

Фиг. 6

| Питерсон У., Уэлдон Э | |||

| Коды, исправляющие ошибки | |||

| М.: Мир, 1976 | |||

| Computer design, 1974, № 3, с | |||

| Экономайзер | 0 |

|

SU94A1 |

Авторы

Даты

1988-06-15—Публикация

1983-07-27—Подача