Изобретение относится к вычислительной технике и может может испол зоваться в системах диагностирования цифровых объектов.

Цель изобретения - расширение функциональных возможностей анализатора за счет обеспечения одновременного контроля групп из ( многовходовых цифровых узлов.

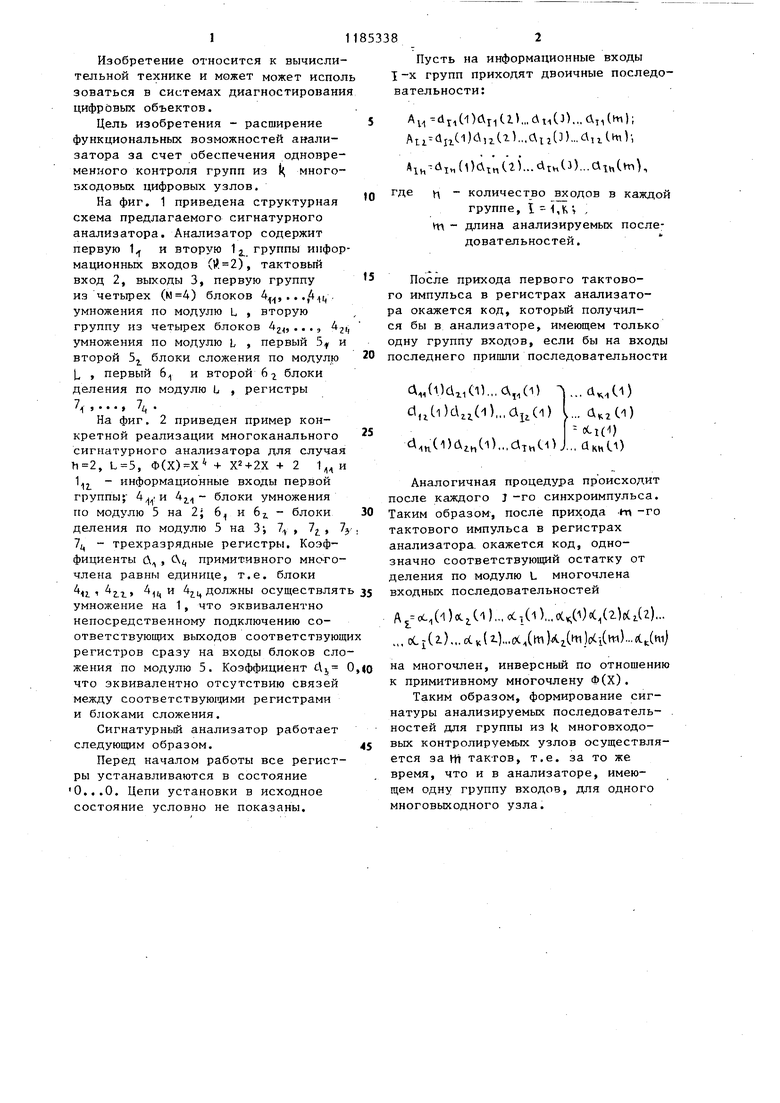

На фиг. 1 приведена структурная схема предлагаемого сигнатурного анализатора. Анализатор содержит первую 1 и вторую 1 группы информационных входов (1.2), тактовый вход 2, выходы 3, первую группу из четьфех () блоков 4, .. .,4,,t, . умножения по модулю L вторую группу из четырех блоков Дг ... ji, умножения по модулю i , первый 5 и второй 5 блоки сложения по модулю L , первый 6| и второй 6- блоки деления по модулю Ь , регистры

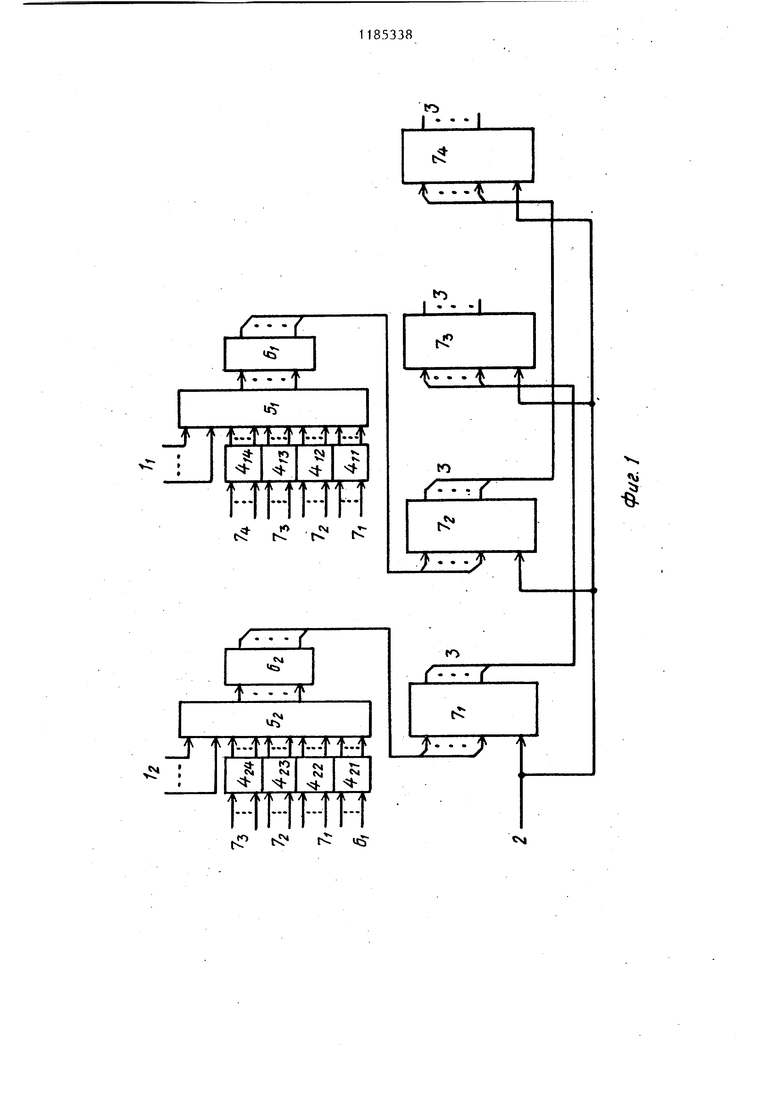

На фиг. 2 приведен пример конкретной реализации многоканального сигнатурного анализатора для случая , , Ф(Х)Х + X2+2X + 2 1 1., - информационные входы первой группы;- 4. и i блоки умножения по модулю 5 на 2; 6 и 6i - блоки деления по модулю 5 на 3; 7 , 7 - трехразрядные регистры. Коэффициенты ( , С примитивного много члена равны единице, т.е. блоки . ,4 должны осуществля умножение на 1, что эквивалентно непосредственному подключению соответствующих выходов соответствую регистров сразу на входы блоков сл жения по модулю 5. Коэффициент 4,, что эквивалентно отсутствию связей между соответствуюрдими регистрами и блоками сложения. Сигнатурный анализатор работает следующим образом. Перед началом работы все регист ры устанавливаются в состояние 0...0. Цепи установки в исходное состояние условно не показаны.

Пусть на информационные входы 1 -X групп приходят двоичные последовательности:

,(1)(r1(IK,.).„aт1();

Ati-dii(l)iizC-i),,.aii(),..d,j.tKi), (l)inUi...)...aiv,ChiK

количество входов в каждой

группе, I - 1|,ц; , m - длина анализируемых последовательностей.

После прихода первого тактового импульса в регистрах анализатора окажется код, которьй получился бы в анализаторе, имеющем только одну группу входов, если бы на входы последнего припши последовательности

a,,{)(i).,.a,,(i) Л...й,Д1)

Ciutl)Wj.(4),,,i,(l) I... а,гС1) -- oCi()

.n(l)Aij,(i),,,ciTttCOj,.,dKhU) Аналогичная процедура происходит после каждого J -го синхроимпульса. Таким образом, после прихода -HI -го тактового импульса в регистрах анализатора, окажется код, однозначно соответствующий остатку от деления по модулю L многочлена входных последовательностей А, осД)),.,),.,о((1)1(г)()С,(г)„. оС j(2L).,. сСк().,.(Х.,(№)л(ки)о(-,(м)...(.ь(п1) многочлен, инверсный по отношению к примитивному многочлену Ф(Х). Таким образом, формирование сигнатуры анализируемых последовательностей для группы из k многовходовых контролируемых узлов осуществляется за И1 тактов, т.е. за то же время, что и в анализаторе, имеющем одну группу входов, для одного многовькодного узла.

I I

| название | год | авторы | номер документа |

|---|---|---|---|

| Многовходовой сигнатурный анализатор | 1987 |

|

SU1478219A1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1995 |

|

RU2087030C1 |

| Запоминающее устройство с контролем информации | 1984 |

|

SU1288758A1 |

| Счетчик | 1986 |

|

SU1422403A1 |

| Сигнатурный анализатор | 1984 |

|

SU1264180A1 |

| Устройство для деления многочленов | 1986 |

|

SU1483461A1 |

| Генератор тестовых последовательностей | 1986 |

|

SU1388999A1 |

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| Генератор цифровых последовательностей | 1987 |

|

SU1513449A1 |

| Сигнатурный анализатор | 1987 |

|

SU1524054A1 |

МНОГОКАНАЛЬНЬЙ СИГНАТУРНЫЙ АНАЛИЗАТОР, содержащий N регистров, первый блок сложения по модулю L , первьй блок деления по модулю L , первую группу из N блоков умножения по модулю L , где N - степень многочлена, примитивного над полем GF(L) выходы первого блока сложения по модулю L соединены с входами первого блока деления по модулю L , выходы регистров через соответствующие блоки умножения по модулю L первой группы соединены с соответствующими группами входов первого блока сложения по модулю L , (м+1)-я группа входов которого является первой группой информационных входов анализатора, тактовые входы регистров объединены и явля --« ются тактовым входом анализатора, отличающийся тем, что, с целью расширения функциональных возможностей за счет обеспечения одновременного контроля группы из Jif многовходовьк цифровых узлов, в ненего введены групп из N блоков умножения по модулю ь , И-1 блоков деления по модулю L ,К-1 блоков сложения по модулю L , причем выходы I -го блюка сложения по модулю L (где и 2,К ,) соединены через соответствую11щй блок деления по модулю.с информационными входами k -(L+1)-ro регистра, выходы первого блока деления по модулю L ел соединены с информационными входами (-го регистра, м групп входов I -го с блока сложения по модулю L подключены через соответствующие блоки умножения по модулю Ь I -и группы к вькодам первых м -

HHRi-T

. Ю cvi - t r rO r

I-IHI-II-I

to t tc te

t I -I

r

« w

to

r

to

Г-- r

l-Z-T

«N

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Устройство для контроля двоичных последовательностей | 1983 |

|

SU1116431A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-10-15—Публикация

1984-01-04—Подача