Предлагаемое изобретение относится к вычислительной технике и может использоваться в системах защиты информации для контроля целостности программ и данных методом сигнатурного анализа, для шифрования информации методом гаммирования, для защиты программ от несанкционированного использования (режим электронного ключа).

Известен многоканальный сигнатурный анализатор, содержащий регистры, блок сложения, блок деления и блоки умножения. Характер обратных связей в устройстве определяется видом образуемого многочлена (Авторское свидетельство СССР N 1116431, кл. G 06 F 11/12, БИ N 36, 1984).

Данное устройство обладает низкой достоверностью при работе в режиме контроля целостности информации, а также ограниченной областью использования - контроль цифровых объектов.

Наиболее близким по технической сущности и по достигаемому эффекту к предлагаемому является устройство, содержащее последовательно соединенные генератор входных воздействий и блок деления многочленов, который при подключении к одному из блоков сложения 7 дополнительной группы входов может выполнять функции формирователя сигнатур. Характер обратных связей в этом формирователе сигнатур определяется видом образующего многочлена (Авторское свидетельство СССР N 1406586, кл. G 06 F 11/12, БИ N 24, 1988).

Данное устройство также обладает низкой достоверностью при работе в режиме контроля целостности программ и данных, ограниченная область использования - контроль цифровых объектов.

Предлагаемое устройство обладает высокой достоверностью не только при анализе выходных последовательностей контролируемых цифровых объектов, но и в режиме контроля целостности программ и данных. Расширяется класс решаемых задач за счет появления возможности работы в режиме генератора гаммы шифра и электронного ключа.

Объект приобретает новые свойства за счет того, что в сигнатурный анализатор, содержащий последовательно соединенный генератор входных воздействий и первый формирователь сигнатур, выходы которого образуют группу информационных выходов анализатора, дополнительно введены второй формирователь сигнатур, блок управления, формирователь серии импульсов, группу элементов И и элемент ИЛИ, выход которого соединен с тактовым входом первого формирователя сигнатур, входы сброса формирователей сигнатур, тактовые входы второго формирователя сигнатур, формирователя серии импульсов и генератора входных воздействий, вход запуска формирователя серии импульсов подключен к соответствующим выходам блока управления. Группа информационных входов устройства подключена к группе информационных входов генератора входных воздействий и через соответствующие элементы И группы ко второй группе информационных входов первого формирователя сигнатур. Три входа режима анализатора, входы считывания, записи и сброса подключены к соответствующим входам блока управления.

Особенностью предлагаемого анализатора является перестраиваемая структура первого формирователя сигнатур, которая позволяет повысить достоверность при контроле целостности информации и криптографическую стойкость при шифровании методом гаммирования. Первое из перечисленных свойств достигается за счет максимального усложнения процедуры определения последовательности, имеющей заданную сигнатуру. Второе - за счет усложнения структуры формируемой псевдослучайной последовательности.

Изменение структуры работы первого формирователя сигнатур осуществляется под управлением формирователя серии импульсов и элемента ИЛИ. Предлагаемый анализатор по своей сути является устройством ввода/вывода, подключаемым к персональному компьютеру типа IBM PC. Указанное подключение обеспечивает блок управления, реализуя запрашиваемую функцию.

Второй формирователь сигнатур функционирует только при установке исходного состояния регистров генератора входных воздействий и первого формирователя сигнатур. В рабочем режиме содержимое регистра второго формирователя сигнатур определяет характер обратных связей первого формирователя сигнатур. Последовательное соединение второго формирователя сигнатур, генератора входных воздействий и первого формирователя сигнатур при установке начального состояния устройства обеспечивает преобразование ключевой информации (содержимого специального файла) в код начального состояния генератора входных воздействий и первого формирователя сигнатур и вектора обратных связей первого формирователя сигнатур. Такая процедура инициализации исключает возможность определения по ключевой информации алгоритма формирования сигнатуры или алгоритма формирования гаммы шифра, что дополнительно увеличивает соответственно достоверность контроля или криптографическую стойкость устройства.

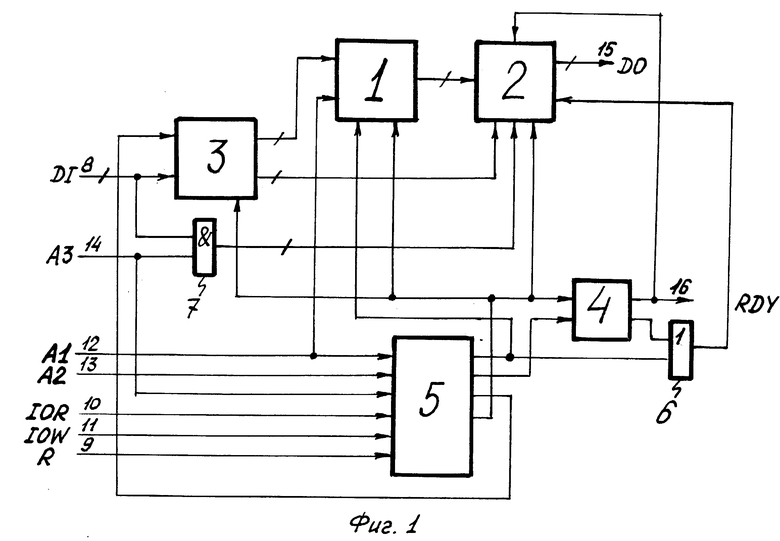

Многоканальный сигнатурный анализатор (МСА) (фиг. 1) содержит генератор 1 входных воздействий, первый 2 и второй 3 формирователи сигнатур (ФС), формирователь 4 серии импульсов блок 5 управления, элемент ИЛИ 6, группу 7 элементов И, имеет группу информационных 8 входов DI (Data Input), вход 9 сброса R (Reset), вход 10 чтения IOR (Input Output Read), выход 11 записи IOW (Input Output Write), три входа 12-14 режима A1, A2, A3, группу информационных 15 выходов DO (Data Output), выход 16 готовности RDY (Ready).

За МСА закрепляется три адреса A1, A2, A3. При появлении на шине адреса PC кода одного из этих адресов селектор адреса (на фиг. 1 не показан) формирует сигнал лог. "1" на соответствующем входе режима МСА.

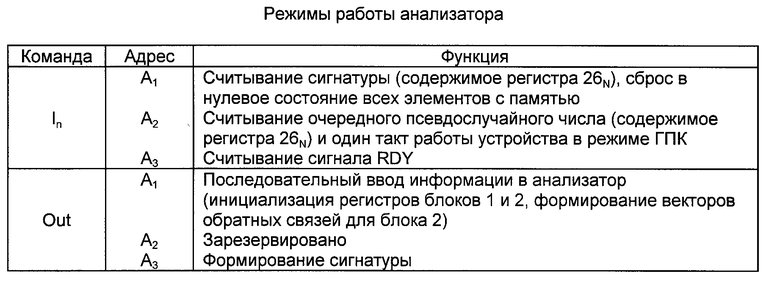

На фиг. 2 показан пример реализации блока 5 управления, который содержит формирователь 17 импульсов (последовательно соединенные двухвходовой элемент И и элемент задержки), элементы И 18-20, элемент ИЛИ-НЕ 21, элементы ИЛИ 22 и 23.

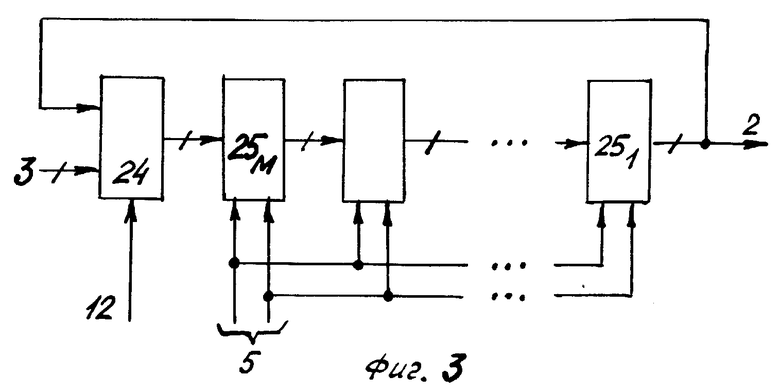

На фиг. 3 показан пример реализации генератора 1 входных воздействий, который содержит мультиплексор 24 и М регистров 251 - 25М, где М - длина управляющего входного воздействия.

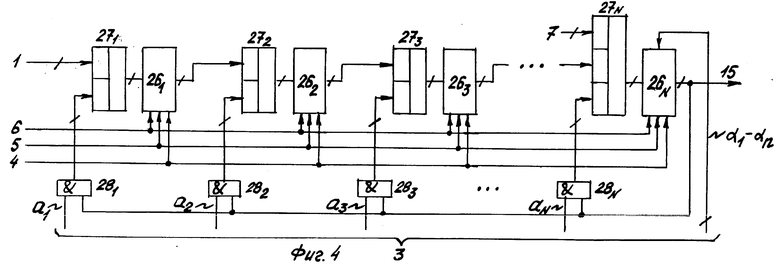

На фиг. 4 показан пример реализации первого формирователя 2 сигнатур, который содержит N регистров 261 - 26N, где N - степень образующего многочлена, разрядность регистров - слово или двойное слово, сумматоры 271 - 27N, группы 281 - 28N элементов И.

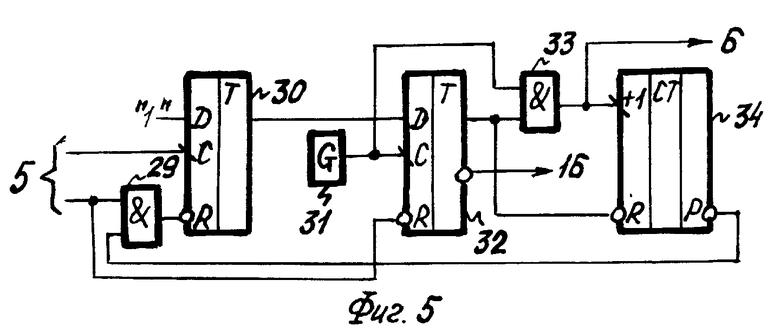

На фиг. 5 показан пример реализации формирователя 4 серии импульсов, который содержит элемент И 29, первый триггер 30, генератора 31 импульсов, второй триггер 32, элемент И 33, счетчик 34, модуль которого выбирается равным, например, разрядности регистров 26.

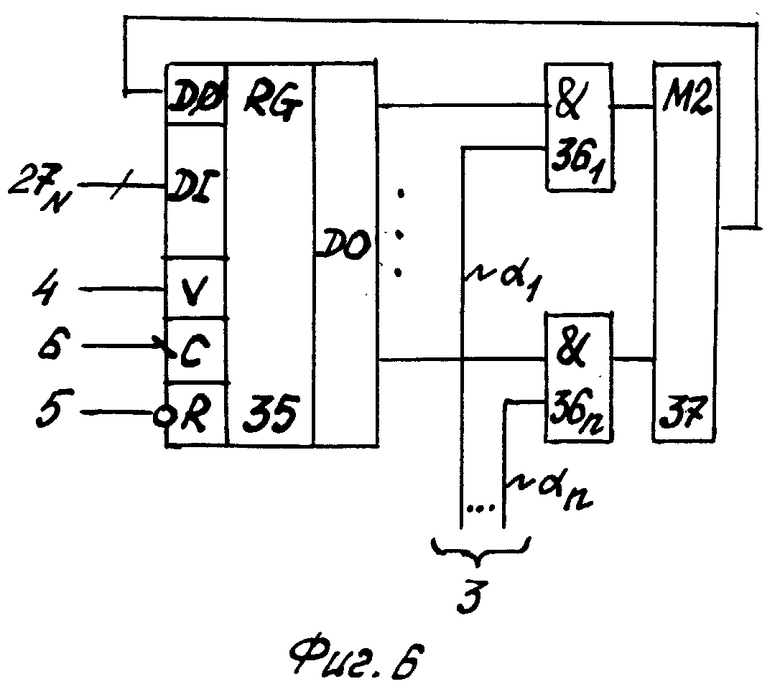

На фиг. 6 показан пример реализации регистра 26N, который содержит регистр 35 сдвига, группу элементов И 36 и сумматор 37 по модулю два.

Группа 8 информационных входов анализатора подключается к соответствующим линиям шины данных IBM PC (в дальнейшем просто РС). Вход 9 сброса анализатора подключается к линии сигнала системного сброса, входы чтения 10 и записи 11 - к линиям сигналов чтения из внешнего устройства (ВУ) и записи во внешнее устройство шины управления РС. Входы режима 12, 13, 14 подключены к выходам селектора адреса, который в свою очередь подключен к соответствующим линиям шины адреса РС. Группа 15 информационных выходов анализатора и выход сигнала 16 готовности подключены к соответствующим линиям шины данных РС через элементы с третьим состоянием (на фиг. 1 не показаны).

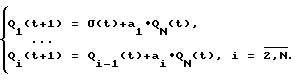

Анализатор работает следующим образом. При поступлении сигнала системного сброса на вход 9 анализатора все элементы с памятью устанавливаются в нулевое состояние. Все остальные функции реализуются программно по командам in (ввод) и out (вывод) в соответствии с таблицей.

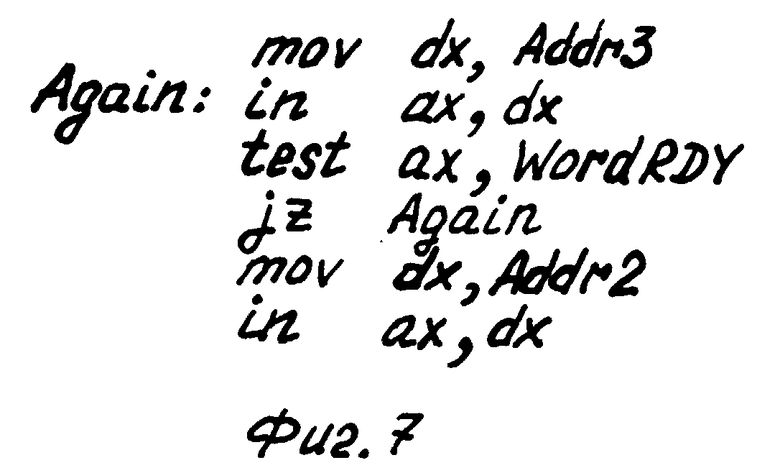

Например, в результате выполнения последовательности команд, приведенной на фиг. 7, в регистр АХ процессора будет считан из устройства шестнадцатиразрядный псевдослучайный код, а в регистре 26N будет сформирован следующий код, который в свою очередь может быть считан аналогичным образом.

Инициализация регистров и задание векторов обратных связей формирователя 2 сигнатур. В этом режиме блоки 3, 1 и 2 образуют последовательную сдвиговую структуру, в которую по сигналам 11 (A1=1, A2=A3=0) со входов 8 вводится информация из специального ключевого файла. При этом формирователь 3 работает в соответствии с фиксированными обратными связями, обратные связи же формирователя 2 динамически изменяются по мере изменения кода на соответствующих выходах формирователя 3, подключенных к входам режима формирователя 2.

После поступления всей ключевой информации в формирователе 3, который в дальнейшем работает только в режиме хранения, будет сформирован код обратных связей для формирователя 2. Коды в регистрах генератора 1 и формирователя 2 будут рассматриваться как начальное состояние соответствующих блоков при дальнейшей работе либо в режиме формирования сигнатуры, либо в режиме генерации псевдослучайных кодов.

Данная процедура преобразования ключевой информации позволяет скрыть от пользователя используемый принцип формирования сигнатуры или псевдослучайной последовательности.

Формирование сигнатуры. При контроле целостности информации каждое слово контролируемой последовательности после обнаружения факта готовности анализатора (RDY= 1) подается на входы 8 в сопровождении импульса записи 11 (A1= A2= 0, A3= 1). После обработки всех слов последовательности из регистра 26N формирователя 2 по сигналу чтения 10 (A1=1, A2=A3=0) считывается сигнатура контролируемой последовательности слов, после чего эта сигнатура сравнивается с эталонной. По результатам сравнения делается вывод о наличии или отсутствии искажений в анализируемой последовательности.

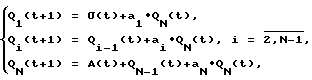

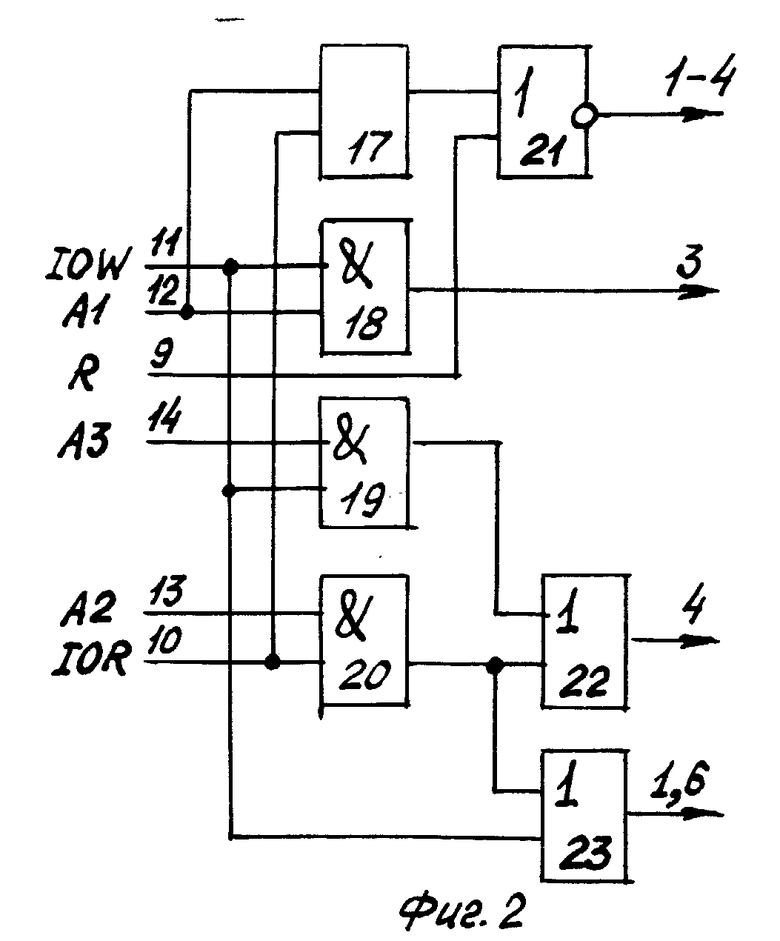

Рассмотрим более подробно один такт работы формирователя 2, особенностью которого является перестраиваемая структура. В первой половине такта все регистры 26 работают в режиме параллельной загрузки информации с выходов соответствующего сумматора 27. Уравнения работы в этом случае можно записать следующим образом:

где σ(t) - очередной символ управляющей последовательности с выхода генератора 1;

Qi(t) и Qi(t+1) - содержимое i-го регистра формирователя 2 соответственно в моменты времени t и t+1,

[a1 a2. . . ai...aN] - первый вектор обратных связей (ai - коэффициенты образующего многочлена Ф(х) степени N);

A(t) - очередное слово контролируемой последовательности.

Во второй половине такта работает только регистр 26N, который превращается в сдвиговый регистр с линейными обратными связями в соответствии с видом образующего многочлена ϕ(x) степени n ([α1α2...αj...αn] - второй вектор обратных связей). Перестройка структуры формирователя осуществляется под воздействием блока 4, который формирует серии импульсов сдвига для регистра 26N, а сигналом 16 подтверждения выдачи серии импульсов блокирует работу регистров 261 - 26N-1 и переводит регистр 26N в режим сдвига.

Генерация псевдослучайных кодов. Считывание очередного псевдослучайного кода осуществляется по сигналу 10 чтения (A1=A3=0, A2=1) после обнаружения факта готовности устройства (см. фиг. 7).

Уравнения работы блока 2 в первой половине такта имеют вид

Поступление информации со входов 8 блокируется сигналом A3=0, поступающим на входы элементов И 7. Логика работы блока 2 во второй половине такта аналогична имевшей место в режиме формирования сигнатуры.

Таким образом при работе устройства в режиме формирования сигнатуры наличие процедуры преобразования ключевой информации в код начального состояния блоков 1, 2 и в вектора обратных связей, а также наличие перестраиваемой структуры блока 2 позволяет повысить достоверность контроля за счет максимального усложнения процесса поиска цифровой последовательности, имеющей заданную сигнатуру. Указанный факт практически исключает ситуацию, когда будет пропущено умышленное искажение защищаемой информации.

Наличие указанной процедуры преобразования ключевой информации в режиме генерации псевдослучайных кодов позволяет использовать предлагаемое устройство при решении задач криптографической защиты информации в качестве источника гаммы шифра, а при решении задач защиты программ от несанкционированного использования в качестве электронного ключа.

Наличие перестраиваемой структуры блока 2 в режиме ГПК позволяет усложнить структуру формируемой последовательности, что дополнительно повышает криптостойкость алгоритма шифрования.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1998 |

|

RU2133057C1 |

| Запоминающее устройство с контролем информации | 1984 |

|

SU1288758A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1246098A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1451781A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1354195A1 |

| Сигнатурный анализатор | 1983 |

|

SU1223230A1 |

| Сигнатурный анализатор | 1984 |

|

SU1264180A1 |

| Устройство для контроля хода микропрограмм | 1990 |

|

SU1728865A1 |

| Сигнатурный анализатор | 1983 |

|

SU1180896A1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1995 |

|

RU2087030C1 |

Изобретение относится к вычислительной технике и может использоваться в системах защиты информации для контроля целостности программ и данных методом сигнатурного анализа, для шифрования информации методом гаммирования, для защиты программ от несанкционированного использования (режим электронного ключа). Анализатор по своей сути является устройством ввода-вывода, подключаемым к персональному компьютеру типа IBM PC. Использование данного изобретения позволяет повысить достоверность при контроле целостности информации и криптографическую стойкость при шифровании методом гаммирования, что является техническим результатом. Устройство содержит генератор входных воздействий, первый формирователь сигнатур, второй формирователь сигнатур, формирователь серии импульсов, блок управления, элемент ИЛИ, группу элементов И. 7 ил., 1 табл.

Многоканальный сигнатурный анализатор, содержащий два формирователя сигнатур, элемент ИЛИ, группу элементов И, при этом первая группа входов элементов И образует группу информационных входов анализатора, группа выходов элементов И подключена к первой группе информационных входов первого формирователя сигнатур, вторые входы элементов И объединены, отличающийся тем, что он дополнительно содержит генератор входных воздействий, блок управления и формирователь серии импульсов, первый выход которого подключен к управляющему входу первого формирователя сигнатур и образует выход готовности анализатора, вторая группа информационных входов первого формирователя сигнатур подключена к первой группе одноименных выходов второго формирователя сигнатур, вторая группа информационных выходов которого подключена к группе одноименных входов генератора входных воздействий, группа информационных выходов которого подключена к третьей группе одноименных входов первого формирователя сигнатур, группа информационных входов второго формирователя сигнатур подключена к группе одноименных входов анализатора, первый вход блока управления объединен с управляющим входом генератора входных воздействий и образует первый вход задания режима анализатора, второй вход блока управления образует второй вход задания режима анализатора, третий вход блока управления подключен к вторым входам элементов И группы и образует третий вход задания режима анализатора, четвертый, пятый и шестой входы блока управления образуют соответственно входы чтения, записи и сброса анализатора, первый выход блока управления соединен с первым входом элемента ИЛИ и тактовым входом генератора входных воздействий, второй выход блока управления соединен с входом запуска формирователя серии импульсов, второй выход которого соединен с вторым входом элемента ИЛИ, третий выход блока управления соединен с тактовым входом второго формирователя сигнатур, четвертый выход блока управления соединен с входами сброса первого и второго формирователей сигнатур, генератора входных воздействий и формирователя серии импульсов, выход элемента ИЛИ соединен с тактовым входом первого формирователя сигнатур, группа информационных выходов которого образует группу одноименных выходов анализатора.

| Многоканальный сигнатурный анализатор | 1989 |

|

SU1797118A1 |

| Центрифуга для очистки смазочного масла | 1958 |

|

SU116431A1 |

| Сигнатурный анализатор | 1989 |

|

SU1624455A1 |

| Сигнатурный анализатор | 1989 |

|

SU1631543A1 |

| Многоканальный сигнатурный анализатор | 1990 |

|

SU1714605A1 |

| Генератор L-ичных последовательностей | 1986 |

|

SU1406586A1 |

Авторы

Даты

1998-10-10—Публикация

1996-11-22—Подача