со

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный умножитель частоты следования импульсов | 1983 |

|

SU1150743A1 |

| Адаптивный умножитель частоты следования импульсов | 1984 |

|

SU1202047A2 |

| Адаптивный умножитель частоты следования импульсов | 1989 |

|

SU1690182A1 |

| Устройство для программного счета изделий | 1985 |

|

SU1365103A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 2023 |

|

RU2798746C1 |

| Реверсивный счетчик в избыточном коде | 1986 |

|

SU1411917A1 |

| Устройство для автоматического адресования объектов | 1979 |

|

SU867819A1 |

| Устройство для программного регулирования | 1988 |

|

SU1524024A2 |

| Устройство для сопряжения линии связи с приемником информации | 1985 |

|

SU1305694A1 |

| ОБНАРУЖИТЕЛЬ КОМБИНАЦИИ ДВОИЧНЫХ СИГНАЛОВ | 1996 |

|

RU2096822C1 |

Изобретение относится к импульсной технике и может быть использовано в измерительной технике, автоматике и телемеханике. Цель изобретения - расширение функциональных возможностей устройства - достигается за счет автоматической установки коэффициента (К) умножения, а также исключения

Ш

Р4

м

L48/ Д2 В2 «

вз

KI, В1,

/7

18,1 rr-t /3,2 .у-,

-4 D-tl5}-cbty

-Lw jLfOf

-WiS

s

ш

iO

ошибочного перехода на другой К при больших К .умножения. Устройство содержит элементы 1 и 2 задержки, входную шину 3, элементы И-НЕ 4, 5 и 27, , элемент И 6, элементы ИЛИ 7, 8, счетчики 9 и 2А импульсов, преобразователь 10 код-напряжение, регулируемую линию задержки 11, элемент ИЛИ-НЕ 12, инверторы 13 и J4, выходную шину 15, многоотводную линию задержки 16, коммутатор 17, интегрирующие цепочки из

1

Изобретение относится к импульсно технике и может быть использовано в .измерительной технике, автоматике и телемеханике.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения автоматической установки коэффициентов умножения, а также за счет исключения оши- бочного перехода на другой коэффициент при больших коэффициентах умножения, что позволяет расширить диапазон коэффициентов умножения частоты.„

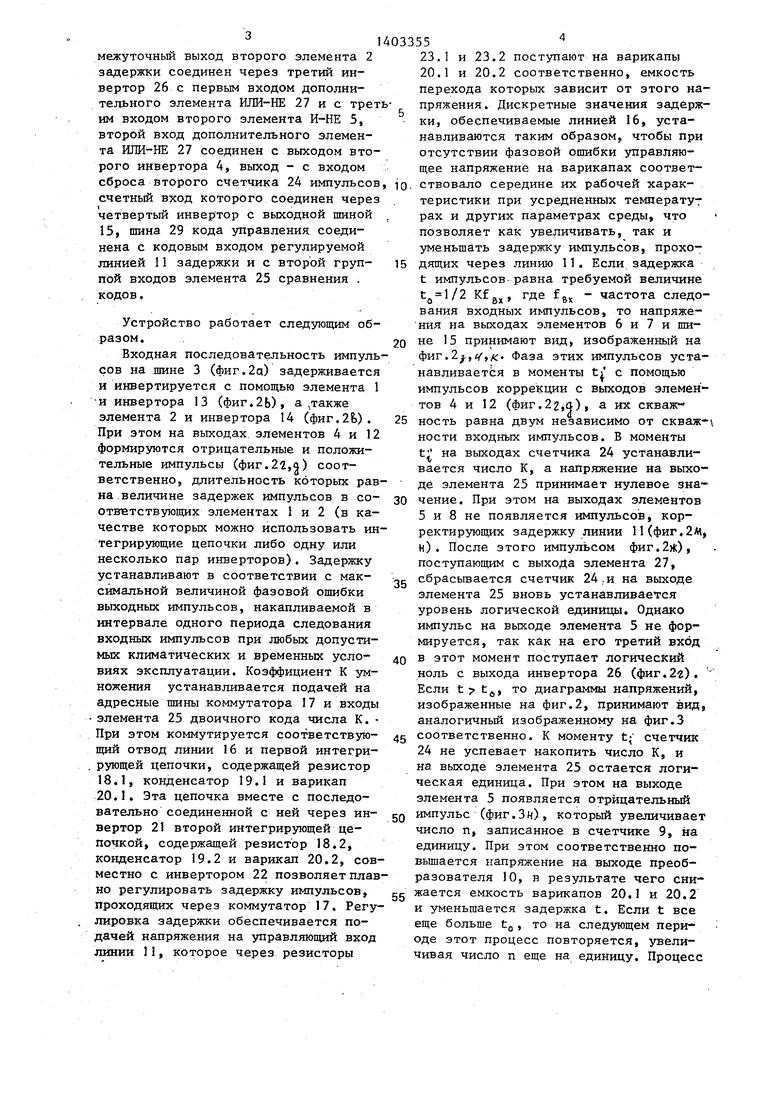

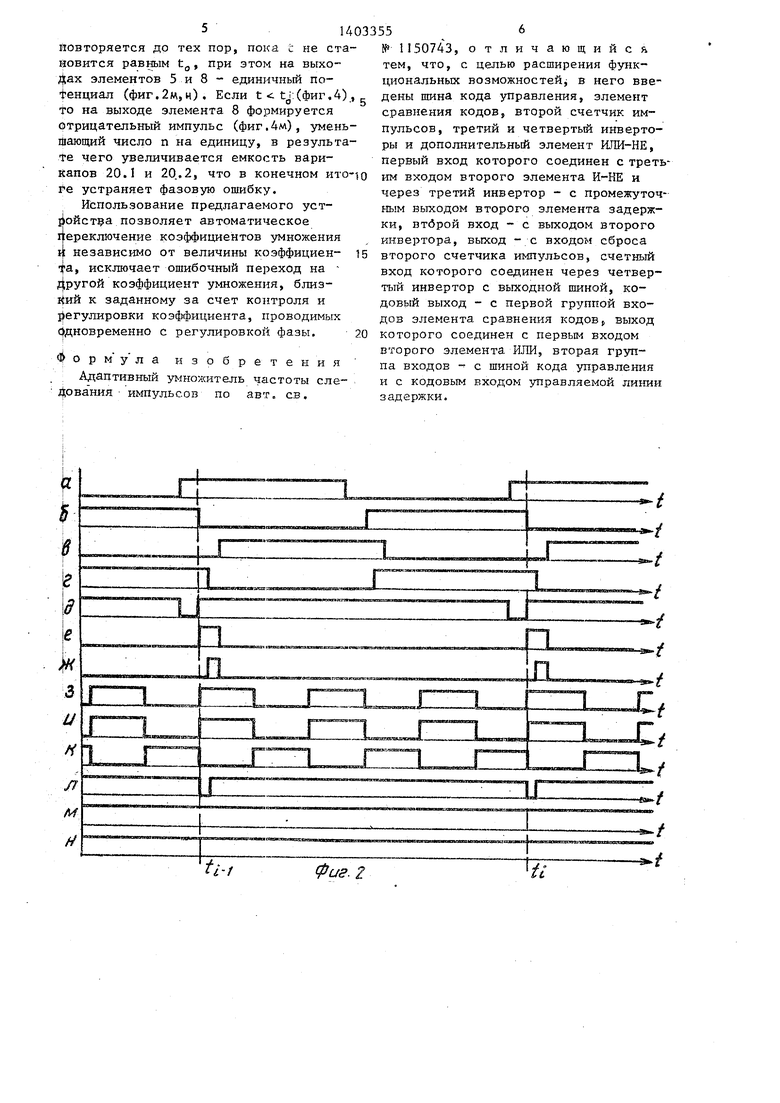

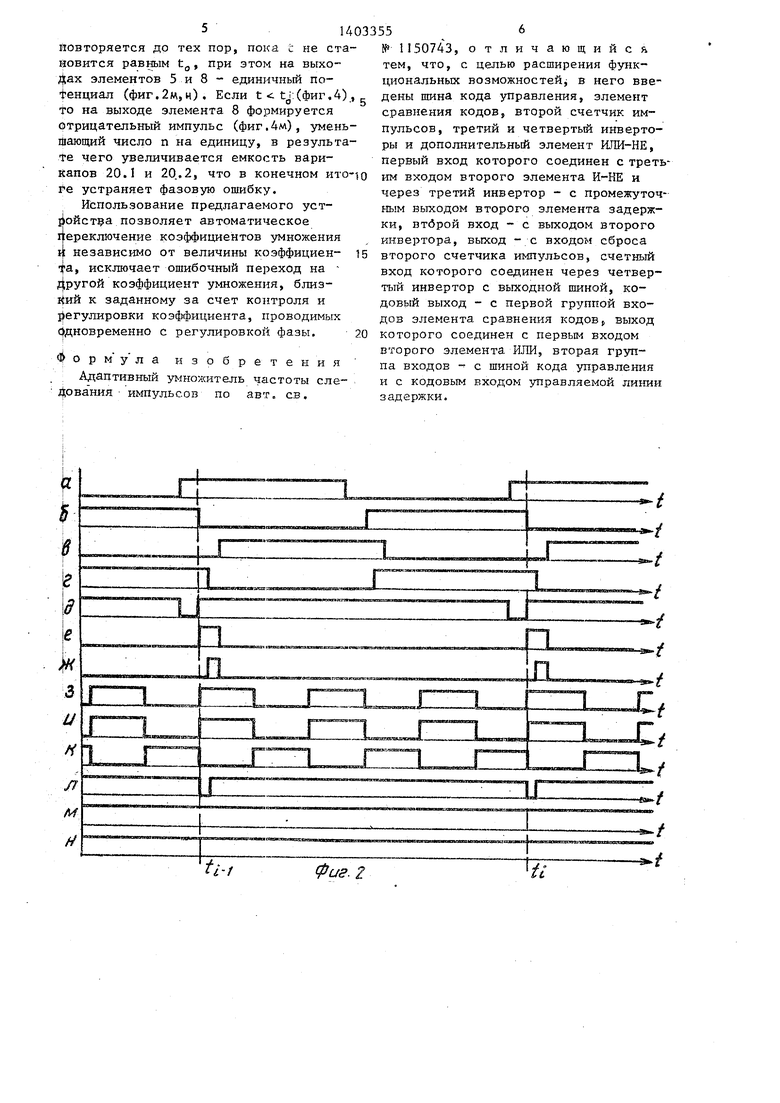

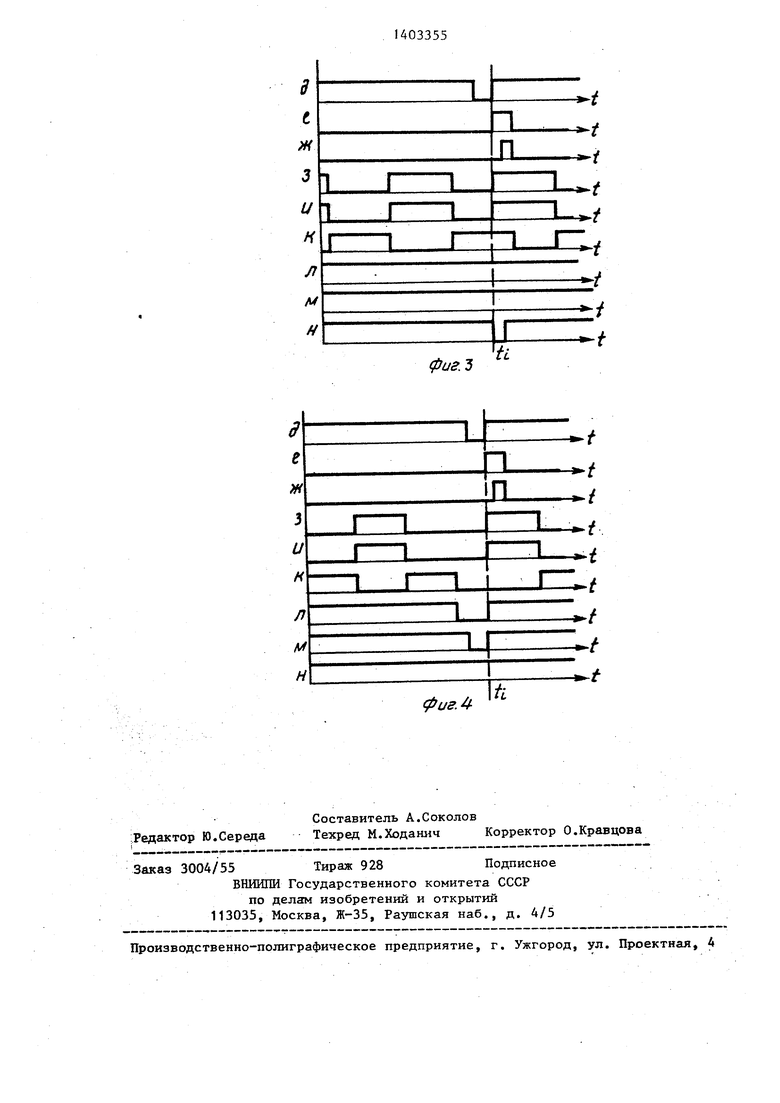

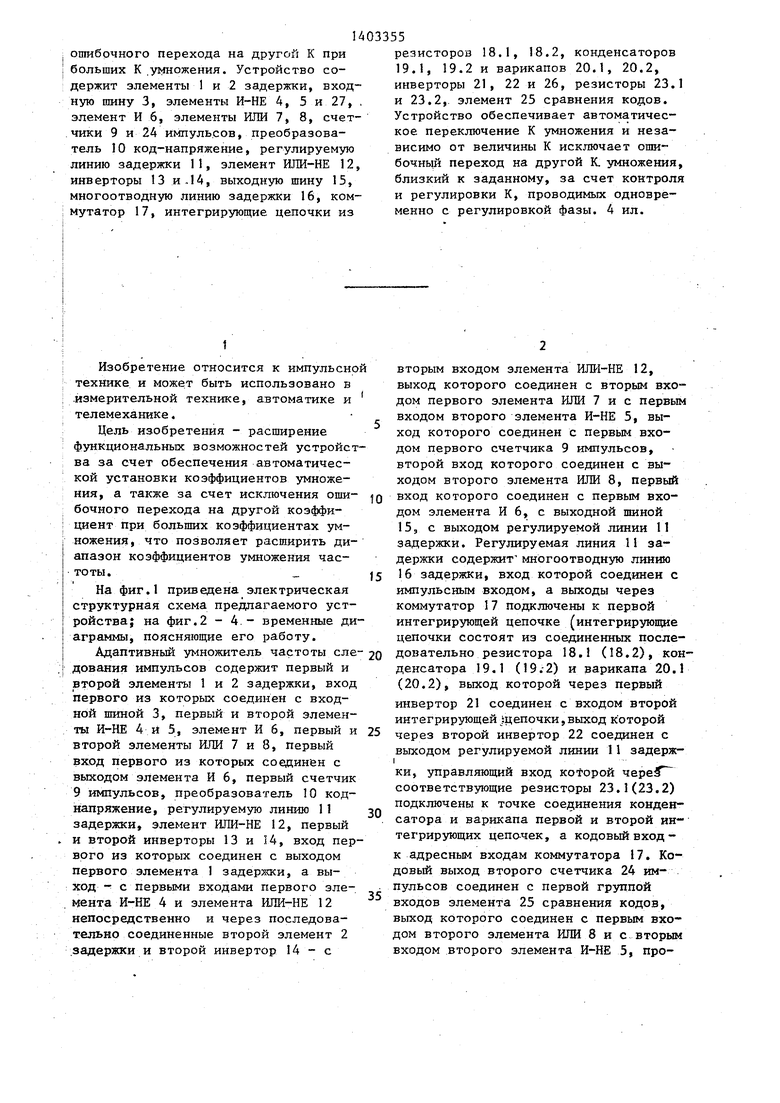

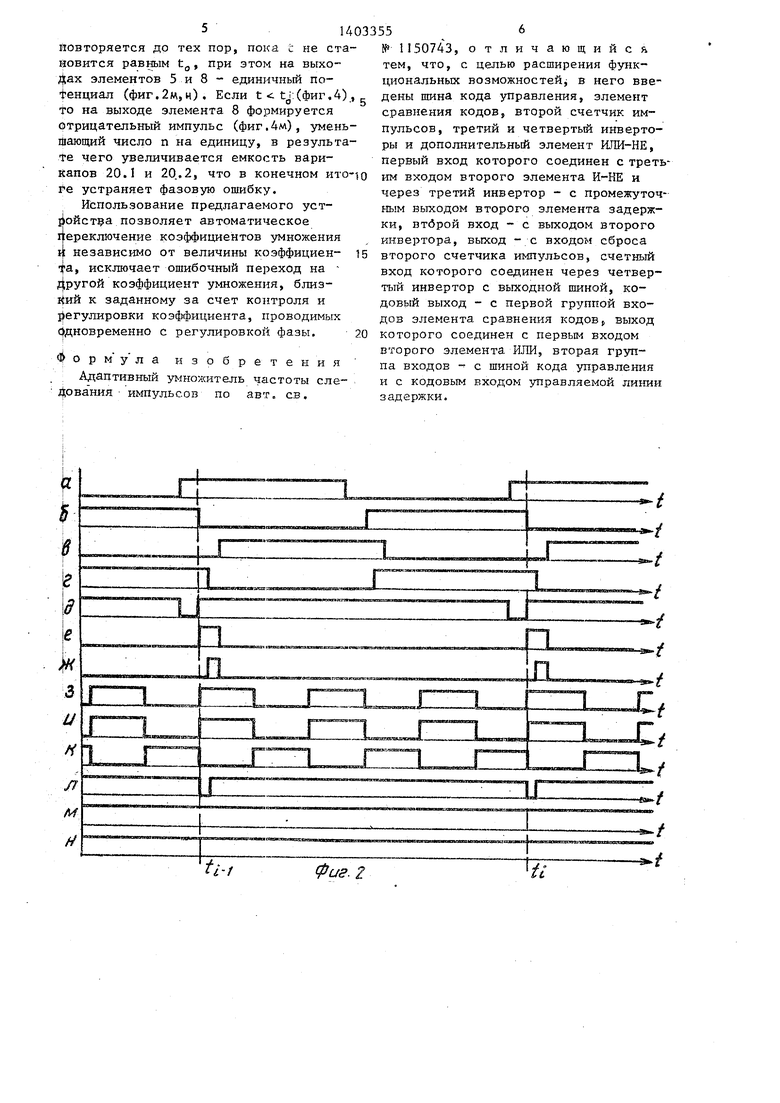

На фиг.1 приведена электрическая стрзгктурная схема предлагаемого устройства; на фиг.2 - 4.- временные диаграммы, поясняющие его работу.

Адаптивньй умножитель частоты еле дования импульсов содержит первый и рторой элементы 1 и 2 задержки, вход первого из которых соединен с входной шиной 3, первый и второй элементы И-НЕ 4 и 5, элемент И 6, первый и второй элементы РШИ 7 и 8, первый вход первого из которых соединен с выходом элемента И 6, первый счетчик 9 импульсов, преобразователь 10 код- напряжение, регулируемую линию 11 задержки, элемент ИЛИ-НЕ 12, первый и второй инверторы 13 и 14, вход первого из которых соединен с выходом первого элемента 1 задержки, а выход - с первыми входами первого элемента И-НЕ 4 и элемента ИЛИ-НЕ 12 непосредственно и через последовательно соединенные второй элемент 2 задержки и второй инвертор 14 - с

резисторов 18.1, 18.2, конденсаторов 19.1, 19.2 и варикапов 20.1, 20.2, инверторы 21, 22 и 26, резисторы 23.1 и 23.2, элемент 25 сравнения кодов. Устройство обеспечивает автоматическое переключение К умножения и независимо от величины К исключает оши бочный переход на другой К. умножения близкий к заданному, за счет контроля и регулировки К, проводимых одновременно с регулировкой фазы. 4 ил.

Q 5

0 5 О

5

вторым входом элемента ШШ-НЕ 12, выход которого соединен с вторым входом первого элемента ИЛИ 7 и с первым входом второго элемента И-НЕ 5, выход которого соединен с первым входом первого счетчика 9 импульсов, второй вход которого соединен с выходом второго элемента ИЛИ 8, первый вход которого соединен с первым входом элемента И 6, с выходной шиной IS, с выходом регулируемой линии 11 задержки. Регулируемая линия 11 задержки содержит многоотводную линию 16 задержки, вход которой соединен с импульсным входом, а выходы через коммутатор 17 подключены к первой интегрирующей цепочке (интегрируюпще цепочки состоят из соединенных последовательно резистора 18.1 (18.2), конденсатора 19.1 (19.-2) и варикапа 20.1 (20.2), выход которой через первый

инвертор 21 соединен с входом второй интегрирующей :цепочки, выход которой через второй инвертор 22 соединен с

выходом регулируемой линии 11 задержI

ки, управляющий вход которой чере

соответствующие резисторы 23.1(23.2) подключены к точке соединения конденсатора и варикапа первой и второй интегрирующих цепо-чек, а кодовый входк адресным входам коммутатора 17. Кодовый выход второго счетчика 24 импульсов соединен с первой группой входов элемента 25 сравнения кодов, выход которого соединен с первым входом второго элемента ИЛИ 8 и с вторым входом второго элемента И-НЕ 5, промежуточный выход второго элемента 2 задержки соединен через третий инвертор 26 с первым входом дополнительного элемента ИЛИ-НЕ 27 и с третьим входом второго элемента И-НЕ 5, второй вход дополнительного элемента ИЛИ-НЕ 27 соединен с выходом второго инвертора 4, выход - с входом сброса второго счетчика 24 импульсов, счетный вход которого соединен через четвертый инвертор с выходной шиной 15, шина 29 кода зшравления соединена с кодовым входом регулируемой линией 11 задержки и с второй группой входов элемента 25 сравнения . кодов.

Устройство работает следующим образом.

Входная последовательность импульсов на шине 3 (фиг.2а) задерживается и инвертируется с помощью элемента 1 и инвертора 13 (фиг.2Ь), а также элемента 2 и инвертора 14 (фиг.2Ь). При этом на выходах, элементов 4 и 12 формируются отрицательные и положительные импульсы (фиг.22,и) соответственно, длительность которых равна . величине задержек импульсов в соответствующих элементах 1 и 2 (в качестве которых можно использовать интегрирующие цепочки либо одну или несколько пар инверторов). Задержку устанавливают в соответствии с максимальной величиной фазовой ошибки выходных импульсов, накапливаемой в интервале одного периода следования входных импульсов при любых допустимых климатических и временных условиях эксплуатации. Коэффициент К умножения устанавливается подачей на адресные шины коммутатора 17 и входы

элемента 25 двоичного кода числа К. При этом коммутируется соответствующий отвод линии 16 и первой интегрирующей цепочки, содержащей резистор 18.1, конденсатор 19.1 и варикап 20.1. Эта цепочка вместе с последовательно соединенной с ней через инвертор 21 второй интегрирующей цепочкой, содержащей резистор 18.2, конденсатор 19.2 и варикап 20.2, совместно с инвертором 22 позволяет плавно регулировать задержку импульсов, проходящих через коммутатор 17. Регуировка задержки обеспечивается поачей напряжения на управляющий вход линии 1I, которое через резисторы

0

5

0

5

0

0

0

с сбрасывается счетчик 24 ..и на выходе элемента 25 вновь устанавливается уровень логической единицы. Однако импульс на выходе элемента 5 не формируется, так как на его третий вход в этот момент поступает логический ноль с выхода инвертора 26 (фиг.2г). Если t t, то диаграммы напряжений, изображенные на фиг.2, принимают вид, аналогичный изображенному на фиг.З

5 соответственно. К моменту t- счетчик 24 не успевает накопить число К, и на выходе элемента 25 остается логическая единица. При этом на выходе элемента 5 появляется отрицательный импульс (фиг.Зи), который увеличивает число п, записанное в счетчике 9, на единицу. При этом соответственно по- вьш1ается напряжение на выходе преобразователя 10, в результате чего сниg жается емкость варикапов 20.1 и 20.2 и уменьшается задержка t. Если t все еще больше t, то на следующем периоде этот процесс повторяется, увеличивая число п еще на единицу. Процесс

Иовторяется до тех пор, пока t не ста- йовится равным t, при этом на выхо- Дах элементов 5 и 8 - единичный по- Фенциал (фиг.2м,и). Если t tj:(фиг.4), то на выходе элемента 8 формируется отрицательный импульс (фиг.4м), уменьшающий число п на единицу, в результате чего увеличивается емкость варикапов 20.1 и 20..2, что в конечном итоге устраняет фазовую ошибку.

Использование предлагаемого уст- 1 ойст9а позволяет автоматическое переключение коэффициентов умножения И независимо от величины коэффициен- 4а, исключает ошибочный переход на - ;|ругой коэффициент умножения, близкий к заданному за счет контроля и 1 егулировки коэффициента, проводимых с дновременно с регулировкой фазы.

Формула изобретения

Адаптивный умножитель частоты сле 4ования импульсов по авт. св.

№ 1150743, отличающийся тем, что, с целью расширения функциональных возможностей в него введены шина кода управления, элемент сравнения кодов, второй счетчик импульсов, третий и четвертьй инверторы и дополнительный элемент ИЛИ-НЕ, первый вход которого соединен с третим входом второго элемента И-КЕ и через третий инвертор - с промежуточ ВЫХОДОМ второго элемента задержки, втброй вход - с выходом второго инвертора, выход - с входом сброса второго счетчика импульсов, счетный вход которого соединен через четвертый инвертор с выходной шиной, кодовой выход - с первой группой входов элемента сравнения кодовр выход которого соединен с первым входом второго элемента ИЛИ, вторая группа входов - с шиной кода управления и с кодовым входом управляемой линии задер)жки.

фигЛ

tL

| Адаптивный умножитель частоты следования импульсов | 1983 |

|

SU1150743A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-15—Публикация

1986-09-22—Подача