1

(61) II56006

(21)4389708/24-24

(22)09.03.88

(46) 23.11 .89. Бюл. N 43

(72) В.С.Харченко, А.В.Мунтяну,

Г.Н.Тимонькии и С.Н.Ткачеико

(53)621.503.55 (088.8)

(56)Авторское свидетельство СССР К 1156006, кл. G 05 В 19/18, 1983.

(54)УСТРОЙСТВО ДЛЯ ПРОГРА1 МНОГО РЕГУЛИРОВАНИЯ

(57)Изобретение относится к цнфро-. вой автоматике и программному управлению и может быть использовано при проектировании программируемых микроконтроллеров для АСУ ТП. Ыеяь изобретения - расширение области применения за счет расширения номенклатуры программно-аппаратно формируемых аппроксимирующих кривых для управляющих воздействий. Она достигается введением регистра задания 13, второго 14 - четвертого 16 элементов I, триггера 17 и их связей. Сущность изобретения состоит в расширении области применения устройства путем обеспечения возможности как линейной, так и нелинейной аппроксимации управляк1Щ1-гх воздействий с варьируемьм тагом. Это обеспечивает повышение точности регулирования и уменьшение суммарных аппаратных затрат. 4 ил.

(Л

СП N5

Ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного регулирования | 1986 |

|

SU1437833A2 |

| Устройство для кусочно-линейной аппроксимации | 1990 |

|

SU1837272A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Устройство для программного регулирования | 1988 |

|

SU1571550A1 |

| Устройство для программного управления | 1986 |

|

SU1397880A1 |

| Устройство для моделирования радиотелеграфного канала связи | 1981 |

|

SU1034053A1 |

| Число-импульсное линеаризующее устройство с масштабированием | 1983 |

|

SU1109759A1 |

| Устройство для считывания графической информации | 1985 |

|

SU1252803A1 |

| Генератор случайного процесса | 1983 |

|

SU1113800A1 |

Изобретение относится к цифровой автоматике и программному управлению и может быть использовано при проектировании программируемых микроконтроллеров для АСУ ТП. Цель изобретения - расширение области применения за счет расширения номенклатуры программно-аппаратноформируемых аппроксимирующих кривых для управляющих воздействий. Она достигается введением регистра задания 13, второго 14 - четвертого 16 элементов И, триггера 17 и их связей. Сущность изобретения состоит в расширении области применения устройства путем обеспечения возможности как линейном, так и нелинейной аппроксимации управляющих воздействий с варьируемым шагом. Это обеспечивает повышение точности регулирования и уменьшение суммарных аппаратных затрат. 4 ил.

ГЧ)

Изобретение относится к автоматике, предназначено для программного регулирования технологическими процессами и является усовершенствованием изобретения по авт. св. № 1156006.

Цель изобретения - растчирение области применения устройства за счет реализации возможности получения на выходе устройства как линейно, так и нелинейно изменяющихся управляющих воздействий и управления точностью аппроксимации путем изменения коэффициента деления делителя за время выполнения одной подпрограммы и управления режимом работы задаю1чего генератора.

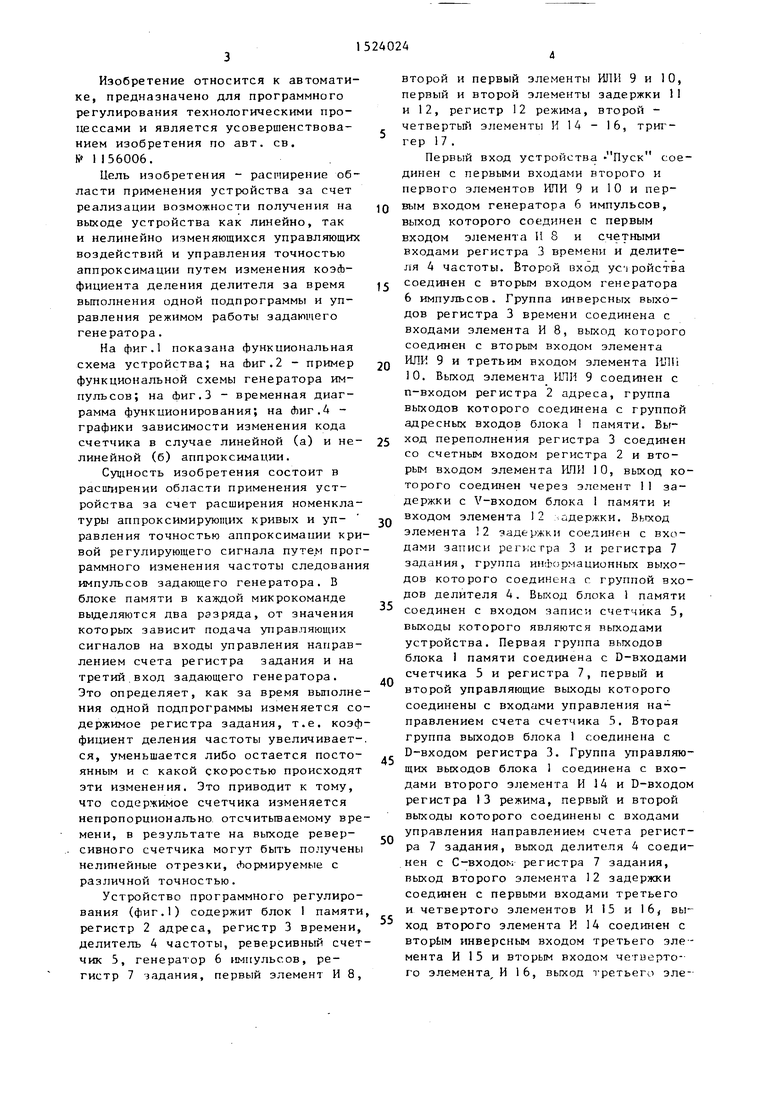

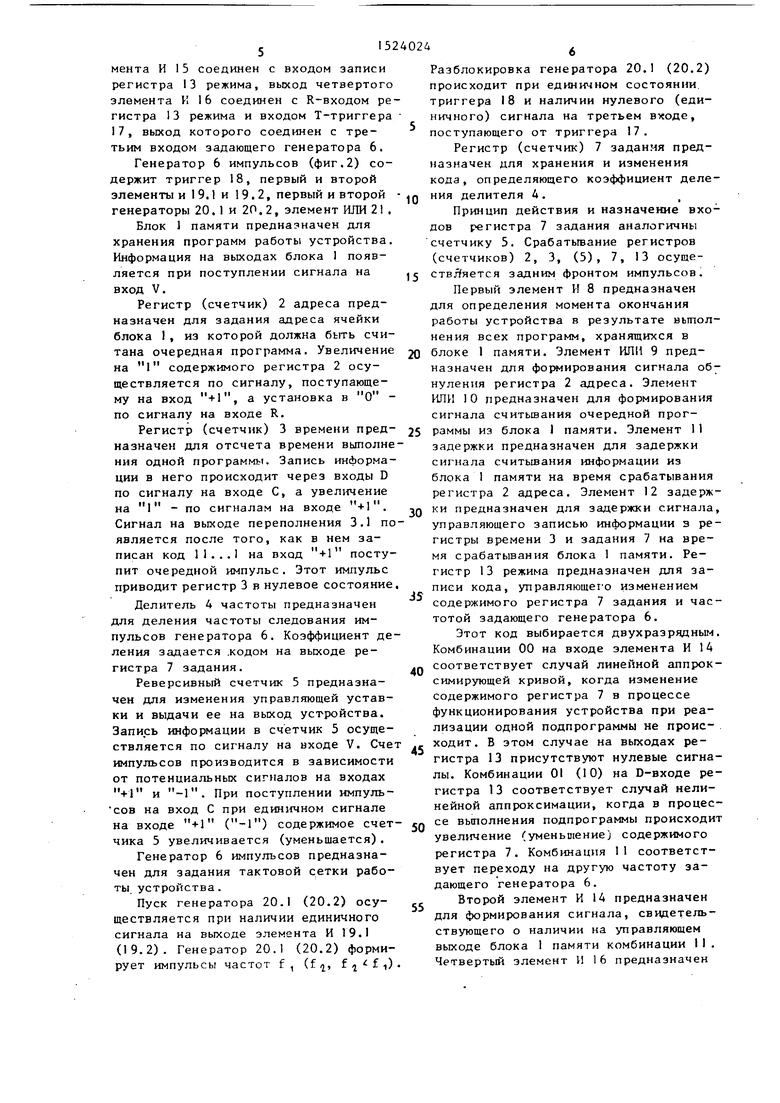

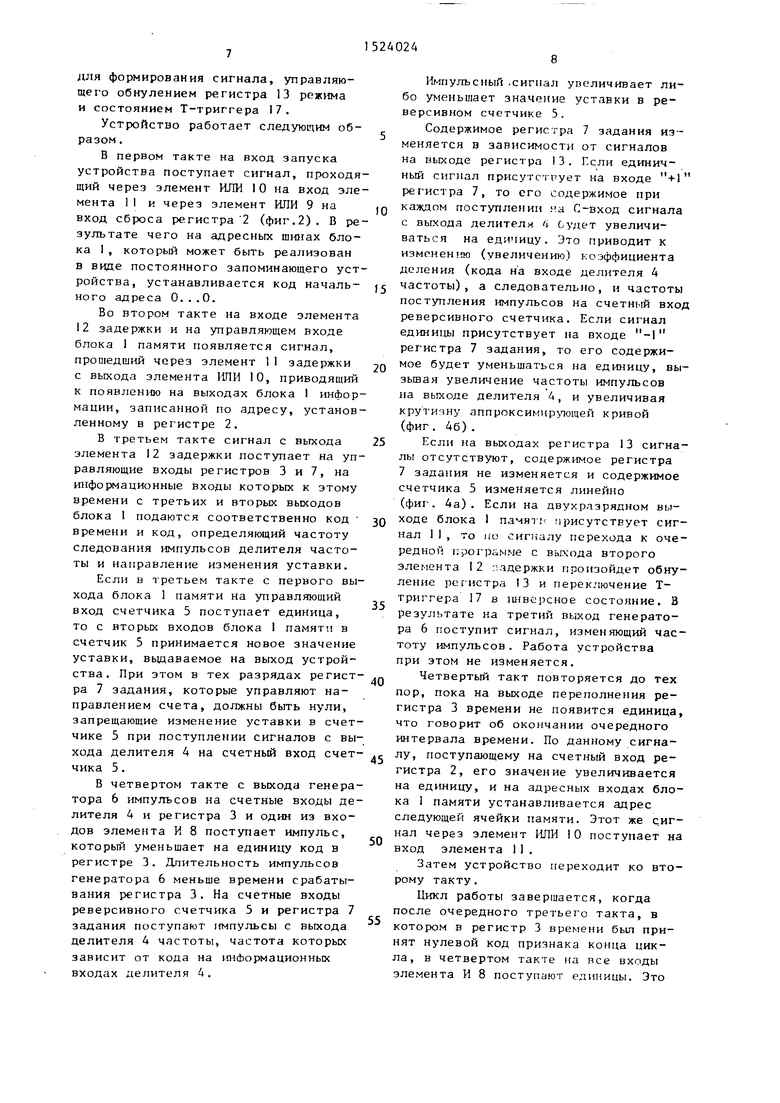

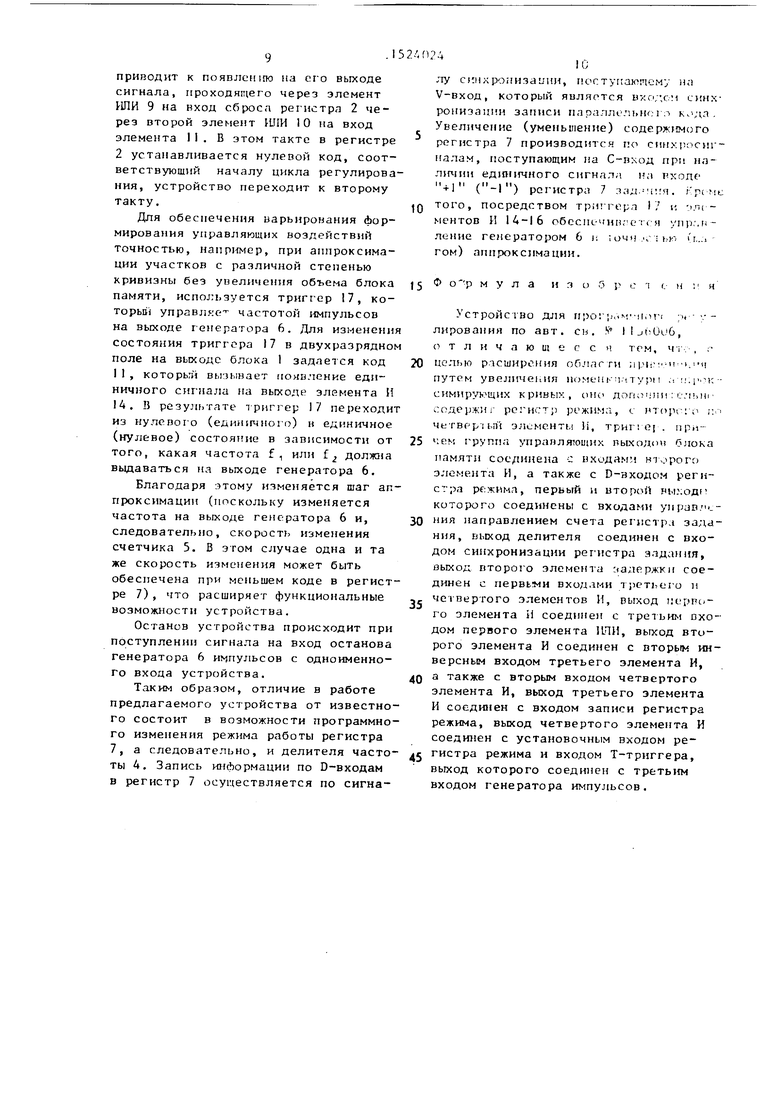

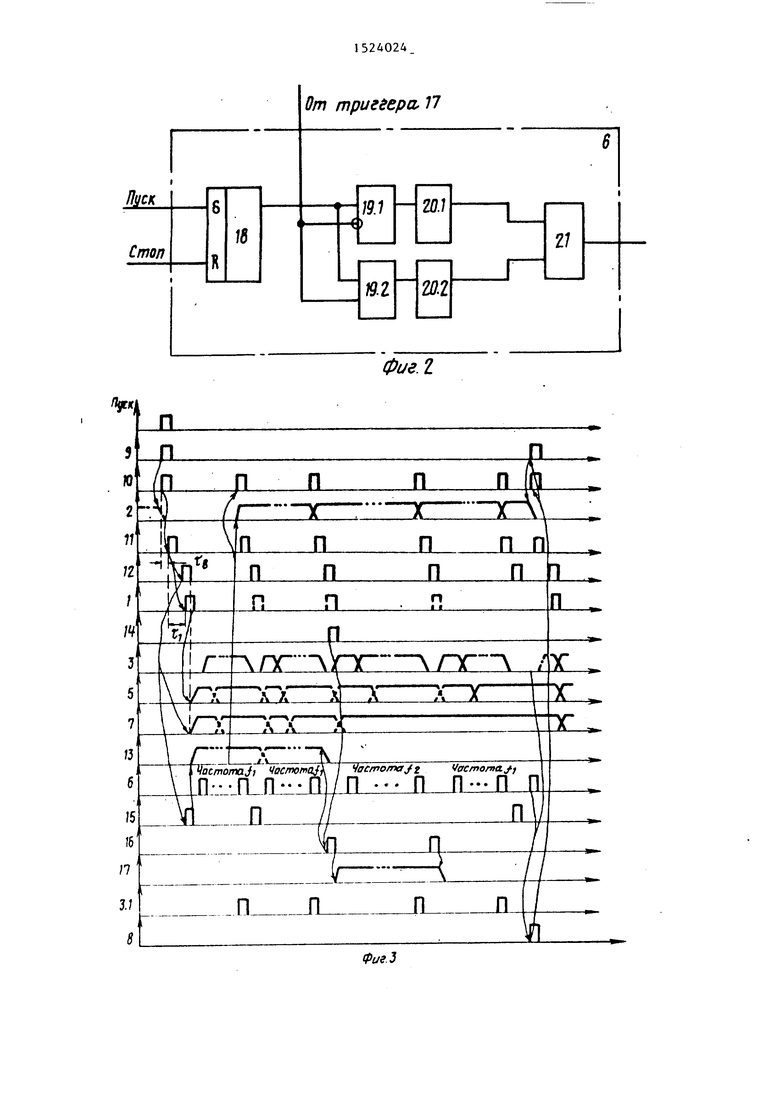

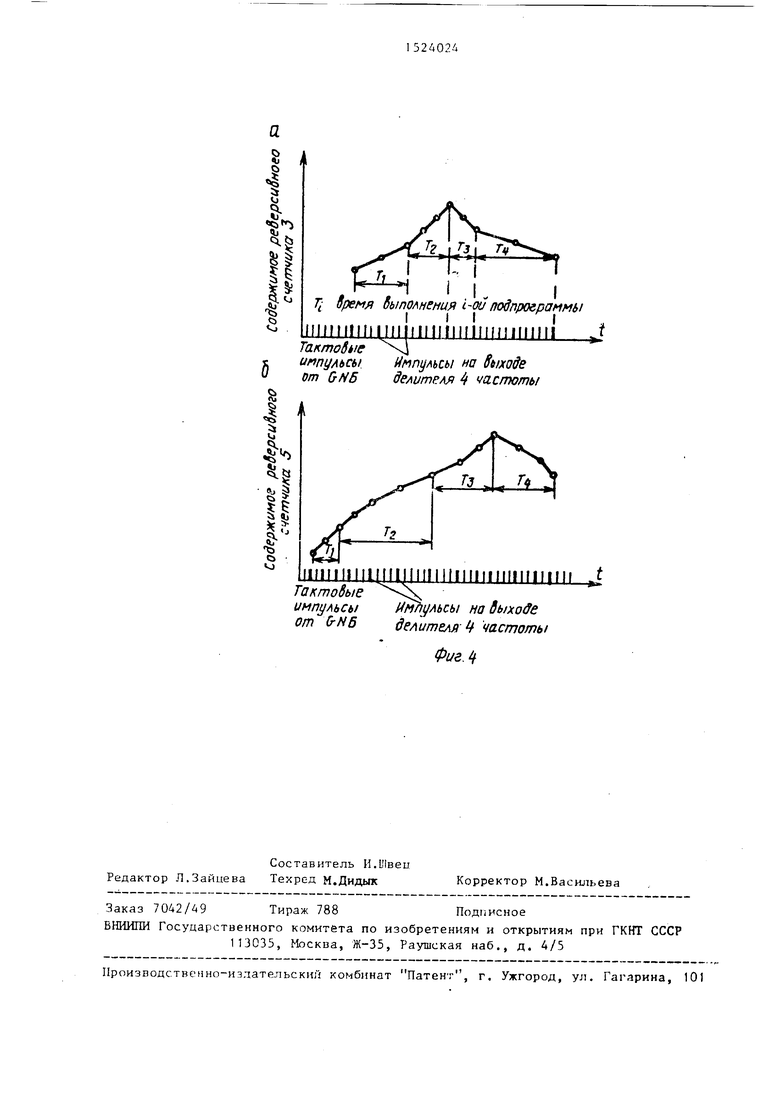

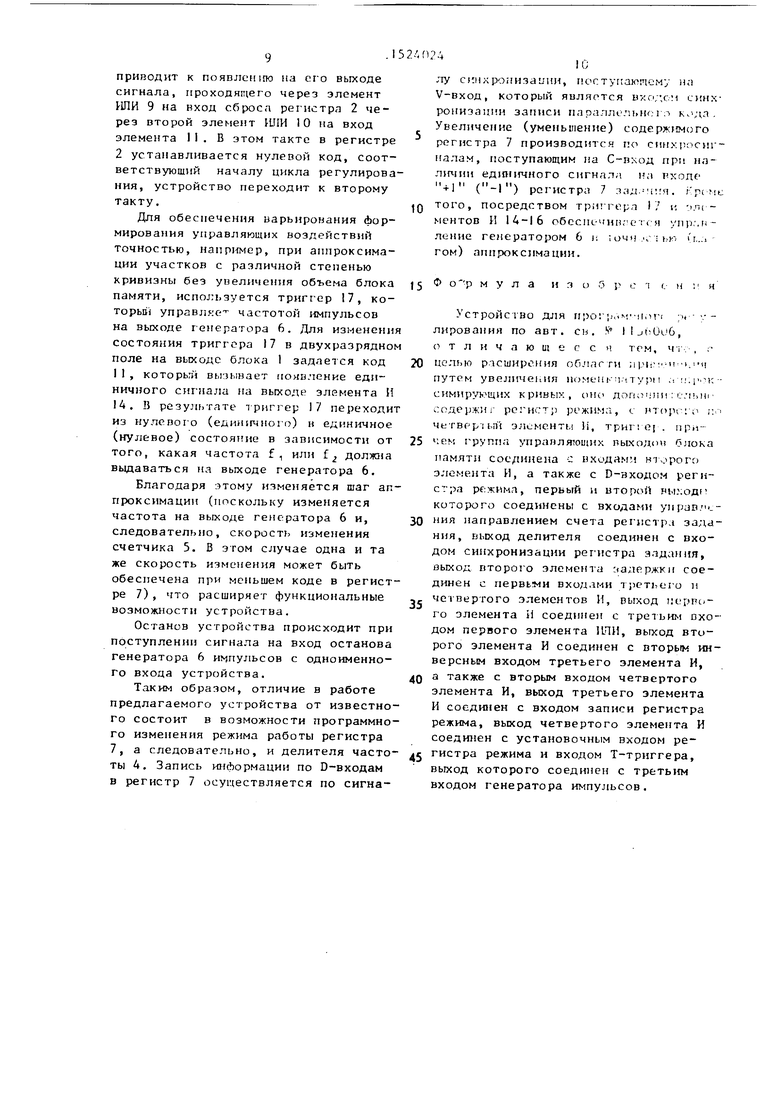

На фиг.1 показана функциональная схема устройства; на Фиг.2 - пример функциональной схемы генератора импульсов; на фиг.З - временная диаграмма функционирования; на Лиг.4 - графики зависимости изменения кода счетчика в случае линейной (а) и нелинейной (б) аппроксимации.

Сущность изобретения состоит в расширении области применения устройства за счет расширения номенклатуры аппроксимирующих кривых и управления точностью аппроксимации кривой регулирующего сигнала путем программного изменения частоты следовани импульсов задающего генератора. В блоке памяти в каждой микрокоманде выделяются два разряда, от значения которых зависит подача управляющих сигналов на входы управления направлением счета регистра задания и на третий,вход задающего генератора. Это определяет, как за время выполнения одной подпрограммы изменяется содержимое регистра задания, т.е. коэффициент деления частоты увеличивается, уменьшается либо остается постоянным и с какой скоростью происходят эти изменения. Это приводит к тому, что содержимое счетчика изменяется непропорционально отсчитьшаемому времени, в результате на выходе реверсивного счетчика могут быть получены нелинейные отрезки, Нормируемые с различной точностью.

Устройство программного регулирования (фиг.1) содержит блок 1 памяти регистр 2 адреса, регистр 3 времени, делитель 4 частоты, реверсивный счетчик 5, генератор 6 импульсов, регистр 7 задания, первый элемент И 8,

5

0

5

0

5

0

5

0

5

второй и первый элементы ИЛИ 9 и 10, первый и второй элементы задержки 11 и 12, регистр 12 режима, второй - четвертый элементы И 14 - 16, триггер 1 7 .

Первый вход устройства соединен с первыми входами второго и первого элементов ИЛИ 9 и 10 и первым входом генератора 6 импульсов, выход которого соединен с первым входом элемента И 8 и счет ными входами регистра 3 времени и делителя 4 частоты. Второй вход усч ройства соединен с вторым входом генератора 6 импульсов. Группа инверсных выходов регистра 3 времени соединена с входами элемента И 8, выход которого соединен с вторым входом элемента ИЛИ 9 и третьим входом элемента Iinii 10. Выход элемента ИЛИ 9 соединен с п-входом регистра 2 адреса, группа выходов которого соединена с группой адресных входов блока 1 памяти. Выход переполнения регистра 3 соединен со счетным входом регистра 2 и вто- рътм входом элемента ИЛИ 10, выход которого соединен через элемент 11 задержки с V-входом блока 1 памяти и входом элемента 12 .адержки. Выход элемента 12 задержки соединен с входами записи рег ;сгра 3 и регистра 7 задания, группа информационных выходов которого соединена с группой входов делителя 4. Выход блока 1 памяти соединен с входом записи счетчика 5, выходы которого являются выходами устройства. Первая группа выходов блока 1 памяти соединена с D-входами счетчика 5 и регистра 7, первый и второй управляющие выходы которого соединены с входами управления направлением счета счетчика 5. Вторая группа выходов блока 1 соединена с D-входом регистра 3. Группа управляющих выходов блока 1 соединена с входами второго элемента И 14 и D-входом регистра 13 режима, первый и второй выходы которого соединены с входами управления направлением счета регистра 7 задания, выход делителя 4 соединен с С-входом регистра 7 задания, выход второго элемента 12 задержки соединен с первыми входами третьего и четвертого элементов И 15 и 16, выход второго элемента И 14 соединен с BTopfciM инверсным входом третьего элемента И 15 и вторым входом четвертого элемента И 16, выход третьего элемента И 15 соединен с входом записи регистра 13 режима, выход четвертого элемента И 16 соединен с R-входом регистра 13 режима и входом Т-триггера 17, выход которого соединен с третьим входом задающего генератора 6.

Генератор 6 импульсов (фиг.2) содержит триггер 18, первый и второй элементы и 19.1 и 19.2, первый и второй генераторы 20. 1 и 20.2, элемент ИЛИ 21 .

Блок 1 памяти предназначен для Хранения программ работы устройства. Информация на выходах блока 1 появляется при поступлении сигнала на вход V.

Регистр (счетчик) 2 адреса предназначен для задания адреса ячейки блока 1, из которой должна быть считана очередная программа. Увеличение на 1 содержимого регистра 2 осуществляется по сигналу, поступающему на вход -t-1, а установка в О - по сигналу на входе R.

Регистр (счетчик) 3 времени предназначен для отсчета времени вьтолне ния одной программы. Запись информации в него происходит через входы D по сигналу на входе С, а увел1тчение на 1 - по сигналам на входе . Сигнал на выходе переполнения 3.1 появляется после того, как в нем записан код 11... 1 на вход + 1 поступит очередной импульс. Этот импульс приводит регистр 3 в нулевое состояние

Делитель 4 частоты предназначен для деления частоты следования импульсов генератора 6. Коэффициент деления задается .кодом на выходе регистра 7 задания.

Реверсивный счетчик 5 предназначен для изменения управляющей уставки и выдачи ее на вькод устройства. Запись информации в счетчик 5 осуществляется по сигналу на входе V. Счет импульсов производится в зависимости от потенциальных сигналов на входах +1 и -1. При поступлении импуль- сов на вход С при единичном сигнале на входе +1 (-1) содержимое счетчика 5 увеличивается (уменьщается).

Генератор 6 импульсов предназначен для задания тактовой сетки работы устройства.

Пуск генератора 20.1 (20.2) осуществляется при наличии единичного сигнала на выходе элемента И 19.1 (19.2). Генератор 20.1 (20.2) формирует импульсы частот f , (f/i, f f i)

0

0

5

0

S

0

5

0

5

Разблокировка генератора 20.1 (20.2) происходит при единичном состоянии, триггера 18 и наличии нулевого (единичного) сигнала на третьем входе, поступающего от триггера 17.

Регистр (счетчик) 7 задания предназначен для хранения и изменения кода, определяющего коэффициент деления делителя Д.

Принцип действия и назначение входов регистра 7 задания аналогичны счетчику 5. Срабатьгеание регистров (счетчиков) 2, 3, (5), 7, 13 осуще- ствЛяется задним фронтом импульсов.

Первый элемент И 8 предназначен для определения момента окончания работы устройства в результате вьшол- нения всех программ, хранящихся в блоке 1 памяти. Элемент НПИ 9 предназначен для формирования сигнала обнуления регистра 2 адреса. Элемент ИЛИ 10 предназначен для формирования сигнала считьшания очередной программы из блока 1 памяти. Элемент 11 задержки предназначен для задержки сигнала считьшания информации из блока 1 памяти на время срабатывания регистра 2 адреса. Элемент 12 задержки предназначен для задержки сигнала, управляющего записью информации в регистры времени 3 и задания 7 на время срабатывания блока 1 памяти. Регистр 13 режима предназначен для записи кода, управляющего изменением содержимого регистра 7 задания и частотой задающего генератора 6.

Этот код выбирается двухразрядным. Комбинации 00 на входе элемента И 14 соответствует случай линейной аппроксимирующей кривой, когда изменение содержимого регистра 7 в процессе функционирования устройства при реализации одной подпрограммы не пронс- . ходит. В этом случае на выходах регистра 13 присутствуют нулевые сигналы. Комбинации 01 (10) на D-входе регистра 13 соответствует случай нелинейной аппроксимации, когда в процессе выполнения подпрограммы происходит увеличение (уменьшение) содержимого регистра 7. Комбинация 11 соответствует переходу на другую частоту задающего генератора 6.

Второй элемент И 14 предназначен для формирования сигнала, свидетельствующего о наличии на управляющем выходе блока 1 памяти комбинации II. Четвертый элемент И 16 предназначен

для формирования сигнала, управляющего обнулением регистра 13 режима и состоянием Т-триггера 17.

Устройство работает следующим образом ,

В первом такте на вход запуска устройства поступает сигнал, проходящий через элемент ИЛИ 10 на вход элемента 1I и через элемент ИЛИ 9 на вход сброса регистра 2 (фиг.2). В результате чего на адресных шинах блока 1, который может быть реализован в виде постоянного запоминающего устройства, устанавливается код начального адреса 0. . .0.

Во втором такте на входе элемента 12 задержки и на управляющем входе блока 1 памяти появляется сигнал, прои|едший через элемент 1 1 задержки с выхода элемента ИЛИ 10, приводящий к появлению на выходах блока I информации, записанной по адресу, установленному в регистре 2.

В третьем такте сигнал с выхода элемента 12 задержки поступает на управляющие входы регистров 3 и 7, на информационные входы которых к этому времени с третьих и вторых выходов блока 1 подаются соответственно код времени и код, определяющий частоту следования импульсов делителя частоты и направление изменения уставки.

Если в третьем такте с первого выхода блока 1 памяти на управляющий вход счетчика 5 поступает единица, то с вторых входов блока I памятя в счетчик 5 принимается новое значение уставки, выдаваемое на выход устройства. При этом в тех разрядах регистра 7 задания, которые управляют направлением счета, должны быть нули запрещающие изменение уставки в счетчике 5 при поступлении сигналов с выхода делителя 4 на счетный вход счетчика 5.

В четвертом такте с выхода генератора 6 импульсов на счетные входы делителя 4 и регистра 3 и один из входов элемента И 8 поступает импульс, который уменьшает на единицу код в регистре 3. Дпительность импульсов генератора 6 меньше времени срабатывания регистра 3. На счетные входы реверсивного счетчика 5 и регистра 7 задания поступают импульсы с выхода делителя 4 частоты, частота которых зависит от кода на информационных входах делителя 4.

0

5

0

5

0

5

0

5

Импульсный .сигнал увеличивает либо уменьшает значоше уставки в реверсивном счетчике 5.

Содержимое регистра 7 задания изменяется в зависимости от сигналов на выходе регистра 13. Гели единичный сигнал присутс 1тует на входе -f-1 регистра 7, то его содержимое при каждом поступлении на С-вход сигнала с выхода делителя i Судет увеличиваться на едичицу. Это приводит к изменен М (увеличению) коэффициента деления (кода на входе делителя 4 частоты), а следовательно, и частоты поступления импульсов на счетнь Й вход реверсивного счетчика. Если сигнал единигда присутствует на входе -1 регистра 7 задания, то его содержимое будет уменьшаться на единицу, вы- зьшая увеличение частоты импульсов на выходе делителя 4, и увеличивая крутизну аппроксимир тощей кривой (фиг. 46).

Если на выходах регистра 13 сигналы отсутствуют, содержимое регистра 7 задания не изменяется и содержимое счетчика 5 изменяется линейно (фиг. 4а). Если на двухрязрядном выходе блока 1 памят.ч присутствует сигнал 11, То Jio сигналу перехода к очередной программе с выхода второго элемента I 2 ;1лдержки произойдет обнуление регистра 13 и переключение Т- триггера 17 в инверсное состояние. В результате на третий выход генератора 6 поступит сигнал, изменяющий частоту импульсов . Работа устройства при этом не изменяется.

Четвертый такт повторяется до тех пор, пока на выходе переполнения регистра 3 времени не появится единица, что говорит об окончании очередного интервала времени. По данному сигналу, поступающему на счетный вход регистра 2, его значение увеличивается на единицу, и на адресных входах блока 1 памяти устанавливается адрес следующей ячейки памяти. Этот же сигнал через элемент ИЛИ 10 поступает на вход элемента 11 .

Затем устройство переходит ко второму такту.

Цикл работы завершается, когда после очередного третьего такта, в котором в регистр 3 времени бып принят нулевой код признака конца цикла, в четвертом такте F(a все входы элемента И 8 поступают единицы. Это

приводит к появлению на сг о выходе сигнала, проходящего через элемент ИЛИ 9 на вход сброса регистра 2 через второй элемент Ш1И 10 на вход элемента II, В этом такте в регистре 2 устанавливается нулевой код, соответствующий началу цикла регулирования, устройство переходит к второму такту.

Для обеспечения варьиронания формирования управляющих воздействий точностью, Hanpiwep, при аппроксимации участков с различной степенью кривизны без увеличения объема блока памяти, испо::ьзуется триггер 17, ко- TopbQi управл е- частотой импульсов на выходе генератора 6. Для изменения состояния триггера 17 в двухразрядном поле на выходе блока 1 задле1ся код 1 1 , который вызывает покв.чение единичного сигиа;1а на выходе элемента И 1А. В результате 7риггер 17 переходит из нулепог о (едия1гчно1-о) в единичное (нулевое) состояние в зависимости от того, какая частота f , или f должна выдаваться на выходе генератора 6.

Благодаря этому изменяется шаг аппроксимации (поскольку изменяется частота на выходе генератора 6 и, следовательно, скорость изменения счетчика 5, В этом случае одна и та же скорость изменения может быть обеспечена при мепьшем коде в регистре 7), что расширяет функциональные возможности устройства.

Останов устройства происходит при поступлении сигнала на вход останова генератора 6 импульсов с одноименного входа устройства.

Таким образом, отличие в работе предлагаемого устройства от известного состоит в возможности программного изменения режима работы регистра 7, а следовательно, и делителя частоты Д. Запись информации по D-входам в регистр 7 осуществляется по сигналу сслхроиизаиил, поступаюпсму на V-вход, который является B-/CI; ,C;I ciiHX- роиизации записи гьчралло. и.нгм ;т к, д-т Увеличение (уменьшение) содержимого регистра 7 производится синхросигналам, поступающим па С-вход при на- Л1ГЧИИ едшмгчного сигнала на Рходс (-1) регистра 7 л:и1-н:гя. Кр( ме ТОГО, посредством трштерл 17 : -j.ni - ментов И 14-16 обеспечип, С г я упр .и ление генератором 6 ч IOMH ггью гои) аппроксимации.

о -р м у л а и 3 о 5 р с -1 (.

Устройс гво для лирования по авт. (: т л и ч а ю U1 е

jiinii : е.чьш inopi-; о ; ej . прицолГ)Ю расширения об.плгги ;ii путем уве1П1чеиия симирук щих кривых, cuic доги содерж И регистр pejKisNia, с четвррм,п 1 элементы ii, трип чем группа управляющих пыходон блока памяти соединена - входами второго э. И, а также с D-входом регистра режима, первый и второй яы.чодс которого соединены с входами управ..- ния направлением счета регистра задания, выход делителя соединен с входом синхронизации регистра задания, выход второго элемента :(алержки соединен с первьми входами iретьего и четвертого элементов И, выход черного элемента И соединен с тре1ьим входом первого элемента 1ПИ, выход второго элемента И соединен с вторын инверсным входом третьего элемента И, а также с вторьм входом четвертого элемента И, выход третьего элемента И соединен с входом записи регистра режима, выход четвертого элемента И соединен с установочным входом ре- гистра режима и входом Т-триггера, вькод которого соединен с третьим входом генератора и шульсов.

Фиг. г

а g

I

ll i|

|i 1

Spefi/ Ьыпо нения i-ou подпрограммы

nininiiiiitiiiiiiifiiMiinniMiii

ТактоКие иппульсы от &НБ

1Ш11Ш11111И1111111111111И111П1 J

Тактобые импульсы от О-N6

iitiiiiiiifiiMiinniMii

Иг пуАьсы на быхаде делиггх ля vacmomb/

f j/Abcbt на dbixoffe делителл частоты

Фиг.

Авторы

Даты

1989-11-23—Публикация

1988-03-09—Подача