4 О СП

О

х

15

20

25

Изобретение относится к вычислительной технике и может быть использовано в аппаратуре дискретной информации для высокоскоростных буферов в цифровых устройствах.

Целью изобретения является расширение 5 бласти применения устройства за счет возможности многократного чтения данных.

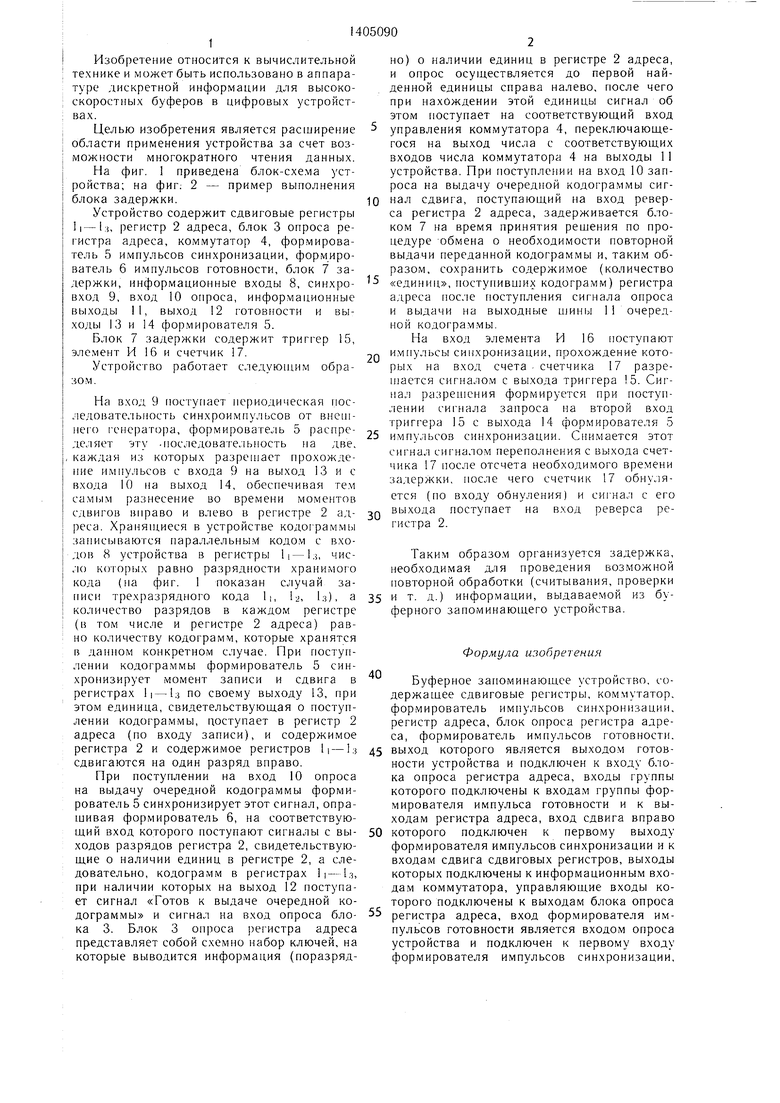

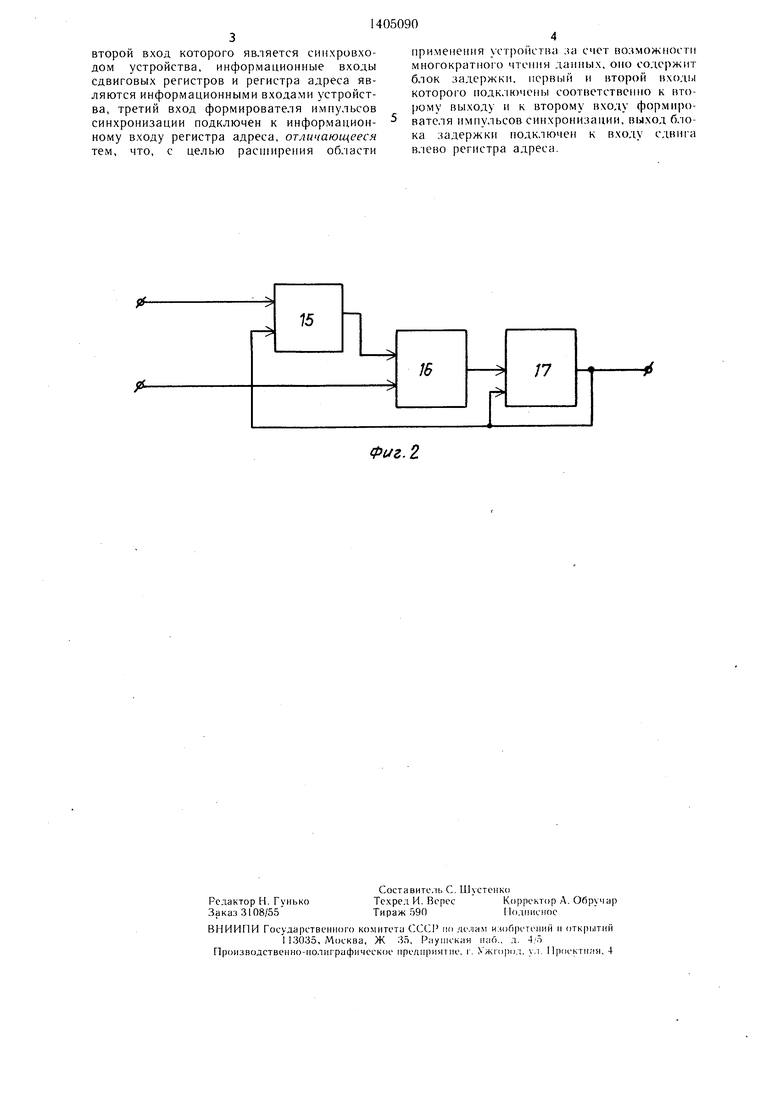

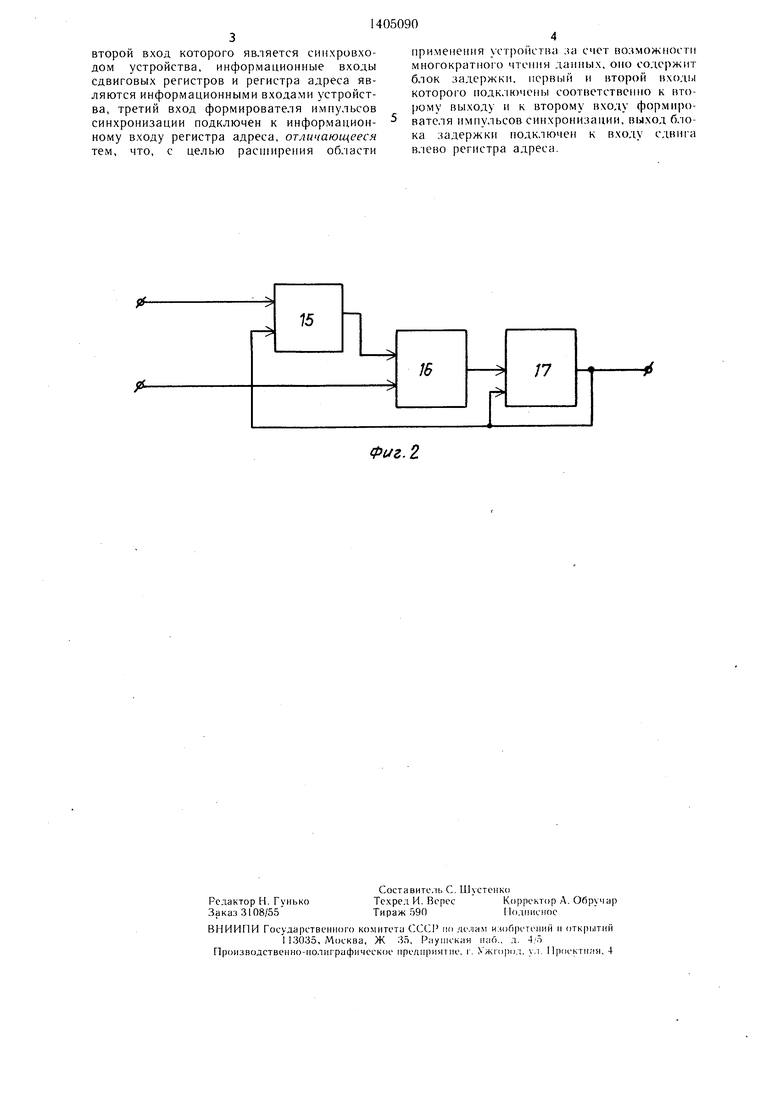

На фиг. 1 приведена блок-схема устройства; на фиг: 2 - пример выполнения блока задержки.IQ

Устройство содержит сдвиговые регистры 1|-1.S, регистр 2 адреса, блок 3 опроса регистра адреса, коммутатор 4, формироваель 5 импульсов синхронизации, формирователь 6 импульсов готовности, блок 7 заержки, информационные входы 8, синхро- ход 9, вход 10 опроса, информационные ыходы 11, выход 12 готовности и выоды 13 и 14 формирователя 5.

Блок 7 задержки содержит триггер 15, лемент И 16 и счетчик 17.

Устройство работает следующим обраом.

На вход 9 поступает периодическая последовательность синхроимпульсов от внсш- Hei o генератора, формирователь 5 распределяет эту -последовате ьность на две. каждая из которых разрешает прохождение импульсов с входа 9 на выход 13 и с входа 10 на выход 14, обеспечивая тем самым разнесение во времени моментов сдвигов вправо и влево в регистре 2 адреса. Храняпхиеся в устройстве кодограммы записываются параллельным кодом с входов 8 устройства в регистры Ь-l.j, число KOTOpiiix равно разрядности хранимого кода (на ф|иг. 1 показан случай записи трехразрядного кода 1|, U, 1.з), а 35 количество разрядов в каждом регистре (в том числе и регистре 2 адреса) равно количеству кодограмм, которые хранятся в данном конкретно.м случае. При поступлении кодограммы формирователь 5 синхронизирует момент записи и сдвига в регистрах 1|-1з по своему выходу 13, при этом единица, свидетельствующая о поступлении кодограммы, поступает в регистр 2 адреса (по входу записи), и содержимое регистра 2 и содержимое регистров 1 - з сдвигаются на один разряд вправо.

При поступлении на вход 10 опроса на выдачу очередной кодограммы формирователь 5 синхронизирует этот сигнал, опрашивая формирователь б, на соответствующий вход которого поступают сигналы с вы- 50 ходов разрядов регистра 2, свидетельствующие о наличии единиц в регистре 2, а следовательно, кодограмм в регистрах Ь-1з, при наличии которых на выход 12 поступает сигнал «Готов к выдаче очередной кодограммы и сигнал на вход опроса бло- 55 ка 3. Блок 3 опроса регистра адреса представляет собой схем но набор ключей, на которые выводится информация (поразряд30

40

- 3 45

5

0

5

5

Q

5

0

но) о наличии единиц в регистре 2 адреса, и опрос осуществляется до первой найденной единицы справа налево, после чего при нахождении этой единицы сигнал об этом поступает на соответствующий вход управления коммутатора 4, переключающегося на выход числа с соответствующих входов числа коммутатора 4 на выходы 11 устройства. При поступлении на вход 10 запроса на выдачу очередной кодограммы сигнал сдвига, поступающий на вход реверса регистра 2 адреса, задерживается блоком 7 на время принятия рещепия по процедуре обмена о необходимости повторной выдачи переданной кодограммы и, таким образом, сохранить содержимое (количество «единиц, поступивших кодограмм) регистра адреса после поступления сигнала опроса и выдачи на выходные шипы 1 1 очередной кодограм.мы.

На вход элемента И 16 поступают импульсы синхронизации, прохождение которых на вход счета счетчика 17 разрешается сигналом с выхода триггера 5. Сигнал разрешения формируется при поступлении сигнала запроса на второй вход триггера 15 с выхода 14 формирователя 5 импульсов синхронизации. Снимается этот сигнал сигналом переполнения с выхода счетчика 17 после отсчета необходимого времени задержки, после чего счетчик 17 обнуляется (по входу обнуления) и си1 нал с его выхода поступает на вход реверса регистра 2.

Таким образо.м организуется задержка, необходимая для проведения возможной повторной обработки (считывания, проверки и т. д.) информации, выдаваемой из буферного запоминающего устройства.

Формула изобретения

Буферное запоминающее устройство, соержащее сдвиговые регистры, коммутатор, фор.мирователь импульсов синхронизации, регистр адреса, блок опроса регистра адреса, формирователь импульсов готовности, выход которого является выходо.м готовности устройства и подключен к входу б. Ю- ка опроса регистра адреса, входы группы которого подключены к входам группы формирователя импульса готовности и к выходам регистра адреса, вход сдвига вправо которого подключен к первому выходу формирователя импульсов синхронизации и к входам сдвига сдвиговых регистров, выходы которых подключены к информационным входам коммутатора, управляющие входы которого подключены к выходам блока опроса регистра адреса, вход формирователя импульсов готовности является входом опроса устройства и подключен к первому входу формирователя импульсов синхронизации.

второй вход которого является сннхровхо- дом устройства, информационные входы сдвиговых регистров и регистра адреса являются информационными входами устройства, третий вход формирователя импульсов синхронизации подключен к информационному входу регистра адреса, отличающееся тем, что, с целью расншрения области

применения ycTjioncTBa за счет ЕЮЗМОЖПОСТИ многократного чтсмин данных, оно содержит блок задержки, iicpBi.ifi и второй вход) которого подк,1К)чепы соот)етствемно к второму выходу и к второму входу формирователя импульсов синхронизации, выход блока задержки подключен к входу сдвига влево регистра адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1977 |

|

SU746735A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1575236A1 |

| Устройство для управления обменом информацией | 1987 |

|

SU1413637A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1980 |

|

SU918944A1 |

| Устройство для контроля электрических соединений | 1989 |

|

SU1633433A1 |

| Устройство для поиска информации | 1989 |

|

SU1686464A1 |

| Устройство для ввода информации от двухпозиционных датчиков | 1985 |

|

SU1280640A1 |

| Устройство для ввода-вывода информации при обработке физических величин | 1981 |

|

SU966683A1 |

| Устройство для вывода информации на экран электронно-лучевой трубки | 1985 |

|

SU1312560A1 |

| Устройство для сопряжения | 1981 |

|

SU966687A1 |

Изобретение относится к вычислительной технике и может быть использовано в аппаратуре дискретной информации для высокоскоростны.х оуферов в цифровы.х устройствах. Целью изобретения является расширение области применения устройства за счет возможности многократного чтения данных. Устройство содержит сдвиговые регистры 1| - l:i, регистр 2 адреса, блок 3 опроса регистра адреса, коммутатор 4, формирователь 5 и.мпульсов синхронизации, формирователь 6 импульсов готовности, блок 7 задержки. В устройстве организуется задержка, необходимая для проведения возможной повторной обработки (считывания, проверки и т. д.) информации, выдаваемой из буферного запоминающего устройства. 2 ил.

Фиг. 2

| Запоминающее устройство | 1974 |

|

SU469142A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Буферное запоминающее устройство | 1977 |

|

SU746735A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-06-23—Публикация

1986-07-04—Подача