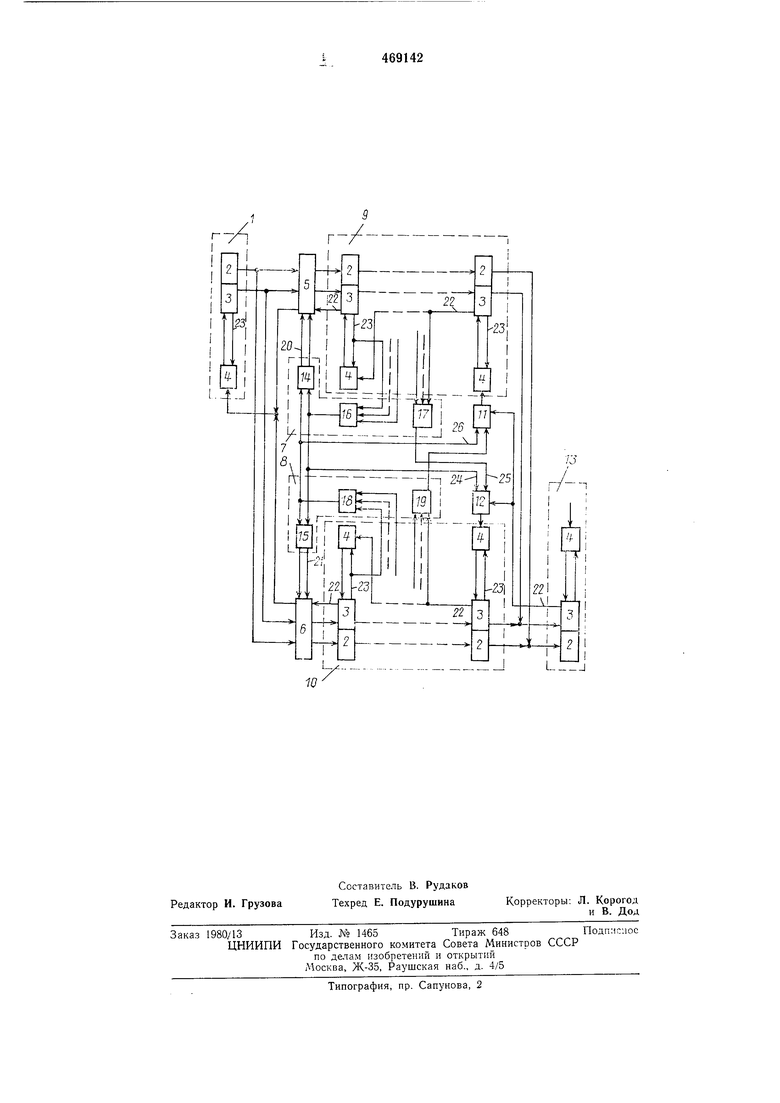

первого регистра 9, а затем автоматически продвигается к последнему регистру 9.

Выход 22 регистра 13 через переключатели 11 и 12 подключен к ячейкам 4 последних регистров 9 и Ш. Но в регистрах 10 информации нет, а с выхода последнего регистра 9 она поступает в регистр 13 и на выход устройства.

При увеличении скорости поступления информации на входе устройства, происходит заполнение регистров 9. Когда все регистры 9 заполнятся, на выходе элемента «И 16 появляется сигнал, который проходит на вход 24 переключателя 12 и отключает вход ячейки 4 от выхода 22 регистра 13. Кроме того, этот сигнал поступает на вход триггера 14 и перебрасывает его так, что элементы «И 5 закрываются, а также - на вход триггера 15 и перебрасывает его, при этом па его выходе появляется сигнал, открываюш,ий элементы «И 6.

Таким образом, к выходу регистра 1 подключаются регистры 10 и информация заполняет эти регистры.

Однако выборка информации продолжается из регистров 10, так как переключатель 12 разъединил ячейку 4 управления регистров 10. Но как только освободятся все регистры 9, то на выходе элемента «И 17 появляется сигнал, который поступает на вход 25 переключателя 12. Он подключает к входу ячейки 4 выход 22 маркерного разряда 3 регистра 13, после этого информация из регистров 10 автоматически переписывается в регистр 13.

Если заполнены информацией все регистры 10, то па выходе элемента «И 18 образуется сигнал, который подается на вход 26 переключателя 11 и отключает вход ячейки 4 от выхода 22 регистра 13. Этот сигнал перебрасывает триггеры 14 и 15 так, что элементы «И 6 запираются, а элементы «И 5 открываются, и информация снова пдет в регистры 9.

Предмет изобретения

Запоминающее устройство, содержащее входной регистр, группы основных регистров и выходной регистр, каждый из которых состоит из маркерного и информационных разрядов и ячейки управления записью, отличающееся тем, что, с целью повышения быстродействия и надежности работы устройства, оно содержит группы элементов «И, схемы управления и переключатели по количеству групп основных регистров, информационные входы элементов «И подключены к выходам входного регистра, управляющие входы - к выходам соответствующих схем управления, соединенным с маркерными разрядами основных регистров, а выходы - к входам соответствующих первых основных регистров, входы переключателей соединены со схемами

управления и с выходом маркерного разряда выходного регистра, а выходы - с ячейками управления записью последних основных регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ маркирования информационных комбинаций в системах последовательной записи с двухчастотным кодированием и устройства записи и воспроизведения для его осуществления | 1987 |

|

SU1543445A1 |

| Способ последовательной записи или передачи с двухчастотным кодированием и устройство для его осуществления | 1989 |

|

SU1645993A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Запоминающее устройство с частичным резервированием | 1986 |

|

SU1434503A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Буферное запоминающее устройство | 1982 |

|

SU1053163A1 |

| Устройство для сопряжения ЦВМ с внешними устройствами | 1989 |

|

SU1784840A1 |

| Устройство для синхронизации операндов в однородных структурах | 1973 |

|

SU552600A1 |

LX

221

-231

2

L

j

Авторы

Даты

1975-04-30—Публикация

1974-04-03—Подача