Изобретение относится к вычислительной технике, в частности к буферным запоминающим устройствам в аппаратуре обмена дискретной информацией, и может быть использовано при разработке высокоскоростных буферов в цифровых устройствах.

Цель изобретения - расширение области применения устройства за счет возможности чтения данных по приоритетам, а также записи и хранения данных с приоритетами нескольких асинхронных потоков.

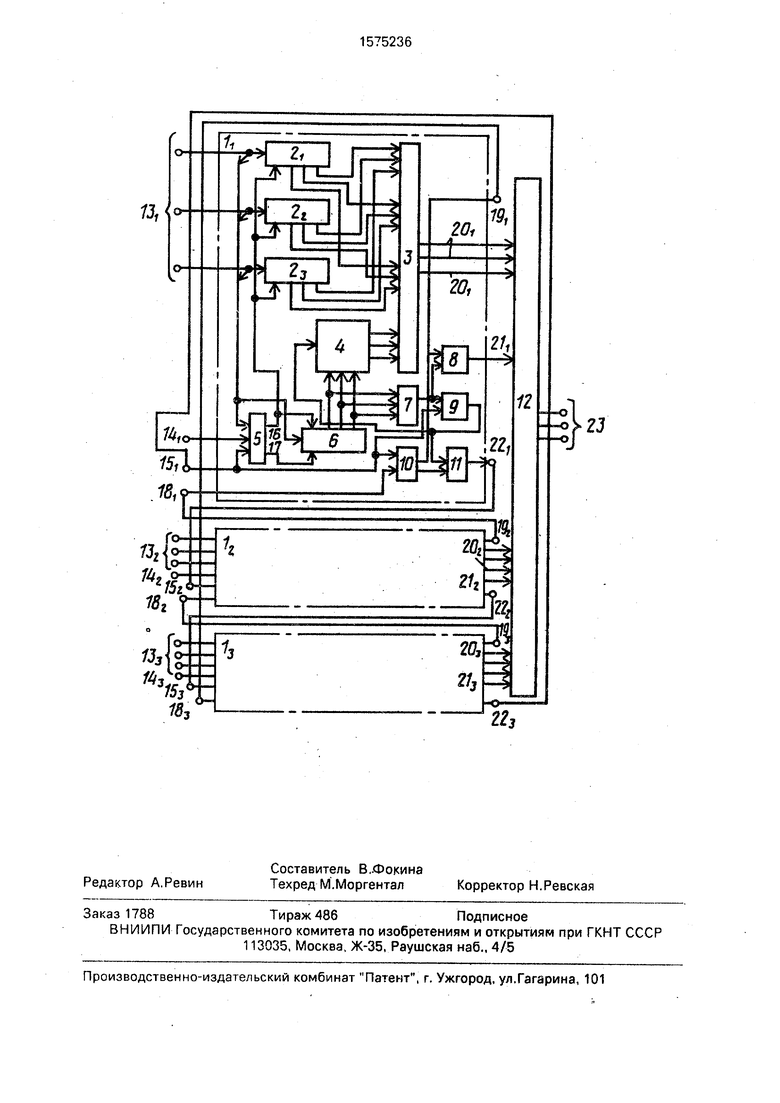

На чертеже изображена блок-схема предлагаемого устройства.

Устройство содержит блоки (ББП) 11 - 1 з буферной памяти, число которых равно числу приоритетов (на чертеже показан случай трех уровней приоритета), регистры 2i - 2з сдвига, первый коммутатор 3, блок 4 опроса регистра адреса, формирователь 5 импульсов синхронизации, регистр 6 адреса, элемент ИЛИ 7, первый 8 и второй 9 элементы И, элемент 10 памяти, элемент ИЛИ-НЕ 11, второй коммутатор 12, входы 13i - 13з записи, входы 14i - 14з синхронизации, входы 15i - 15з опроса, выходы 16 и 17 формирователя 5, входы 18i - 18з установки, выходы 19i - 19з установки, выходы 20ч - 20з ББП 1i - 1з, входы 21 т - 21з управления второго коммутатора 12, выходы 22t - 22з отсутствия заявок ББП 11 - 1з и информационные выходы 23 устройства.

.Формирователь 5 предназначен для синхронизации импульсов записи (сдвиг регистра 6 адреса вправо) и импульсов опроса (сдвиг регистра 6 адреса влево) отьосигель- но последовательности синхроимпульсов, поступающих от внешнего генератора.

сл

ю

Регистр б адреса представляет собой реверсивный регистр и служит для хранения адресов поступающих заявок.

Элемент ИЛИ 7 предназначен для определения наличия адреса заявки.

Первый элемент Л 8 ББП предназначен для формирования импульса управления для второго коммутатора 12.

Второй элемент И 9 ББП предназначен для формирования импульса опроса блока 4 данного ББП, если есть хотя бы одна заявка данного приоритета или если нет ни одной заявки в данном ББП для формирования импульса отсутствия заявок при помощи элемента ИЛИ-НЕ 11.

Элемент 10 памяти предназначен для хранения импульса опроса, поступающего по входу 15 опроса.

Устройство работает следующим образом.

На вход 14ч поступает периодическая последовательность синхроимпульсов от внешнего генератора. Формирователь 5 распределяет эту последовательность на две, каждая из которых разрешает прохождение импульсов со входов 13i на выход 16 и со входа 15i (с входа опроса) на выход 17, в результате чего осуществляется разнесение во времени моментов сдвигов вправо и влево в регистре 6 адреса. Хранящаяся в буфере кодограмма записывается параллельным кодом по входам 13i устройства в регистры 2i - 2з сдвига, число которых равно разрядности хранимого кода (для простоты на чертеже показан случай записи трехразрядного кода), а количество разрядов в каждом регистре (в том числе и регистре 6 адреса) равно количеству кодограмм, которое буфер хранит в данном конкретном случае.

При поступлении кодограмм по входам 13i записи формирователь 5 синхронизирует момент записи и сдвига в регистрах 2i - 2з по своему выходу 16, при этом 1, свидетельствующая о поступлении кодограммы, поступает в регистр 6 адреса (по входу записи) и содержимое регистра 6, как и содержимое регистров 2i 2з, сдвигается на один разряд вправо. Аналогично производится запись кодограммы более низкого приоритета в буферное запоминающее устройство по входам 132 и 13з записи.

Импульс опроса с входа 15i одновременно поступает на формирователь 5, на вход второго элемента И 9 и на вход записи элемента 10 памяти.

Формирователь 5 синхронизирует импульс опроса с синхроимпульсами, поступающими на вход 14i и синхронизированный импульс с выхода 17 сдвигает содержимое

(единицы поступивших кодограмм) регистра 6 назад влево (по входу реверса).

При поступлении импульса опроса на вход элемента 10 памяти на его прямом выходе появляется единичный сигнал.

Элемент ИЛИ 7, определив наличие хотя бы одной единицы (адреса кодограммы) в регистре 6, выдает единичный сигнал на второй вход элемента И 9 (на первом входе

0 которого - единичный импульс запроса), в результате чего элемент И 9 формирует импульс опроса для блока 4.

Блок 4 представляет собой пирамиду опроса, например, ключей, на которые вы5 водится информация (поразрядно) о наличии единиц в регистре 6 и опрос осуществляется до первой найденной единицы справо налево, после чего при нахождении этой единицы сигнал об этом

0 поступает на соответствующий вход управления коммутатора 3, переключающегося на вывод кодограммы с соответствующих входов коммутатора 3 на выходы 20i второго коммутатора 12.

5При этом на вход 211 управления второго коммутатора 12 подается единичный сигнал с выхода элемента И 8, гак как на один его вход поступает единичный сигнал с прямого выхода элемента 10 памяти, а на вто0 рой его вход поступает единичный сигнал с выхода элемента ИЛИ 7, в результате чего на выходах 23 устройства появляется информация с регистров 2ч - 2з ББП 11 (высшего приоритета).

5Если элемент ИЛИ 7 не обнаруживает

ни одной единицы (нет адресов кодограмм) в регистре 6, то на выходе элемента ИЛИ 7 - нулевой сигнал, на выходе элемента И 9 также нулевой сигнал, который и

0 поступает на первый вход элемента ИЛИ- НЕ 11, на второй вход которого поступает нулевой сигнал с элемента 10 памяти, если был импульс опроса, то тогда на выходе элемента ИЛИ-НЕ 11 формируется единич5 ный сигнал, который поступает через выход 22i отсутствия заявок на вход 152 ББП Ъ более низкого приоритета и для него этот сигнал является импульсом опроса. Этот импульс опроса запоминается в элементе

0 10 памяти ББП 12 и с его прямого выхода 19а (выход установки) поступает на вход 18i ББП 1i и на вход установки элемента 10 памяти ББП 1i в исходное состояние.

Если же и во втором ББП 12 нет адресов

5 кодограмм, то импульс опроса поступает на вход 15з опроса ББП 1з (низшего приоритета) и, если же и там не-находится ни одного адреса кодограмм, то тогда импульс опроса поступает на вход 15i опроса первого ББП, имеющего самый высокий приоритет.

Например, если 1 найдена в последнем разряде регистра 6 адреса ББП, то коммутатор 3 подключает выходы последнего разряда каждого из регистров 2ч - 2з ББП на входы 201 второго коммутатора 12 и с выходов коммутатора 12 на выходы 23 устройства.

Таким образом достигается возможность обработки приоритетных заявок и время поиска выдаваемой кодограммы составляет время задержки переключаемых элементов.

Устройство позволяет накапливать и выдавать приоритетные кодограммы в режиме асинхронной работы обменивающихся устройств в вычислительной аппаратуре различного назначения.

Формула изобретения Буферное запоминающее устройство, содержащее блок буферной памяти, включающий первый коммутатор, формирователь импульсов синхронизации, регистр адреса, блок опроса регистра адреса и регистры сдвига, информационные входы которых и информационный вход регистра адреса являются информационными входами устройства, выходы регистров сдвига подключены к информационным входам первого коммутатора, управляющие входы которого подключены к выходам блока опроса регистра адреса, входы группы которого соединены с выходами регистра адреса, вход сдвига вправо которого подключен к первому выходу формирователя импульсов синхронизации и к входам сдвига регистров сдвига, второй выход формирователя импульсов синхронизации соединен с входом сдвига влево регистра адреса, первый вход формирователя импульсов синхронизации подключен к информационному входу регистра адреса, второй и третий входы формирователя импульсов синхронизации являются соответственно входами синхронизации и опроса устройства, отличающееся тем, что, с целью расширения области применения устройства за счет возможности чтения данных по приоритетам, а также записи и хранения данных с приоритетами нескольких асинхронных потоков, в блок буферной памяти введены элемент ИЛИ, два элемента И, элемент ИЛИ-НЕ и Элемент памяти, а в устройство введены (К- 1) где К - число приоритетов аналогичных блоков буферной памяти и второй коммутатор, управляющие входы которого соединены с выходом первого элемента И соответствующего блока буферной памяти, первые входы первого и второго элементов И объединены и подключены к выходу элемента ИЛИ, входы которого соединены с

соответствующими выходами регистра адреса, второй вход второго элемента И и первый вход элемента памяти объединены и подключены к входу опроса устройства, второй вход элемента памяти является установочным входом устройства, первый выход элемента памяти соединен с первым входом элемента ИЛИ-НЕ, второй вход которого и вход блока опроса адреса объединены и подключены к выходу второго элемента И,

второй вход первого элемента И соединен с вторым выходом элемента памяти, является выходом установки первого блока буферной памяти и подключен к входу установки последнего блока буферной памяти, выход

элемента ИЛИ-НЕ является выходом отсутствия данных каждого блока буферной памяти и соединен с входом опроса последующего блока буферной памяти, кроме по- следнего, выход отсутствия данных

последнего блока буферной памяти соединен с входом опроса первого блока буферной памяти, выходы установки каждого блока буферной памяти, начиная со второго, подключены к соответствующим входам

предыдущего блока буферной памяти, выходы каждого блока буферной памяти соединены с информационными входами второго коммутатора, выходы которого являются информационными выходами устройства, входы записи каждого блока буферной памяти являются входами разрешения записи устройства.

I сЛ

°J

23

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1977 |

|

SU746735A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1405090A1 |

| МОДУЛЬ ДЛЯ РЕТРАНСЛЯЦИИ СООБЩЕНИЙ В КОММУТАЦИОННОЙ СТРУКТУРЕ | 2002 |

|

RU2222044C2 |

| Устройство программного опроса телеметрических каналов | 1984 |

|

SU1225032A1 |

| Устройство для согласования потоков телеметрических отсчетов | 1987 |

|

SU1543561A1 |

| Приемный модуль модели начального узла графа | 1990 |

|

SU1705838A1 |

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ | 1996 |

|

RU2107995C1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287236A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

Изобретение относится к вычислительной технике, в частности к буферным запоминающим устройствам в аппаратуре обмена дискретной информацией, и может быть использовано при разработке высокоскоростных буферов в цифровых устройствах. Целью изобретения является расширение области применения за счет чтения данных по приоритетам, а также записи и хранения данных с приоритетами нескольких асинхронных потоков. Это достигается тем, что в буферный блок памяти устройства, содержащий регистры сдвига, формирователь импульсов синхронизации, регистр адреса, коммутатор, блок опроса регистра адреса, введены элемент ИЛИ, первый и второй элементы И, элемент ИЛИ-НЕ и элемент памяти, а в устройство введены K-1 аналогичных буферных запоминающих блоков и второй коммутатор. Устройство позволяет накапливать и выдавать приоритетные кодограммы в режиме асинхронной работы обменивающихся устройств в вычислительной аппаратуре различного назначения. 1 ил.

| Буферное запоминающее устройство | 1977 |

|

SU746735A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1405090A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-06-30—Публикация

1987-10-21—Подача