о

СП

Изобретение относится к цифровой электроизмерительной технике и может быть использовано в устройствах измерения сдвига фаз двух электрических сигналов с цифровым выходом

Цель изобретения - повышение быстродействия цифрового фазометра при обеспечении требуемой точности измерения за счет одновременного автома- JQ тического выбора тактовой частоты при измерении периода Т у исследуемого сигнала и временного интервала д, пропорционального измеряемому сдвигу фаз lAf, в течение одного пе- 15 риода исследуемого сигнала.

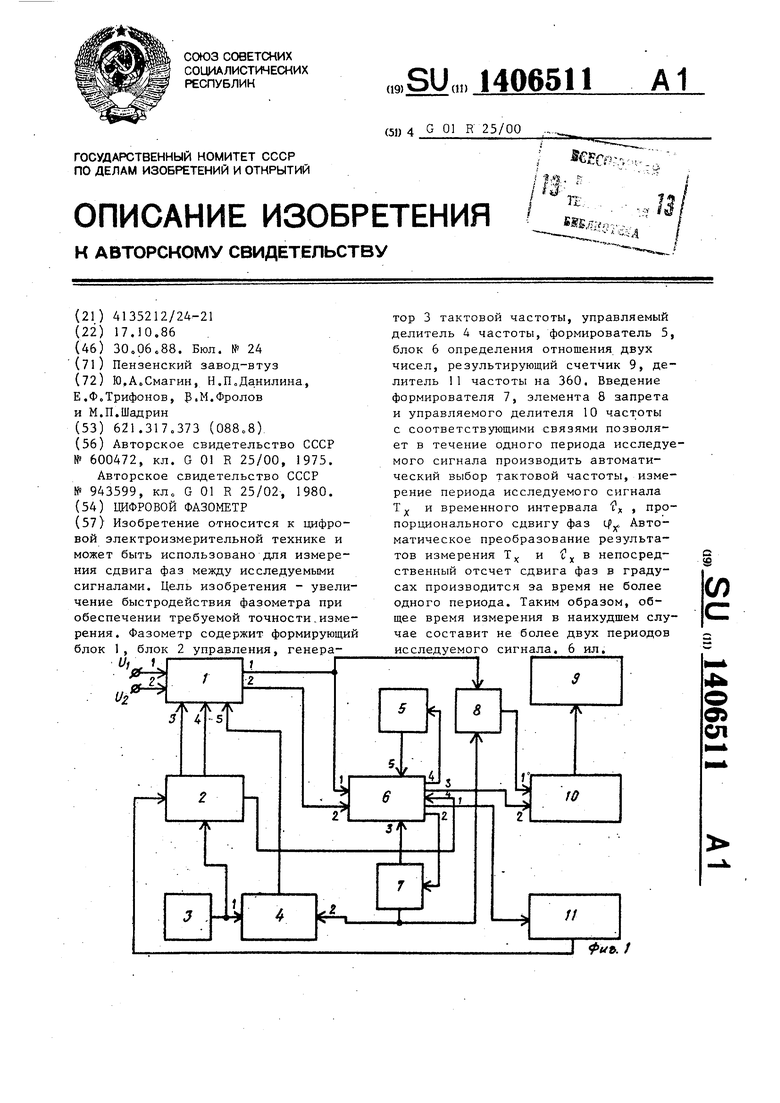

На фиг о 1 изображена структурная схема цифрового фазометра; на фиг.2 - блок-схема формирующего блока; на фиг.З - блок-схема первого управляе- 20 мого делителя частоты; на фиг. 4 - блок-схема блока определения отношения двух чисел; на фиг, 5 - блок-схема второго управляемого делителя частоты; на фиг о 6 - временные диаграм- 25 мы, поясняющие работу цифрового фазометра „

Цифровой фазометр содержит формирующий блок. 1, блок- 2 управления, генератор 3 тактовой частоты, первый 30 управляемый делитель 4 частоты, пер- вый формирователь 5 импульсов, блок 6 определения отношения двух чисел второй формирователь 7 импульсов, эле- мент 8 запрета, результирующий счет- 5 чик 9, второй управляемый делитель 10 частотв), делитель 11 частрты на 360 (д). Первый и второй входы цифро- вого фазометра соединены соответст- венно с первым и вторым входами фор- 40 мирующего блока 1, первый выход которого соединен с первым входом блока 6 определения отношения двух чисел и с запрещающим входом элемента 8 запрета, выход которого соединен дз с первым входом управляемого делителя 10 частоты, выход которого соединен с входом счетчика 9, Второй выход формирующего блока (ФВ) 1 соединен с вторым входом блока 6, первый CQ выход которого через делитель 11 соединен с первым входом блока 2, первый и второй выходы которого соединены соответственно с третьим и четвертым входами блока 1, пятый вход которого соединен с выходом делителя 4, первый вход которого соединен с вторым входом блока 2 и с выходом генератора 3. Второй вход делителя 4 соединен

с информационным входом элемента 8 и с первым выходом формирователя 7 имг

пульсов, второй выход которого соединен с третьим входом блока 6, второй и третий выходы которого соединены соответственно с входом формирователя 7 и вторым входом делителя 10« Третий выход блока 2 соединен с четвертым входом блока 6, четвертый выход которого через формирователь 5 соединен с пятым входом блока 6,

Блок-схема формирующего блока 1 содержит два формирователя 12 и 13 и два ключа 14 и 15, Первый и второй входы блока 1 через формирователи 12 и 13 соединены соответственно с первыми входами ключей 15„ Третий и четвертый входы блока 1 соединены соответственно с вторыми входами ключей 14 и 15, а пятый вход блока 1 соединен с третьими входами ключей 14 и 15о Выходы ключей 14 и 15 являются соответственно первым и вторым выходами блока 1 о.

Блок-схема первого управляемого делителя 4 частоты содержит делитель 16 частоты, блок 17 элементов совпа- дейий, двоичный счетчик 18, элемент ИЛИ 19. Первый вход делителя 4 соединен с входом делителя 16, i-выходы которого (где i 1,п) соединены с j-ми входами блока 17 (где J 1 ,ri), j-e выходы которого (где j 1,п) соединены с а-ми (где i 1,п) входами элемента ИЛИ 19, выход которого является выходом делителя 4«Второй вход делителя 4 соединен с входом счетчика 18, i-e выходы которого (где i 1 ,ri) соединены с j-ми входами (где J п + 1,2п) блока 17 i

Блок-схема блока 6 определения отношения двух чисел состоит из счетчика 20 сдвига фазы, блока 21 - элементов совпадений, общего счетчика 22, блока 23 элементов совпадений, счетчика 24 импульсов периода (СП) и двух элементов ИЛИ 25 и 26, Первый вход блока 6 соединен с первым входом счетчика 20, первый выход которого является четвертым выходом блока 6 о Второй вход блока 6 соединен с первым входом счетчика 24, первый выход которого является вторым выходом блока 6. Третий вход блока 6 соединен с вторым входом счетчика 24 1-е выходы которого (где i 2,n+l) соединены с j-ми входами (где J 1,п) блока 23, j-e выходы которо31А

го соединены с i-ми входами (где i 1; п) элемента ИЛИ 26, выход которого является первым выходом блока 6 Четвертый вход блока 6 соединен с входом счетчика 22, i-e выходы которого (где i 1, п) соединены с J-ми (где J п+1,2п) входами блока 23, а i-e (где i п + 1 , 2п) выходы счетчика 22 соединены с J-ми входами (где j 1,п)блока 21, j-e выходы ко- торого соединены с i-ми (где ,n) входами элемента ИЛИ 25, выход которого является третьим выходом блока 6 о Пятый вход блока 6 соединен с вто- рым входом счетчика 20, i-e выходы которого (где i 25П +1) соединены с j-ми входами (где J п+1,2п) блока 2 Г,

Блок-схема второго управляемого делителя 10 частоты состоит из двоичного счетчика 27 переполнений,блока

28элементов совпадений, делителя

29частоты и элемента ИЛИ 30„ Первый вход делителя 10 соединен с входом счетчика 27, i-e выходы которого

(где i 1 ji)соединены с j-ми входами (где j 1,п).блока 28, j-e выходы которого (где j 1,п) соединены с i-ми входами элемента ИЛИ 30, вы- ход которого является выходом делителя 10. Второй вход делителя 10 соединен с входом делителя 29, i-e выходы (где i 1,п) которого соединены с J-ми (где J п+1,2п) входами блока 2-8

Работа цифрового фазометра основана на автоматическом выборе тактовой частоты в течение одного периода входного сигнала при одновременном измерении .периода Т,; исследуемого сигнала и временного интервала D, пропорционального измеряемому сдвигу фаз if, и последующем автоматическом преобразовании результатов этих двух измерений в непосредственный отсчет сдвига фаз в градусах.

Цифровой фазометр работает следующим образом.

Перед началом измерения счетчик 9,делитель 11, счетчики 18, 20, 24 и 27 импульсом с блока 2 устанавливаются в нулевое состояние,. Формирователи 12 и 13 из входных сигналов

и, и и (диаграммы 31 и 32 на фиг,6) формируют импульсы, равные по длительности периоду Т исследуемого сигнала и времени /2 запаздывания (опережения) одного входного

сигнала относительно другого (диаграммы 33 и ЗА на фиг.6). Длительность этих импульсов определяет время заполнения импульсами тактовой частоты счетчиков 24 и 20 соответственно. В течение первого периода входного сигнала на счетчики 24 и 20 от генератора 3 через делитель 4 и блок 1 поступает максимальная тактовая частота f, соответствующая верхнему поддиапазону исследуемых частот.

При поступлении на вход с четчика 24 количества импульсов 2 , где п - разрядность двоичного счетчика, происходит переполнение этого счетчика частотой fg, которое осуществляется за отрезок времени Т , Импульс

переполнения длительностью «.---

о

поступает на счетчик 18, который через блок 17 управляет работой делителя 16 так, что с последнего через тот же блок 17, элемент ИЛИ 19 и ключ 15 на заполнение счетчика 24 постУпа- ет тактовая частота f;| т,е., вдвое меньшая по сравнению с предыдущей тактовой частотой (диаграммы 33 и 34 на фиг,б)о Этот же импульс переполнения счетчика 24 через формирователь 7 поступает в старший разряд счетчика 24 и записывает в нем 1. Таким образом, перед 1 ачалом заполнения тактовой частотой f в нем зафиксировано количество импульсов N 2 , что соответствует числу импульсов, поступивших на вход счетчика с учетом новой, уменьшенной вдвое, тактовой частоты. Действительно, количество импульсов N, поступивших с частотой fi fe/2 за отре- зок времени Т , равно N

- T-f ь 1 f 2.

Если время запаздьгоания одного входного сигнала относительно дру- го превышает отрезок времени Т, то одновременно с переполнением в счетчике 24 происходит переполнение в счетчике 20, Импульс переполнения счетчика 20 через формирователь 5 поступает в старший разряд счетчика 20, Таким образом, в счетчике 20 (как и в счетчике 24 перед началом аапол- нения его тактовой частотой f fo/2) зафиксировано количество поступивших на вход счетчика импульсов с учетом новой, уменьшенной вдвое, тактовой частоты.

Если при заполнении счетчиков

20

тоты вдвое

(т.е„ f,

-)

и 24 тактовой частотой f, вновь произойдет переполнение обоих счетчиков, то импульс переполнения счетчиков вызовет уменьшение тактовой часfi fo ..,

и через формирователи 7 и 5 поступит в старшие разряды счетчиков 20, 24 и запишет в них 1.

Если при заполнении счетчиков 20 и 24 тактовой Частотой f (где К 0,1,2,..,, га - номер частотного поддиапазона) произойдет переполнение только в счетчике 24р а в счетчике 20.переполнение отсутствует, что свидетельствует о завершении измерения временного интервала С ,; , то импульс переполнения счетчика 24 через элемент 8, открытый отсутствием сигнала и X с блока I, поступает в счетчик 27. Таким образом, в счетчике 20 будет зафиксировано число, пропорциональное интервалу

f

к

(1)

в счетчике 27 фиксируется количество ;1 переполнений счетчика 24 при измере НИИ интервала ()J а уменьшенная

fK., к/2 бу- 24

; вдвое тактовая частота

;дет поступать только в счетчик

I (диаграмма 34 на фиг.6). Подобным

образом будет осуществляться измене|ние тактовой частоты и фиксация коли:чества переполнений счетчика 24 до

|конца интервала Ту, а в счетчике 9

получается число,

периоду Т, т.е.

X

пропорциональное

5

0

По окончанию периода Tj происходит считывание информации со счетчиков 20 и 24 следующим образом. С блока 2 поступает команда, по которой импульсы максимальной тактовой частоты fp поступают в счетчик 22.

Выходные уровни триггеров разрядов счетчиков 20 и 24 управляют потенциальными входами блоков 21 и 23, а выходные сигналы триггеров разрядов счетчика 22 поступают на импульс ные входы блоков 21 и 23с. При совпадении обоих сигналов на входах блоков 21 и 23 появляются сигналы, которые проходят через элемент ИЛИ 25 и делитель 29, управляемый кодом в счетчике 27, через блок 28, элемент ИЛИ. 30 на результируюш;ий счетчик 9 и через элемент ИЛИ 26 на делитель 11.

Состояние блоков 21 и 23 и, следовательно, суммарную частоту на выходе элементов ИЛИ 25 и 26.задают состояния триггеров счетчиков 20,24 и 5 22. Например, триггеры самых старших

двоичных разрядов счетчиков 20 и 24 . управляют элементами блоков 21 и 23 совпадений, на которые подаются сигналы от триггера самого младшего разряда счетчика 22„

Суммарная частота с выхода элемента ИЛИ 26 равна

0

Jr. . f W, V

(4)

где Ng - числовая емкость каждого из счетчиков 20, 24 и 22.

Принимая во внимание выражение (2), получим

Тх- f i

f

N,

(5)

| название | год | авторы | номер документа |

|---|---|---|---|

| Высокочастотный фазометр | 1981 |

|

SU1125554A1 |

| Цифровой фазометр | 1982 |

|

SU1075186A1 |

| Инфранизкочастотный фазометр | 1980 |

|

SU1057878A1 |

| ЦИФРОВОЙ ФАЗОМЕТР | 1971 |

|

SU310195A1 |

| Измеритель группового времени запаздывания | 1990 |

|

SU1725180A2 |

| Цифровой фазометр | 1979 |

|

SU983578A1 |

| Цифровой фазометр | 1982 |

|

SU1045155A1 |

| Преобразователь сдвига фаз в код | 1980 |

|

SU943599A1 |

| Цифровой фазометр | 1985 |

|

SU1265647A2 |

| Цифровой фазометр | 1977 |

|

SU705371A1 |

Изобретение относится к цифровой электроизмерительной технике и может быть использовано для измерения сдвига фаз между исследуемыми сигналами. Цель изобретения - увеличение быстродействия фазометра при обеспечении требуемой точности.измерения. Фазометр содержит формирующий блок 1, блок 2 управления, генератор 3 тактовой частоты, управляемый делитель 4 частоты, формирователь 5, блок 6 определения отношения двух чисел, результирующий счетчик 9, делитель 11 частоты на 360. Введение формирователя 7, элемента В запрета и управляемого делителя 10 частоты с соответствующими связями позволяет в течение одного периода исследуемого сигнала производить автоматический выбор тактовой частоты, измерение периода исследуемого сигнала Т. и временного интервала f , пропорционального сдвигу фаз Lfjjo Автоматическое преобразование результатов измерения Т. t в непосредственный отсчет сдвига фаз в градусах производится эа время не более одного периода. Таким образом, общее время измерения в наихудшем случае составит не более двух периодов исследуемого сигнала. 6 ил. с (Л

N

,f

(2)

где 1 - номер частотного поддиапазона ().

Учитывая, что после каждого переполнения тактовая частота уменьшается в.два раза, то количество 1 переполнений в счетчике 24 при измереНИИ интервала ( как

1 log, (- -).

)

определится

(3)

Таким образом, в течение одного йериода Т у происходит получение кодов и/j и N .J. в счетчиках 20 и 24 соответственно

выхода элеменСуммарная частота с та ИЛИ 25 равна

f . -Lt . f

Ч N« 0

0

5

Учитывая выражение (I), получим

о f

- ; I к f.

f

N,

(6)

Импульсы с выхода элемента ИЛИ 25 поступают на делитель 29, который через блок 28 управляется счетчиком 27 переполнений так, что на выходе элемента ИЛИ 30 суммарная частота получается в 2 раз меньше, чем на входе делителя 29, Тое на выходе элемента ИЛИ 30 частота импульса равна

°

Учитывая вьфажение (6) и лучим

Я -г 1- X 1 1

f -, . f

кГ в

При поступлении на делитель 11 360 импульсов суммарной частоты f вьдается импульс переполнения на блок 2,.который прекращает доступ тактовой частоты на счетчик 22. Импульсы частоты f (J поступают в счетчик 22 в течение времени

.t - .t - --.(8)

где N 360 - коэффициент деления частоты делителя 11,

Число подсчитанных импульсов в счетчике 9 за интервал At равно N at f,

Принимая во внимание выражение (5), (7) и (8), получим

N 360 .

т.е число будет равно непосредственно сдвигу фаз в градусах

Таким образом, время Т, измерения сдвига фаз цифрового фазометра складывается из периода исследуемого сигнала, в течение которого измеряются период Т j( исследуемого сигнала и временной интервал о , пропорциональный измеряемому сдвигу фаз 0, и времени автоматического преобразования результатов измерения Т и 11X в непосредственный отсчет сдвига фаз в градусах, которое зависит от требуемой погрешности измерения и быстродействия используемых элементов , т, е,

Т + 4t, ,

Составляющая ut (как следует из выражений (8) и (4))тем меньше, чем больше частота f генератора тактовой частоты и значение отношения и чем меньше коэффициент деления делителя 11. Частота f ограничивается максимально достигаемым быстродействием компонент схемы Отношение (j изменяется в пределах поддиапазона от 1/2 до 1 о Что касается коэффициента деления делителя 11, то он выбирается, исходя из условия получения требуемой точности измерения Таким образом, если, например, значение коэффициента деления выбран равным 360, что соответствует желаемой точности измерения сдвига фаз в 1 ,

значение fj 1

МГц и отношение

т. -Ж- (худшее быстродействие),

то составляющая будет равна 0,72 х X 10 Со Следовательно, при измере10 НИИ сдвига фаз сигналов низкой .и инфранизкой частот составляющая /it . соизмерима с периодом исследуемых сигналов,, Таким образом, общее время измерения в наихудшем случае составит

15 не более двух периодов исследуемого сигнала, в то время, как в прототипе оно составляет три периода, т.е„ при обеспечении требуемой погрешности измерения увеличивается быстродейст20 вие фазометра, в/результате чего снижается динамическая погрешность измерения сдвига фаз.

Предлагаемый цифровой фазометр может использоваться в качестве лабо25 раторного измерительного прибора, а

также в качестве блока в цифровьГх - системах обработки информации и автоматического контроля,

30 Формула изобретения

Цифровой фазометр,.содержащий формирующий блок, первый и второй входы которого соединены с входными клеммами устройства, первый и второй выходы формирующего блока соединены соответственно с первым и вторым входами блока определения отношения двух чисел, первый выход которого через делитель частоты подсоединен к первому входу блока управления i первый выход которого соединен с третьим входом формирующего блока, четвертый вход которого соединен с выходом первого управляемого делителя частоты, первый вход которого соединен с выходом генератора тактовой частоты, первый выход формирователя импульсов соединен с третьим входом блока определения отношения двух чисел, второй выход которого соединен с входом формирователя импульсов, второй выход которого соединен с вторым входом первого управляемого делителя частоты, а четвертый вход блока определения отношения двух чисел соединен с вторым выходом блока управления, а также результирующий счетчик, о т.- личающийся тем, что, с

35

40

45

50

55

целью повышения быстродействия за счет одновременного автоматического выбора тактовой частоты, измерения периода исследуемого сигнала и временного интервала, пропорционального сдвигу фаз, в течение одного периода исследуемого сигнала, в него введены второй формирователь импульсов, второй управляемый делитель частоты и элемент запрета, информационный вход которого соединен с вторым выходом первого формирователя импульсов, запрещающий вход соединен с первым выходом формирующего блока.

12

/4

13

15

/

фиг.2

О

а выход - с входом второго управляемого делителя частоты, выход которого соединен с входом результирующего счетчика, а второй вход - с третьим выходом блока определения отношения двух чисел, четвертый выход которого через второй формирователь импульсов соединен с пятым входом блока определения отно- щения двух чисел, при 3ffOM выход генератора тактовой частоты соединен с вторым входом блока управления, третий выход которого соединен с пя- тым входом формирующего блока.

. J

ive.

31

31

3Z

Ifo fof/f.

Тх

II - I - fffo Ifo

V/V.,

Ktl

///i

фиг.6

| Цифровой фазометр мгновенных значений | 1975 |

|

SU600472A1 |

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

| Преобразователь сдвига фаз в код | 1980 |

|

SU943599A1 |

Авторы

Даты

1988-06-30—Публикация

1986-10-17—Подача