о:

to

4315

25

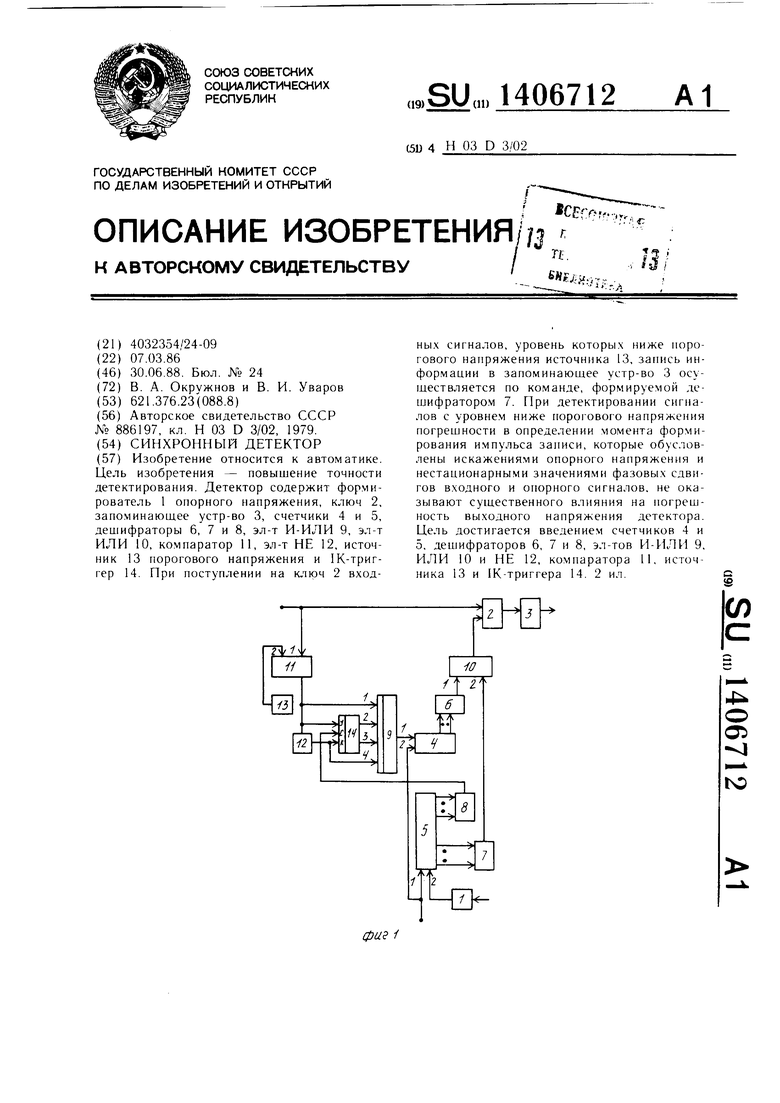

Изобретение относится к автоматике и может быть использовано для синхронной демодуляции амплитудно-модулированных сигналов.

Цель изобретения - повышение точности детектирования.

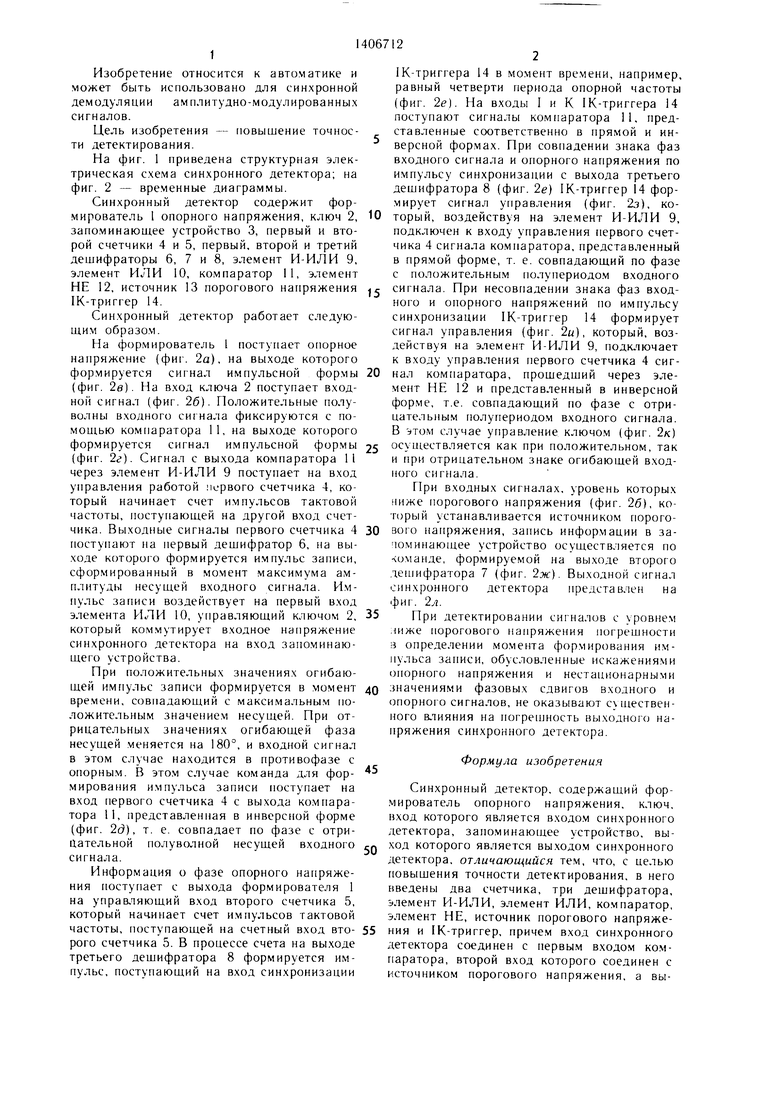

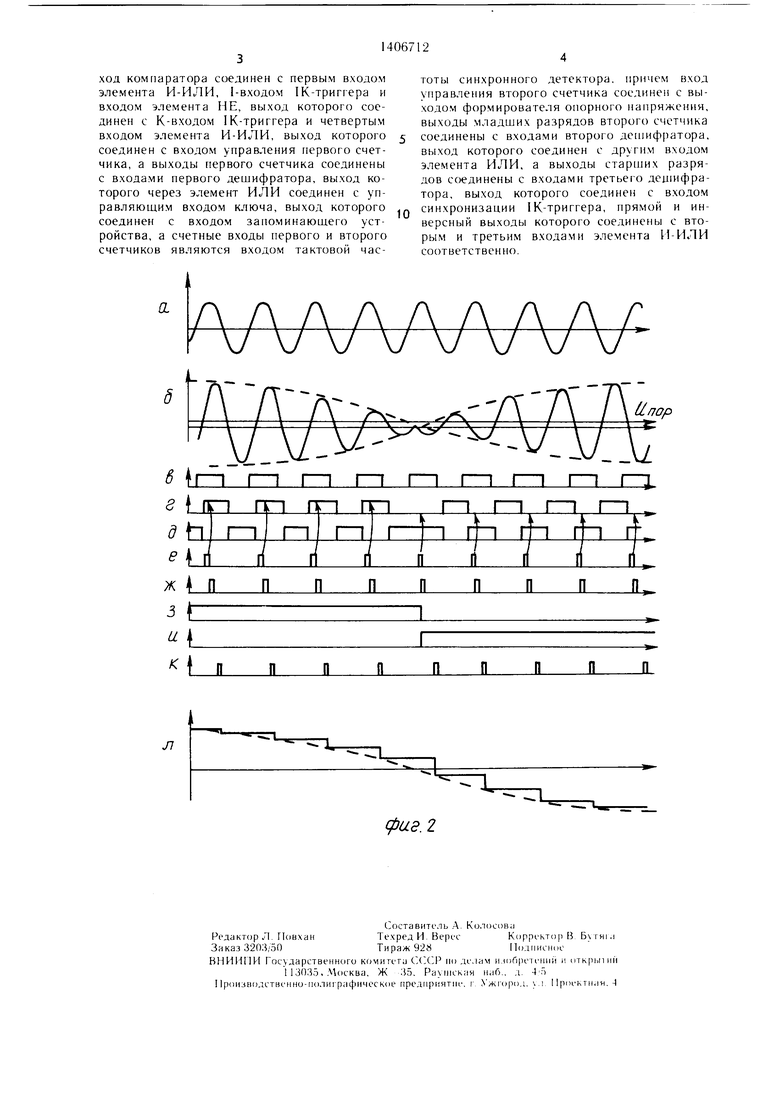

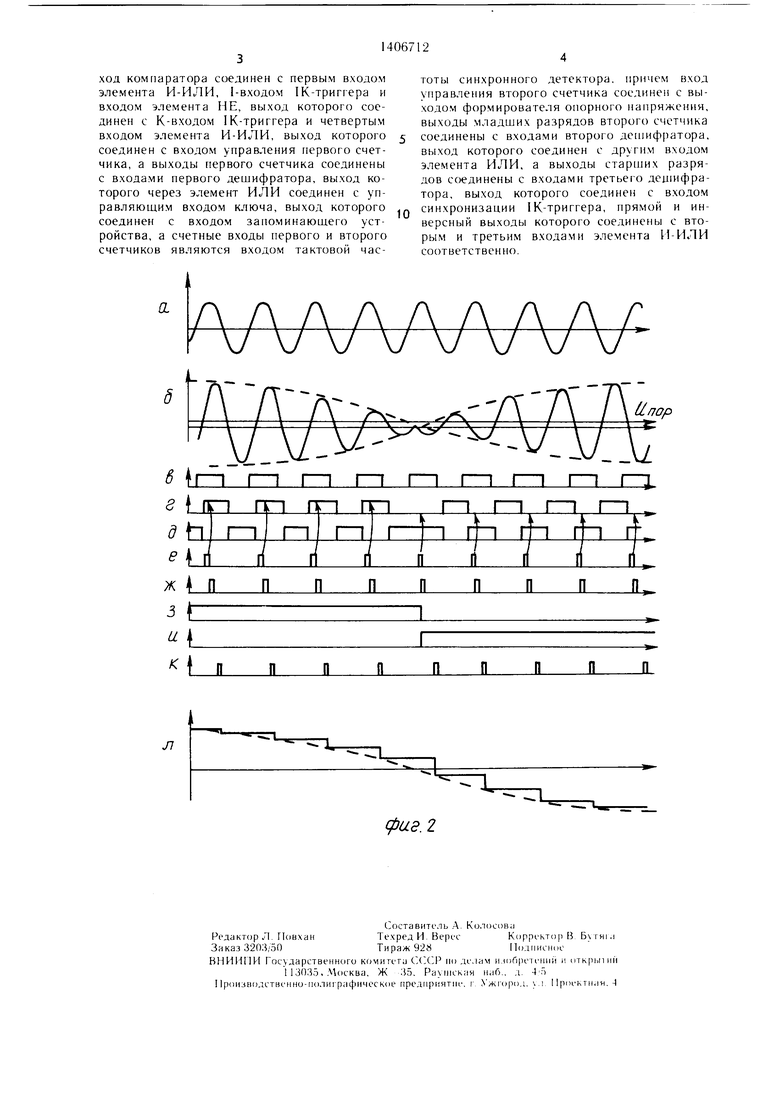

На фиг. 1 приведена структурная электрическая схема син.хронного детектора; на фиг. 2 - временные диаграммы.

Синхронный детектор содержит формирователь 1 опорного напряжения, ключ 2, Ю запоминающее устройство 3, первый и второй счетчики 4 и 5, первый, второй и третий дешифраторы 6, 7 и 8, элемент И-ИЛИ 9, элемент ИЛИ 10, компаратор 11, элемент НЕ 12, источник 13 порогового напряжения 1К-триггер 14.

Синхронный детектор работает следую- Ш.ИМ образо.м.

На формирователь 1 поступает опорное напряжение (фиг. 2а), на выходе которого формируется сигнал импульсной формы 20 (фиг. 2в). На вход ключа 2 поступает входной сигнал (фиг. 26). Положительные полуволны входного сигнала фиксируются с по- мошью компаратора 11, на выходе которого формируется сигнал импульсной формы (фиг. 2г). Сигнал с выхода компаратора 11 через элемент И-ИЛИ 9 поступает на вход управления работой первого счетчика 4, который начинает счет импульсов тактовой частоты, 11остуг1аюш.ей на другой вход счетчика. Выходные сигналы первого счетчика 4 30 поступают на первый дешифратор 6, на выходе которого формируется и.мпульс записи, сформированный в момент максимума амплитуды несуплей входного сигнала. Импульс записи воздействует на первый вход элемента ИЛИ 10, управляющий ключом 2, который коммутирует входное напряжение синхронного детектора на вход запоминающего устройства.

При положительных значениях огибающей импульс записи формируется в момент дО вре.мени, совпадающий с максимальным положительным значением несущей. При отрицательных значениях огибающей фаза несущей меняется на 180°, и входной сигнал в этом случае находится в противофазе с опорным. В это.м случае команда для формирования и.мпульса записи поступает на вход первого счетчика 4 с выхода компаратора 11, представленная в инверсной форме (фиг. 2д), т. е. совпадает по фазе с отрицательной полуволной несушей входного сигнала.

Информация о фазе опорного напряжения поступает с выхода формирователя 1 на управляющий вход второго счетчика 5, который начинает счет импульсов тактовой

35

45

50

1К-триггера 14 в момент времени, например, равный четверти периода опорной частоты (фиг. 2е). На входы I и К 1К-триггера 14 поступают сигналы компаратора 11, представленные соответственно в прямой и инверсной формах. При совпадении знака фаз входного сигнала и опорного напряжения по импульсу синхронизации с выхода третьего дешифратора 8 (фиг. 2е) 1К-триггер 14 формирует сигнал управления (фиг. 2з), который, воздействуя на элемент И-ИЛИ 9, подключен к входу управления первого счетчика 4 сигнала компаратора, представленный в прямой форме, т. е. совпадающий по фазе с положительным полупериодо.м входного сигнала. При несовпадении знака фаз входного и опорного напряжений по импульсу синхронизации 1К-триггер 14 формирует сигнал управления (фиг. 2и), который, воздействуя на элемент И-ИЛИ 9, подключает к входу управления первого счетчика 4 сигнал KOMtiapaTQpa, прошедший через элемент НЕ 12 и представленный в инверсной форме, т.е. совпадающий по фазе с отрицательным полупериодо.м входного сигнала. В этом случае управление ключом (фиг. 2к) осуществляется как при положительном, так и при отрицательном знаке огибающей входного сигнала.

При входных сигналах, уровень которых ниже порогового напряжения (фиг. 26), который устанавливается источником порогового напряжения, запись информации в запоминающее устройство осуществляется по чоманде, формируемой на выходе второго дешифратора 7 (фиг. 2ж). Выходной сигнал синхронного детектора представлен на фиг. 2л.

При детектировании сигналов с уровнем :и1же порогового напряжения погрешности я определении момента формирования импульса загшси, обусловленные искажениями опорного напряжения и нестационарными значениями фазовых сдвигов входного и опорного сигналов, не оказывают существенного влияния на погрешность выходного напряжения синхронного детектора.

Формула изобретения

Синхронный детектор, содержащий формирователь опорного напряжения, ключ, вход которого является входом синхронного детектора, запоминающее устройство, выход которого является выходо.м синхронного детектора, отличающийся тем, что, с целью повыщения точности детектирования, в него введены два счетчика, три дешифратора, элемент И-ИЛИ, элемент ИЛИ, ко.мпаратор, элемент НЕ, источник порогового напряжечастоты, поступающей на счетный вход вто- 55ния и 1К-триггер, приче.м вход синхронного рого счетчика 5. В процессе счета на вы.ходедетектора соединен с первым входом ком- третьего дешифратора 8 формируется им-г аратора, второй вход которого соединен с пульс, поступающий на вход синхронизацииисточником порогового напряжения, а вы5

5

0 0

О

5

5

0

1К-триггера 14 в момент времени, например, равный четверти периода опорной частоты (фиг. 2е). На входы I и К 1К-триггера 14 поступают сигналы компаратора 11, представленные соответственно в прямой и инверсной формах. При совпадении знака фаз входного сигнала и опорного напряжения по импульсу синхронизации с выхода третьего дешифратора 8 (фиг. 2е) 1К-триггер 14 формирует сигнал управления (фиг. 2з), который, воздействуя на элемент И-ИЛИ 9, подключен к входу управления первого счетчика 4 сигнала компаратора, представленный в прямой форме, т. е. совпадающий по фазе с положительным полупериодо.м входного сигнала. При несовпадении знака фаз входного и опорного напряжений по импульсу синхронизации 1К-триггер 14 формирует сигнал управления (фиг. 2и), который, воздействуя на элемент И-ИЛИ 9, подключает к входу управления первого счетчика 4 сигнал KOMtiapaTQpa, прошедший через элемент НЕ 12 и представленный в инверсной форме, т.е. совпадающий по фазе с отрицательным полупериодо.м входного сигнала. В этом случае управление ключом (фиг. 2к) осуществляется как при положительном, так и при отрицательном знаке огибающей входного сигнала.

При входных сигналах, уровень которых ниже порогового напряжения (фиг. 26), который устанавливается источником порогового напряжения, запись информации в запоминающее устройство осуществляется по чоманде, формируемой на выходе второго дешифратора 7 (фиг. 2ж). Выходной сигнал синхронного детектора представлен на фиг. 2л.

При детектировании сигналов с уровнем :и1же порогового напряжения погрешности я определении момента формирования импульса загшси, обусловленные искажениями опорного напряжения и нестационарными значениями фазовых сдвигов входного и опорного сигналов, не оказывают существенного влияния на погрешность выходного напряжения синхронного детектора.

Формула изобретения

Синхронный детектор, содержащий формирователь опорного напряжения, ключ, вход которого является входом синхронного детектора, запоминающее устройство, выход которого является выходо.м синхронного детектора, отличающийся тем, что, с целью повыщения точности детектирования, в него введены два счетчика, три дешифратора, элемент И-ИЛИ, элемент ИЛИ, ко.мпаратор, элемент НЕ, источник порогового напряже5ния и 1К-триггер, приче.м вход синхронного детектора соединен с первым входом ком- г аратора, второй вход которого соединен с источником порогового напряжения, а выход компаратора соединен с первым входом элемента И-ИЛИ, 1-входом 1К-триггера и входом элемента НЕ, выход которого соединен с К-входом 1К-триггера и четвертым входом элемента И-ИЛИ, выход которого соединен с входом управления первого счетчика, а выходы первого счетчика соединены с входами первого дешифратора, выход которого через элемент ИЛИ соединен с уп- равляюш.им входом ключа, выход которого соединен с входом запоминающего устройства, а счетные входы первого и второго счетчиков являются входом тактовой час

тоты синхронного детектора, причем вход управления второго счетчика соединен с выходом формирователя опорного напряжения, выходы младших разрядов второго счетчика соединены с входами второго де пифратора, выход которого соединен с другим входом элемента ИЛИ, а выходы старших разрядов соединены с входами третьего дешифратора, выход которого соединен с входом синхронизации 1К-триггера, прямой и инверсный выходы которого соединены с вторым и третьим входами элемента И-ИЛИ соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель параметров комплексных сопротивлений | 1989 |

|

SU1751690A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В НАПРЯЖЕНИЕ | 1987 |

|

RU2056700C1 |

| Сигнализатор наличия пламени | 1983 |

|

SU1168992A1 |

| Частотно-фазовый детектор | 2019 |

|

RU2721416C1 |

| Самонастраивающееся устройство управления | 1983 |

|

SU1130830A1 |

| Устройство для демодуляции фазоманипулированного сигнала | 1981 |

|

SU1054923A1 |

| КОГЕРЕНТНЫЙ ПРИЕМНИК РЛС С ЦИФРОВЫМ УСТРОЙСТВОМ ДЛЯ АМПЛИТУДНОЙ И ФАЗОВОЙ КОРРЕКТИРОВКИ КВАДРАТУРНЫХ СОСТАВЛЯЮЩИХ ПРИНИМАЕМОГО СИГНАЛА | 2004 |

|

RU2273860C2 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2004 |

|

RU2261531C1 |

| Устройство для корреляционного приема фазоманипулированных псевдослучайных сигналов | 1984 |

|

SU1252964A1 |

| Синхронный детектор | 1989 |

|

SU1706005A1 |

Изобретение относится к автоматике. Цель изобретения - повышение точности детектирования. Детектор содержит фор.ми- рователь 1 опорного напряжения, ключ 2, запоминающее устр-во 3, счетчики 4 и 5, дешифраторы 6, 7 и 8, эл-т И-ИЛИ 9, эл-т ИЛИ 10, компаратор II, эл-т НЕ 12, источник 13 порогового напряжения и 1К-триг- гер 14. При поступлении на ключ 2 входны.х сигналов, уровень которы.х ниже порогового напряжения источника 13, запись информации в запоминающее устр-во 3 осуществляется по команде, формируемой дешифратором 7. При детектировании сигналов с уровнем ниже порогового напряжения погрешности в определении момента фор.ми- рования импульса записи, которые обусловлены искажениями опорного напряжения и нестационарными значениями фазовы.х сдвигов в.ходного и опорного сигналов, не оказывают существенного влияния на погрешность выходного напряжения детектора. Цель достигается введением счетчиков 4 и 5, дешифраторов 6, 7 и 8, эл-тов И-ИЛИ 9, ИЛИ Ю и НЕ 12, компаратора И, источника 13 и 1К-триггера 14. 2 ил.

е.

ж LJL

3 tz: L

LJL

л

Vtinop

| Фазочувствительный детектор | 1979 |

|

SU886197A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-30—Публикация

1986-03-07—Подача