1

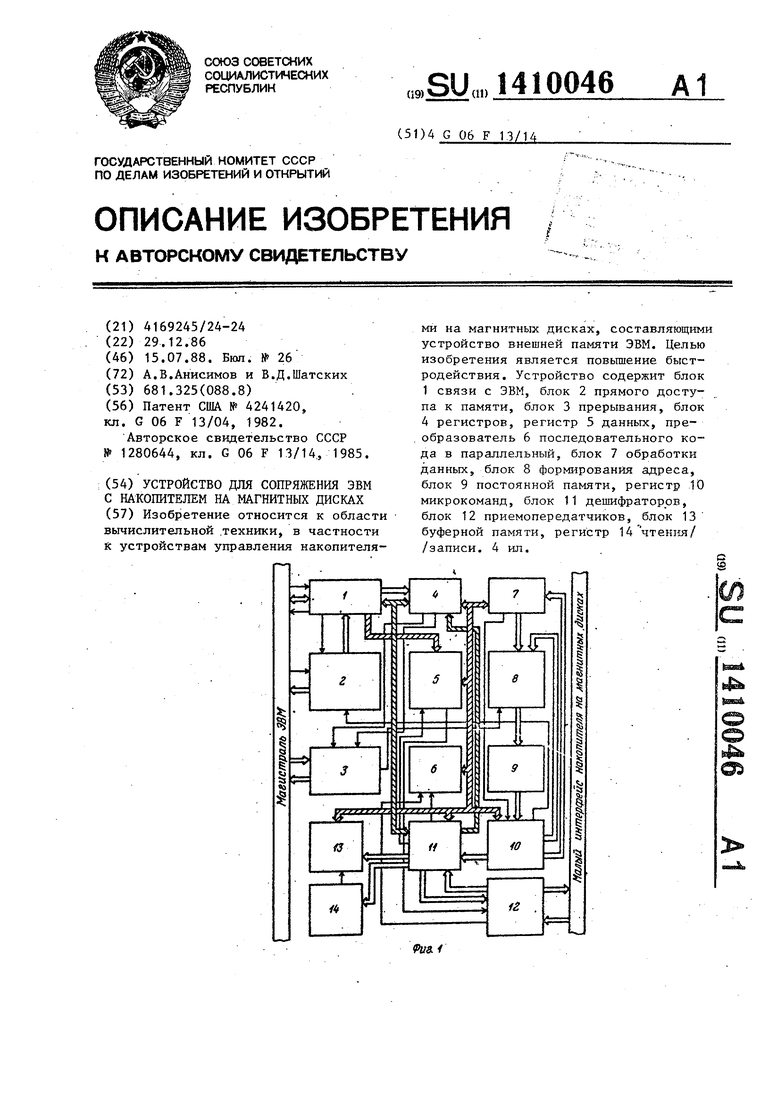

Изобретение относится к области вычислительной техники, в частности к устройствам управления накопителями на магнитных дисках, составляющим устройство внешней памяти ЭВМ,

Целью изобретения является повышение быстродействия устройства.

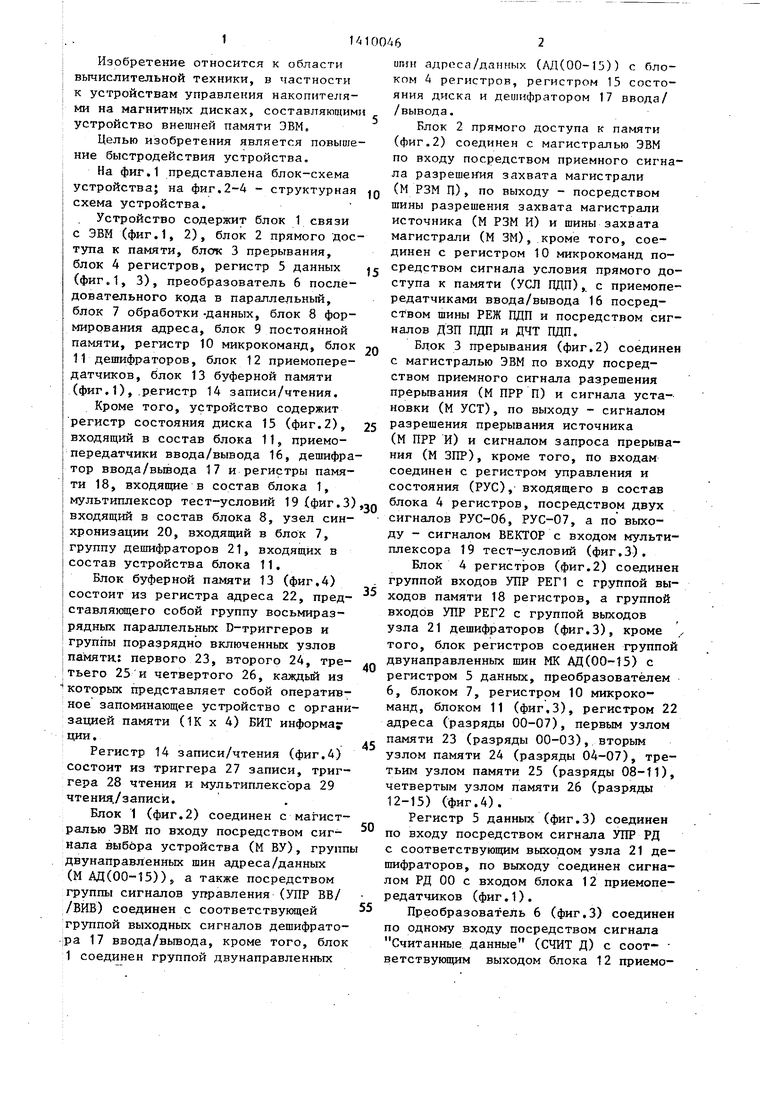

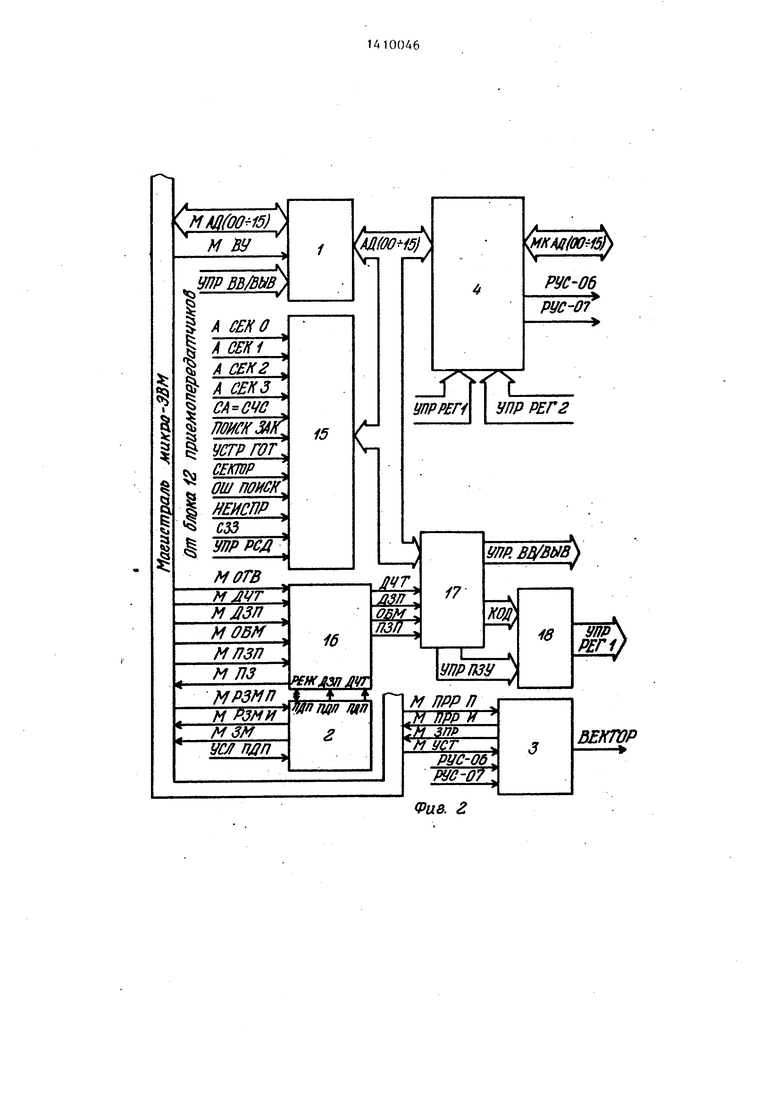

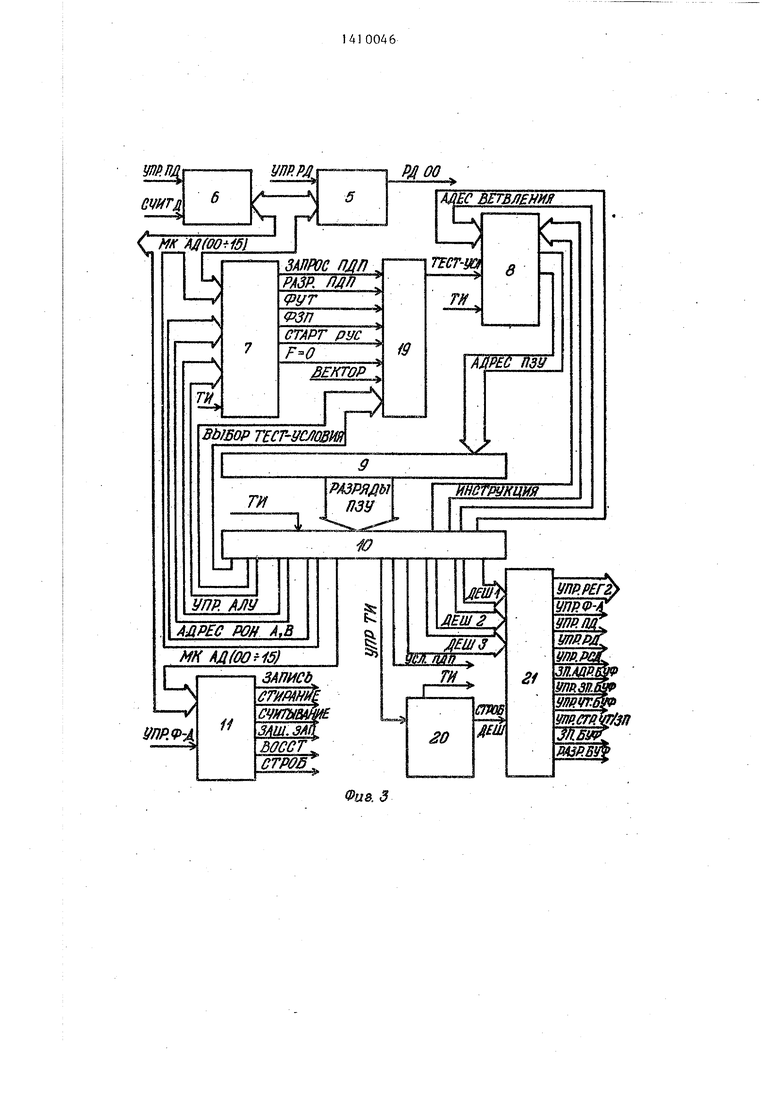

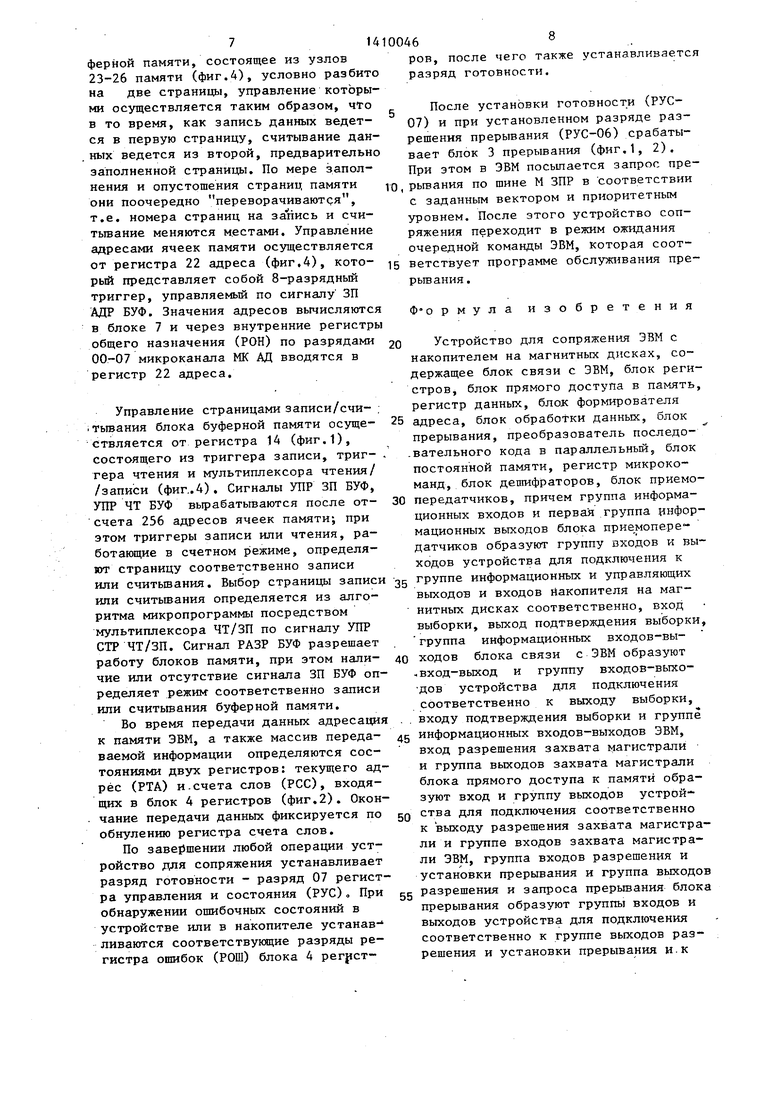

На фиг,1 представлена блок-схема устройства; на фиг,2-4 - структурная схема устройства.

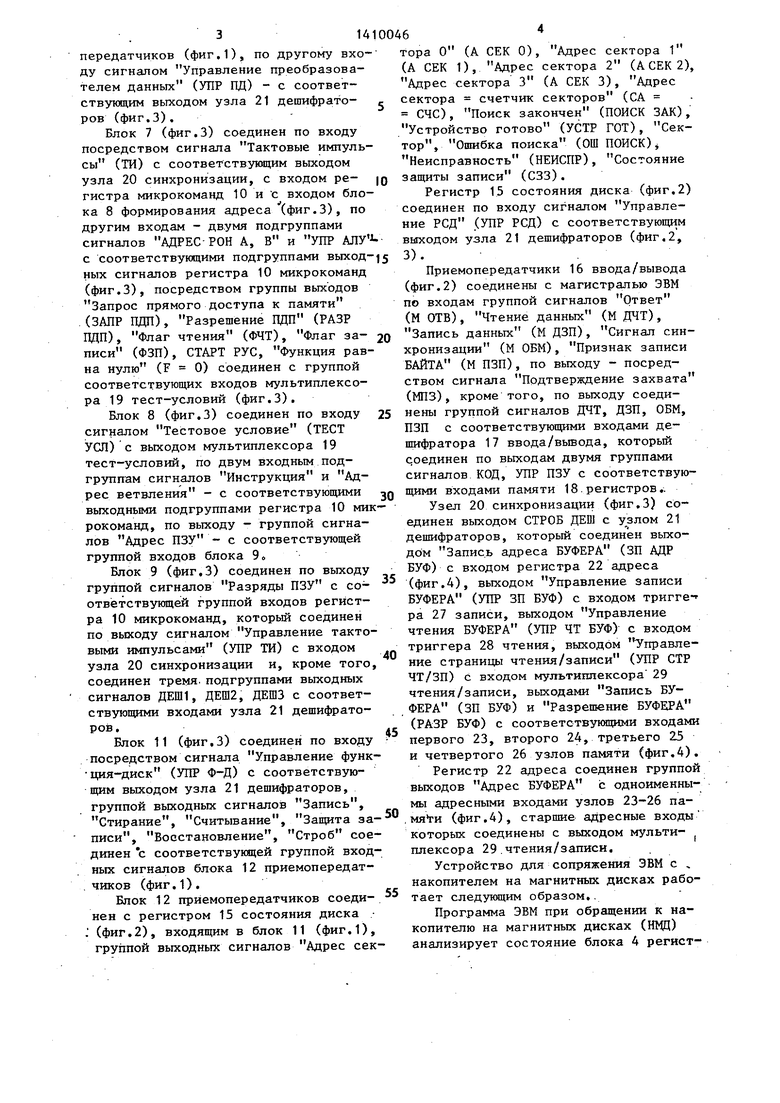

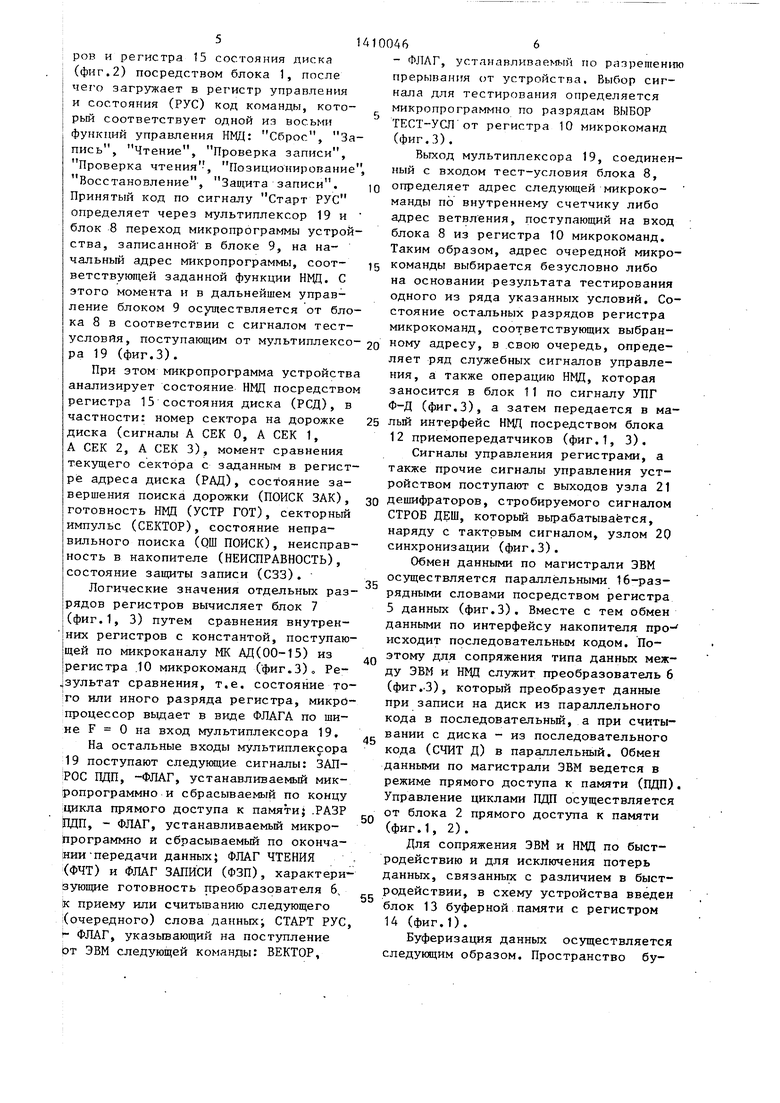

Устройство содержит блок 1 связи с ЭВМ (фиг.1, 2), блок 2 прямого доступа к памяти, блок 3 прерывания, блок 4 регистров, регистр 5 данных (фиг.1, 3), преобразователь 6 последовательного кода в параллельный, блок 7 обработки -данных, блок 8 формирования адреса, блок 9 постоянной памяти, регистр 10 микрокоманд, блок 11 дешифраторов, блок 12 приемопередатчиков, блок 13 буферной памяти (фиг,1),.регистр 14 записи/чтения.

Кроме того, устройство содержит регистр состояния диска 15 (фиг.2), входящий в состав блока 11, приемопередатчики ввода/вывода 16, дешифратор ввода/вьпвода 17 и регистры памяКЛ

БЛОК 3 прерывания (фиг,2) соединен с магистралью ЭВМ по входу посредством приемного сигнала разрешения прерьгеания (М ПРР П) и сигнала установки (М УСТ), по выходу - сигналом разрешения прерывания источника (М ПРР И) и сигналом запроса прерывания (М ЗПР), кроме того, по входам соединен с регистром управления и состояния (РУС), входящего в состав

40

ти 18, входящие в состав блока 1, мультиплексор тест-условий 19(фиг.3),з0 блока 4 регистров, посредством двух входящий в состав блока 8, узел син- сигналов РУС-06, РУС-07, а по выходу - сигналом ВЕКТОР с входом мультиплексора 19 тест-условий (фиг.З),

Блок 4 регистров (фиг.2) соединен . группой входов УПР РЕП с группой вы- 35 ходов памяти 18 регистров, а группой входов УПР РЕГ2 с группой выходов узла 21 дешифраторов (фиг.З), кроме того, блок регистров соединен группой двунаправленных шин МК АД(00-15) с регистром 5 данных, преобразователем 6, блоком 7, регистром 10 микрокоманд, блоком 11 (фиг.З), регистром 22 адреса (разряды 00-07), первым узлом памяти 23 (разряды 00-03), вторым узлом памяти 24 (разряды 04-07), третьим узлом памяти 25 (разряды 08-11), четвертым узлом памяти 26 (разряды 12-15) (фиг.4).

Регистр 5 данных (фиг.З) соединен по входу посредством сигнала УПР РД с соответствующим выходом узла 21 дешифраторов, по выходу соединен сигналом РД 00 с входом блока 12 приемопередатчиков (фиг.1).

Преобразователь 6 (фиг.З) соединен

хронизации 20, входящий в блок 7, группу дешифраторов 21, входящих в состав устройства блока 11.

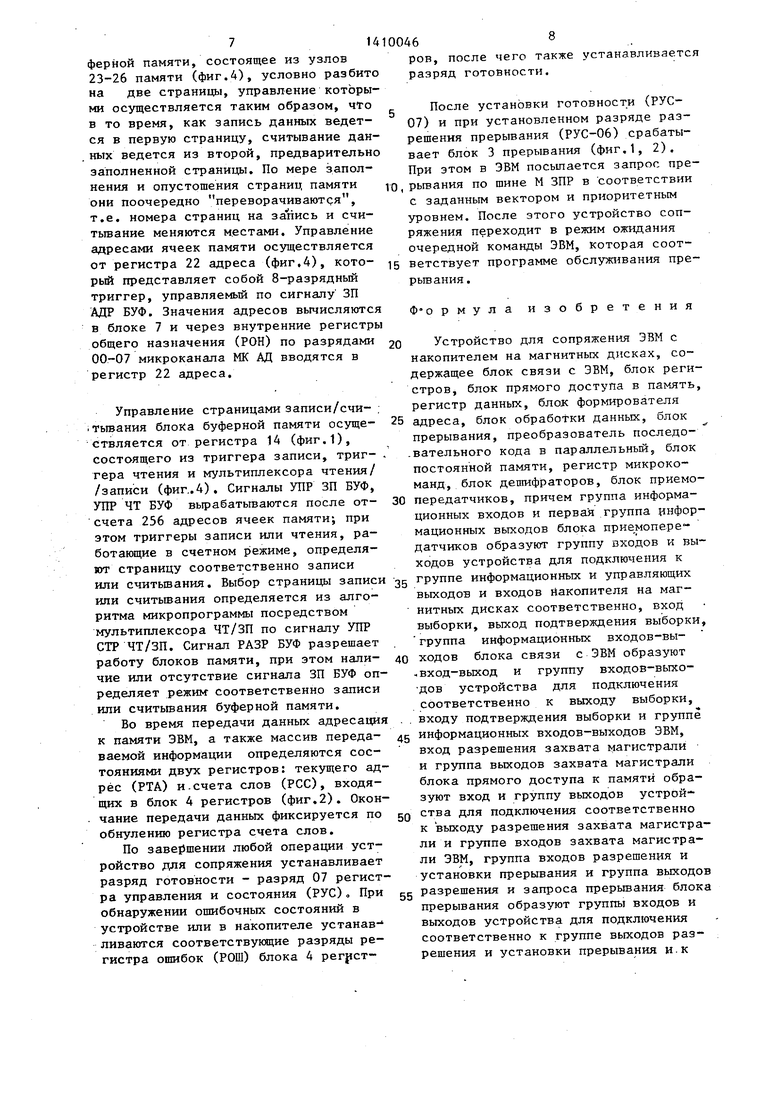

Блок буферной памяти 13 (фиг.4) состоит из регистра адреса 22, пред- ставлякяцего собой группу восьмираз- I рядных параллельных D-триггеров и I группы поразрядно включенных узлов I памяти.: первого 23, второго 24, тре- Iтьего 25 и четвертого 26, каждьй из которых представляет собой оперативное запоминающее устройство с организацией памяти (1К X 4) БИТ информау ции,

Регистр 14 записи/чтения (фиг.4) состоит из триггера 27 записи, триггера 28 чтения и мультиплексора 29 чтения./записй.

Блок 1 (фиг.2) соединен с магистралью ЭВМ по входу посредством сигнала выббра устройства (М ВУ), группы двунаправленньк шин адреса/данных (М АД(00-15))5 э также посредством группы сигналов управления (УПР ВВ/ /вив) соединен с соответствуюцей группой выходных сигналов дешифратора 17 ввода/вьшода, кроме того, блок 1 соединен группой двунаправленных

45

50

55

по одному входу посредством сигнала Считанные данные (СЧИТ Д) с соот- ветствующим выходом блока 12 приемо10

jnООДб2

ипгн адреса/данных (АД(00-15)) с блоком 4 регистров, регистром 15 состояния диска и дешифратором 17 ввода/ /вывода.

Блок 2 прямого доступа к памяти (фиг,2) соединен с магистралью ЭВМ по входу посредством приемного сигнала разрешения захвата магистрали (М РЗМ П), по выходу - посредством шины разрешения захвата магистрали источника (М РЗМ И) и шины захвата магистрали (М ЗМ), кроме того, соединен с регистром 10 микрокоманд посредством сигнала условия прямого доступа к памяти (УСЛ ПДП), с приемопередатчиками ввода/вывода 16 посредством шины РЕЖ ПДП и посредством сигналов ДЗП ПДП и ДЧТ ПДП.

БЛОК 3 прерывания (фиг,2) соединен с магистралью ЭВМ по входу посредством приемного сигнала разрешения прерьгеания (М ПРР П) и сигнала установки (М УСТ), по выходу - сигналом разрешения прерывания источника (М ПРР И) и сигналом запроса прерывания (М ЗПР), кроме того, по входам соединен с регистром управления и состояния (РУС), входящего в состав

15

25

,з0 блока 4 регистров, посредством двух сигналов РУС-06, РУС-07, а по выходу - сигналом ВЕКТОР с входом мультиплексора 19 тест-условий (фиг.З),

по одному входу посредством сигнала Считанные данные (СЧИТ Д) с соот- ветствующим выходом блока 12 приемо314

передатчиков (фиг.1), по другому входу сигналом Управление преобразователем данных (УПР ПД) - с соответствующим выходом узла 21 дешифраторов (фиг.З).

Блок 7 (фиг.З) соединен по входу посредством сигнала Тактовые импуль

сы (ТИ) с соответствующим выходом узла 20 синхронизации, с входом ре- ю гистра микрокоманд 10 и с входом блока 8 формирования адреса (фиг.З), по другим входам - двумя подгруппами сигналов АДРЕС-РОН А, В и УПР с соответствующими подгруппами выход- 5 ных сигналов регистра 10 микрокоманд (фиг.З), посредством группы выходов Запрос прямого доступа к памяти . (ЗАПР ЩЩ), Разрешение ПДП (РАЗ ПДП), Флаг чтения (ФЧТ), Флаг за- 20 писи (ФЗП), СТАРТ РУС, Функция равна нулю (F 0) соединен с группой соответствующих входов мультиплексора 19 тест-условий (фиг.З).

Блок 8 (фиг.З) соединен по входу 25 сигналом Тестовое условие (ТЕСТ УСЛ) с выходом мультиплексора 19 тест-условий, по двум входным под- групяам сигналов Инструкция и Адрес ветвления - с соответствующими п выходными подгруппами регистра 10 микрокоманд, по выходу - группой сигналов Адрес ПЗУ - с соответствующей группой входов блока 9

Блок 9 (фиг.З) соединен по выходу группой сигналов Разряды ПЗУ с соответствующей группой входов регистра 10 микрокоманд, который соединен по выходу сигналом Управление такто- (УПР ТИ) с входом

35

выми импульсами узла 20 синхронизации и, кроме того, соединен тремя, подгруппами выходных сигналов ДЕШ1, ДЕШ2, ДЕШЗ с соответствующими входами узла 21 дешифраторов.

Блок 11 (фиг.З) соединен по входу посредством сигнала Управление функ- ция-диск (УПР Ф-Д) с соответствующим выходом узла 21 дешифраторов, группой выходных сигналов Запись,

40

45

Тора О (А СЕК 0), Адрес сектора Г (А СЕК 1), Адрес сектора 2 (А СЕК 2), Адрес сектора 3 (А СЕК 3), Адрес сектора счетчик секторов (СА СЧС), Поиск закончен (ПОИСК ЗАК), Устройство готово (УСТР ГОТ), Сектор, Опшбка поиска (ОШ ПОИСК) Неисправность (НЕИСПР), Состояние защиты записи (СЗЗ).

Регистр 15 состояния диска (фиг.2) соединен по входу сигналом Управление РСД (УПР РСД) с соответствующим выходом узла 21 дешифраторов (фиг.2, 3).

Приемопередатчики 16 ввода/вывода (фиг.2) соединены с магистралью ЭВМ по входам группой сигналов Ответ (М ОТВ), Чтение данных (М ДЧТ), Запись данных (М ДЗП), Сигнал синхронизации (М ОБМ), Признак записи БАЙТА (М ПЗП), по выходу - посредством сигнала Подтверждение захвата (МПЗ), кроме того, по выходу соединены группой сигналов ДЧТ, ДЗП, ОБМ, ПЗП с соответствующими входами дешифратора 17 ввода/вьюода, который соединен по выходам двумя группами сигналов КОД, УПР ПЗУ с соответствующими входами памяти 18. регистров..

Узел 20 синхронизации (фиг.З) соединен выходом СТРОБ ДЕ01 с 21 дешифраторов, который соединен выходом Запись адреса БУФЕРА (ЗП АДР БУФ) с входом регистра 22 адреса (фиг.4), выходом Управление записи БУФЕРА (УПР ЗП БУФ) с входом тригге- ра 27 записи, выходом Управление чтения БУФЕРА (УПР ЧТ БУФ) с входом триггера 28 чтения, выходом Управление страницы чтения/записи (УПР СТР ЧТ/ЗП) с входом мультиплексора 29 чтения/записи, выходами Запись БУФЕРА (ЗП БУФ) и Разрешение БУФЕРА (РАЗР БУФ) с соответствукящми входами первого 23, второго 24, третьего 25 и четвертого 26 узлов памяти (фиг.4).

Регистр 22 адреса соединен группой выходов Адрес БУФЕРА с одноименны- мы адресными входами узлов 23-26 па Стирание, Считывание, Защита за-,мя ги (фиг.4), старшие адресные входы

писи, Восстановление, Строб соединен с соответствукяцей группой входных сигналов блока 12 приемопередатчиков (фиг.1).

Блок 12 приемопередатчиков соединен с регистром 15 состояния диска . (фиг.2), входящим в блок 11 (фиг.1), группой выходных сигналов Адрес сек55

которых соединены с выходом мультиплексора 29.чтения/записи.

Устройство для сопряжения ЭВМ с , накопителем на магнитных дисках работает следующим образом..

Программа ЭВМ при обращении к накопителю на магнитных дисках (НМД) анализирует состояние блока 4 регнст-

п

5

0

5

Тора О (А СЕК 0), Адрес сектора Г (А СЕК 1), Адрес сектора 2 (А СЕК 2), Адрес сектора 3 (А СЕК 3), Адрес сектора счетчик секторов (СА СЧС), Поиск закончен (ПОИСК ЗАК), Устройство готово (УСТР ГОТ), Сектор, Опшбка поиска (ОШ ПОИСК) Неисправность (НЕИСПР), Состояние защиты записи (СЗЗ).

Регистр 15 состояния диска (фиг.2) соединен по входу сигналом Управление РСД (УПР РСД) с соответствующим выходом узла 21 дешифраторов (фиг.2, 3).

Приемопередатчики 16 ввода/вывода (фиг.2) соединены с магистралью ЭВМ по входам группой сигналов Ответ (М ОТВ), Чтение данных (М ДЧТ), Запись данных (М ДЗП), Сигнал синхронизации (М ОБМ), Признак записи БАЙТА (М ПЗП), по выходу - посредством сигнала Подтверждение захвата (МПЗ), кроме того, по выходу соединены группой сигналов ДЧТ, ДЗП, ОБМ, ПЗП с соответствующими входами дешифратора 17 ввода/вьюода, который соединен по выходам двумя группами сигналов КОД, УПР ПЗУ с соответствующими входами памяти 18. регистров..

Узел 20 синхронизации (фиг.З) соединен выходом СТРОБ ДЕ01 с 21 дешифраторов, который соединен выходом Запись адреса БУФЕРА (ЗП АДР БУФ) с входом регистра 22 адреса (фиг.4), выходом Управление записи БУФЕРА (УПР ЗП БУФ) с входом тригге- ра 27 записи, выходом Управление чтения БУФЕРА (УПР ЧТ БУФ) с входом триггера 28 чтения, выходом Управление страницы чтения/записи (УПР СТР ЧТ/ЗП) с входом мультиплексора 29 чтения/записи, выходами Запись БУФЕРА (ЗП БУФ) и Разрешение БУФЕРА (РАЗР БУФ) с соответствукящми входами первого 23, второго 24, третьего 25 и четвертого 26 узлов памяти (фиг.4).

Регистр 22 адреса соединен группой выходов Адрес БУФЕРА с одноименны- мы адресными входами узлов 23-26 па,мя ги (фиг.4), старшие адресные входы

которых соединены с выходом мультиплексора 29.чтения/записи.

Устройство для сопряжения ЭВМ с , накопителем на магнитных дисках работает следующим образом..

Программа ЭВМ при обращении к накопителю на магнитных дисках (НМД) анализирует состояние блока 4 регнст-

ров и регистра 15 состояния диска (фнг.2) посредством блока 1, после чег о загружает в регистр управления и состояния (РУС) код команды, который соответствует одной из восьми функций управления НЩ: Сброс, Запись, Чтение, Проверка записи, Проверка чтения - , Позиционирование Восстановление, Защита записи. Принятый код по сигналу Старт РУС определяет через мультиплексор 19 и блок 8 переход микропрограммы устройства, записанной в блоке 9, на начальный адрес микропрограммы, соответствующей заданной функции ИОД. С этого момента и в дальнейшем управление блоком 9 осуществляется от блока 8 в соответствии с сигналом тест- условия, поступающим от мультиплексора 19 (фиг.З).

При этом микропрограмма устройства анализирует состояние НВД посредством регистра 15 состояния диска (РСД), в частности: номер сектора на дорожке диска (сигналы А СЕК О, А СЕК 1, А СЕК 2, А СЕК 3), момент сравнения текущего сектора с заданным в регистре адреса диска (РАД), состояние завершения поиска дорожки (ПОИСК ЗАК), готовность НМД (УСТ ГОТ), секторный импульс (СЕКТОР), состояние неправильного поиска (ОШ ПОИСК), неисправность в накопителе (НЕИСПРАВНОСТЬ), состояние защиты записи (СЗЗ).

Логические значения отдельных разрядов регистров вычисляет блок 7 (фиг.1, 3) путем сравнения внутренних регистров с константой, поступающей по микроканалу Ж АД(00-15) из регистра .10 микрокоманд (фиг.З), Ре зультат сравнения, т.е. состояние то го или иного разряда регистра, микропроцессор вьщает в виде ФЛАГА по шине F О на вход мультиплексора 19.

На остальные входы мультиплексора 19 поступают следукяцие сигналы: ЗАП- РОС ПДП, -ФЛАГ, устанавливаемый микропрограммно и сбрасываемый по концу :цикла прямого доступа к памяти} .РАЗР ПДП, - ФЛАГ, устанавливаемьй микропрограммно и сбрасываемый по окончании -передачи данных; ФЛАГ ЧТЕНИЯ (ФЧТ) и ФЛАГ ЗАПИСИ (ФЗП), характеризующие готовность преобразователя 6, к приему или считыванию следующего

(очередного) слова данных; СТАРТ РУС Ь- ФЛАГ, указывающий на постзшление от ЭВМ следующей команды: ВЕКТОР,

5

0

5

0

5

0

5

0

5

- ФЛАГ, устанавливаемый по разрешению прерывания от устройства. Выбор сигнала для тестирования определяется микропрограммно по разрядам ВЫБОР ТЕСТ-УСЛ от регистра 10 микрокоманд (фиг.З).

Выход мультиплексора 19, соединенный с входом тест-условия блока 8, определяет адрес следующей микрокоманды по внутреннему счетчику либо адрес ветвления, поступающий на вход блока 8 из регистра 10 микрокоманд. Таким образом, адрес очередной микрокоманды выбирается безусловно либо на основании результата тестирования одного из ряда указанных условий. Состояние остальных разрядов регистра микрокоманд, соответствующих выбранному адресу, в свою очередь, определяет ряд служебных сигналов управления, а также операцию НМД, которая заносится в блок 11 по сигналу УПГ Ф-Д (фиг.З), а затем передается в малый интерфейс НЩ посредством блока 12 приемопередатчиков (фиг.1, 3).

Сигналы управления регистрами, а также прочие сигналы управления устройством поступают с выходов узла 21 дешифраторов, стробируемого сигналом СТРОБ ДЕШ, который вырабатывается, наряду с тактовым сигналом, узлом 20 синхронизации (фиг.З).

Обмен данными по магистрали ЭВМ осуществляется параллельными 16-разрядными словами посредством регистра 5 данных (фиг.З), Вместе с тем обмен данными по интерфейсу накопителя про- исходит последовательным кодом. Поэтому для сопряжения типа данных между ЭВМ и НЩ служит преобразователь 6 (фиг. З), который преобразует данные при записи на диск из параллельного кода в последовательный, а при считывании с диска - из последовательного кода (СЧИТ Д) в параплельный. Обмен данными по магистрали ЭВМ ведется в режиме прямого доступа к памяти (ПДП). Управление циклами ПДП осуществляется от блока 2 прямого доступа к памяти (фиг.1, 2),

Для сопряжения ЭВМ и НЩ по быстродействию и для исключения потерь данных, связанных с различием в быстродействии, в схему устройства введен блок 13 буферной памяти с регистром 14 (фиг,1).

Буферизация данньк осуществляется следукщим образом. Пространство буферной памяти, состоящее из узлов 23-26 памяти (фиг.4), условно разбито на две страницы, управление которы- мк осуществляется таким образом, что в то время, как запись данных ведется в первую страницу, считывание дан- . ных ведется из второй, предварительно заполненной страницы. По мере заполнения и опустощения страниц памяти они поочередно переворачиваются, т.е. номера страниц на запись и счи- тьгоание меняются местами. Управление адресами ячеек памяти осуществляется от регистра 22 адреса (фиг,4), который представляет собой 8-разрядный триггер, управляемый по сигналу ЗП АДР БУФ. Значения адресов вьтисляются в блоке 7 и через внутренние регистры общего назначения (РОН) по разрядами 00-07 микроканала Ж АД вводятся в регистр 22 адреса.

Управление страницами записи/счи- тьгеания блока буферной памяти осуществляется от регистра 14 (фиг.1), состоящего из триггера записи, триг- . гера чтения и мультиплексора чтения/ /записи (фиг..4). Сигналы УПР ЗП БУФ, УТГР ЧТ БУФ вырабатьгоаются после отсчета 256 адресов ячеек памяти; при этом триггеры записи или чтения, работающие в счетном режиме, определяют страницу соответственно записи

о - - о я ы

14100468

ров, после чего также разряд готовности.

После установки готовности (РУС- 07) и при установленном разряде раз- рещения прерывания (РУС-06) срабатывает блок 3 прерывания (фиг.1, 2). При этом в ЭВМ посыпается запрос прерывания по шине М ЗПР в соответствии с заданным вектором и приоритетным уровнем. После этого устройство сопряжения переходит в режим ожидания очередной команды ЭВМ, которая соответствует программе обслуживания пре- рьш ания.

Ф-ормула изобретения

Устройство для сопряжения ЭВМ с накопителем на магнитных дисках, содержащее блок связи с ЭВМ, блок регистров, блок прямого доступа в память, регистр данных, блок формирователя

адреса, блок обработки данных, блок прерывания, преобразователь последо- вательного кода в параллельньй, блок постоянной памяти, регистр микрокоманд, блок дешифраторов, блок приемопередатчиков, причем группа информационных входов и первая группа информационных выходов блока приемопередатчиков образуют группу входов к выходов устройства для подключения к

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления накопителями на магнитных дисках | 1988 |

|

SU1532956A1 |

| Устройство для сопряжения ЭВМ с накопителями на магнитных дисках | 1985 |

|

SU1280644A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1983 |

|

SU1141418A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1984 |

|

SU1254498A2 |

| Устройство для сопряжения ЭВМ с периферийной системой | 1989 |

|

SU1635188A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для сопряжения двух ЭВМ с абонентами | 1988 |

|

SU1529237A1 |

Изобретение относится к области вычислительной .техники, в частности К устройствам управления накопителями на магнитных дисках, составляющими устройство внешней памяти ЭВМ. Целью изобретения является повышение быстродействия. Устройство содержит блок 1 связи с ЭВМ, блок 2 прямого доступа к памяти, блок 3 прерывания, блок 4 регистров, регистр 5 данных, преобразователь 6 последовательного кода в параллельный, блок 7 обработки данных, блок 8 формирования адреса, блок 9 постоянной памяти, регистр 10 микрокоманд, блок 11 дешифраторов, блок 12 приемопередатчиков, блок 13 буферной памяти, регистр 14 чтения/ /записи. 4 ил. с ()

или считьшания. Выбор страницы записи 35 группе информационных и управляющих

или считьгоания определяется из алгоритма микропрограммы посредством мультиплексора ЧТ/ЗП по сигналу УПР СТР ЧТ/ЗП. Сигнал РАЗР БУФ разрешает работу блоков памяти, при зтом наличие или отсутствие сигнала ЗП БУФ определяет режик соответственно записи или считьшания буферной памяти.

Во время передачи данных адресация к памяти ЭВМ, а также массив передаваемой информации определяются состояниями двух регистров: текущего адрес (РТА) и.счета слов (РСС), входящих в блок 4 регистров (фиг,2). Окон- чание передачи данных фиксируется по обнулению регистра счета слов.

По завершении любой операции устройство для сопряжения устанавливает разряд готовности - разряд 07 регистра управления и состояния (РУС), При обнаружении ошибочных состояний в устройстве или в накопителе устанав- ливаются соответствующие разряды регистра ошибок (РОШ) блока 4 регрствыходов и входов Накопителя на маг- нитных дисках соответственно, вход выборки, выход подтверждения выборки, группа информационных входов-выходов блока связи с ЭВМ образуют вход-вькод и группу входов-выхо- дов устройства для подключения соответственно к выходу выборки,

входу подтверждения выборки и группе

информационных входов-выходов ЭВМ, вход разрешения захвата магистрали и группа выходов захвата магистрали блока прямого доступа к памяти образуют вход и группу выходов устройства для подключения соответственно к выходу разрешения захвата магистрали и группе входов захвата магистрали ЭВМ, группа входов разрешения и установки прерывания и группа выходов

разрешения и запроса прерывания блока прерывания образуют группы входов и выходов устройства для подключения соответственно к группе выходов разрешения и установки прерывания и.к

Irpynne входов разрешения и запроса рерывания ЭВМ, при этом первая груп- а информационных выходов блока связи ЭВМ соединена с группой входов раз- ешения записи блока регистров, пер- ая группа информационных входов-выводов которого соединена с первой : руппой выходов блока дешифраторов и

1

группой информационных входов-выхо- 10 дов блока- дешифраторов, первый выход

,0В блока связи с ЭВМ -группа управ- :яющих входов и информационный выход :оторого соединены соответственно- с группой выходов управления передачей и с входом задания режима блока пряного доступа к памяти, вход разреше- 1ИЯ которого соединен с информацион- 1ЫМ выходом регистра микрокоманд, первая группа информационных выходов t синхровход которого соединены соот- ;етственно с группой адресных и уп- |авляющих входов и тактовым выходом |лока обработки данных, группа информационных выходов которого соеди- ена с первой группой информационных кходов блока формирования адреса, иторая группа информационных входов которого соединена с второй группой информационных: выходов регистра мик- окоманд, группа информационных вхо- ов которого соединена с группой информационных выходов блока постоянной ;амяти, группа адресных входов кото- ого соединена с группой информацион- ых выходов блока формирования адре- а, вход логш1еского условия которого оединен с выходом блока прерьгоания, :ервый и второй входы управления ре- :имом которого соединены с первым и |торым информационными выходами блока егистров, вторая группа информацион- ых входов-выходов которого соединена с| группой входов логического условия блока обработки данных, с первой Группой информационных входов блока 4ешифраторов, с группой информацион15

20

25

30

35

40

45

которого.соединен с входом запуска преобразователя последовательлого кода в параллельный, информационный вход которого соединен с информационным выходом блока приемопередатчиков, информационный вход которого соединен с информационным выходом регистра данных, синхровход которого соединен с вторым выходоц блока дешифраторов, вторая группа выходов и третья группа информационных входов которого соединены соответственно с группой управляющих входов и с второй группой информационных выходов, блока приемопередатчиков, третья группа выходов блока дешифраторов соединена с группой синхровходов блока регистров, вторая группа информационных выходов блока связи с ЭВМ соединена с группой информационных входов регистра данных, отличающееся тем, что, с целью повышения быстродействия, в него введены блок буферной памяти и регистр чтения записи, причем вторая группа информационных входода- ;вьгходов блока регистров соединена с группой информационных и адресных входов-выходов блока буферной памяти группа входов разрешения чтения-записи соединена с четвертой группой вы-, ходов блока дешифраторов, пятая .группа выходов которого соединена с группой тактовых входов регистра чтения- записи, выход которого соединен с входом чтения-записи блока буферной памяти.

о

46 ных

входов-выходов регистра данных, с группой информационных входов-выходов преобразователя последовательного кода в параллельный и с группой информационных входов-выходов регистра микрокоманд, третья группа информационных вЬтходов которого соединена с второй группой информационных вхо5

0

5

0

5

0

5

которого.соединен с входом запуска преобразователя последовательлого кода в параллельный, информационный вход которого соединен с информационным выходом блока приемопередатчиков, информационный вход которого соединен с информационным выходом регистра данных, синхровход которого соединен с вторым выходоц блока дешифраторов, вторая группа выходов и третья группа информационных входов которого соединены соответственно с группой управляющих входов и с второй группой информационных выходов, блока приемопередатчиков, третья группа выходов блока дешифраторов соединена с группой синхровходов блока регистров, вторая группа информационных выходов блока связи с ЭВМ соединена с группой информационных входов регистра данных, отличающееся тем, что, с целью повышения быстродействия, в него введены блок буферной памяти и регистр чтения записи, причем вторая группа информационных входода- ;вьгходов блока регистров соединена с группой информационных и адресных входов-выходов блока буферной памяти группа входов разрешения чтения-записи соединена с четвертой группой вы-, ходов блока дешифраторов, пятая .группа выходов которого соединена с группой тактовых входов регистра чтения- записи, выход которого соединен с входом чтения-записи блока буферной памяти.

fPu8. 2

УПР.РМ

Г

ЗАПРОС ЛЛЛ ,

РАЗР, njjn

(рут

СТАРТ РУС

F-0

-И г-,

ВЕКТОР

BbJEOP ТЕСТ УСЛОВШ

ти

РАЗРЯДЫ ПЗУ

1,:

УПР. АЛУ

АДРЕС РОН А,В

МН АД (00 г 15}

ЗАПИСЬ

ffrj/fifm

и

считав

ЗАШ. ЗА

шест

СТРОВ

Фив. J

РЛОО

ВЕТВЛЕНИЯ

ТЕСТ Ш

-

8

тн

W

АДРЕС ПЗУ

чх

ИНСТРУКЦЩ

$рг/щ

.

УПР.ЛД УПКРЛ

ти

21

стт

4fW

УПРСГР.тЗП MSlflf

| Патент США № 4241420, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения ЭВМ с накопителями на магнитных дисках | 1985 |

|

SU1280644A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1988-07-15—Публикация

1986-12-29—Подача