Изобретение относится к вычислительной технике и может быть использовано при отладке аппаратуры и программ в реальном масштабе времени.и может найти широкое применение при отладке и эксплуатации микропроцессорных систем и устройств (как однопроцессорных/так и многопроцессорных).

Целью изобретения является повышение производительности при отладке программ и расширение функциональных возможностей за счет возможности отладки восьми - и шестнадцати разрядных микропроцессоров.

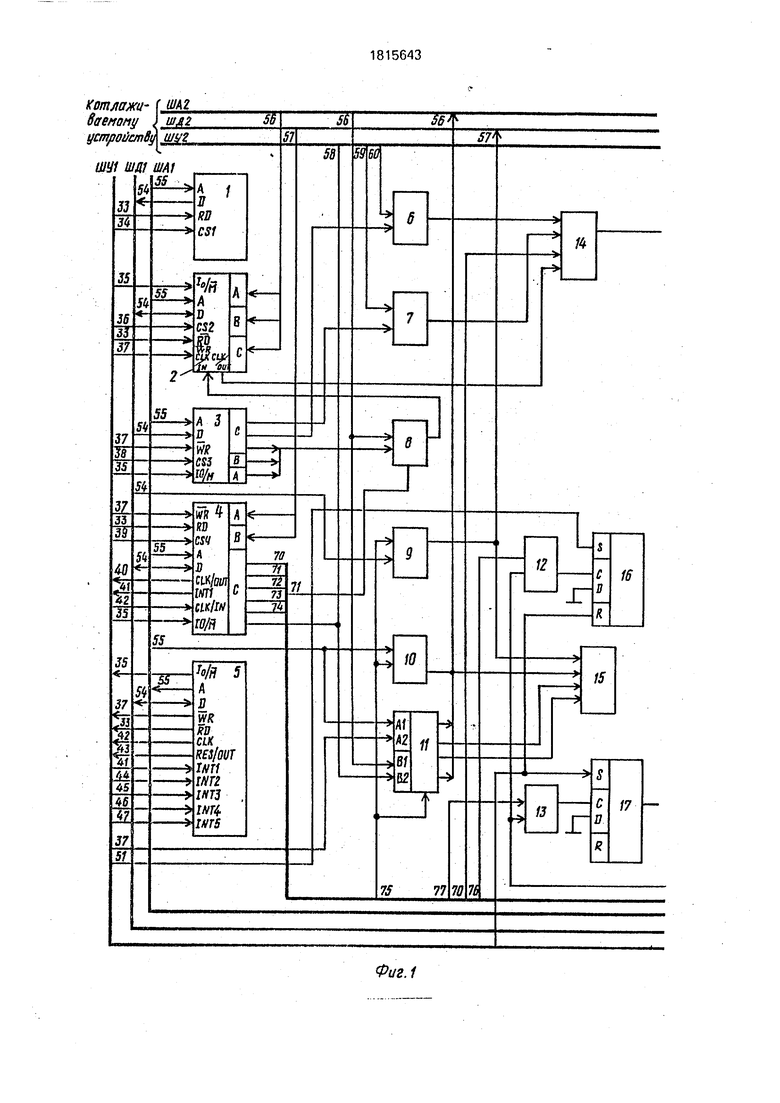

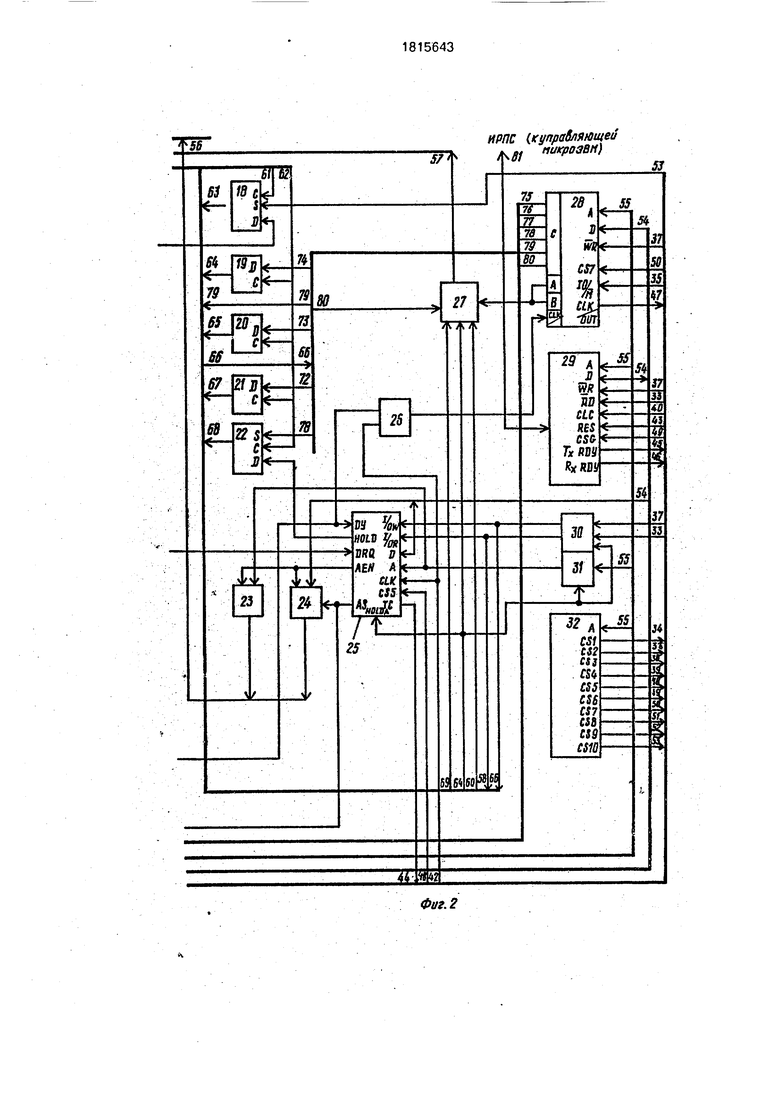

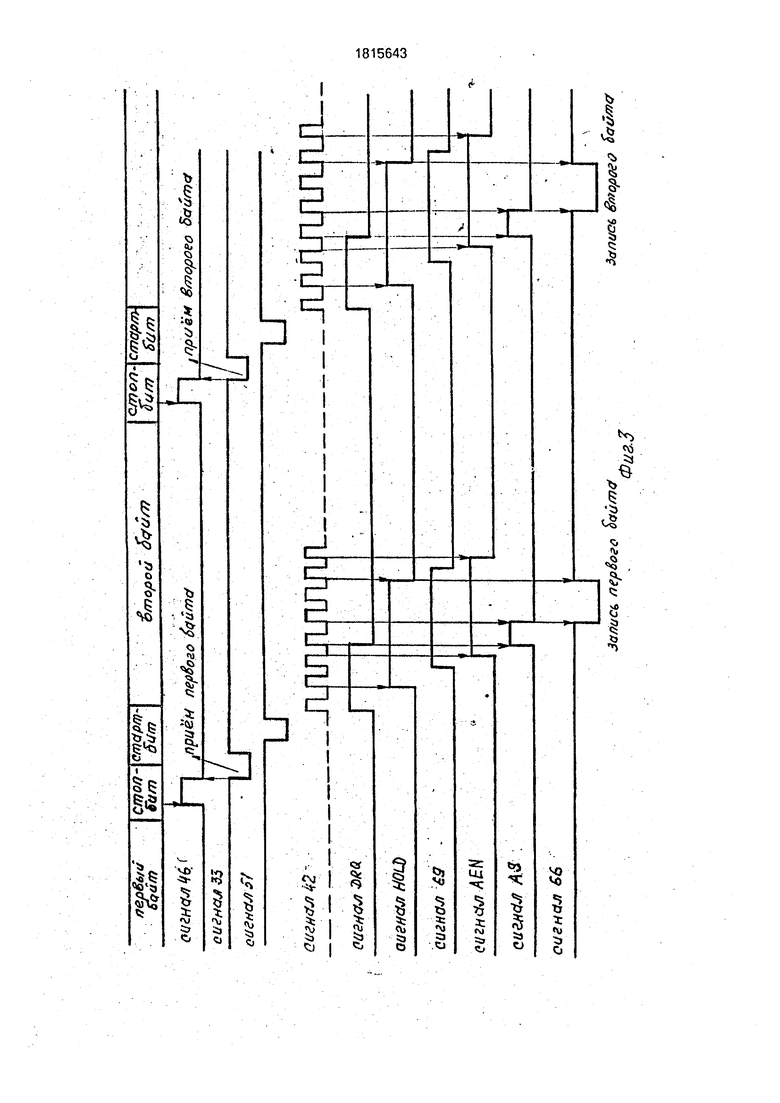

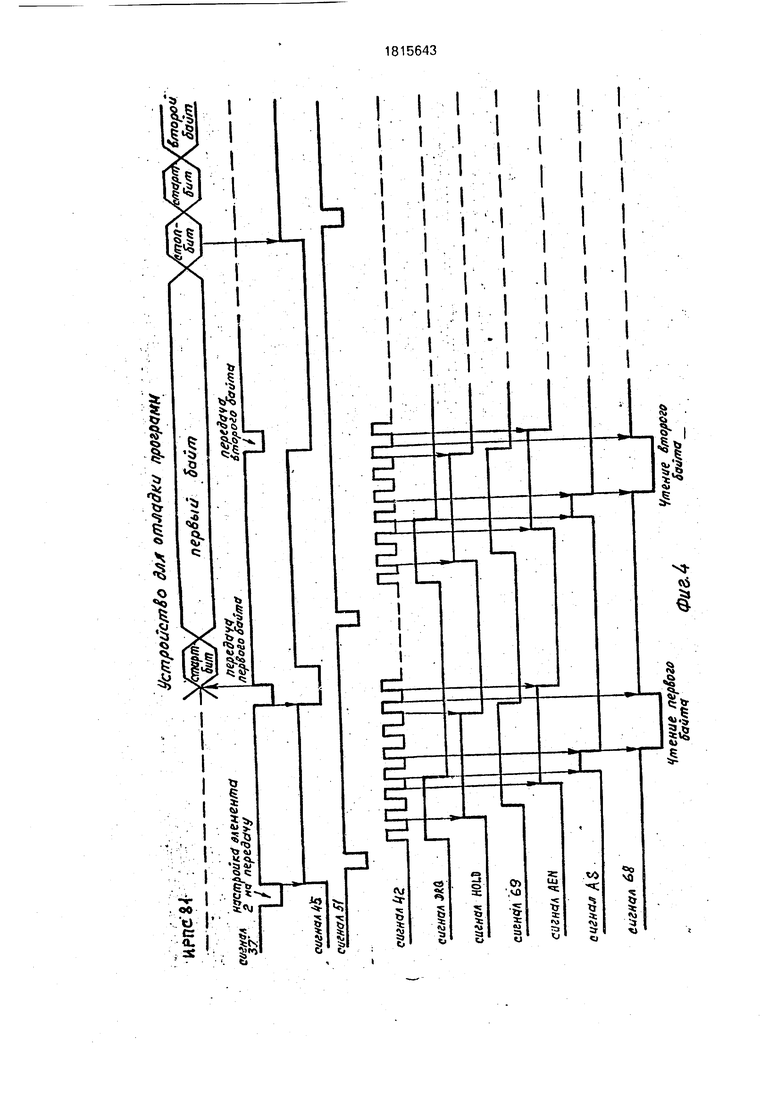

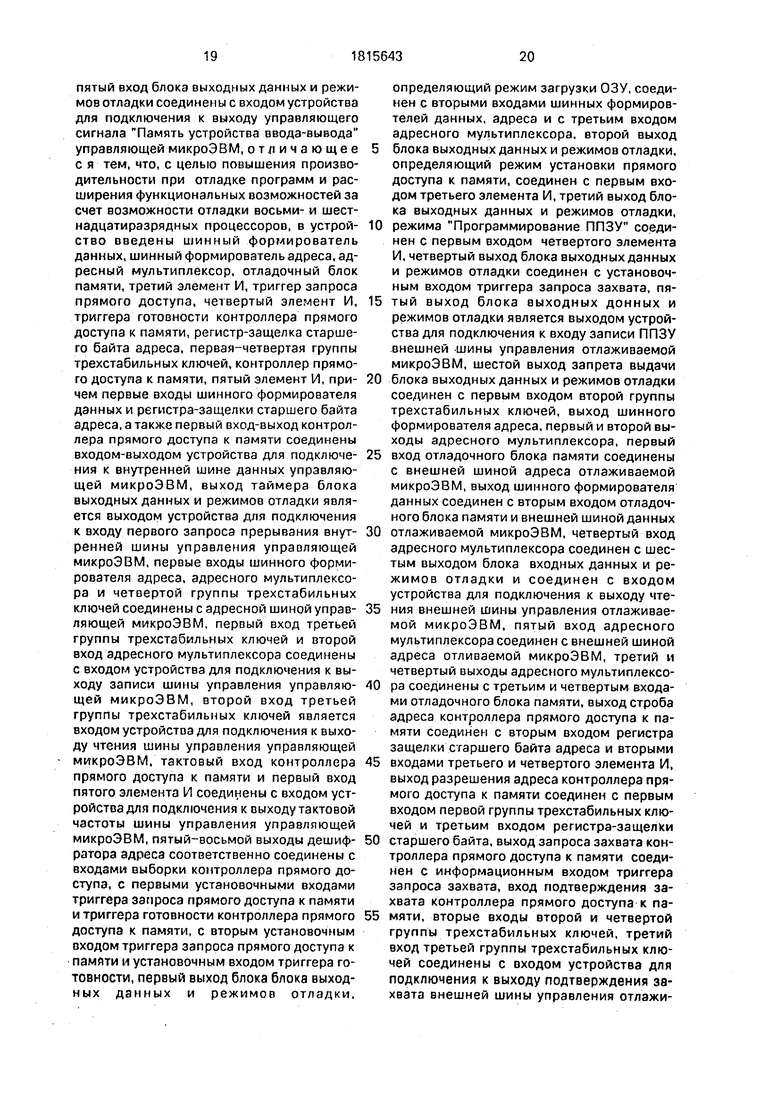

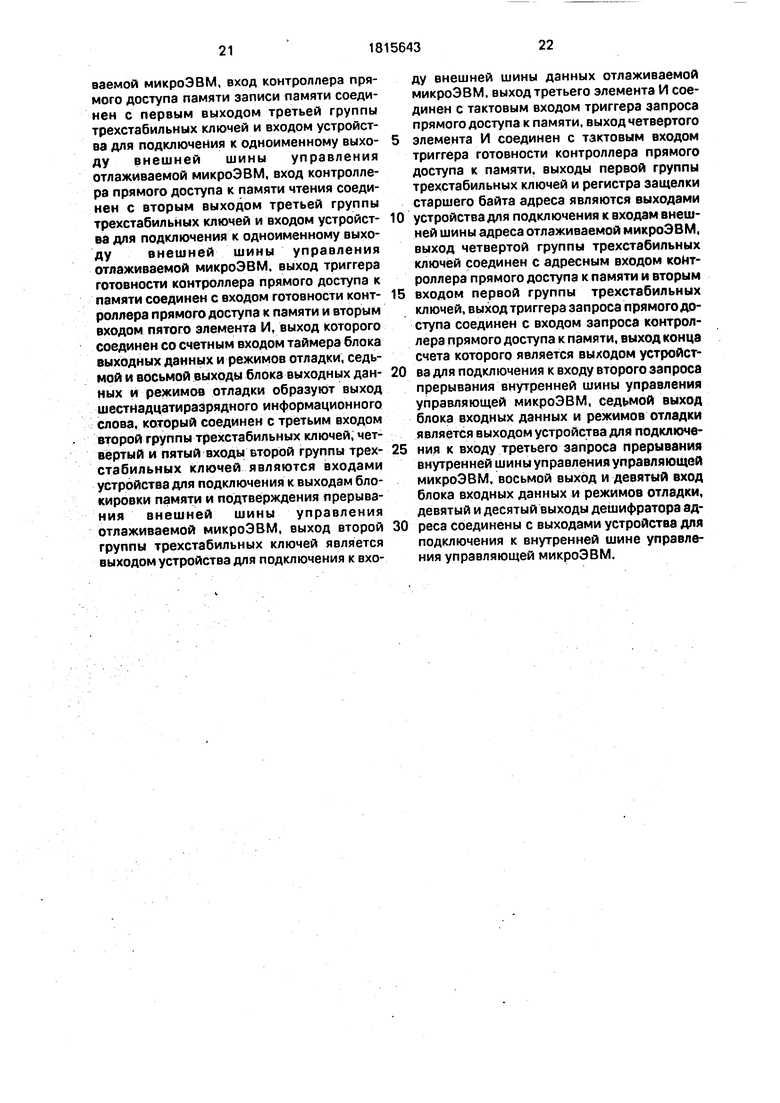

На фиг. 1 и 2 представлена функциональная схема устройства отладки программ; на фиг.З - временная диаграмма в

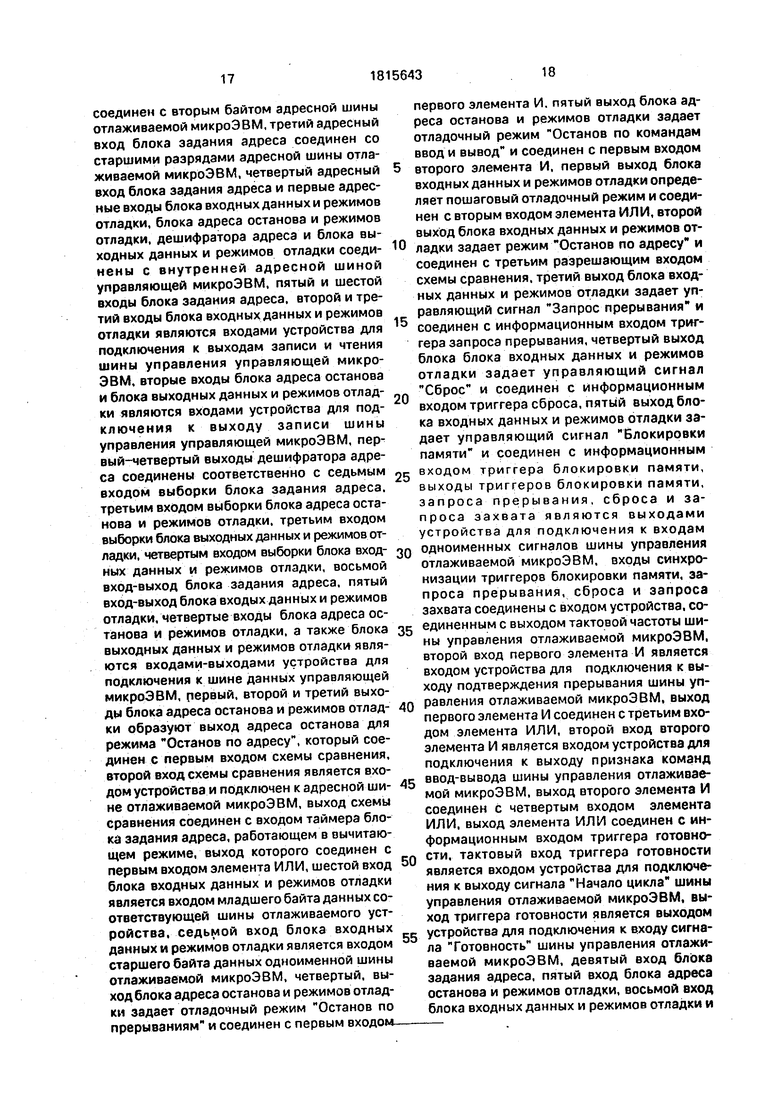

режиме загрузки -информации в отлаживаемое устройство на управляющей микро- ЭВМ; на фиг.4 - временная диаграмма чтения памяти отлаживаемого устройства и ее передачи в управляющую микроЭВМ; на фиг.5- временная диаграмма программирования ПЗУ.

Устройство (фиг.1, 2) содержит ПЗУ 1, блок 2 задания адреса, блок 3 адреса останова и режимов отладки, блок 4 входных данных и режимов отладки, микропроцессор 5. первый и второй элементы И 6. 7, схему сравнения 8, шинные формирователи данных 9 и 10, адресный мультиплексор 11, третий и четвертый элементы адреса И 12, 13, элемент ИЛИ 14. отладочный блок памяти 15, триггер 16 запроса прямого доступа.

00

ел о

&

со

триггер 17 готовности контроллера прямого доступа к памяти, триггер 18 готовности, триггер 19 блокировки памяти, триггер 20 сброса, триггер 21 запроса прерывания, триггер 22 запроса захвата, первую группу 23 трехстабильных ключей, регистр-защелку 24 старшего байта адреса, контроллер 25 прямого доступа к памяти (ПДП), пятый элемент И 26, вторую группу 27трехстабильных ключей, блок 28 выходных данных и режимов отладки, приемопередатчики 29 последовательного канала ИРПС, третью и четвертую группы 30, 31 трехстабильных ключей, дешифратор 32 адреса. На шине ШУ1 показаны следующие сигналы: 33 - сигнал чтения, 34 - сигнал выбора ПЗУ 1, 35 - сигнал память устройства ввода вывода, 36 - сигнал выбора блока 2,37 - сигнал записи, 38 - сигнал выбора блока 3, 3, 39 - сигнал выбора блока 4,40 - сигнал тактовая частота контроллера, последовательного интерфейса, 41 - запрос прерывания обслуживания режима прямого доступа к памяти, 42 -тактовая частота, 43 - сброс, 44 - запрос прерывания конца обмена в режиме прямого доступа к памяти, 45 - запрос прерывания по передаче в отладочную микроэвм, 46 - запрос прерывания по приему информации от отладочной мякроЭВМ, 47 - запрос прерывания для режима программирования ППЗУ.1, 48 - сигнал выбора контроллера 25 ПДП, 49 - сигнал выбора контроллера 29 ИРПС, 50 - сигнал выбора блока 28, 51 сигнал установки триггера 16 запроса прямого доступа, 52 - сигнал установки триггера готовности ПДП, 53 - сигнал установки триггера готовности 18. Кроме внутренней шины ШУ1 устройство отладки имеет внутренние шину данных ШД1 54 и шину адреса ША1 55, а также внешние шины адреса ША2, 56, данных ЩД2 57 и управления ШУ2 для подключения к отлаживаемому микропроцессорному устройству. На ШУ2 показаны следующие сигналы: сигнал Чтение памяти 58, сигнал Признак команд ввода/вывода 59, сигнал Подтверждение прерывания 60, синхросигнал Начало цикла 61, сигнал Тактовая частота 62, сигнал Готовность 62, сигла Блокировка памяти 64, сигнал Сброс 65, сигнал Запись памяти 66, сигнал Запрос прерывания 67; сигнал Запрос захвата 68, сигнал Подтверждение захвата 69.

На внутренней шине устройства показаны следующие сигналы: Установка по- циклового режима 70, Установка режима останова по заданному адресу 71, Установка запроса прерывания 72, Установка

сброса 73, Установка блокировки памяти 74, Загрузка ОЗУ 75, Установка прямого доступа к памяти 76, Программирование ППЗУ 77, Требование захвата 78,3апись

ППЗУ 79, Запрет выдачи 80.

Связь устройства с управляющей мик- роЭВМ осуществляется в ранге интерфейса ИРПС 81.

ПЗУ 1 и микропроцессор 5 предназначе ны для обработки информационного потока.

содержащего команды управления адреса и

данных и поступающие из управляющей

микроэвм в соответствии с заданным жимом работы, задаваемым оператором на клавиатуре терминала. В качестве микропроцессорного элемента может быть использован элемент 1821 ВМ 85. Приемопередатчик 29 последовательного

Q канала предназначен для связи устройства отладки с управляющей микроЭВМ и может быть реализован на базе 580 ВВ 51. Дешифратор микроЭВМ и может быть реализован на базе 580 В В 51. Дешифратор 32 предназ5 начен для выбора программно-управляемых элементов устройства.

Блок 2 со встроенным таймером и ОЗУ предназначен для чтения адреса отлаживаемого устройства и фиксации прохождения

0 отлаживаемой программы через заданный адрес с формированием управляющего сигнала останова по данному адресу в режиме поиска-ожидания. Блок 3 предназначен для задания адреса сравнения и формирования

5 двух управляющих сигналов останов по командам ввода/вывода, останов по прерываниям. Блок 4 со встроенным таймерам и ОЗУ предназначен для чтения данных отлаживаемого устройства, формированию слу0 жебных управляющих сигналов и тактовой частоты блока 29. Блок 28 со встроенным таймером и ОЗУ предназначен для выдачи информации на ШД2, формированиюуправ- ляющих сигналов и запроса прерывания

5 при работе в работе в режиме программирования ППЗУ. В качестве блоков 2, 3, 4, 28 используем БИС 1821 Р.У55. Ключи 30. 31 с третьим состоянием предназначен для сопряжения блока 25 с ШУ1 и ША1. Ключ 27 с

™ третьим состоянием обеспечивает подключение блока 28 к ШД2. Элемент И 25 транслирует тэктовую.частоту 42 на счетный вход таймера программирования ПЗУ, входящего в состав блока 28. Элементы И 6,7 схемы сравнения 8, элемент ИЛИ 14, триггер 18 готовности предназначен для формирования управляющего сигнала готовность 63 а зависимости от выбранного режима отладки. Шинные формирователи 9, 10 предназ5

начены для сопряжения ШД1 и ША1 с ОЗУ 15. Мультиплексор 11 управляет подключением ОЗУ 15 либо к ША1, ШД1. ШУ1, либо к ША2.ЩД2.ДУ2.

Контроллер 25 ПДП предназначен для организации обмена информацией между управляющей микроЭВМ и отлаживаемым устройством. В качестве блока 25 используется БИС ПДП 580 ВТ 57. Элемент И 13 управляет триггером готовности 1.7 контроллера ПДП 25. Регистр 24 защелкивает старший байт адреса, формируемый контроллером 25 и выдает его на ША2. Триггер 16 запроса прямого доступа запускает контроллер 25 в режимах обмена по прямому доступу к памяти. Ключ 23 с третьим состоянием выставляет на ШУ2 младший байт адреса. Триггеры 19, 20, 21, 22 предназначены для формирования сигналов управления сброс, блокировка памяти, запрос прерывания, запрос отлаживаемой микро- ЭВМ. В качестве триггеров могут быть использованы D-триггеры.

Устройство в процессе отладки программ обеспечивает следующие режимы работы:

отладка 8-разрядных микропроцессорных устройств; .

отладка 16-разрядных микропроцессорных устройств;

обмен информацией между управляющей микроЭВМ и отлаживаемым устройством в режиме ПДП;

работа с отладочным ОЗУ;

программирование ПЗУ микропроцессорных устройств;

сброс отлаживаемых микроЭВМ и их запуск;

пошаговое выполнение программ;

останов программы по заданному адресу и количеству циклов;

останов по прерыванию, возникающему в отлаживаемом микропроцессорном устройстве;

останов по командам ВВОД или ВЫВОД;

блокировка памяти отлаживаемого микропроцессорного устройства;

прерывание отлаживаемого микропроцессорного устройстаа, задаваемое через устройство отладки.

Режимы работы задаются программно отладочной микроЭВМ через блоки 4 и 28. Работа устройства начинается с его начальной установки посредством сигнала СБРОС 65 шины ШУ2, подаваемого из отладочной микроЭВМ.

5

0

Этап выбора и назначения устройств осуществляется пользователем, который программно определяет на каком из п системных рангов ИРПС будет осуществляться

сопряжение управляющей микроЭВМ с устройством отладки (фиг.1). Этап загрузки отлаживаемых программ в память микропроцессорных устройств производится посредством управляющей программы

отладочной микроЭВМ. В данном случае устройство отладки по рангу ИРПС приемопередатчиком 29 последовательного канала принимает команду управления, формат которой определяет режим работы, а также начальный и конечный адрес загружаемой зоны памяти отлаживаемого устройства. По заполнению выходного буфера, приемопередатчик 29 вырабатывает сигнал готовность приема R X RDY, который является сигналом запроса прерывания 46 микро- процессора 5. Микропроцессор 5 переходит на подпрограмму обработки запроса 46, считывает входной регистр приемопередат5 чика 29 и в соответствии с информацией команды управления осуществляет настройку программно-управляемых блоков 4, 28 и контроллера 25 ПДП. Одновременно . процессор 5 устанавливает в единичное соо стояние сигнал установка прямого доступа к памяти 76, разблокируя тем самым триггер 16 ПДП. По завершению процесса настройки устройства отладки на режим загрузки, по каналу ИРПС передаются дан5 ные, которые необходимо загрузить в ОЗУ отлаживаемого устройства. Когда байт данных принят приемопередатчиком 29, формируется запрос прерывания 46, микропроцессор 5 переходит на подпрог0 рамму обработки информации, считывает в аккумулятор содержимое приемопередатчика 29 и посылает байт данных в порт А блока 28, где он защелкивается. Затем по команде ВЫВОД микропроцессора 5 фор5 мируется управляющий сигнал 51 установ- китриггера 16 ПДП, который своим выходом переводит вход запроса прямого доступа контроллера ПДП 25 в активное состояние. В ответ на поступление запроса прямого

0 доступа DRQ контроллер 25 ПДП формирует сигнал HOLD запрос-захвата, который подается на Д-вход 22 и тактируется частотой 62. Триггер 22 переходит в другое устойчивое состояние и формирует на ШУ 2 сигнал

° запрос захвата 68. Микропроцессор отлаживаемого устройства переходит в третье . состояние и отвечает сигналом подтверждение захвата 69, поступающим на соответствующий вход контроллера ПДП 25 и

переводящим в третье состояние ключи 30 и 31, через .Которые проходят сигналы записи 37, чтения 33 и младший байт адреса 55 от микропроцессора 5 при настройке контроллера на требуемый режим работы. Одновременно сигнал подтверждение захвата 69 открывает ключ 27, и выходные данные, записанные в порт А блока 28 поступают на ЩД2, а контроллер 25 ПДП формирует сигнал строб адреса AS по переднему фронту которого в регистр 24 адреса записывается старший байт адреса и разрешение адреса AEN, который открывается регистр 24 и элемент 23. Таким образом, на ША 2 будет установлен адрес загружаемого ОЗУ. Кроме этого передним фронтом строба адреса AS опрокидывается триггер 16 и активный уровень сигнала запроса доступа DRQ снимается с соответствующего входа контроллера 25. Затем в соответствии с алгоритмом функционирования контроллер 25 при выставленных адресах и данных на LUA2 и ШД2 формирует сигнал Запись памяти 66 на ШУ2. Таким образом происходит единичный цикл данных в ОЗУ отлаживаемого устройства. Контроллер 25 ждет прихода следующего байта данных по каналу ИРПС 81, когда опять будет выработан запрос прерывания 46 и микропроцессор 5 взведет триггер 16. Использование триггера 16 позволяет синхронизировать по времени относительно медленный по времени обмен по ИРПС и быстродействующий режим ПДП. Скорость обмена управляющей микроЭВМ и отлаживаемого устройства1 будет определяться параметрами канала ИРПС 81. Временная диаграмма функционирования в режиме записи информации в память отлаживаемого устройства представлена на фиг.З.

Передача информации из памяти отлаживаемого устройства в ведущую микро- ЭВМ осуществляется под действием управляющей программы. При этом устройство отладки по каналу ИРПС приемопередатчиком 29 принимает команду управления, формат которой определяет режим работы, а также начальный и конечный адрес памяти отлаживаемого устройства.

По Приему приемопередатчиком 29 команды управления формируется запрос прерывания 46. Микропроцессор 5 переходит на подпрограмму обработки запроса прерывания 46, считывает входной регистр приемопередатчика 29 и в соответствии с содержимым команды управления осуществляет настройку блоков 4,28 и контроллера 25 ПДП на режим чтения памяти, причем

порт А блока 4 настраивается на режим стробируемого чтения, когда входная- информация защелкивается во входном буфере по переднему фронту сигнала чтения

памяти 58. Кроме того, микропроцессор 5 устанавливает в единичное состояние сигнал установка прямого доступа в памяти 76 и сигнал запрет выдачи 80, который в состоянии захвата ША2, ШД2. и ШУ2 блокирует передачу содержимого блока 28 через ключ 27. Затем микропроцессор 5 по команде ВЫВОД настраивает приемопередатчик 29 на режим передачи, при этом формируется сигнал готовности передачи Т X RDY, который является запросом прерывания 45. При его появлении происходит переход на соответствующую подпрограмму, в кото- рой по команде ВЫВОД формируется управляющий сигнал 51 установки триггера 16 запроса ПДП. Триггер 16 своим выходом переводит в активное состояние вход DRQ запроса прямого доступа контроллера 25 ПДП. Затем контроллер 25 ДПД формирует

сигнал ЗАПРОС захвата HOLD, который подается на D вход триггера 22 захвата и тактируется частотой 62. Триггер 22 переходит в другое устойчивое состояние информирует на ШУ2 сигнал запрос захвата 68.

Микропроцессор 5 отлаживаемого устройства переходит в третье состояние и отвечает сигналом подтверждение захвата 69, поступающим на контроллер 25 ПДП и переводящим в третье состояние ключи 30 и

31. через которые поступают управляющие сигналы 37,33 и младший байт адреса 55 от микропроцессора при настройке контроллера 25 ПДП на данный режим работы. В соответствии с алгоритмом функционирования контроллер 25 ПДП формирует сигнал AS строб адреса, по переднему фронту которого в блок 4 записывается старший байт адреса и AEN разрешение адреса, которым открывается регистр 24 и элемент 23. Таким

образом на ША2 будет установлен адрес считываемого ОЗУ. Затем контроллер 25 устанавливает сигнал чтение памяти 58 на ШУ2 и его задним фронтом в блок 4 защелкиваются данные с ШД2. Блок 4 выставляет

запрос прерывания 41, по которому микропроцессор считывает соответствующий порт, выполняя команду ВВОД, и по команде ВЫВОД байт данных записывает в приемопередатчик 29 и принимает от него

сигнал готовность передачи Т X RDY, который является запросом прерывания 45, по которому начинается очередной цикл чтения памяти отлаживаемого устройства. Конец обмена, характеризуемый обращением

к последнему адресу памяти отлаживаемого устройства, сопровождается формированием соответствующего сигнала ТС, который подается на один из входов 44 запроса прерывания. Поэтому запросу44 микропроцессор 5 выходит из программы обмена по каналу прямого доступа. Временная диаграмма функционирования в режиме чтения информации из памяти отлаживаемого устройства представлена на фиг.4.

Следующий после загрузки этап прогона программы осуществляется либо в непрерывном режиме, либо по шагам. Пользователь с клавиатуры видеотерминала набирает соответствующую отладочную директиву, которая представляется определенной командой управления, передаваемой в устройство отладки по каналу ИРПС 81 и обрабатывается микропроцессором 5 . Требуемый режим работы определяется состоянием порта С блока 4, запись информации в который производится по сигналу 37. В этом случае внутренний управляющий сигнал 74, поступающий на Д-вход триггера 19 блокировки памяти и сигнала 73, поступающий на Д-вход триггера 20 сброса обеспечивают сигналы блокировка памяти 64 и сброс 65 уровня лог.О, В случае непрерывного режима работы в порте С блока 4 устанавливаются в состояние лог. О сигналы 70, 71 и два разряда порта С блока 3, поступающие на элементы И6 и И7, в результате чего с выхода элемента ИЛИ 14 на Д-вход триггера готовности поступает лог. О и формируется единичный сигнал ШУ2 -63 готовность.

При работе в режиме выполнения отлаживаемой программы по шагам устанавливается в единичное состояние сигнал 70, который через элемент ИЛИ 14 поступает на Д-вход триггера 18. На С-вход поступает сигнал 61 - начало цикла. В результате формируется нулевой сигнал готовность 63. После чего отлаживаемое устройство переходит в состояние ожидания, на ШД2 и ША2 будут находиться текущие значения данных и адресов. Микропроцессор 5 по команде ВВОД считывает блок 2 адреса и порты А и В блока данных 4, а затем через приемопередатчик 29 передает их содержимое в управляющую микроЭВМ. Прогон отлаживаемой программы на шаг осуществляется установкой триггера 18 готовности в единичное состояние путем подачи управляющего сигнала 53 на Р вход.

Функционирование устройства в режиме прогона рабочих программ с признаком останова определяется установкой в еди

ничное состояние сигналов 71 - задание режима останов по адресу, задание режима останов по прерываниям (поступает с порта 6 блока 2 на элемент 6), задание ре- жима останов по командам ВВОД и ВЫВОД (поступает с порта С блока 2 на элемент 7).

При отладке рабочих программ с остановом по командам ВВОД и ВЫВОД устанавливется в единичное состояние бит порта С блока 2, поступающий на первый вход элемента И 7. На второй входэлемен-о та И 7 поступает сигнал ШУ2 59, признак команд ВВОДА/ВЫВОДА. Выход элемента

«у| ч соединен с одним из четырех входов элемента ИЛИ 14, на выходе которого будет установлен уровень лог. 1 при наличии в отлаживаемой программе команд ВВОДА и ВЫВОДА. В этом случае на Д-вход триггера готовности 18 поступает лог. Г и по приходу управляющего сигнала ШУ2 61 начало команды на С-вход триггера 18 будет сформирован сигнал готовность 63 с уровнем лог. О. Отлаживаемое устройство переходит в состояние ожидания. На ША2 будет установлен адрес устройства ввода/вывода, на ШД2 считываемые или запи- сываемые во внешнее устройство данные, в

зависимости от того, как выполняется команда ВВОД или ВЫВОД.

Затем микропроцессор 5 по команде ВВОД считывает ШД2 и ША2 соответственно через блоки 2, 4 и через приемопередатчик 29 передает их в управляющую микроЭВМ. Пуск программы после останова осуществляется переустановкой триггера 18 готовности управляющим сигналом 53. При отладке рабочих программ в режиме останов по прерываниям устанавливается в единичное состояние бит порта С регистра, поступающий на первый вход элемента И 6. На второй вход этого элемента поступает сигнал ШУ2 60 подтверждение

прерывания. Выход элемента И 6 соединен с одним из четырех входов элемента ИЛИ 14, на выходе которого будет установлен уровень лог. 1 при наличии в отлаживаемой программе подтверждения

прерывания. В этом случае на Д-вход триггера готовности 18 поступает лог. 1й и по приходу управляющего сигнала ШУ2 61 начало команды на С-вход триггера будет сформирован сигнал 63 готовность с уровнем лог. О. Отлаживаемое устройство переходит в состояни-э ожидания. На ША2 будет находиться адрес возврата в отлаживаемую программу по завершению обработки прерываний, на ШД2 - код команды

RESTART, определяющий вектор прерываний. Считывание шин ШД2 и ША2 производится так же, как ив цикле ВВОД и ВЫВОД.

При отладке рабочих программ в режи- ме останов по адресу микропроцессорное устройство переходит в состояние ожидания, когда отлаживаемая программа проходит через заданный дрес останова требуемое количество циклов, Для этой це- ли по каналу ИРПС 81 микропроцессор 5 принимает информацию, содержащую тип режима отладки (в данном случае останов по адресу, адрес останова и количество цик- лов). Затем по команде ВВОД осуществля- ется запись в блок 3 адреса останова, а его встроенный таймер настраивается на требуемое количество циклов прохождения заданного адреса. Запуск режима осуществляется установкой в единичное состояние управляющего сигнала 71 установка режима останова по заданному адресу блока 4. В этом случае открывается схема сравнения 8, которая осуществляет сравне- ние адреса останова, записанного в блок 3, с текущим значением ША2. В случае совпадения адресов схема 8 вырабатывает сигнал равенства. Выход элемента 8 соединен со счетным входом вычитания таймера блока 2, Когда значение таймера станет нулевым, т.е. программа пройдет заданное количество цикло, формируется сигнал переноса, ко- торый поступает на один из входов элемента ИЛИ 14, а выход элемента ИЛИ 14 связан с Д-входом триггера готовности 18. Таким образом, на Д-входе триггера 18 появится логическая единица при условии нулевого значения таймера блока 2. Триггер готовности 18 сформирует сигнал готов- ность 63 по переднему фронту сигнала 61 начала команды, идущего на С-вход. Процессор отлаживаемого устройства перейдет в состояние ожидания. На ША2 будет находиться адрес останова, на ШД2 соответст- вующие этому адресу данные. Считывание шин микроЭВМ производится так же, как и в предыдущих режимах работы с остановом.

Помимо формирования сигнала готовность устройство может формировать сиг- нал 65 сброс, поступающий на отлаживаемую микроЭВМ. Для этого служит триггер 20. На Д-вход поступает управляющий сигнал 73, который устанавливается в состояние логической единицы через соответствующий разряд порта М блока 4. На С-вход триггера 20 принимается тактовая частота 62. Снимается сброс подачей на Д-вход триггера 20 нулевого сигнала 73 по переднему фронту тактовой частоты 62.

Применение триггера в схеме формирования сброса необходимо для того, чтобы асинхронный сигнал, сформированный в порте С блока 4 был переведен к временной диаграмме работы отглаживаемой микро- ЭВМ. Для этой же цели синхронизации управляющих сигналов 72, 76, 74 используются триггер 21 запроса прерывания, триггер запроса 22 захвата и триггер 19 блокировки памяти.

Помимо выше перечисленных, устройство отладки программ обеспечивает режим работы с отладочным ОЗУ 15, необходимость введения которого обусловлена следующими причинами.

Отладка программного обеспечения микропроцессорных устройств включает в себя прогон программ в реальном масштабе времени и их корректировку по результатам выполнения команд памяти. Так как отлаживаемые устройства имеют в своем составе ПЗУ, то естественно вести отладку программ в области адресов ПЗУ не представляется возможным. Для обеспечения работы в требуемой зоне адресов в устройстве имеется отладочное ОЗУ, в которое загружается рабочая программа из управляющей микроЭВМ по каналу ИРПС 81, а затем это ОЗУ 15 переключается на шины адреса, данных и управления микропроцессорного устройства и подается сигнал блокировка памяти 64. который отключает ПЗУ, место которой занялоотла- дочное ОЗУ 15. При работе в режиме загрузки отладочного ОЗУ 15 микропроцессор 5 по каналу ИРПС 81 принимает команду управления, содержащую тип режима работы и декодирует ее. Затем в соответствий с заданным режимом по команде ввод устанавливается в единичное состояние управляющий сигнал 78 требование захвата путем обращения к соответствующему биту порта С блока 28. Сигнал 78, поступает на S вход триггера запроса захвата 22, устанавливает в единичное состояние сигнал 68 за- прос захвата , в результате чего микропроцессор отлаживаемого устройства переходит в состояние захвата и отключается от ША2 и ШД2, которые связаны с соответствующими входами отладочного ОЗУ 15. Следующей командой ВВОД устанавливается в единичное состояние управляющий сигнал 75 загрузка ОЗУ, который открывает шинные формирователи данных 9 и адресов 10, подключая таким образом ОЗУ 15 к внутренним шинам данных ШД1 и

адресов ША1. Этим же сигналом 75 мультиплексор 11 подключает к ОЗУ 15 старшие адреса ША1 и сигнал запись 37. Таким образом ОЗУ 15 подключается к внутренним шинам ШД1, ША1 и ШУ1. Затем по каналу ИРПС 81 на приемопередатчик 29 поступает массив данных, которые необходимо загрузить в ОЗУ 15. Микропроцессор 5 по запросу прерывания 46 принимает поступающую информацию и формирует цикл записи ее в ОЗУ 15. Для того, чтобы в это время не произошло обращение к ОЗУ блоков, 2, 3, 4, 28 адресные поля и ОЗУ 15 должны быть разнесены, По завершению обмена сигнал загрузка ОЗУ 75 снова устанавливается в состояние в состояние логического нуля, шинные формирователи 9, 10, переходят в третье состояние и как следствие ША1 и ШД1 отключаются от ОЗУ 15, а мультиплексор 11 переключается на ША2 и ШУ2. Таким образом отладочное ОЗУ будет подключено к микропроцессорному устройству. Для того, чтобы пользователь мог работать в данном режиме необходимо установить единичный сигнал 74 блокировка памяти и нулевой сигнал запрос захвата 78 по команде ВЫВОД с обращением к порту С блока 28. В этом случае блокируется ПЗУ микропроцессорного устройства и микропроцессор отлаживаемого устройства выходит из захвата, а вместо ПЗУ подключается ОЗУ 15.

Следующий этап после загрузки рабочих программ в память отлаживаемого устройства, их прогона и корректировки заключается в программировании ПЗУ с ультрафиолетовым стиранием. В этом случае устройство отладки по рангу ИРПС приемопередатчиком 29 последовательного канала принимает команду управления, формат которой определяет режим работы, а также начальный и конечный адрес программируемого ПЗУ и вырабатывает запрос прерывания 46, поступающий на соответствующий вход микропроцессора 5. Микропроцессор 5 переходит на подпрограмму обработки прерываний и в соответствии с кодом команды управления осуществляет настройку программных блоков 4,328 и контроллера 25 ПДП. Затем производится настройка встроенного таймера блока 28 на временную задержку 50 мсек, необходимую выдержать для соблюдения временной диаграммы программирования ПЗУ с УФ стиранием.

После передачи по ИРПС команды управления и настройки устройства на режим программирования осуществляется пере

сылка массива данных из управляющей мик- роЭВМ в ОЗУ блоков 4, 28. Затем микропроцессор, загрузив последний байт информации в п.амять, по команде ВЫВОД защелкивает первый байт в порт А блока 28 и устанавливает в состояние логического нуля управляющий сигнал 76 установка прямого доступа к памяти, блокируя тем самым С вход триггера 16 запроса ПДП.

Следующей командой ВЫВОД формируется управляющий сигнал 51, поступающий на S-вход триггера 16, который переводит вход запроса прямого доступа DRQ контроллера 26 в активное состояние. В ответ на поступление апроса прямого доступа контроллер 25 формирует сигнал запрос захвата HOLD, который подается на D-вход триггера 22 и тактируется частотой 62. Триггер 22 формирует на ШУ2 единичный сигнал 68 Запрос захвата. Микропроцессор отлаживаемого устройства отключается от ШД2, ДА2, ШУ2 и отвечает сигналом подтзерждение захвата 69, поступающим на соответствующий

вход контроллера ПДП 25 и переводящим в третье состояние элементы 30,31, через которые проходят сигналы записи 37, чтение 33 и младший байт адреса 55 от микропро- цессора 5 при настройке контроллера на

требуемый режим работы.

Одновременно сигнал 69 подтверждение захвата открывает элемент 27 и байт данных, записанный в порте А блока 28 поступает на ШД2, а контроллер ПДП формиРУет сигналы AS строб адреса, по переднему фронту которого в регистр адреса 24 записывается старший байт адреса и сигнал AEN разрешение адреса, которым открывается регистр 24 и элементы 23. Таким образом на ША2 будет установлен адрес программируемого ПЗУ.

Затем в соответствии с алгоритмом функционирования контроллер при выставленных адресах и данных на ША2 и ШД2

формирует сигнал 66, запись памяти на ШУ2. Передний фронт строба адреса AS через элемент И 13 при единичном сигнале 77 программирование ППЗУ поступает на С-вход триггера 17 готовности контроллера

25 ПДП, последний, в свою очередь, выходом нулевого уровня переводит в состояние ожидания контроллер 25, в результате чего на ША2, ШД2 будут удерживаться адрес и данные программирования, а на ШУ2 сигнал 66 запись памяти. Одновременно выходной сигнал триггера 17 открывает элемент И26 и тактовая частота 37 поступает на счетный вход таймера блока 28, настроенного на 50 мсек. Для соблюдения

временной диаграммы программирования БИС ППЗУ с УФ стиранием микропроцессор через время не менее 4 мксек после выдачи управляющего сигнала 51 по команде ВЫВОД установкой определенного бита порта С регистра 28 формируется сигнал 79 запись ППЗУ.

По истечении 50 мсек, необходимых для

программирования ППЗУ, таймер регистра выдает одиночный импульс 47, который по- ступает на один из входов запросов прерывания микропроцессора 5. Последний переходит на подпрограмму обработки прерывания, снимает управляющий сигнал 79, а сигналом 52 установка триггера готовно- С.ТИ ППД через триггеры 16, 17 выводит контроллер из цикла ожидания с завершением захвата шин ША2 и ШД2. Программирование следующей ячейки памяти осуществляется по тому же алгоритму с записью очередного байта информации в порт А блока 28. Временная диаграмма данного отладочного режима представлена на фиг.5.

Работа с восьмиразрядными или шест- надцатиразрядными микропроцессорными устройствами определяется пользователем перед началом отладки. В этом случае задается конфигурация программно-доступных портов блоков 2, 3, 4, 28. Для отладки вось- миразрядных процессоров испоьзуются порты А, В блоков 2,3, порты А блоков 4,28. Для отладки шестнадцатиразрядных процессоров используются все порты в соответствии с фиг. 1.

В качестве отладочной микроЭВМ могут использоваться отечественные микро- ЭВМ ИСКРА 1030, С-1840, ЕС-1810 и другие совместно с сервисным периферийным оборудованием. Стандартное програм- мное обеспечение указанных микроЭВМ для работы с предлагаемыми п устройствами расширено дополнительным интерпретатором командной строки и программным монитором.

Интерпретатор командной строки анализирует консольный ввод (с клавиатуры видеотерминала) и в зависимости от введенной информации передает управление на загрузчик операционной системы или загрузчки программного монитора.

При переходе в режим отладки программного обеспечения используется программный монитор, который позволяет работаь как с программой в отлаживаемых микроЭВМ, так и в самой отладочной микроЭВМ.

Процедуры выполнения деректив программного монитора по каналу ИРПС поступают в устройство отладки, где анализируются и обрабатываются, обеспечивая вводи вывод информации на УВВ, работу с памятью и регистрами ввода-вывода и управления ходом выполнения программ отлаживаемых микроЭВМ.

Программный монитор дает возможность пользователю работать по следующим дерективам: заполнение области памяти константой, сравнение двух массивов памяти, перемещение массива памяти, подсчет контрольной суммы области памяти, замена содержимого памяти, вывод на устройство отображения содержимого области памяти, запуск и останов микропроцессора по заданному адресу, трассировка программы, редактирование регистров общего назначения, чтение памяти с ВЫВОДОМ ее содержимого в управляющую микроЭВМ, запись в память отглаживаемого устройства информации из управляющей микроЭВМ, установка номера отлаживаемой микроЭВМ.

Предлагаемое устройство совместно с отладочной микроЭВМ позволяет осуществить полный цикл разработки программного обеспечения: составления, исправления программ, отладки их на микроЭВМ и мик- ро-процессорных устройствах. Помимо ска- занного устройство . обладает программно-аппаратной гибкостью. Так, за счет ввода нескольких устройств обеспечивается многопрограммная отладка микропроцессорных систем, что повышает производительность процесса отладки программ.

С учетом указанных возможностей, предложенное устройство позволяет осуществить полный процесс разработки программного обеспечения, а также контроль и диагностику микропроцессорных устройств.

Формула изобретен и я

Устройство для отладки программ микроЭВМ, содержащее блок задания адреса, блок входных данных и режимов отладки, дешифратор адреса, блок адреса останова и режимов отладки, блок выходных данных и режимов отладки, схему сравнения, первый и второй элементы И, элемент ИЛИ, триггеры готовности, блокировки памяти, запроса прерывания, сброса и запроса захвата, причем первый адресный вход блока задания адреса соединен с первым младшим байтом адресной шины отлаживаемой микроЭВМ, второй адресный вход блока задания адреса

соединен с вторым байтом адресной шины отлаживаемой микроЭВМ, третий адресный вход блока задания адреса соединен со старшими разрядами адресной шины отлаживаемой микроЭВМ, четвертый адресный вход блока задания адреса и первые адресные входы блока входных данных и режимов отладки, блока адреса останова и режимов отладки, дешифратора адреса и блока выходных данных и режимов отладки соединены с внутренней адресной шиной управляющей микроЭВМ, пятый и шестой входы блока задания адреса, второй и третий входы блока входных данных и режимов отладки являются входами устройства для подключения к выходам записи и чтения шины управления управляющей микро- ЭВМ, вторые входы блока адреса останова и блока выходных данных и режимов отладки являются входами устройства для подключения к выходу записи шины управления управляющей микроЭВМ, пер- вый-четвертый выходы дешифратора адреса соединены соответственно с седьмым входом выборки блока задания адреса, третьим входом выборки блока адреса останова и режимов отладки, третьим входом выборки блока выходных данных и режимов отладки, четвертым входом выборки блока входных данных и режимов отладки, восьмой вход-выход блока задания адреса, пятый вход-выход блока входых данных и режимов отладки, четвертые входы блока адреса останова и режимов отладки, а также блока выходных данных и режимов отладки являются входами-выходами устройства для подключения к шине данных управляющей микроЭВМ, первый, второй и третий выходы блока адреса останова и режимов отладки образуют выход адреса останова для режима Останов по адресу, который соединен с первым входом схемы сравнения, второй вход схемы сравнения является входом устройства и подключен к адресной шине отлаживаемой микроЭВМ, выход схемы сравнения соединен с входом таймера блока задания адреса, работающем в вычитающем режиме, выход которого соединен с первым входом элемента ИЛИ, шестой вход блока входных данных и режимов отладки является входом младшего байта данных соответствующей шины отлаживаемого устройства, седьмой вход блока входных данных и режимов отладки является входом старшего байта данных одноименной шины отлаживаемой микроЭВМ, четвертый, выход блока адреса останова и режимов отладки задает отладочный режим Останов по прерываниям и соединен с первым входом5

первого элемента И. пятый выход блока адреса останова и режимов отладки задает отладочный режим Останов по командам ввод и вывод и соединен с первым входом 5 второго элемента И, первый выход блока входных данных и режимов отладки определяет пошаговый отладочный режим и соединен с вторым входом элемента ИЛИ, второй выход блока входных данных и режимов отладки задает режим Останов по адресу и соединен с третьим разрешающим входом схемы сравнения, третий выход блока входных данных и режимов отладки задает управляющий сигнал Запрос прерывания и соединен с информационным входом триггера запроса прерывания, четвертый выход блока блока входных данных и режимов отладки задает управляющий сигнал

П Сброс и соединен с информационным входом триггера сброса, пятый выход блока входных данных и режимов отладки задает управляющий сигнал Блокировки памяти и соединен с информационным

5 входом триггера блокировки памяти, выходы триггеров блокировки памяти, запроса прерывания, сброса и запроса захвата являются выходами устройства для подключения к входам

Q одноименных сигналов шины управления отлаживаемой микроЭВМ, входы синхронизации триггеров блокировки памяти, запроса прерывания, сброса и запроса захвата соединены с входом устройства, со5 единенным с выходом тактовой частоты шины управления отлаживаемой микроЭВМ, второй вход первого элемента И является входом устройства для подключения к выходу подтверждения прерывания шины уп0 равления отлаживаемой микроЭВМ, выход первого элемента И соединен с третьим входом элемента ИЛИ, второй вход второго элемента И является входом устройства для подключения к выходу признака команд

5 ввод-вывода шины управления отлаживаемой микроЭВМ, выход второго элемента И соединен с четвертым входом элемента ИЛИ, выход элемента ИЛИ соединен с информационным входом триггера готовно0 сти. тактовый вход триггера готовности является входом устройства для подключения к выходу сигнала Начало цикла шины управления отлаживаемой микроЭВМ, выход триггера готовности является выходом

5 устройства для подключения к входу сигнала Готовность шины управления отлаживаемой микроЭВМ, девятый вход блока задания адреса, пятый вход блока адреса останова и режимов отладки, восьмой вход блока входных данных и режимов отладки и

пятый вход блока выходных данных и режимов отладки соединены с входом устройства для подключения к выходу управляющего сигнала Память устройства ввода-вывода управляющей микроЭВМ, отличающее с я тем, что, с целью повышения производительности при отладке программ и расширения функциональных возможностей за счет возможности отладки восьми- и шестнадцатиразрядных процессоров, в устройство введены шинный формирователь данных, шинный формирователь адреса, адресный мультиплексор, отладочный блок памяти, третий элемент И, триггер запроса прямого доступа, четвертый элемент И, триггера готовности контроллера прямого доступа к памяти, регистр-защелка старшего байта адреса, первая-четвертая группы трехстабильных ключей, контроллер прямого доступа к памяти, пятый элемент И, причем первые входы шинного формирователя данных и регистра-защелки старшего байта адреса, а также первый вход-выход контроллера прямого доступа к памяти соединены входом-выходом устройства для подключения к внутренней шине данных управляющей микроЭВМ, выход таймера блока выходных данных и режимов отладки является выходом устройства для подключения к входу первого запроса прерывания внутренней шины управления управляющей микроЭВМ, первые входы шинного формирователя адреса, адресного мультиплексора и четвертой группы трехстабильных ключей соединены с адресной шиной управляющей микроЭВМ, первый вход третьей группы трехстабильных ключей и второй вход адресного мультиплексора соединены с входом устройства для подключения к выходу записи шины управления управляющей микроЭВМ, второй вход третьей группы трехстабильных ключей является входом устройства для подключения к выходу чтения шины управления управляющей микроЭВМ, тактовый вход контроллера прямого доступа к памяти и первый вход пятого элемента И соединены с входом устройства для подключения к выходу та кто вой частоты шины управления управляющей микроЭВМ, пятый-восьмой выходы дешифратора адреса соответственно соединены с входами выборки контроллера прямого доступа, с первыми установочными входами триггера запроса прямого доступа к памяти и триггера готовности контроллера прямого доступа к памяти, с вторым установочным входом триггера запроса прямого доступа к памяти и установочным входом триггера готовности, первый выход блока блока выход- ных данных и режимов отладки.

определяющий режим загрузки ОЗУ, соединен с вторыми входами шинных формиров- телей данных, адреса и с третьим входом адресного мультиплексора, второй выход

блока выходных данных и режимов отладки, определяющий режим установки прямого доступа к памяти, соединен с первым входом третьего элемента И, третий выход блока выходных данных и режимов отладки,

0 режима Программирование ППЗУ соединен с первым входом четвертого элемента И, четвертый выход блока выходных данных и режимов отладки соединен с установочным входом триггера запроса захвата, пя5 тый выход блока выходных донных и режимов отладки является выходом устройства для подключения к входу записи ППЗУ внешней шины управления отлаживаемой микроЭВМ, шестой выход запрета выдачи

0 блока выходных данных и режимов отладки соединен с первым входом второй группы трехстабильных ключей, выход шинного формирователя адреса, первый и второй выходы адресного мультиплексора, первый

5 вход отладочного блока памяти соединены с внешней шиной адреса отлаживаемой микроЭВМ, выход шинного формирователя данных соединен с вторым входом отладочного блока памяти и внешней шиной данных

0 отлаживаемой микроЭВМ, четвертый вход адресного мультиплексора соединен с шестым выходом блока входных данных и режимов отладки и соединен с входом устройства для подключения к выходу чте5 ния внешней шины управления отлаживаемой микроЭВМ, пятый вход адресного мультиплексора соединен с внешней шиной адреса отливаемой микроЭВМ, третий и четвертый выходы адресного мультиплексо0 ра соединены с третьим и четвертым входами отладочного блока памяти, выход строба адреса контроллера прямого доступа к памяти соединен с вторым входом регистра защелки старшего байта адреса и вторыми

5 входами третьего и четвертого элемента И, выход разрешения адреса контроллера прямого доступа к памяти соединен с первым входом первой группы трехстабильных ключей и третьим входом регистра-защелки

0 старшего байта, выход запроса захвата контроллера прямого доступа к памяти соединен с информационным входом триггера запроса захвата, вход подтверждения захвата контроллера прямого доступа к па5 мяти, вторые входы второй и четвертой группы трехстабильных ключей, третий вход третьей группы трехстабильных ключей соединены с входом устройства для подключения к выходу подтверждения захвата внешней шины управления отлаживземой микроЭВМ, вход контроллера прямого доступа памяти записи памяти соединен с первым выходом третьей группы трехстабильных ключей и входом устройства для подключения к одноименному выходу внешней шины управления отлаживаемой микроЭВМ, вход контроллера прямого доступа к памяти чтения соединен с вторым выходом третьей группы трехстабильных ключей и входом устройства для подключения к одноименному выходу внешней шины управления отлаживаемой микроЭВМ, выход триггера готовности контроллера прямого доступа к памяти соединен с входом готовности контроллера прямого доступа к памяти и вторым входом пятого элемента И, выход которого соединен со счетным входом таймера блока выходных данных и режимов отладки, седьмой и восьмой выходы блока выходных данных и режимов отладки образуют выход шестнадцатиразрядного информационного слова, который соединен с третьим входом второй группы трехстабильных ключей, четвёртый и пятый входы второй группы трехстабильных ключей являются входами устройства для подключения к выходам блокировки памяти и подтверждения прерывания внешней шины управления отлаживаемой микроЭВМ, выход второй группы трехстабильных ключей является выходом устройства для подключения к входу внешней шины данных отлаживаемой микроЭВМ. выход третьего элемента И соединен с тактовым входом триггера запроса прямого доступа к памяти, выход четвертого

элемента И соединен с тактовым входом триггера готовности контроллера прямого доступа к памяти, выходы первой группы трехстабильных ключей и регистра защелки старшего байта адреса являются выходами

устройства для подключения к входам внешней шины адреса отлаживаемой микроЭВМ, выход четвертой группы трехстабильных ключей соединен с адресным входом контроллера прямого доступа к памяти и вторым

входом первой группы трехстабильных ключей, выход триггера запроса прямого доступа соединен с входом запроса контроллера прямого доступа к памяти, выход конца счета которого является выходом устройства для подключения к входу второго запроса прерывания внутренней шины управления управляющей микроЭВМ, седьмой выход блока входных данных и режимов отладки является выходом устройства для подключения к входу третьего запроса прерывания внутренней шины управления управляющей микроЭВМ, восьмой выход и девятый вход блока входных данных и режимов отладки, девятый и десятый выходы дешифратора адреса соединены с выходами устройства для подключения к внутренней шине управления управляющей микроЭВМ.

Фиг.1

w: T&SStiSSS™1

--/---

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| Устройство для отладки микропроцессорных систем | 1985 |

|

SU1285482A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Система отладки микропроцессорных устройств | 1989 |

|

SU1700559A1 |

| Устройство для отладки программно-аппаратных комплексов | 1990 |

|

SU1795464A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1247877A1 |

| Устройство для отладки программ | 1987 |

|

SU1425685A1 |

| Устройство для отладки программ | 1985 |

|

SU1297064A1 |

| УСТРОЙСТВО ДЛЯ ОТЛАДКИ МИКРОЭВМ | 1990 |

|

RU2015540C1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

Изобретение относится к вычислительной технике и может быть использовано при отладке аппаратуры и программ в реальном масштабе времени. С целью повышения производительности при отладке программ и расширения функциональных возможностей, в устройство, содержащее блок задания адреса, блок входных данных и режимов отладки, дешифратор адреса, блок адреса останова, схему сравнения, первый и второй элементы И, элемент ИЛИ, триггеры готовности, блокировки памяти, запроса прерывания, сброса, запроса захвата, введены микропроцессор, блок выходных данных и режимов отладки, шинный формирователь данных, шинный формирователь адреса, мультиплексор, отладочное ОЗУ, три элемента И, триггер запроса прямого доступа к памяти, регистр-защелка старшего байта адреса, четыре группы трехстабильных ключей, контроллер прямого доступа к памяти, приемопередатчик последовательного канала с соответствующей совокупностью связей. 5 ил. (Л С

Чтение первого faufrtef

Фиг. 4

Чтение Второго байта

5 3

г

SI

| Устройство для отладки программ | 1984 |

|

SU1213482A1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1993-05-15—Публикация

1989-12-05—Подача